实验八程序计数器PC 实验

计算机组成原理--实验报告

实验一寄存器实验实验目的:了解模型机中各种寄存器结构、工作原理及其控制方法。

实验要求:利用CPTH 实验仪上的K16..K23 开关做为DBUS 的数据,其它开关做为控制信号,将数据写入寄存器,这些寄存器包括累加器A,工作寄存器W,数据寄存器组R0..R3,地址寄存器MAR,堆栈寄存器ST,输出寄存器OUT。

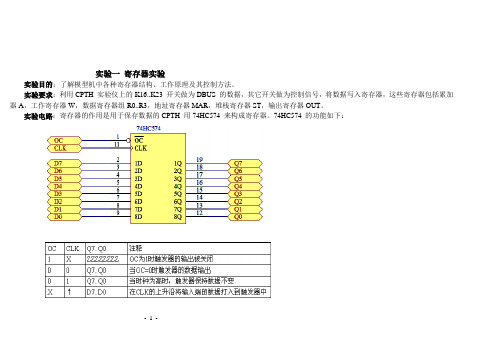

实验电路:寄存器的作用是用于保存数据的CPTH 用74HC574 来构成寄存器。

74HC574 的功能如下:- 1 -实验1:A,W 寄存器实验原理图寄存器A原理图寄存器W 原理图连接线表:- 2 -系统清零和手动状态设定:K23-K16开关置零,按[RST]钮,按[TV/ME]键三次,进入"Hand......"手动状态。

在后面实验中实验模式为手动的操作方法不再详述.将55H写入A寄存器二进制开关K23-K16用于DBUS[7:0]的数据输入,置数据55H置控制信号为:按住STEP脉冲键,CK由高变低,这时寄存器A的黄色选择指示灯亮,表明选择A寄存器。

放开STEP键,CK由低变高,产生一个上升沿,数据55H被写入A寄存器。

将66H写入W寄存器二进制开关K23-K16用于DBUS[7:0]的数据输入,置数据66H- 3 -置控制信号为:按住STEP脉冲键,CK由高变低,这时寄存器W 的黄色选择指示灯亮,表明选择W寄存器。

放开STEP 键,CK 由低变高,产生一个上升沿,数据66H 被写入W 寄存器。

注意观察:1.数据是在放开STEP键后改变的,也就是CK的上升沿数据被打入。

2.WEN,AEN为高时,即使CK有上升沿,寄存器的数据也不会改变。

实验2:R0,R1,R2,R3 寄存器实验连接线表- 4 -将11H、22H、33H、44H写入R0、R1、R2、R3寄存器将二进制开关K23-K16,置数据分别为11H、22H、33H、44H置控制信号为:K11、K10为10,K1、k0分别为00、01、10、11并分别按住STEP 脉冲键,CK 由高变低,这时寄存器R0、R1\R2\R3 的黄色选择指示灯分别亮,放开STEP键,CK由低变高,产生一个上升沿,数据被写入寄存器。

计算机组成原理双端口存储器实验报告

计算机组成原理实验报告实验名称双端口存储器实验专业软件工程学院计算机与软件学院姓名徐振兴班级(2)学号20111344069 指导老师任勇军实验日期2013.5.24 得分一、实验类别原理性+分析性二、实验目的⑵了解双端口静态存储器IDT7132的工作特性及其使用方法;⑵了解半导体存储器怎样存储和读取数据;⑶了解双端口存储器怎样并行读写;⑷熟悉TEC-8模型计算机中存储器部分的数据通路。

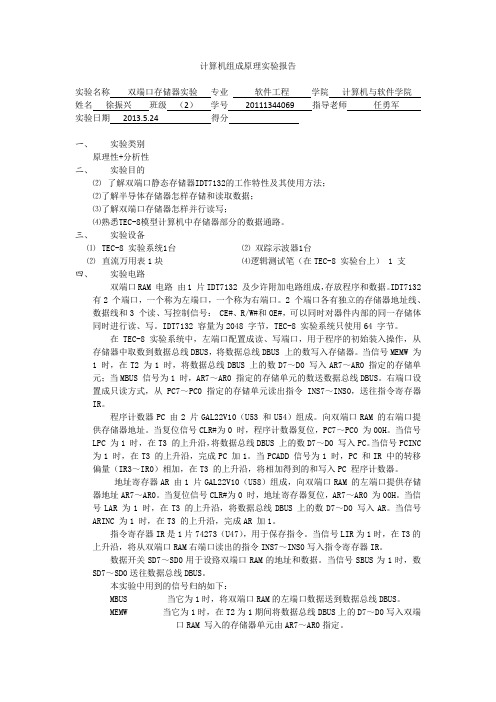

三、实验设备⑴TEC-8 实验系统1台⑵双踪示波器1台⑵直流万用表1块⑷逻辑测试笔(在TEC-8 实验台上) 1 支四、实验电路双端口RAM 电路由1 片IDT7132 及少许附加电路组成,存放程序和数据。

IDT7132 有2 个端口,一个称为左端口,一个称为右端口。

2 个端口各有独立的存储器地址线、数据线和3 个读、写控制信号: CE#、R/W#和OE#,可以同时对器件内部的同一存储体同时进行读、写。

IDT7132 容量为2048 字节,TEC-8 实验系统只使用64 字节。

在TEC-8 实验系统中,左端口配置成读、写端口,用于程序的初始装入操作,从存储器中取数到数据总线DBUS,将数据总线DBUS 上的数写入存储器。

当信号MEMW 为1 时,在T2 为1 时,将数据总线DBUS 上的数D7~D0 写入AR7~AR0 指定的存储单元;当MBUS 信号为1 时,AR7~AR0 指定的存储单元的数送数据总线DBUS。

右端口设置成只读方式,从PC7~PC0 指定的存储单元读出指令INS7~INS0,送往指令寄存器IR。

程序计数器PC 由2 片GAL22V10(U53 和U54)组成。

向双端口RAM 的右端口提供存储器地址。

当复位信号CLR#为0 时,程序计数器复位,PC7~PC0 为00H。

当信号LPC 为1 时,在T3 的上升沿,将数据总线DBUS 上的数D7~D0 写入PC。

当信号PCINC 为1 时,在T3 的上升沿,完成PC 加1。

实验八、九 子程序、中断程序实验

实验八子程序实验一、实验目的1、掌握全局、局部变量的定义与作用;2、熟悉无参子程序和有参子程序的建立和调用方法3、进一步熟悉常用功能指令(加、减、数据类型转换、循环等(另:自学内容已经布置:数学运算指令和数据转换指令)二、实验设备TKPLC-1实验实训装置一台,装有STEP7软件的计算机一台,西门子编程电缆一根、连接导线若干。

三、实验内容与步骤1、不带参数子程序调用例子:设置存储器位或字节的几种方法(注意符号的定义与使用,其它功能指令的学习包含在子程序和中断程序实验中。

下同)本程序描述了用一定值存入预定的存储器位或字节,以及清除存储区内容的几种方法采用下列指令:FILL 设置一个或几个字FOR...NEXT FOR...NEXT循环R 对一位或几位置0输入以下子程序和主程序,注意体会各指令作用及符号的使用。

子程序0功能:如果输入I0.0=1,则把VW200中值复制到VW204至VW216子程序1功能:当输入I0.1=1时,把几个初始数复制到变量存储区。

循环次数取决于VW10中的首次循环数和VW0中的最后一次循环数。

当前循环次数存储在内存字VW20中,首次计数值(50)存储在累加器AC0中,计数值缓冲区首址(& VB100)存储在累加器AC1中,AC1为计数值缓冲区指针,每循环一次的功能:AC0的计数值存入AC1指针所指向的内存单元,AC1指针加2个字节,指向下一个内存字,AC0的计数值加4,直至最后一次循环。

子程序2的功能,使V100.0开始的176个位复位,V204.0开始的112个位复位。

2、带参数子程序的调用例子:求变量区和。

局部变量设置表:子程序功能:求VW100开始的10个数据字的和。

先将整形数转为双整型数,再加,指针值每次增2,循环10次。

注意体会各指令作用。

提醒:欲间接存取字节,将指针用一递增或递减。

欲间接存取字,将指针用二递增或递减。

欲间接存取双字,将指针用四递增或递减。

计算机网络实验八

计算机⽹络实验⼋计算机⽹络实验指导书昆明理⼯⼤学信⾃学院实验⼋:计算机⽹络协议分析实验⼀、实验⽬的:了解各种协议的格式与⼯作机制,学习使⽤Wireshaek协议分析⼯具。

通过eNSP抓包⼯具,分析所获取报⽂的内容。

⼆、实验原理:1.TCP协议通讯的双⽅由IP地址和端⼝号标识。

32位序号、32位确认序号、窗⼝⼤⼩。

4位⾸部长度和IP协议头类似,表⽰TCP协议头的长度,以4字节为单位,因此TCP协议头最长可以是4x15=60字节,如果没有选项字段,TCP协议头最短20字节。

URG、ACK、PSH、RST、SYN、FIN是六个控制位。

16位检验和将TCP协议头和数据都计算在内。

2.UDP协议3.IP协议IP数据报的⾸部长度和数据长度都是可变长的,但总是4字节的整数倍。

对于IPv4,4位版本字段是4。

4位⾸部长度的数值是以4字节为单位的,最⼩值为5,也就是说⾸部长度最⼩是4x5=20字节,也就是不带任何选项的IP⾸部,4位能表⽰的最⼤值是15,就是说⾸部长度最⼤是60字节。

8位TOS字段有3个位⽤来指定IP数据报的优先级(⽬前已经废弃不⽤),还有4个位表⽰可选的服务类型(最⼩延迟、最⼤呑吐量、最⼤可靠性、最⼩成本),还有⼀个位总是0。

总长度是整个数据报的字节数。

每传⼀个IP数据报,16位的标识加1,可⽤于分⽚和重新组装数据报。

3位标志和13位⽚偏移⽤于分⽚。

TTL(Time to live)是这样⽤的:源主机为数据包设定⼀个⽣存时间,⽐如64,每过⼀个路由器就把该值减1,如果减到0就表⽰路由已经太长了仍然找不到⽬的主机的⽹络,就丢弃该包,因此这个⽣存时间的单位不是秒,⽽是跳(hop)。

协议字段指⽰上层协议是TCP、UDP、ICMP还是IGMP。

然后是校验和,只校验IP⾸部,数据的校验由更⾼层协议负责。

IPv4的IP地址长度为32位。

4.ICMP报⽂类型ICMP全称Internet Control Message Protocol(⽹际控制信息协议)。

电子科技大学 PLC实验指导书(答案)

PLC实验指导书目录实验一基本指令实验 (3)实验二常用功能指令实验 (8)实验三交通灯控制实验 (16)实验四刀库捷径选择控制实验 (18)实验五液体混合装置自动控制实验 (22)实验六四级传送带控制实验 (25)实验七步进电机控制实验 (27)实验八邮件分拣控制实验 (29)附录 (33)实验一基本指令实验一、实验目的1.熟悉PLC实验装置。

2.练习手持编程器的使用3.熟悉系统操作。

4.掌握与、或、非逻辑功能的编程方法。

5.掌握定时器指令的使用。

6.掌握计数器的使用。

7.掌握计数器/定时器内部时基脉冲的参数设置。

二、实验内容1.熟悉三菱GX-Developer 编程软件的使用方法,请详细阅读本书附录的全部内容。

2.编制梯形图并写出程序,通过程序判断Y1、Y2、Y3、Y4的输出状态,然后再输入并运行程序加以验证。

3.熟悉时间继电器典型电路的工作原理,在理论上分析运行结果,预先写出程序的调试步骤。

三、实验原理1.线圈驱动指令LD、LDI、OUTLD:取指令。

表示一个与输入母线相连的常开接点指令,即常开接点逻辑运算起始。

LDI:取反指令。

表示一个与输入母线相连的常闭接点指令,即常闭接点逻辑运算起始。

OUT:线圈驱动指令,也叫输出指令。

LD、LDI两条指令的目标元件是X、Y、M、S、T、C,用于将接点接到母线上。

也可以与ANB指令、ORB指令配合使用,在分支起点也可使用。

OUT是驱动线圈的输出指令,它的目标元件是Y、M、S、T、C。

对输入继电器X不能使用。

OUT指令可以连续使用多次。

LD、LDI是一个程序步指令,这里的一个程序步即是一个字。

OUT是多程序步指令,要视目标元件而定。

OUT指令的目标元件是定时器T和计数器C时,必须设置常数K。

2.接点串联指令AND、ANIAND,与指令。

用于单个常开接点的串联。

ANI,与非指令。

用于单个常闭接点的串联。

AND与ANI都是一个程序步指令,它们串联接点的个数没有限制,也就是说这两条指令可以多次重复使用。

八位计数器

八位计数器一、实验要求练习在Modesim下编写Verilog程序,熟悉Modelsim运行过程,并学会用Verilog语言编写一个八位计数器。

二、实验内容八位计数器的真值表如下:由真值表可设计源代码如下:1.代码(1)功能模块:module Counter(jcounter,clk,rst);//输入和输出端口声明output [7:0] jcounter;input clk,rst;reg [7:0] jcounter;//使用always语句,且为多个电平触发always @(posedge clk or negedge rst)if(!rst)jcounter<=0;elsebeginif(!jcounter[0])jcounter[7:0]<={1'b1,jcounter[7:1]};elsejcounter[7:0]<={1'b0,jcounter[7:1]};endendmodule(2)测试模块:module stimulus;//设置变量reg clk,rst;wire [7:0] jcounter;//实例引用CounterCounter JCounter(.jcounter(jcounter),.clk(clk),.rst(rst));//设置信号的监视initial$monitor($time,"clk=%b,rst=%b,---jcounter=%b\n",clk,rst,jcounter) ;//初始值的设置initialbeginclk=1'b0;rst=1'b0;#10 rst=1'b1;end//产生时钟always#5 clk=~clk;//结束仿真initial#500 $finish;endmodule2.仿真结果# 0clk=0,rst=0,---jcounter=00000000 ## 5clk=1,rst=0,---jcounter=00000000 ## 10clk=0,rst=1,---jcounter=00000000 ## 15clk=1,rst=1,---jcounter=10000000 ## 20clk=0,rst=1,---jcounter=10000000 ## 25clk=1,rst=1,---jcounter=11000000 ## 30clk=0,rst=1,---jcounter=11000000 ## 35clk=1,rst=1,---jcounter=11100000 ## 40clk=0,rst=1,---jcounter=11100000 ## 45clk=1,rst=1,---jcounter=11110000 ## 50clk=0,rst=1,---jcounter=11110000 ## 55clk=1,rst=1,---jcounter=11111000 ## 60clk=0,rst=1,---jcounter=11111000 ## 65clk=1,rst=1,---jcounter=11111100 ## 70clk=0,rst=1,---jcounter=11111100 ## 75clk=1,rst=1,---jcounter=11111110 ## 80clk=0,rst=1,---jcounter=11111110 ## 85clk=1,rst=1,---jcounter=11111111 ## 90clk=0,rst=1,---jcounter=11111111## 95clk=1,rst=1,---jcounter=01111111 ## 100clk=0,rst=1,---jcounter=01111111 ## 105clk=1,rst=1,---jcounter=00111111 ## 110clk=0,rst=1,---jcounter=00111111 ## 115clk=1,rst=1,---jcounter=00011111 ## 120clk=0,rst=1,---jcounter=00011111 ## 125clk=1,rst=1,---jcounter=00001111 ## 130clk=0,rst=1,---jcounter=00001111 ## 135clk=1,rst=1,---jcounter=00000111 ## 140clk=0,rst=1,---jcounter=00000111 ## 145clk=1,rst=1,---jcounter=00000011 ## 150clk=0,rst=1,---jcounter=00000011 ## 155clk=1,rst=1,---jcounter=00000001 ## 160clk=0,rst=1,---jcounter=00000001 ## 165clk=1,rst=1,---jcounter=00000000 #3.波形三、实验小结本次实验之前,我对计数器的功能、结构有一定的了解,但对于Verilog语言不是很了解。

计算机组成原理实验报告

计算机组成原理实验报告实验报告运算器实验⼀、实验⽬的掌握⼋位运算器的数据传输格式,验证运算功能发⽣器及进位控制的组合功能。

⼆、实验要求完成算术、逻辑、移位运算实验,熟悉ALU运算控制位的运⽤。

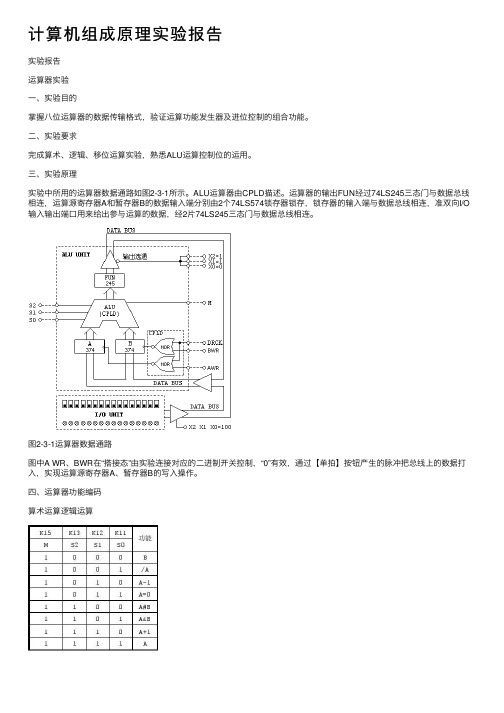

三、实验原理实验中所⽤的运算器数据通路如图2-3-1所⽰。

ALU运算器由CPLD描述。

运算器的输出FUN经过74LS245三态门与数据总线相连,运算源寄存器A和暂存器B的数据输⼊端分别由2个74LS574锁存器锁存,锁存器的输⼊端与数据总线相连,准双向I/O 输⼊输出端⼝⽤来给出参与运算的数据,经2⽚74LS245三态门与数据总线相连。

图2-3-1运算器数据通路图中A WR、BWR在“搭接态”由实验连接对应的⼆进制开关控制,“0”有效,通过【单拍】按钮产⽣的脉冲把总线上的数据打⼊,实现运算源寄存器A、暂存器B的写⼊操作。

四、运算器功能编码算术运算逻辑运算K23~K0置“1”,灭M23~M0控位显⽰灯。

然后按下表要求“搭接”部件控制路。

表2.3.2 运算实验电路搭接表算术运算1.运算源寄存器写流程通过I/O单元“S7~S0”开关向累加器A和暂存器B置数,具体操作步骤如下:2.运算源寄存器读流程关闭A、B写使能,令K18=K17=“1”,按下流程分别读A、B。

3.加法与减法运算令M S2 S1 S0(K15 K13~K11=0100),为算术加,FUN及总线单元显⽰A+B的结果令M S2 S1 S0(K15 K13~K11=0101),为算术减,FUN及总线单元显⽰A-B的结果。

逻辑运算1.运算源寄存器写流程通过“I/O输⼊输出单元”开关向寄存器A和B置数,具体操作步骤如下:2.运算源寄存器读流程关闭A、B写使能,令K17= K18=1,按下流程分别读A、B。

①若运算控制位设为(M S2 S1 S0=1111)则F=A,即A内容送到数据总线。

②若运算控制位设为(M S2 S1 S0=1000)则F=B,即B内容送到数据总线。

实验八 可编程定时计数器8253的Proteus仿真实验

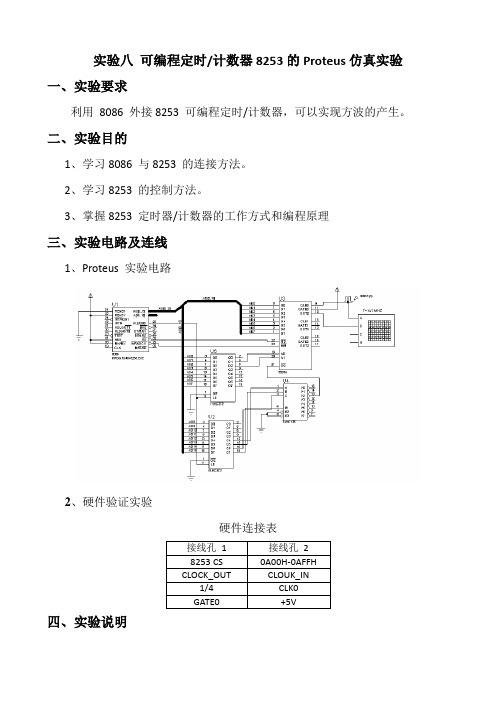

实验八可编程定时/计数器8253的Proteus仿真实验一、实验要求利用8086 外接8253 可编程定时/计数器,可以实现方波的产生。

二、实验目的1、学习8086 与8253 的连接方法。

2、学习8253 的控制方法。

3、掌握8253 定时器/计数器的工作方式和编程原理三、实验电路及连线1、Proteus 实验电路2、硬件验证实验硬件连接表四、实验说明1、8253 芯片介绍8253 是一种可编程定时/计数器,有三个十六位计数器,其计数频率范围为0-2MHz,用+5V 单电源供电。

2、8253的功能用途:(1)延时中断(2)可编程频率发生器(3)事件计数器(4)二进制倍频器(5)实时时钟(6)数字单稳(7)复杂的电机控制器3、8253 的六种工作方式:(1)方式0:计数结束中断(2)方式l:可编程频率发生(3)方式2:频率发生器(4)方式3:方波频率发生器(5)方式4:软件触发的选通信号(6)方式5:硬件触发的选通信号五、实验程序流程图六、实验步骤1、Proteus 仿真a.在 Proteus 中打开设计文档“8253_STM.DSN”;b.建立实验程序并编译,仿真;c.如不能正常工作,打开调试窗口进行调试。

参考程序:CODE SEGMENT;H8253.ASMASSUME CS:CODESTART:JMP TCONTTCONTROEQU0A06HTCON0 EQU0A00HTCON1 EQU0A02HTCON2 EQU0A04HTCONT:MOV DX,TCONTROMOV AL,16H ;计数器0,只写计算值低8 位,方式3,二进制计数OUT DX,ALMOV DX,TCON0MOV AX,20 ;时钟为1MHZ,计数时间=1us*20=20us,输出频率50KHZOUT DX,ALJMP $CODE ENDSEND START2、实验板验证a.通过USB 线连接实验箱b.按连接表连接电路c.运行PROTEUS 仿真,检查验证结果。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验八程序计数器PC 实验

【实验要求】

利用CP226实验箱上的K16…K23 开关做为DBUS 数据的输入端,其它开关做为控制信号的输入端,实现程序计数器PC预置与加1功能。

【实验目的】

掌握模型机中程序计数器PC的功能及其功能实现的工作原理与控制方法,程序执行过程中顺序和跳转的实现。

【主要集成电路芯片及其逻辑功能】

1. 计数器74HC161

本实验所涉及的主要集成电路芯片之一为74HC161,用于实现程序计数器PC预置与加1功能。

74HC161是四位二进制可预置同步加法计数器,芯片包含一条时钟输入线CP、四条数据输入线(P0~P3)、一条清零信号线MR、二条使能信号线CEP和CET、一条预置信号线PE、四条数据输出线(Q0~Q3)、一条进位输出TC(TC= Q0·Q1·Q2·Q3·CET)。

74HC161引脚结构如下图所示,其功能逻辑如下表所示。

2. 数据选择器74HC151

本实验所涉及的主要集成电路芯片之二为74HC151,用于指令执行过程中形成跳转条件。

74HC151为互补输出的8选1数据选择器,芯片包含三条选择控制线(地址端,S0、S1、S2)、

8

条数据输入线(I0~I7)、二条互反输出线(Z 、~Z)、二条使能信号线E 。

74HC161引脚结构如下图所示,其功能逻辑如下表所示。

【实验涉及的逻辑电路及原理】 1. 程序计数器PC

程序计数器PC 是由两片74HC161构成的八位带预置计数器,预置数据来自于数据总线。

PC 输出可以通过由PCOE(低电平有效)控制的74HC245送到地址总线,还可以通过由PCOE_D (低电平有效)控制的另一片74HC245送回到数据总线。

程序计数器PC 实验原理逻辑电路如下图所示,其中PC+1、LDPC 、RST 、PCOE_D 、PCOE 分别为计数器使能、计数器预置、计数器清0、数据总线收发器使能、地址总线收发器使能控制信号,CK 为脉冲信号。

在CPP226实验箱中,PC+1由PCOE 取反产生,LDPC 由指令执行过程中形成跳转条件逻辑电路形成。

当LDPC=0时,在CK 的上升沿,预置数据被打入程序计数器PC 。

当PC+1=1时,在CK 的上升沿,程序计数器PC 加1

D 7

D 7

1

1

1

D 6 D 6 0 1 1 0 D 5 D 5 1 0 1 0 D 4 D 4 0 0 1 0 D 3 D 3 1 1 0 0 D 2 D 2 0 1 0 0 D 1 D 1 1 0 0 0 D 0 D 0 0 0 0 0 1 0 × × × 1 W Y A 0(A) A 1(B) A 2(C) S

程序计数器PC实验原理逻辑电路

2. 跳转条件形成

跳转条件形成电路是由一片74HC151构成,逻辑电路及功能逻辑如下图表所示,其中Cy、Z分别为数据选择器的数据输入信号I0和I1(来自于标志寄存器的进位、零标志位),ELP、IR3、IR2为数据选择器选择控制信号(IR3、IR2来自于指令译码器,ELP为CPP226实验箱中

的特殊信号),LDPC为跳转条件信号(跳转即PC预置为0,顺序即PC加一为1)。

指令执行过程中形成跳转条件逻辑电路

ELP IR3 IR2 Cy Z LDPC

1 X X X X 1

0 0 0 1 X 0

0 0 0 0 X 1

0 0 1 X 1 0

0 0 1 X 0 1

0 1 X X X 0

从跳转条件形成逻辑电路的功能逻辑有:

当ELP=1 时,LDPC = 1,不允许PC被预置。

当ELP=0 时,LDPC由IR3、IR2、Cy、Z确定:

当IR3 IR2 = 1 X 时,LDPC=0,PC 被预置;

当IR3 IR2 = 0 0 时,LDPC=非Cy,当Cy=1时,PC 被预置;

当IR3 IR2 = 0 1 时,LDPC=非Z,当Z=1 时,PC 被预置。

【实验内容及步骤】

(1)实验连接线:实验具体连接线如下表所示。

程序计数器PC实验连接线

连接信号孔接入孔作用状态说明

1J2座J3座将K23-K16接入DBU[7:0]实验模式:手动

2PCOE K5PC输出到地址总线低电平有效

3JIR3K4预置选择1

4JIR2K3预置选择0

5JRZ K2Z标志输入

6JRC K1C标志输入

7ELP K0预置允许低电平有效

8CK已连PC工作脉冲上升沿打入(2)程序计数器PC加一

二进制开关K5、K0分别用于置控制信号PCOE、ELP。

K5(PCOE)K0(ELP)

01

按一次STEP脉冲键,CK产生一个上升沿,程序计数器PC的数据被加一。

(3)程序计数器PC预置

二进制开关K23~K16用于DBUS[7:0]的数据输入,置数据12H。

K23K22K21K20K19K18K17K16

二进制开关K4~K0分别用于置控制信号IR3、IR2、Z、Cy、ELP。

K4(IR3)K3(IR2)K2(Z)K1(Cy)K0(ELP)LDPC PC黄色预置指示灯X X X X11

00X100

00X001

011X00

010X01

1X X X00

每置一次控制信号,按一下STEP键,观察PC黄色预置指示灯的变化。

江西师范大学计算机信息工程学院学生实验报告。