数字电路试题汇总

数字电路试题及答案

数字电路试题及答案二、单项选择题(本大题共10小题,每小题2分,共20分)1、十六进制数(8F)16对应的十进制数是( C )A、141 B、142 C、143 D、1442、逻辑函数L(A,B,C)=(A+B)(B+C)(A+C)的最简与或表达式为( D)A、 (A+C)B+ACB、 AB+(B+A)CC、 A(B+C)+BCD、 AB+BC+AC3、与非门输出为低电平时,需满足 ( D )A、只要有一个输入端为低电平B、只要有一个输入端为高电平C、所有输入端都是低电平D、所有输入端都是高电平4、能够实现“线与”功能的门电路是( D )A、与非门B、或非门C、三态输出门D、集电极开路门5、由与非门构成的基本RS触发器,要使Qn+1=Qn,则输入信号应为(A)A、R=S=1B、R=S=0C、R=1,S=0D、R=0,S=16、要使T触发器Qn+1=Qn,则(B)A、T=QnB、T=0C、T=1D、T=n7、对于JK触发器,要使Q n+1=Q n,则 ( B)A、J=K=1B、J=K=0C、J=1,K=0D、J=0,K=18、为实现D触发器转换成T触发器,题图所示的虚线框内应是.( C )A、与非门B、异或门C、同或门D、或非门9、十六个数据输入端的数据选择器必有地址输入端的个数为 ( D)A、1B、2C、3D、410、一个4位二进制计数器的最大模数是( C )A、4B、8C、16D、32三、简答题(本大题共2小题,每小题5分,共10分)1、数字电路从整体上看可分为几大类?答:(1)、按集成度分,有小、中、大、超大、甚大规模;(3分)(2)、按结构工艺分,有TTL、CMOS集成电路。

(2分)2、最简与-或表达式的标准是什么?答:(1)、包含的与项最少; (3分)(2)、每个与项中变量的个数最少。

(2分)四、分析计算题(本大题共6小题,每小题10分,共60分)1、逻辑电路的输入变量A、B和输出函数F的波形如题3—1图所示,试列出真值表,写出逻辑函数F的逻辑表达式,并画逻辑图。

(完整版)数字电路试题汇总

逻辑门电路(158)一、填空题3。

14.3。

1。

1。

与门是反向逻辑门. (× )2.或非门是反向逻辑门. (√ )3.当一个逻辑门被禁止时,它被激活,允许将一个信号传到输出端.(× )4.当一个二输入与门被一个输入端的逻辑0信号禁止时,它的另一个输入端将成为无关输入。

( √ )5.逻辑门对与门而言是一个禁止信号6.逻辑门对与门而言是一个使能信号7.对于一个二输入或非门而言,如果A =0,B =1,则输出电平应该是输入 逻辑08.数字电路中的三极管在( )区只是一种过渡状态。

放大区9。

影响二极管开关速度的主要因素是由于( )时间的存在。

P N 结内部结电容10.正逻辑或门可以是负逻辑( )门电路. 与11。

在数字电路中,晶体三极管工作在( )状态。

开关12。

正逻辑的约定是高电平为0,低电平为1 。

(× ) 13.用双极性三极管组成开关电路其饱和工作状态的条件是( A )。

A 。

β/I ICS B> B.V V BE 6.0=C.I IC B<D 。

I IBceo ≤14.在数字电路中,高电平代表逻辑“1”状态,低电平代表逻辑“0"状态。

(×) 15.与条件语句中至少需要( )个条件。

2 16.或条件语句中至少需要( )个条件。

217.4输入与门有()种可能的输入状态组合。

16 18.对于5输入与门,其真值表有()行.32 19.与门使用矩形符号表示时,其标志符是()。

&20.对于4输入或门而言,有()种可能的输入状态组合.16 21.5输入或门的真值表有()列。

522.或门使用矩形符号表示时,其标志符是()。

≥123.非门有()个输入.124.非门使用矩形符号表示时,其标志符是().125.与逻辑门相关的两种错误是()。

开路或短路26.I C中常见的内部错误是()。

开路27。

如果向与非门输入数字波形,则什么情况下输出为低电平?答案:当所有输入都是高电平时,与非门输出为低电平。

数字电路期末考试题及答案

数字电路期末考试题及答案一、选择题(每题2分,共20分)1. 在数字电路中,最基本的逻辑关系是:A. 与逻辑(AND)B. 或逻辑(OR)C. 非逻辑(NOT)D. 异或逻辑(XOR)答案:C2. 下列哪个不是数字电路的特点?A. 精确度高B. 稳定性好C. 功耗大D. 抗干扰能力强答案:C3. 一个简单的触发器可以存储多少位二进制信息?A. 1位B. 2位C. 3位D. 4位答案:A4. 以下哪个是组合逻辑电路的特点?A. 有记忆功能B. 无记忆功能C. 可以进行算术运算D. 可以进行逻辑运算答案:B5. 在数字电路中,同步计数器与异步计数器的主要区别是:A. 同步计数器速度更快B. 同步计数器结构更复杂C. 同步计数器计数更准确D. 异步计数器计数更准确答案:A6. 一个4位二进制计数器最多能计数到:A. 15B. 16C. 8D. 4答案:B7. 以下哪个是数字电路中常用的存储元件?A. 电阻B. 电容C. 电感D. 晶体管答案:D8. 以下哪个不是数字电路中的逻辑门?A. NANDB. NORC. XORD. TRIAC答案:D9. 一个完整的数字电路设计流程包括以下哪些步骤?A. 需求分析B. 电路设计C. 仿真测试D. 所有选项答案:D10. 以下哪个是数字电路中的时序逻辑电路?A. 门电路B. 触发器C. 运算放大器D. 模数转换器答案:B二、简答题(每题5分,共20分)1. 简述数字电路与模拟电路的区别。

答案:数字电路主要处理离散的数字信号,具有逻辑功能,而模拟电路处理连续的模拟信号,主要用于信号放大、滤波等。

2. 解释什么是触发器,并说明其在数字电路中的作用。

答案:触发器是一种具有记忆功能的逻辑电路,能够存储一位二进制信息。

在数字电路中,触发器用于存储数据,实现计数、定时等功能。

3. 什么是组合逻辑电路?请举例说明。

答案:组合逻辑电路是由逻辑门组成的电路,其输出只依赖于当前的输入状态,不具有记忆功能。

(完整版)数字电路试题及参考答案

《数字电路》试卷及答案一、【单项选择题】 ( 本大题共20 小题,每题 2 分,共40 分) 在每题列出的四个选项中只有一个选项是切合题目要求的,请将正确选项前的字母填在答题卷相应题号处。

1、关于钟控 RS触发器,若要求其输出“ 0”状态不变,则输入的RS信号应为( A)。

[A] RS=X0[B] RS=0X[C] RS=X1[D] RS=1X2、以下各电路中,( B)能够产生脉冲准时。

[A]多谐振荡器[B]单稳态触发器[C]施密特触发器[D]石英晶体多谐振荡器3、以下逻辑电路中为时序逻辑电路的是(C)。

[A]变量译码器[B]加法器[C]数码存放器[D]数据选择器4、同步时序电路和异步时序电路比较,其差别在于后者(B)。

[A]没有触发器[B]没有一致的时钟脉冲控制[C]没有稳固状态[D]输出只与内部状态相关5、当用专用输出构造的PAL设计时序逻辑电路时,一定还要具备有(A)。

[A]触发器[B]晶体管[C] MOS 管[D]电容6、能将输出端直接相接达成线与的电路有(C)。

[A] TTL 与门[B]或门[C]三态门[D]三极管非门7、 TTL 与非门的剩余脚悬空等效于(A)。

[A] 1[B] 0[C] Vcc[D] Vee8、以下哪一条不是除去竟争冒险的举措(B)。

[A]接入滤波电路[B]利用触发器[C]加当选通脉冲[D]改正逻辑设计9、主从触发器的触发方式是(D)。

[A] CP=1[B] CP上涨沿[C] CP 降落沿[D]分两次办理10、组合型 PLA 是由( A)组成。

[A]与门阵列和或门阵列[B]一个计数器[C]一个或阵列[D]一个存放器11、以下四个数中,最大的数是(B)。

[A] (AF) 16[B] (001010000010)8421BCD[C] (10100000) 2[D] (198) 1012、触发器有两个稳态,储存8 位二进制信息要(B)个触发器。

[A] 2[B] 8[C] 16[D] 3213、以下门电路属于双极型的是(A)。

数字电路试题及答案

数字电路试题及答案一、选择题1. 数字电路中最基本的逻辑门是以下哪一个?A. 与非门B. 或非门C. 与门D. 异或门答案:C2. 在二进制数系统中,用三个比特(bit)可以表示多少个不同的数值?A. 4B. 6C. 8D. 10答案:C3. 下列哪个触发器具有记忆功能?A. 组合逻辑B. 时序逻辑C. D型触发器D. T型触发器答案:C4. 在数字电路中,"0" 和 "1" 分别代表什么逻辑状态?A. 低电平 / 高电平B. 高电平 / 低电平C. 接地 / 供电D. 禁用 / 启用答案:A5. 以下哪种类型的逻辑门是使用晶体管实现开关功能的?A. 模拟门B. 数字门C. 模拟数字门D. 晶体管逻辑门答案:D二、填空题1. 在数字电路中,一个______门输出的高电平可以驱动多个输入端,而不会改变输出电平。

答案:或门2. _______是数字电路设计中的一种基本方法,它将复杂的电路分解为更简单的子电路。

答案:模块化设计3. 在数字电路中,一个______触发器在时钟信号的上升沿改变状态,而______触发器在下降沿改变状态。

答案:D型;JK型4. 一个4位二进制计数器的最大输出值是______。

答案:155. 在数字电路中,______是一种用于存储数据的电路,它可以在没有时钟信号的情况下保持信息。

答案:触发器三、简答题1. 请简述数字电路与模拟电路的主要区别。

答:数字电路处理的是离散的信号,通常只有两种状态(如高电平代表“1”,低电平代表“0”),而模拟电路处理的是连续变化的信号。

数字电路的主要优点是抗干扰能力强,易于实现逻辑运算和存储功能,而模拟电路则更擅长处理连续变化的信号,如音频和视频信号。

2. 什么是组合逻辑和时序逻辑?答:组合逻辑是指其输出仅依赖于当前输入信号的逻辑电路,不包含存储元件,如与门、或门和非门等。

时序逻辑则包含存储元件(如触发器),其输出不仅依赖于当前的输入信号,还依赖于历史状态,因此具有记忆功能。

数电考试题及答案

数电考试题及答案一、选择题(每题2分,共20分)1. 在数字电路中,最基本的逻辑关系是:A. 与逻辑B. 或逻辑C. 非逻辑D. 异或逻辑答案:A2. 下列哪个不是数字电路的特点?A. 高速度B. 低功耗C. 高成本D. 可靠性高答案:C3. 一个D触发器具有几个输入端?A. 1B. 2C. 3D. 4答案:B4. 一个完整的数字系统通常包括哪些部分?A. 输入、处理、存储B. 输入、处理、输出C. 输入、存储、输出D. 存储、处理、输出答案:B5. 下列哪个不是组合逻辑电路的特点?A. 输出只依赖于当前输入B. 输出在输入改变后立即改变C. 有记忆功能D. 结构简单答案:C6. 一个4位二进制计数器最多能计数到:A. 15B. 16C. 255D. 1023答案:B7. 在数字电路中,逻辑门的输入端可以连接多少个其他逻辑门的输出端?A. 1个B. 2个C. 3个D. 无限制答案:D8. 一个简单的数字钟电路至少需要几个计数器?A. 1B. 2C. 3D. 4答案:B9. 逻辑门的输出电压通常分为哪两个电平?A. 高电平、低电平B. 正电平、负电平C. 直流电平、交流电平D. 标准电平、非标准电平答案:A10. 下列哪个是数字电路设计中常用的仿真软件?A. MATLABB. AutoCADC. PhotoshopD. SolidWorks答案:A二、填空题(每空2分,共20分)1. 数字电路中最基本的逻辑关系包括______、______和非逻辑。

答案:与逻辑,或逻辑2. 一个3-8译码器有______个输入端,______个输出端。

答案:3,83. 在数字电路中,常用的计数器类型包括二进制计数器、______计数器和______计数器。

答案:十进制,BCD4. 一个8位寄存器可以存储______位二进制数。

答案:85. 触发器的两个稳定状态是______和______。

答案:0,1三、简答题(每题10分,共30分)1. 请简述数字电路与模拟电路的主要区别。

数字电路试题五套(含答案)汇总

《数字电子技术》试卷一一、 填空(每空1分,共25分)1、(10110)2=( )10=( )16(28)10=( )2=( )16(56)10=( )8421BCD2、最基本的门电路是: 、 、 。

3、有N 个变量组成的最小项有 个。

4、基本RS 触发器的特征方程为_______ ,约束条件是 __.5、若存储器的容量是256×4RAM ,该RAM 有 ___存储单元,有 字,字长_____位,地址线 根。

6、用N 位移位寄存器构成的扭环形计数器的模是________.7、若令JK 触发器的J=K=T 则构成的触发器为_______.8、如图所示,Y= 。

9、如图所示逻辑电路的输出Y= 。

10、已知Y=D AC BC B A ++,则Y = ,Y/= 。

11、组合逻辑电路的特点是_________、___________;与组合逻辑电路相比,时序逻辑电路的输出不仅仅取决于此刻的_______;还与电路 有关。

二、化简(每小题5分,共20分)1、公式法化简++++(1)Y=ABC ABC BC BC A=+++(2)Y ABC A B C2、用卡诺图法化简下列逻辑函数=+++(1)Y BCD BC ACD ABDY=∑+∑(2)(1,3,4,9,11,12,14,15)(5,6,7,13)m d三、设下列各触发器初始状态为0,试画出在CP作用下触发器的输出波形(10分)四、用74LS161四位二进制计数器实现十进制计数器(15分)五、某汽车驾驶员培训班结业考试,有三名评判员,其中A 为主评判员,B 、C 为副评判员,评判时,按照少数服从多数原则,但若主评判员认为合格也可以通过。

试用74LS138和与非门实现此功能的逻辑电路。

(15分)P Q A Q B Q C Q D C T 74LS161 LD CPA B C D CrQ A 、Q B 、Q C 、Q D :数据输出端; A 、B 、C 、D :数据输入端; P 、T :计数选通端;r C :异步复位端;CP :时钟控制输入端;D L :同步并置数控制端;C :位输出端;六、试分析如图电路的逻辑功能,设各触发器的初始状态为0(15分)《数字电子技术》试卷一参考答案一、填空(每空1分,共25分)1、10(22)、16(16);2(11100)、16(1)C ;8421(01010110)BCD 。

数字电路试题及答案

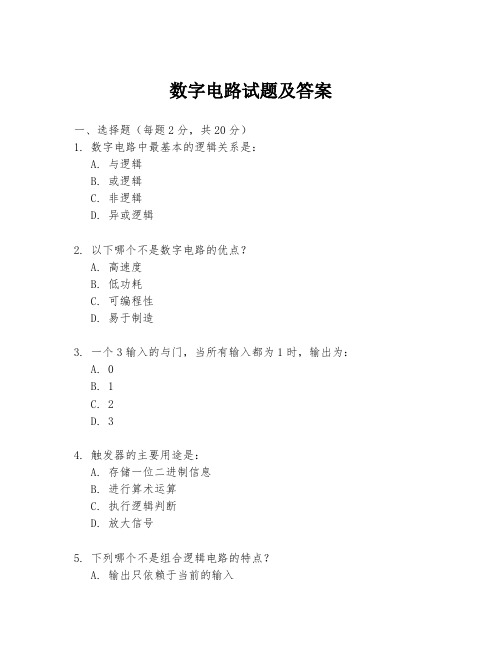

数字电路试题及答案一、选择题(每题2分,共20分)1. 数字电路中最基本的逻辑关系是:A. 与逻辑B. 或逻辑C. 非逻辑D. 异或逻辑2. 以下哪个不是数字电路的优点?A. 高速度B. 低功耗C. 可编程性D. 易于制造3. 一个3输入的与门,当所有输入都为1时,输出为:A. 0B. 1C. 2D. 34. 触发器的主要用途是:A. 存储一位二进制信息B. 进行算术运算C. 执行逻辑判断D. 放大信号5. 下列哪个不是组合逻辑电路的特点?A. 输出只依赖于当前的输入B. 输出可以延迟输入C. 没有记忆功能D. 可以进行复杂的逻辑运算二、填空题(每空2分,共20分)6. 一个典型的数字电路由________、________和输出三部分组成。

7. 一个4位二进制计数器可以计数的最大数值是________。

8. 一个D触发器的两个主要输入端是________和________。

9. 在数字电路中,________是一种常用的同步信号,用于协调电路的时序。

10. 一个3-8译码器可以将3位二进制信号转换为________种可能的输出状态。

三、简答题(每题15分,共30分)11. 简述数字电路与模拟电路的主要区别。

12. 解释什么是时钟信号,并说明它在数字电路中的作用。

四、计算题(每题15分,共30分)13. 给定一个逻辑表达式 Y = A'B + AB',使用卡诺图化简该表达式,并画出相应的逻辑电路图。

14. 设计一个2位二进制计数器,使用D触发器实现,并说明其工作原理。

答案一、选择题1. 答案:A(与逻辑)2. 答案:D(易于制造)3. 答案:B(1)4. 答案:A(存储一位二进制信息)5. 答案:B(输出可以延迟输入)二、填空题6. 答案:输入、处理7. 答案:15(2^4 - 1)8. 答案:数据输入(D)、时钟输入(CLK)9. 答案:时钟信号(Clock Signal)10. 答案:8三、简答题11. 数字电路与模拟电路的主要区别在于:数字电路处理的是离散的数字信号,而模拟电路处理的是连续的模拟信号。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

逻辑门电路(158)一、填空题3.14.3.1.1.与门是反向逻辑门。

(× )2.或非门是反向逻辑门。

(√ )3.当一个逻辑门被禁止时,它被激活,允许将一个信号传到输出端。

(× )4.当一个二输入与门被一个输入端的逻辑0信号禁止时,它的另一个输入端将成为无关输入。

( √ )5.逻辑门对与门而言是一个禁止信号6.逻辑门对与门而言是一个使能信号7.对于一个二输入或非门而言,如果A =0,B =1,则输出电平应该是输入 逻辑08.数字电路中的三极管在( )区只是一种过渡状态。

放大区9.影响二极管开关速度的主要因素是由于( )时间的存在。

P N 结内部结电容10.正逻辑或门可以是负逻辑( )门电路。

与11.在数字电路中,晶体三极管工作在( )状态。

开关12.正逻辑的约定是高电平为0,低电平为1 。

(× )13.用双极性三极管组成开关电路其饱和工作状态的条件是( A )。

A.β/I I CS B> B.V V BE 6.0= C.I I C B < D.I I B ceo ≤14.在数字电路中,高电平代表逻辑“1”状态,低电平代表逻辑“0”状态。

(×)15.与条件语句中至少需要( )个条件。

216.或条件语句中至少需要()个条件。

217.4输入与门有()种可能的输入状态组合。

1618.对于5输入与门,其真值表有()行。

3219.与门使用矩形符号表示时,其标志符是()。

&20.对于4输入或门而言,有()种可能的输入状态组合。

1621.5输入或门的真值表有()列。

522.或门使用矩形符号表示时,其标志符是()。

≥123.非门有()个输入。

124.非门使用矩形符号表示时,其标志符是()。

125.与逻辑门相关的两种错误是()。

开路或短路26.I C中常见的内部错误是()。

开路27.如果向与非门输入数字波形,则什么情况下输出为低电平?答案:当所有输入都是高电平时,与非门输出为低电平。

28.对于5输入的与非门,有()种可能的输入状态组合。

3229.对于4输入与非门,其真值表有()列。

530.对于8输入与非门,所有可能的输入状态组合有()组输入状态能够输出低电平。

一组31.什么情况下或非门的输出为逻辑低电平?答案:只要有一个或多个输入为高电平,则或非门输出为低电平32 .对于4输入的或非门,有()种可能的输入状态组合。

1633.对于5输入与或非门,其真值表有()行。

3234.如果向或非门输入数字波形,则什么情况下输出为低电平?答案:任有一个输入波形为高电平时,或非门输出为低电平。

35.或门和非门应该如何连接才能搭建出或非门?答案:把或非门的输出端接到非门的输入端36.如何正确连接未使用的与非门输入?答案:通过上拉电阻将未使用的与非门输入接到V C C.37.如何正确连接未使用的或非门输入?答案:将未使用的或非门输入接到地。

38.什么是“上拉”电阻?答案:上拉电阻是将某点与V C C连接起来的电阻,它使得该点为高电平。

39.I C门中较常见的是()。

开路40.T T L或非门和或门相比,两者开路输入导致的输出不同。

(√)41.与非门输入短路到地时,会对其输出产生何种影响?答案与非门输入短路到地时,输出总是高电平。

42.或非门输入短路到地时,会对其输出产生何种影响?答案:输出取决于其它输入。

43.或非门输入直接连接到V CC时,会对其输出产生何种影响?答案:输出总是低电平。

44.满足()时,与非门输出为低电平。

所有输入都是高电平45.满足(D)时,或非门输出为低电平。

A.一个输入为高电平B.所有输入都是低电平C.多于一个输入的是高电平D.A和C都对46.执行求补运算的逻辑电路是(D)。

A.与非门B.或非门C.反相器D.以上答案都正确47.什么情况下异或门的输出为1?当两个输入不同时,异或门输出为 1.48.在逻辑运算规则上,异或门和或门有什么区别?当两个输入为1时,异或门输出为0.49.异或门矩形符号中的标准标志符为“=1”,说明其意义?“=1”表示异或运算需要且只需要一个输入为1,才能使输出为 1.50.当异或门的两个输入门都是1(高电平)时,可以判决其输出的唯一状态(√)。

51.如何将异或门用作反相器?将其一个输入端接高电平,另一个输入端接反相的信号。

52.什么情况下异或非门的输出为低电平?当两个输入不同时,异或非门输出为0.53.在逻辑运算规则上,异或非门和或非门有什么区别?当两个输入为1时,异或非门输出为 1.54.异或非门矩形符号的标准标志为小三角形,说明其意义。

小三角形表示输出断言状态为0.55.当异或非门的两个输入门都是高电平时,可以判决其输出的唯一状态(×)。

56.如何将异或非门用作反相器?将其一个输入端接低电平,另一个输入端接反相的信号。

57.与或电路中有()个或门。

158.与或电路中有()个与门。

任意多个。

59.对于两个2输入与门构成的与或逻辑,其输入为A =1,B =0,C =1,D =1,求其输出?与或输出为60.逻辑门的功耗取决于什么?功耗取决于直流电源电压和直流供电电流。

61.异或门的等效逻辑电路包含( B )。

A.两个或门、一个与门和两个非门B.两个与门、一个或门和两个非门C.两个与门和一个或门D.两个或门和一个与门62.异或运算对应的逻辑符号是( )。

⊕63.T T L 器件中应用了( )类型的晶体管。

双极型64.标准T T L 门输出端可线与。

(× )65.哪种类型的数字器件特点为中到高的速度、低成本和良好的驱动能力。

()T T L 66.74L S 00中的L S 指什么?3.21.使用C M O S 门时,多余的输入端不能( )。

悬空2.如果C M O S 反相器的电源电压是V DD ,则反相器的门槛电压为( )。

2/V D D3.已知C M O S 与非门C D 4011的部分静态参数为:V V IH MIN 4=,V V V V V O L MAX O H MIN ILMAX 05.0,95.4,1===,试求该与门的噪声容限。

解答:根据噪声容限的定义,易得出输入高电平噪声容限,95.0495.4=-=-=V VV IH MIN O H MIN NH 输入低电平噪声容限V V V V V V O LMAX ILMAX NL 95.005.01=-=-=。

4.C M O S反相器的关门电平提高时,将使其低电平的噪声容限()。

提高5.C M O S器件的主要优点是()。

静态功耗极小6.C M O S传输门不但可以传送数字信号,还可以传送()信号。

连续变化的模拟信号7.一般C M O S门的输出端()直接相连,实现线与。

不能8.C M O S器件中应用了()类型的晶体管。

单极性9.驱动门和负载门之间总是要用到专门的接口电路。

(×)10.当输出为低(V OL)时,逻辑门()电流。

灌入11.若扇出(低或高)过载,则逻辑门无法正常工作。

(√)12.哪种类型的数字器件具有高集成度和低功耗的特点。

C M O S13.肖特基T T L器件可比标准T T L器件工作于更高的时钟速度。

(√)14.某些C M O S集成电路和T T L兼容。

(√)15.标准的习惯电流方向总是指向门的输出或输入引脚。

(√)16.符号V IH表示(C)A.门的高电平输出电压B.门的低电平输出电压C.门的高电平输入电压D.门的低电平输入电压17.一个逻辑门输出能够可靠驱动的最大输入数称为(C)A.噪声免疫力B.噪声容限C.扇出D.扇入18.定义三态。

答案:集成电路输出端应用三态:逻辑0、逻辑1、高阻态19.定义总线争用。

答案:总线同时允许多个器件工作时引起的总线无效状态。

20.说明数字系统中总线收发器的用途。

允许在两个数据总线之间实现异步双向传输的器件。

3.31.T T L逻辑门的逻辑0的典型电压范围限制是(B)。

A.0~0.2VB.0~2VC.0~0.4VD.0~5V2.与M O S逻辑系列相比,T T L逻辑系列相比的主要优点之一是(A)。

A.高速B.高集成度C.低功耗D.高稳定性3.与T T L逻辑系列相比,M O S逻辑系列相比的主要优点之一是(B)。

A.高速B.高集成度C.低功耗D.高稳定性4.悬空输入(D)。

A.将使能逻辑门B.将禁止逻辑门C.使T T L逻辑门动作将其作为低电平输入来动作D.使T T L逻辑门动作将其作为高电平输入来动作5.或门上的未输入引脚可以通过一个上拉电阻固定在高电平上,以使能该逻辑门(×)。

6.与非门上的未输入引脚可以通过一个上拉电阻固定在高电平上,以使能该逻辑门(√)。

7.下面哪一种测试仪器最适合将逻辑脉冲注入到电路中(B)。

A.逻辑探针B.逻辑脉冲发生器C.扩展接线柱D.测试监视器接线柱8.下面哪一种测试仪器最适合用于检测电路中的逻辑电平、脉冲信号和失效的导线(A)。

A.逻辑探针B.逻辑脉冲发生器C.扩展接线柱D.测试监视器接线柱9.造成图 3.64所示电路故障的原因可能是(注意标出的逻辑电平,它们是从实际电路中测出的)(D)。

A.逻辑门1A的引脚2在内部被短路到地B.逻辑门1A的引脚2在内部被短路到V CCC.逻辑门1A的引脚1在内部被断开D.逻辑门2的引脚2在内部被断开10.造成图 3.64所示电路故障的原因可能是(注意标出的逻辑电平)(C)。

A.逻辑门1B的引脚4被短路到地B.逻辑门2的引脚3被短路到地C.逻辑门2的引脚3被短路到V CCD.逻辑门1A的引脚1处于悬空状态11.C M O S电路的静态功耗比T T L电路的静态功耗()。

小12.提高阈值的目的是()。

为了提高低电平噪声容限。

13.若将一个T T L 异或门(输入端为A 、B )当作反相器使用,则A 、B 端应(A )连接。

A.A 或B 中有一个接1B.A 或B 中有一个接0C.A 和B 并联使用D.不能实现14.已知某T T L 门电路的部分参数为:最高输出高电平V V OH 7.2min =,最大输出低电平V V OL 5.0max =,开门电平V V V IH ON 2min =)(,关门电平V V V IH OH 8.0)(max=,则其高电平噪声容限=V NH ()。

0.7V15.T T L 与非门为拉电流负载时,其输入为 电平。

低16.T T L 门电路采用推拉式输出结构,其主要优点是 。

有效地降低了输出级的静态功耗,并提高了驱动负载的能力。

17.对于T T L 与非门,下列说法属于逻辑“0”的是(A )。

A.输入端接0.8V 的电源B.输入端悬空C.输入端通过10K 电阻接地D.输入端接同类与非门输出高的电平18.某T T L 与非门的输入高低电平的额定值分别为3V 和0.3V ,已知高低电平的噪声容限为 1.2V 和0.8V 。