DDR2控制和FPGA实现

基于DDR2 SDRAM乒乓双缓冲的高速数据收发系统设计

基于DDR2 SDRAM乒乓双缓冲的高速数据收发系统设计刘杰;赛景波【摘要】在高速数据收发系统设计中,首先需要解决的问题是实时数据的高速缓存,然而FPGA内部有限的存储资源无法满足海量数据缓存的要求。

为了解决系统中海量数据的缓存问题,系统创新提出了一种基于DDR2 SDRAM的乒乓双缓冲设计方案。

方案设计了两路基于DDR2 SDRAM的大容量异步FIFO,通过FPGA内部选择逻辑实现两条通路间的乒乓操作,从而实现数据的高速缓存。

实验结果表明,基于DDR2 SDRAM的数据收发系统实现了每路512 Mbit的缓存空间和200 MHz的总线速率,解决了海量数据的高速缓存问题。

%In the high-speed data transceiver system design, the first problem to be solved is the real-time data cache,However,the limited memory resources of FPGA can not meet the requirements of massive data cache,To solve the problem of system cache huge amounts of data,the system proposed ping-pong double buffering innovative design based on the DDR2 SDRAM. Design of two-way high-capacity asynchronous FIFO based on DDR2 SDRAM, selection logic operations to achieve a ping-pong between the two paths through the FPGA to achieve the cached da-ta . Experimental results show that the Data transceiver system based on DDR2 SDRAM realized every road 512 Mbit cache space and 200 MHz of the bus rate and solved the problem of the huge amounts of data cache.【期刊名称】《电子器件》【年(卷),期】2015(000)003【总页数】5页(P650-654)【关键词】高速数据收发;乒乓双缓冲;DDR2 SDRAM技术;异步FIFO【作者】刘杰;赛景波【作者单位】北京工业大学电控学院,北京100022;北京工业大学电控学院,北京100022【正文语种】中文【中图分类】TN919.6高速数据传输是现代信号处理的基础,在雷达、通信、遥测遥感等技术应用领域得到了广泛的应用。

基于FPGA的视频转换系统设计

基于FPGA的视频转换系统设计任勇峰;王大伟;石永亮;于丽娜【摘要】为解决不同视频系统之间显示时序、色彩空间、帧频、分辨率等不一致的问题,设计了一种以FPGA为控制核心, DDR2 SDRAM为高速缓存的视频转换系统,该系统从图形工作站采集到DVI视频,先进入高速缓存模块,然后通过视频转换算法在FPGA内部完成RGB至YCbCr的色彩空间转换,最后控制硬件实现PAL视频输出,实现了由DVI视频向PAL视频的转换。

经长期测试证明:该系统稳定可靠,达到设计要求。

%In order to solve the display between different video systems in consistencies timing,color space,framerate,resolution,etc,a video conversion system was designed,which regards FPGA as the control core,DDR2 SDRAM for cache. the device system collected DVI video from workstation graphics,firstly enters the cache mod⁃ule,and then completes the color space conversion and frame rate conversion via video conversion algorithm within the FPGA,and finally controls hardware PAL video output,completed by the DVI video conversion to PAL video. The long-term test proves:the system is stable and reliable,and meet the design requirements.【期刊名称】《电子器件》【年(卷),期】2016(039)003【总页数】7页(P655-661)【关键词】视频转换;DVI;PAL;高速缓存;转换算法【作者】任勇峰;王大伟;石永亮;于丽娜【作者单位】中北大学仪器科学与动态测试教育部重点实验室;中北大学仪器科学与动态测试教育部重点实验室;中北大学仪器科学与动态测试教育部重点实验室;中北大学电子测试技术重点实验室,太原030051【正文语种】中文【中图分类】TP274.2随着多媒体信息技术的高速发展,视频技术多元化发展成为趋势,而同时也激化了视频系统之间互联的矛盾。

DDR存储控制器的设计与应用

DDR存储控制器的设计与应用随着科技的不断进步,数字电子设备在日常生活和工作中的应用越来越广泛。

其中,DDR存储控制器作为计算机存储系统的重要组成部分,对于整个系统的性能和稳定性具有举足轻重的作用。

本文将详细阐述DDR存储控制器的概念、设计步骤、技术方案以及实验结果,并探讨其未来的发展趋势。

DDR存储控制器,全称Double Data Rate SDRAM控制器,是一种用于管理计算机存储系统的芯片或模块。

其主要作用是控制数据的传输速率和带宽,协调内存与处理器之间的数据交换,从而确保数据的高速、稳定传输。

DDR存储控制器适用于各种计算机存储设备,如DDR SDRAM、DDR2 SDRAM、DDR3 SDRAM等。

DDR存储控制器的硬件设计主要包括以下步骤:(1)确定控制器的架构和组成元件,包括数据路径、控制逻辑、时钟发生器等。

(2)设计电路板,包括布局布线和元件放置等。

(3)编写硬件描述语言(HDL),如Verilog或VHDL,用于实现控制器的逻辑功能。

(4)仿真和验证硬件设计,确保其符合预期的功能和性能要求。

DDR存储控制器的软件设计主要包括以下步骤:(1)编写存储控制器的驱动程序,包括初始化和配置控制器、读写数据等操作。

(2)优化数据传输速率和带宽,以实现更高效的数据传输和控制。

(3)配合硬件设计,实现软硬件联合调试和测试。

在DDR存储控制器的设计中,我们采用了以下技术方案:采用同步动态随机存取存储器(SDRAM)作为主要的存储介质,其具有较高的存储密度和较低的功耗。

使用双倍数据速率(DDR)技术,使得SDRAM在每个时钟周期内可以进行两次数据传输,从而大幅提高了数据传输速率和带宽。

引入高速缓存接口(Cache Interface),以提高数据访问速度和降低CPU的负载。

使用可编程逻辑门阵列(FPGA)作为控制器的主要芯片,其具有灵活性和可定制性,能够满足各种不同的存储需求。

我们设计并实现了一款DDR存储控制器,并对其进行了严格的测试。

DDR2 控制器Altera FPGA 管脚分配步骤

DDR2 控制器Altera FPGA管脚分配步骤 骏龙科技技术支持部1.在megawizard中选择DDR2控制器。

2.设置memory相关参数,包括DDR2数据位宽,时钟速率,地址等。

3.设置controller相关参数,册。

5.设置board timing,这里的参数与PCB走线有关。

6.仿真模型设置,如果需要对生成的IP进行功能仿真,选上Generate Simulation Model。

7.生成DDR2控制器IP,在工程目录下可以查看到Altera 提供一个自测程序文件(_example_top.v),把_example_top.v设置为top level file。

8.在settings下的timequest timing analyzer处添加DDR2的时序约束文件SDC文件,如下图。

9.综合工程和管脚约束:综合完成后运行tcl scripts(在tools菜单下):选中_pin_assignments.tcl,然后点击RUN。

10.运行打开pin planner :assignments/pin planner11.分配dqs信号到想要的DQS管脚上,注意DQS group有X8/X9mode,X4/X5mode,X16/X18mode.12.指定DQ,ADDRESS和命令信号等到相应的IO bank,但DQ是跟随DQS的。

如图,只需把location指定到bank位置,不需指定到某个IO号。

13.位置指定完成后,全编译!14.全编译后查看是否有时序不满足,主要看信息栏,是否有报关键警告。

15.16.编译完成,时序也满足要求后运行:assignments/back-annotate assignments将之前指定到IObank的管脚反标到特定的IO管脚上。

再查看pin planner时,你将会发现上图变为下图所示:17.在assignments下选择Pin planner,倒出管脚文件,文件名后缀为*.csv.18.。

FPGA与DDR2SDRAM互联的信号完整性分析

Ke wo d : sg a itg i I p t tu Bufr no main p cf ain(BI ) mo e;hg —p e P itd y r s in l ne ry; n u/ p t t Ou f If r t S e i c t e o i o I S d l ih s e d r e Cic i n rut Bo r ad

联 。4 D 2 S AM共享地址线和控制 命令线 。数据线是 片 DR DR 点对点连接方 式 , 拓扑结构 简单。地址线和控制命令线的连接 存在一个拓扑结构 的选择问题。树形拓扑结构和菊花链式拓扑 结构 是两 种常见 的拓 扑结 构一 章从 仿真 的 角度 分析 上面 。文 两种不 同拓扑结 构下不同的端接方式对信 号完整性的影响 。

S DRAM. mp tr En i e rn n p ia in , 0 1 4 ( 9 : 5 — 6 . Co u e gn e i g a d Ap l to s 2 1 , 7 2 ) 1 8 1 0 c

Ab t a t Ths p p r d s r e h r be o in l ne r y b t e r x 5 n sr c : i a e e ci s t e p o lm f sg a itg i ewe n Vi e - a d DDR2 S b t t DRAM ne c n e t n I a ay e t i tro n ci . n lz s i o t s

o f PCB ouig. e e ul oft s o ott e a hie e nsr ts t a u h t e r s e e t i e d sg o i —p e ic i. r t Th rs t e t n pr oyp m c n d mo tae h ts c o y i f ci n h ve n t e in f hgh s e d cr ut h

基于FPGA+CPU的信号处理系统的设计与实现

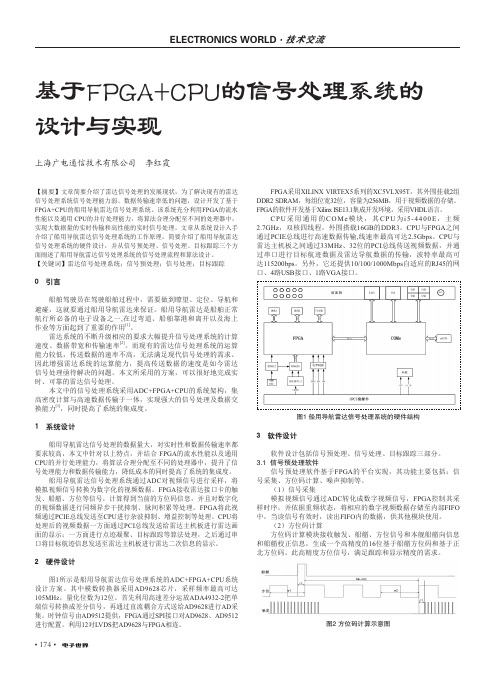

• 174•基于FPGA+CPU的信号处理系统的设计与实现上海广电通信技术有限公司 李红霞【摘要】文章简要介绍了雷达信号处理的发展现状,为了解决现有的雷达信号处理系统信号处理能力弱、数据传输速率低的问题,设计开发了基于FPGA+CPU 的船用导航雷达信号处理系统。

该系统充分利用FPGA 的流水性能以及通用 CPU 的并行处理能力,将算法合理分配至不同的处理器中,实现大数据量的实时传输和高性能的实时信号处理。

文章从系统设计入手介绍了船用导航雷达信号处理系统的工作原理,简要介绍了船用导航雷达信号处理系统的硬件设计,并从信号预处理、信号处理、目标跟踪三个方面阐述了船用导航雷达信号处理系统的信号处理流程和算法设计。

【关键词】雷达信号处理系统;信号预处理;信号处理;目标跟踪0 引言船舶驾驶员在驾驶船舶过程中,需要做到瞭望、定位、导航和避碰,这就要通过船用导航雷达来保证。

船用导航雷达是船舶正常航行所必备的电子设备之一,在过弯道、船舶靠港和离开以及海上作业等方面起到了重要的作用[1]。

雷达系统的不断升级相应的要求大幅提升信号处理系统的计算速度、数据带宽和传输速率[2]。

而现有的雷达信号处理系统的运算能力较低,传送数据的速率不高,无法满足现代信号处理的需求。

因此增强雷达系统的运算能力,提高传送数据的速度是如今雷达信号处理亟待解决的问题。

本文所采用的方案,可以很好地完成实时、可靠的雷达信号处理。

本文中的信号处理系统采用ADC+FPGA+CPU 的系统架构,集高密度计算与高速数据传输于一体,实现强大的信号处理及数据交换能力[1],同时提高了系统的集成度。

1 系统设计船用导航雷达信号处理的数据量大,对实时性和数据传输速率都要求较高,本文中针对以上特点,并结合 FPGA 的流水性能以及通用 CPU 的并行处理能力,将算法合理分配至不同的处理器中,提升了信号处理能力和数据传输能力,降低成本的同时提高了系统的集成度。

船用导航雷达信号处理系统通过ADC 对视频信号进行采样,将模拟视频信号转换为数字化的视频数据。

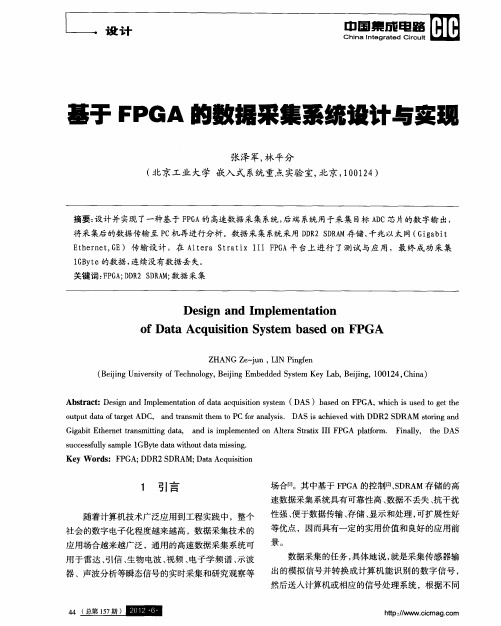

基于FPGA的数据采集系统设计与实现

了异步传输 中跨时钟域造成的亚稳态问题 [ 5 1 。在本 数据采集系统的设计中采用异步 FF IO的方式来解

图 2 数 据 采 集 系统 数 据 流 程

决跨时钟域 的数据传输 问题 。因为本数据采集系统 是针对 A C芯片的测试所用的, D 因此数据采集接 口 的数据率不是 固定 的 10 H x4i 而 D R 控制 5M z5b , D 2 t 器的用户接 口和 G E控制器接 口数据率是 固定的 , 分别为 10 H x 1b 和 15 z 2i 5 M zl2i t 2MH x b ,所 以选用 3 t 异步 FF IO可以使 系统更加灵活。

基于 F GA的数据采集系统设计与实现 P

张 泽 军 , 平 分 林

( 北京工业 大学 嵌入式 系统重点 实验 室, 北京, 1 4 102 ) 0

摘要 : 设计 并 实现 了一种基 于 FG P A的 高速 数据 采 集 系统 , 端 系统 用于采 集 目标 A C芯 片 的数 字输 出, 后 D 将 采集后 的数据传 输 至 P C机再 进行 分析 。数据 采 集 系统 采用 DR D A 储 、 兆 以太 网 ( ia i D 2SRM存 千 G gb t

数据传输及控制。同时 , 模块还负责 G I F E控制器、

图 1数 据 采 集 系统 框 图

D R D 2控制 器 的用户 总线及 外 部数 据采 集 接 口之间

h¨ n . h n nA 、 ,m a , , n / s A i, ;、 1 、

L一设 — 计

巾国集成电路

Chi na nt I eg r ed icu i at C r t

块 ,其 功 能 相 当 于 一 个 D MA ( i c M m r Dr t e oy e

DDR PCB设计

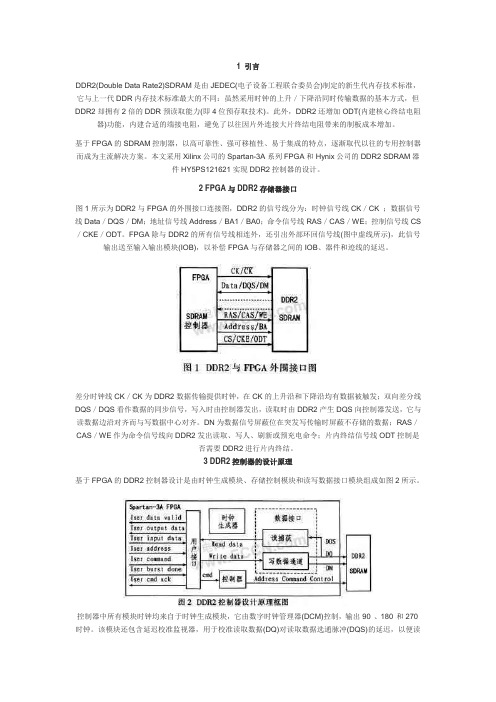

1 引言DDR2(Double Data Rate2)SDRAM是由JEDEC(电子设备工程联合委员会)制定的新生代内存技术标准,它与上一代DDR内存技术标准最大的不同:虽然采用时钟的上升/下降沿同时传输数据的基本方式,但DDR2却拥有2倍的DDR预读取能力(即4位预存取技术)。

此外,DDR2还增加ODT(内建核心终结电阻器)功能,内建合适的端接电阻,避免了以往因片外连接大片终结电阻带来的制板成本增加。

基于FPGA的SDRAM控制器,以高可靠性、强可移植性、易于集成的特点,逐渐取代以往的专用控制器而成为主流解决方案。

本文采用Xilinx公司的Spartan-3A系列FPGA和Hynix公司的DDR2 SDRAM器件HY5PS121621实现DDR2控制器的设计。

2 FPGA与DDR2存储器接口图1所示为DDR2与FPGA的外围接口连接图,DDR2的信号线分为:时钟信号线CK/CK ;数据信号线Data/DQS/DM;地址信号线Address/BA1/BA0;命令信号线RAS/CAS/WE;控制信号线CS /CKE/ODT。

FPGA除与DDR2的所有信号线相连外,还引出外部环回信号线(图中虚线所示),此信号输出送至输入输出模块(IOB),以补偿FPGA与存储器之间的IOB、器件和迹线的延迟。

差分时钟线CK/CK为DDR2数据传输提供时钟,在CK的上升沿和下降沿均有数据被触发;双向差分线DQS/DQS看作数据的同步信号,写入时由控制器发出,读取时由DDR2产生DQS向控制器发送,它与读数据边沿对齐而与写数据中心对齐。

DN为数据信号屏蔽位在突发写传输时屏蔽不存储的数据;RAS/CAS/WE作为命令信号线向DDR2发出读取、写人、刷新或预充电命令;片内终结信号线ODT控制是否需要DDR2进行片内终结。

3 DDR2控制器的设计原理基于FPGA的DDR2控制器设计是由时钟生成模块、存储控制模块和读写数据接口模块组成如图2所示。