1、原理图设计及符号图生成

原理图设计基础

第三章 电路原理图设计

3.1 装载元件库 措施一 使用元件库浏览器 措施二 使用Design→Add/Remove Library 命令

装载元件库旳环节如下:

⑴打开设计管理器,选择Browse Sch选项卡,在下拉列表中选择 Libaries,单击Add/Remove按钮添 加元件库,屏幕出现图2-6所示旳 添加/删除元件库对话框。

• 设置画图环境(使用TOOL/PREFERENCE和 DESIGN/OPTIONS命令)

2)装载元件库(例如杂元件库 MISCELLANEOUS DEVICE .DDB );

3)放置元器件并布局; 4)布线; 5)加网络标签; 6)放置电源和地线; 7)编辑元件属性(封装、流水号、元件类型等); 8)电气规则检验(ERC); 9)生成元件列表(BOM文件); 10)生成网络表(Design / Create Netlist); 11)存盘及打印输出。

2.经过菜单或工具按钮放置元件

执行菜单Place→Part,或单击绘 制原理图工具上旳 按钮,屏幕弹 出图2-10所示旳放置元件对话框,其 中Lib Ref是元件旳库参照名称.如 CAP,单击Browse按钮能够进行元件 浏览;Designator框中输入元件标号, 如C1;Part Type栏中输入标称值或元 件型号,如103;Footprint框用于设 置元件旳封装形式,如RAD0.2。全 部内容输入完毕,单击OK按钮确认, 此时元件便出目前光标处,单击左键 放置。

元件库 添加旳元件库

图2-6 添加/删除元件库

3.2 放置元件

1.经过元件库浏览器放置元件

装入元件库后,在元件库浏览器中能 够看到元件库、元件列表及元件外观,如 图2-7所示。选中所需元件库,则该元件库 中旳元件将出目前元件列表中,双击元件 名称(如CAP)或单击元件名称后按Place 按钮.

altium designer 10 基本操作

一、Altium Designer 10 简介Altium Designer 10 是一款专业的电子设计自动化软件,提供了丰富的功能和工具来帮助工程师进行电路设计与布局。

它包含了原理图设计、PCB设计、仿真、布线等多种功能模块,能够全面满足电子设计的需求。

二、Altium Designer 10 软件界面介绍1. 主界面:Altium Designer 10 的主界面分为菜单栏、工具栏、项目导航栏、设计区域等部分,通过这些界面的组织,用户可以方便地进行各种操作。

2. 菜单栏:Altium Designer 10 的菜单栏包含了各种功能和命令,用户可以通过菜单栏来进行软件的设置、操作和管理。

3. 工具栏:工具栏中包含了常用的工具和快捷按钮,用户可以通过工具栏来快速访问各种功能。

4. 项目导航栏:项目导航栏用于管理当前项目的各种文件和资源,在设计过程中起到了重要的作用。

5. 设计区域:设计区域是用户进行原理图设计、PCB布局等操作的主要区域,用户可以在设计区域中进行各种设计操作。

三、Altium Designer 10 基本操作1. 创建新项目:在 Altium Designer 10 中,用户可以通过菜单栏的“File”选项来创建新项目,选择“New Project”来新建一个项目,并按照提示逐步完成项目的建立。

2. 原理图设计:在新建的项目中,可以选择“Schematic”来进行原理图设计,通过绘制原理图符号、连接器件、建立电路连接等操作,完成原理图的设计。

3. PCB布局:完成原理图设计后,可以转到PCB布局,通过布置元件、走线、铺铜等操作来完成PCB的设计,保证电路连接安全可靠。

4. 设备连接:在 Altium Designer 10 中,用户可以通过USB线连接设备,在进行原理图设计和布局时,可以实时查看到设备的状态,方便调试和验证电路设计的准确性。

5. 仿真与验证:Altium Designer 10 中还提供了丰富的仿真和验证工具,用户可以对设计的电路进行仿真分析,验证设计的准确性和稳定性。

Altium 09简答题答案

三.简答题(每题10分)1.在Altium Designer系统中,绘制电路原理图主要分为几个步步骤:1.新建项目文件1)执行“文件-新建-项目-PCB 工程”,在Project中将出现项目文件。

2)执行“文件-保存工程”,确定保存路径和输入项目文件名保存。

2.新建原理图文件执行“文件-新建-原理图”,在Project项目文件下新建一个原理图保存3.原理图图纸设置执行“设计-文档选项”,弹出“文档选项”。

图纸类型设置为A4,显示标准标题栏,可视/捕捉栅格均设置为10,电气栅格设置为4。

4.装载原理图元件库在Libraries工作面板上单击【库…】。

单击选项下方【添加库】按钮,选择添加Miscellaneous Devices.IntLib,单击打开添加库完成。

5.放置调整元件1)在Miscellaneous Devices.IntLib中,在元件库中查找电阻。

2)按Tab键,设置元件属性3)然后依次查找并放置无极性电容、电解电容、开关、晶振等。

6.查找元件在“库面板”出现搜索库对话框。

点“搜索”库元件,搜到后放置7.绘制电路1)绘制导线、网络、总线等,完成电路的绘制。

2)给原理图器件编号,“工具-注解或静态注释”8.编译:“工程-**.SchDoc”,如果编译有错,会跳出【Message】窗口,根据提示信息改错。

直到编译通过。

9.保存。

2.联合、片段、设备片有什么区别1.联合用户把常用的一些电源电路、接口电路组成的设计电路创建为“联合”,然后保存为“片段”,以备日后设计复用或者与其他用户共享。

可以多次调用,提高绘图效率。

2.片段片段与联合的生成过程基本相同。

但片段可以长久保存,而且能够使用系统提供的【片段】面板进行查看、管理。

3.设备片设备片是altium designer系统在原理图编辑环境中所提供的又一种独特的设计复用方式,可以把不同设计中需要重复使用的电路图抽象为一个模块(设备片),之后借助于器件图表符,直接放置在原理图中使用即可。

电气CAD绘的基本原理与方法

电气CAD绘的基本原理与方法电气CAD(计算机辅助设计)绘图是电气工程领域的重要工具,它能够帮助工程师快速高效地完成电路设计、布线等任务。

本文将介绍电气CAD绘图的基本原理与方法,以帮助读者更好地理解和应用该技术。

一、电气CAD的基本原理电气CAD的基本原理是利用计算机系统来辅助进行电气绘图和设计。

通过软件工具,工程师可以在计算机上创建电气图形,并进行编辑、组织、修改等操作,最终生成电气图纸。

电气CAD的基本原理可以概括为以下几点:1. 数据建模:电气CAD软件通过建立电路元件的数据模型,将电路元件的属性以数据的形式保存在计算机中,并能与其他元件进行连接和组织,形成电路图。

2. 图形界面:电气CAD软件提供直观的图形界面,通过绘图工具、画线、添加符号等操作,可以在界面上绘制出电气元件和线路连接关系,用于构建电路图。

3. 原理图符号:电气CAD软件提供了大量的电气元件符号库,工程师可以根据需要选择合适的符号进行绘图,符号库的使用方便了电路图的绘制和阅读。

4. 连接关系:电气CAD软件能够根据工程师的操作,自动识别和绘制电路元件之间的连接关系,并在图纸上显示出电路的连线和连接点,简化了电路的布线过程。

二、电气CAD的基本方法在进行电气CAD绘图时,需要掌握一些基本方法和技巧,以提高绘图的准确性和效率。

以下是几个关键的方法和技巧:1. 选择合适的软件:根据自身需求选择合适的电气CAD软件,比如AutoCAD Electrical、EPLAN等,不同软件有不同的特点和功能,选择适合自己使用的软件能提高绘图效率。

2. 学习符号库:掌握符号库的使用方法,了解各种电气元件的符号表示和含义,能够正确地选择和应用符号,保证电路图的准确性。

3. 使用图层:电气CAD软件通常支持多层绘图,可以将不同的电气元件或不同的功能分别绘制在不同的图层上,方便后续的编辑和修改。

4. 定义属性:在绘制电路图时,可以为电气元件添加属性,比如元件的名称、型号、规格等信息,这样可以方便后续的标注和查找。

电路原理图设计

电路原理图设计The document was prepared on January 2, 2021电路原理图设计原理图设计是电路设计的基础,只有在设计好原理图的基础上才可以进行印刷电路板的设计和电路仿真等.本章详细介绍了如何设计电路原理图、编辑修改原理图.通过本章的学习,掌握原理图设计的过程和技巧.电路原理图设计流程原理图的设计流程如图 3-1 所示 . .图 3-1 原理图设计流程原理图具体设计步骤:1 新建原理图文件.在进人 SCH 设计系统之前,首先要构思好原理图,即必须知道所设计的项目需要哪些电路来完成,然后用 Protel DXP 来画出电路原理图.2 设置工作环境.根据实际电路的复杂程度来设置图纸的大小.在电路设计的整个过程中,图纸的大小都可以不断地调整,设置合适的图纸大小是完成原理图设计的第一步.3 放置元件.从元件库中选取元件,布置到图纸的合适位置,并对元件的名称、封装进行定义和设定,根据元件之间的走线等联系对元件在工作平面上的位置进行调整和修改使得原理图美观而且易懂.4 原理图的布线.根据实际电路的需要,利用 SCH 提供的各种工具、指令进行布线,将工作平面上的器件用具有电气意义的导线、符号连接起来,构成一幅完整的电路原理图.5 建立网络表.完成上面的步骤以后,可以看到一张完整的电路原理图了,但是要完成电路板的设计,就需要生成一个网络表文件.网络表是电路板和电路原理图之间的重要纽带.6 原理图的电气检查.当完成原理图布线后,需要设置项目选项来编译当前项目,利用 Protel DXP 提供的错误检查报告修改原理图.7 编译和调整.如果原理图已通过电气检查,那么原理图的设计就完成了.这是对于一般电路设计而言,尤其是较大的项目,通常需要对电路的多次修改才能够通过电气检查.8 存盘和报表输出: Protel DXP 提供了利用各种报表工具生成的报表如网络表、元件清单等,同时可以对设计好的原理图和各种报表进行存盘和输出打印,为印刷板电路的设计做好准备 .原理图的设计方法和步骤为了更直观地说明电路原理图的设计方法和步骤,下面就以图 3 - 2 所示的简单 555 定时器电路图为例,介绍电路原理图的设计方法和步骤.图 3-2 555 电路原理图3.2.1 创建一个新项目电路设计主要包括原理图设计和 PCB 设计.首先创建一个新项目,然后在项目中添加原理图文件和 PCB 文件,创建一个新项目方法:●单击设计管理窗口底部的 File 按钮,弹出如图 3 — 3 所示面板.● New 子面板中单击 Blank Proect PCB 选项,将弹出 Projects 工作面板.建立了一个新的项目后,执行菜单命令 File/Save Project As ,将新项目重命名为“ myProject1 . PriPCB ”,保存该项目到合适位置,如图 3-4 .图 3 — 3 Files 面板图 3 — 4 保存项目对话框3.2.2 创建一张新的原理图图纸执行菜单命令 New / Schematic 创建一张新的原理图文件.可以看到 Sheetl . SchDoc 的原理图文件,同时原理图文件夹自动添加到项目中.执行菜单命令 File/Save As ,将新原理图文件保存在用户指定的位置.同时可以改变原理图文件名为 555 . SchDoc .此时看到一张空白电路图纸,打开原理图图纸设置对话框.对于本例而言 , 没有特殊要求,只需要设置成 A4 图纸就可以了.单击原理图设置对话框的 OK 按钮页面设置完成.原理图工作环境采用默认设置即可.3.2.3 查找元件Protel DXP 库提供了大量元件的原理图符号,在绘制一副原理图之前,必须知道每个元件对应的库.对于 555 电路原理图的每个元件应该在哪个库呢可以采用什么办法找到元件的原理图符号呢利用 Protel DXP 提供的搜索功能来完成查找元件,操作步骤如下:1 SCH 设计界面的下方有一排按钮,单击 Libraries 库按钮,弹出如图 3 —5 所示的库对话框.2 单击图3 - 5 对话框中的 Search 按钮,弹出如图 3 — 6 所示的库搜索对话框,利用此对话框可以找到元件 555 在哪个库中.3 在 Scope 选项区域中确认设置为 Libraries on Path ,单击 Path 右边的打开图标按钮,找到安装的 Protel DXP 库的文件夹路径,如 C :\ Program Files \ Altium \ Library .同时确认 Include subdirectories 复选项被选定.4 在 Seach Criteria 搜索标准选项区域中可以使用 Name 、Description 、 MdelType 、 Model Name 组合来说明要搜索的元件,例如要搜索和 555 元件相关的可以在 Name 文本框中键入 555 .图 3 — 5 库对话框图 3 — 6 库搜索对话框5 单击 Search 按钮开始搜索,查找结果会显示在 Result 对话框中,如图 3— 7 所示.图 3 — 7 搜索结果对话框可以看到很多匹配搜索标准的芯片型号,选择一款适合的元件原理图符号和封装.这里选择元件 NE555P ,属于 TI Analog Timer Circuit . IntLib 库.能否找到所需要的元件关键在于输入的规则设置是否正确,一般尽量使用通配符以扩大搜索范围.6 单击 Install Library 按钮, TI Analog Timer Crcuit . IntLib 库就添加到当前项目中.在当前项目中就可以取用该库中的所有元件.在完成了对一个元件的查找后,可以按照 555 电路原理图的要求,依次找到其他元件所属元件库,见表 3 — 1 所示.表 3 - 1 555 原理图的元件列表元件名称元件库元件符号元件属性NE555PTI Analog Timer U1NE555PCAP MiscellaneousC11uCAP MiscellaneousC2RES MiscellaneousR127kRESMiscellaneousRL10k.ICSimulation Sources. IntLibIC10vVPULSESimulation Sources. IntLibV1VPULSE注:在 Protel DXP 中,电阻元件单位默认以 k 代表 k ,电容元件单位默认以u 代替 uF .△3.2.4 添加或删除元件库已经介绍了当不知道元件在哪个库中,如何查找并把元件库添加到项目中的问题,当知道元件所属的库时,可以直接添加库到设计项目中,添加元件库的步骤如下:1 在如图 3 — 6 所示对话框中单击 Libraries 按钮,弹出如图 3 — 8 所示对话框,其中 Ordered List of Installed Libraries 列表框中主要说明当前项目中安装了哪些元件库.2 添加元件库.单击 Add Library 按钮,将弹出查找文件夹对话框,选择安装Protel DXP 元件库的路径.然后根据项目需要决定安装哪些库就可以了.例如本例中安装了 Miscellaneous 、 TI Analog Timer 等.在当前元件库列表中选中一个库文件,单击 MOVE UP 按钮可以使该库在列表中的位置上以一位, MOVE DOWN 相反.元件库在列表中的位置影响了元件的搜索速度,通常是将常用元件库放在较高位置,以便对其先进行搜索.图 3 — 8 添加、删除元件库3 删除元件库.当添加了不需要的元件库时,可以选中不需要的库,然后单击Remove 按钮就可以删除不需要的库.3.2.5 在原理图中放置元件在当前项目中添加了元件库后,就要在原理图中放置元件,下面以放置 NE555P 为例,说明放置元件的步骤如下:1 执行菜单命令 View / Fit Document ,或者在图纸上右击鼠标,在弹出的快捷菜单中选择 Fit Document 选项,使原理图图纸显示在整个窗口中.可以按Page Down 和 Page Up 键缩小和放大图纸视图.或者右击鼠标,在弹出的快捷菜单中选择 Zom in 和 Zom out 选项同样可以缩小和放大图纸视图.2 在元件库列表下拉菜单中选择 TI Analog Timer 使之成为当前库,同时库中的元件列表显示在库的下方,找到元件 NE555P .3 使用过滤器快速定位需要的元件,默认通配符列出当前库中的所有元件,也可以在过滤器栏键人 NE555P , NE555P 显示出来避免了在当前库很多元件中查找的困难.4 选中 NE555P 选项,单击 Place NE555P 按钮或双击元件名,光标变成十字形,光标上悬浮着一个 555 芯片的轮廓,按下 Tab 键,将弹出 Component Properties 元件属性对话框进行元件的属性编辑,如图 3 - 9 所示.在Designator 框中键人 U1 作为元件符号.可以看到元件的 PCB 封装为右下方的Footprint 一栏设置 Dip - 8 / D 1l .图 3 — 9 元件属性对话框5 在当前窗口移动光标到原理图中放置元件的合适位置,单击鼠标把 NE555P放置在原理图上.按 PageDown 和 PageUp 键缩小和放大元件便于观看元件放置的位置是否合适,按空格键使元件旋转,每按一下旋转 9 0 °来调整元件放置的合适位置方向.6 放置完元件后,右击鼠标或者按 ESC 键退出元件放置状态,光标恢复为标准箭头.下面放置两个电阻、两个电容、脉冲电压源 VPULSE 和静态电压源 IC ,其步骤如下:1 电阻元件在 Miscellaneous 中,在库对话框选中作为当前库.2 在库对话框的过滤器一栏中键人 Res ,将在元件列表中显示相关元件.选中Res1 元件,然后单击 Place 按钮,此时电阻悬浮在光标上,按 Tab 键,在打开的“元件属性”对话框中设置元件符号和元件属性的值,在 Designator 文本框中键人 R1 ,单击 OK 按钮完成电阻 R1 的属性设置.3 移动光标到电路图中合适位置,单击鼠标完成电阻 R1 的放置.4 同时移动光标到另一位置,单击鼠标放置元件 R2 ,系统自动增加元件序号.5 在过滤器栏中键人 Cap ,放置电容 C1 、 C2 的方法与放置电阻的方法相同.6 在库对话框中选中 Simulation 作为当前库,在过滤栏中键人 Vpulse ,在元件列表中显示脉冲电压源符号,单击 Place 按钮使元件处于选取状态,打开元件属性对话框,在 Designator 中键人 V1 即可.7 在过滤栏中键人 . IC ,元件列表中显示静态电压源符号,与脉冲电压源选取相似.8 已经放置完所有的元件,单击右键退出元件放置模式,此时图纸上已经有了全部的元件,如图 3 — 10 所示.图 3 — 10 元件选取完成后的图纸3.2.6 设置元件属性双击相应的元件打开 Component Properties 对话框, Component Properties 对话框图 3 — 9 的设置:1 . Properties 元件属性选项区域设置元件属性设置主要包括元件标识和命令栏的设置等,分别介绍如下:● Designator 元件标识的设置:在 Designator 文本框中键入元件标识,如 U1 、 R1 等. Designator 文本框右边的 Visible 复选项是设置元件标识在原理图上是否可见,如果选定 Visible 复选项,则元件标识 U1 出现在原理图上,如果不选中,则元件序号被隐藏.● Comment 命令栏的设置:单击命令栏下拉按钮,弹出图 3 — 11 所示对话框,其中 Class 指元件类别,可以看出 NE555P 属于模拟器件; Manufacturer 是指制作厂商; Pushlished 是指元件出厂时间; Pushished 是指销售厂商;Subclass 是指子类,例如 NE555P 是模拟器件中的定时器这种子类元件. Comment 命令栏右边的 Visible 复选项是设置 Comment 的命令在图纸上是否可见,如果选中 Visible 选项,则 Comment 的内容会出现在原理图图纸上.在元件属性对话框的右边可以看到与 Comment 命令栏的对应关系,如图 3 — 12 所示. Add 、 Remove 、Edit 、 Add as Rule 按钮是实现对 Comment 参数的编译,在一般情况下,没有必要对元件属性进行编译.图 3 — 11 Comment 的下拉菜单图 3 — 12 Comment 参数设置● Library Ref 元件样本设置:根据放置元件的名称系统自动提供,不允许更改.例如 NE555P 在元件库的样本名为 NE555P .● Library 元件库设置:例如 NE555P 在 TI Analog TimerCircuit . IntLib 库中.● Description 元件描述、 Unique id Id 符号、 Subdesign 设置:一般采用默认设置,不作任何修改.2 . Graphical 元件图形属性选项区域设置Graphical 选项主要包括元件在原理图中位置、方向等属性设置,分别介绍如下:● Location 元件定位设置:主要设置元件在原理图中的坐标位置,一般不需要设置,通过移动鼠标找到合适的位置即可.● Orientation 元件方向设置:主要设置元件的翻转,改变元件的方向.● Mirrored 镜像设置:选中 Mirrored ,元件翻转 l80 °.● Show Hidden Pin 显示隐藏引脚: NE555P 不存在隐藏的引脚,但是 TTL 器件一般隐藏了元件的电源和地的引脚.例如非门 74LS04 等门电路的原理图符号就省略了电源和接地引脚.一般情况下,对元件属性设置只需要设置元件标识和 Comment 参数即可,其他采用默认设置.3.2.7 放置电源和接地符号555 电路图有一个 12V 电源和一个接地符号,下面以接地符号为例,说明放置电源和接地符号的基本操作步骤.放置接地符号的基本操作步骤:1 执行菜单命令 View/Toolbars / Power objects ,将弹出如图 3 — 13 所示的 Power Object 电源符号图标对话框.2 在图3 一 13 中有几种接地符号,根据需要选择,这里选择如图 3 一 14 所示的接地符号.图 3 — 13 电源符号图标图 3 — 14 接地符号3 选中接地符号,出现十字光标,同时光标上悬浮着接地符号的轮廓,此时按Tab 键,出现 PowerPort 接地符号属性对话框,如图 3 一 15 所示,这里需要注意网络名称是否正确.单击 OK 按钮完成网络名称设置.3 — 15 接地符号属性对话框4 移动光标到图纸上合适的位置单击鼠标,接地符号就显示在图纸上. 12V 电源放置与接地放置基本相同.3.2.8 绘制原理图1 .绘制导线元件放置在工作面板上并调整好各个元件的位置后,接下来的工作是对原理图进行布线.对原理图布线的步骤如下:1 为了使原理图图纸有很好的视图效果,可以使用以下三种方法,执行菜单命令View / Fit All Objects ;第二种在原理图图纸上右击鼠标,在弹出的菜单中选择 Fit All Objects 选项;第三种是使用热键 V , F .2 执行主菜单命令 Place / Wire ,进人绘制导线状态,并绘制原理图上的所有导线.以连接 R1 与 NE555P 第七脚之间的连线为例,把十字形光标放在 R1 的引脚上,把光标移动到合适的位置时,一个红色的星形连接标志出现在光标处,这表明光标在元件的一个电气连接点上.3 单击鼠标固定第一个导线点,移动鼠标会看到一根导线从固定点处沿鼠标的方向移动.如果需要转折,在转折处单击鼠标确定导线的位置,每转折一次都需要单击鼠标一次.4 移动鼠标到 NE555P 第七脚,中间有一个转折点,单击鼠标,当移动到 NE555P 第七脚时,光标又变成红色的星形连接标志,单击鼠标完成了 R1 与 NE555P 第七脚之间的连接.5 时光标仍然是十字形,表明仍是处于画线模式,可以继续画完所有的连接线.6 连接完所有的连线后,右击鼠标退出画线模式,光标恢复为箭头形状.2 . Net and Net Label 网络与网络名称彼此连接在一起的一组元件引脚称为网络 net .例如 555 电路图中的 NE555P 的第七脚、第六脚、 R1 、 C1 是连在一起的称为一个网络.网络名称实际上是一个电气连接点,具有相同网络名称的电气连接表明是连在一起的.网络名称主要用于层次原理图电路和多重式电路中的各个模块之间的连接.也就是说定义网络名称的用途是将两个和两个以上没有相互连接的网络,命名相同的网络名称,使它们在电气含义上属于同一网络.在印刷电路板布线时非常重要.在连接线路比较远或线路走线复杂时,使用网络名称代替实际走线使电路图简化.在 555 电路图中,由于走线比较简单,所以没有必要图 3 — 16 网络名称属性对话框放置网络名称.全部使用导线实现了线路的连接,但是可以看到 NE555P 的第六脚和第七脚的连线就比较远,使用网络名称的方法可以代替这段导线,下面以此为例介绍如何放置网络名称:按照第 2 章介绍的方法放置网络名称并打开 Net Label 网络名称属性对话框,如图 3 — 16 所示.这里仅在 Properties 选项区域的 Net 文本框中键人 NE555P _ 6 ,其他采用默认设置即可.移动光标到 NE555P 的第六脚,单击鼠标完成第一个网络名称设置.移动光标到 R1 和 C1 与 NE555P 的第 7 脚连接点处,按 Tab 键定义网络名称为NE555P_ 6 .完成了利用网络名称代替一段导线,使视图更加美观.现在一副完整的 555 电路原理图已经完成了,执行菜单命令 File/Save 保存文件.设置项目选项项目选项包括错误检查规则、连接矩阵、比较设置、 ECO 启动、输出路径和网络选项以及用户指定的任何项目规则.当项目被编译时,详尽的设计和电气规则将应用于设计验证.例如一个 PCB 文件,项目比较器允许用户找出源文件和目标文件之间的差别,并在相互之间进行更新.所有与项目相关的操作,如错误检查、比较文件和 ECO 启动均在 Options For Project 对话框中设置.所有的项目输出,如网络名称、仿真器、文件打印、集合和输出报表均在Outputs For Projects 对话框中设置.执行菜单命令 Project / Project Options ,打开 OPtions for Proect 规则检查设置对话框,如图 3 — 17 所示.接下来,对规则检查设置对话框中各个选项卡进行相应的介绍:◆ Error Reporting 错误报告选项卡Error Reporting 用于报告原理图设计的错误,主要涉及下面几个方面:Violations Associated with Buses 总线错误检查报告、 Violations Associated with Components 元件错误检查报告、 Violations Asociated with Documents 文件错误检查报告、 Violations Associated with WithNets 网络错误检查报告、 Violations Associated with Others 其他错误检查报告、 Violations Associated with Prarmeters 参数错误检查报告.对每一种错误都设置相应的报告类型,例如选中 Bus indices out of range ,单击其后的 Fatal Error 按钮,会弹出错误报告类型的下拉列表.一般采用默认设置不需要对错误报告类型进行修改.图 3 — 17 规则检查设置对话框◆ Connection Matrix 连接矩阵选项卡在规则检查设置对话框中单击 Connection Matrix 标签,将弹出 Connection Matrix 选项卡,如图 3 — 18 所示.图 3 — 18 Connection Matrix 选项卡连接矩阵标签显示的是错误类型的严格性.这将在设计中运行“错误报告”检查电气连接如引脚间的连接、元件和图纸的输人.连接矩阵给出了原理图中不同类型的连接点以及是否被允许的图表描述.●如果横坐标和纵坐标交叉点为红色,则当横坐标代表的引脚和纵坐标代表的引脚相连接时,将出现 Fatal Error 信息.●如果横坐标和纵坐标交叉点为橙色,则当横坐标代表的引脚和纵坐标代表的引脚相连接时,将出现 Error 信息.●如果横坐标和纵坐标交叉点为黄色,则当横坐标代表的引脚和纵坐标代表的引脚相连接时,将出现 Warning 信息.●如果横坐标和纵坐标交叉点为绿色,则当横坐标代表的引脚和纵坐标代表的引脚相连接时,将不出现错误或警告信息.例如在矩阵图的横向找到 Output Pin ,从列向找到 Open Collector Pin ,在相交处是绿色的方块.当项目被编译时,这个绿色方块表示在原理图中从一个Output Pin 连接到 Open Collector Pin 时将启动一个错误条件.如果想修改连接矩阵的错误检查报告类型,比如想改变 Passive Pins 电阻、电容和连接器和 Unconnected 的错误检查,可以采取下述步骤:1 在纵坐标找到 Passive Pins ,在横坐标找到 Unconnected ,系统默认为绿色,表示当项目被编译时,在原理图上发现未连接的 Passive Pins 不会显示错误信息.2 单击相交处的方块,直到变成黄色,这样当编译项目时和发现未连接的Passive Pins 时就给出警告信息.3 单击 Set To Defaults 按钮,可以恢复到系统默认设置.◆ Comparator 比较器选项卡在规则检查设置对话框中单击 Comparator 标签,将弹出 Comparator 选项卡如图 3 - 19 所示.图 3 - 19 Comparator 选项卡Comparator 选项卡用于设置当一个项目被编译时给出文件之间的不同和忽略彼此的不同.在一般电路设计中不需要将一些表示原理图设计等级的特性之间的不同显示出来,所以在 Difference Associated With Compnents 单元找到Changed Room Definitions 、 Extra Room Definitions 和 Extra Components Classes ,在这些选项右边的 Mode 下拉列表选择 Ignore Differences .这样原理图设计等级特性之间的不同就被忽略.对不同的项目可能设置会有所不同,但是一般采用默认设置.单击 Set To Default 一按钮,可以恢复到系统默认设置.◆ ECO Generation 电气更改命令选项卡在规则检查设置对话框中单击 ECO Generation 标签,将弹出 ECO Generation 选项卡,如图 3 — 20 所示.图 3 — 20 ECO Gerleraion 选项卡通过在比较器中找到原理图的不同,当执行电气更改命令后, ECO Generation 显示更改类型详细说明.主要用于原理图的更新时显示更新的内容与以前文件的不同.ECO Engineering Change Order Generation 主要设置与元件、网络和参数相关的改变,对于每种变换都可以通过 Mode 列表框的下拉列表中选择Generate Change Orders 检查电气更改命令还是 Ignore Differences 忽略不同.单击 Set To Defaults 按钮,可以恢复到系统默认设置.Options 选项选项卡在规则检查设置对话框中单击 Options 标签,将弹出 Options 选项卡,图 3 -21 所示.● Output path 输出路径区域:可以设置各种报表的输出路径.默认的路径是系统在当前项目文档所在文件夹内创建.对于文件路径的选择主要考虑用户是希望设置单独的文件夹保存所有的设计项目,还是为每个项目中设置一个文件夹.图 3 — 21 Options 选项卡● Output Options 区域:有四个复选项设置输出文件. Open outputs after compile 编译后输出文件、 Timestamp folder 时间信息文件夹、 Archive project docu-ment 存档项目文件、 Use separate folder for each output type 对每个输出类型使用独立的文件夹.● Netlist Options 区域:有两个复选项分别为 Allow ports to Name Nets 和 Allow Sheet Entries to Name Nets . Allow ports to Name Nets 表示允许用系统所产生的网络名来代替与输人输出端口相关联的网络名.如果所设计的项目只是简单的原理图文档,不包含层次关系,可以选择此项. Allow Sheet Entries to Name Nets 表示允许用系统所产生的网络名来代替与子图入口相关联的网络名.该项为系统默认设置选项. 编译项目编译项目就是在设计文档中检查原理图的电气规则错误.执行菜单命令 Project / Compile PCB Project ,系统开始编译 Myproject1. PrjPCB .当项目被编译时,在项目选项中设置的错误检查都会被启动,同时弹出 Message 窗口显示错误信息.如果原理图绘制正确,将不会弹出 Message 窗口.下面以 Myprojectl . PrjPCB 的 555 原理图为例,删除 NE555P 的第四脚与电源连接的导线,并说明如何设置项目选项和编译项目,其步骤如下:1 如果正确绘制 555 原理图,执行菜单命令 Project/Compile PCB Project ,将不会弹出 Message 窗口.2 选中 NE555P 的第四脚与电源连接的导线,然后删除这段导线.3 然后再执行菜单命令 Project/Compile PCB Project ,将弹出错误检查报告,如图 3 — 22 所示.图 3 — 22 错误检查报告4 通过错误报告中叙述的错误类型可以修改在原理图的错误.在 Message 对话框中单击一个错误,打开 Compile Error 对话框,如图 3 - 23 所示.同时在Compile Error 对话框显示错误的详细信息.从 Compile Error 对话框中单击错误跳转到原理图的违反对象进行检查或修改.此时修改对象高亮显示,电路图上的其他元件和导线模糊.修改完成后,可以单击图纸有下方的 Clear 按钮,清除图纸的模糊状态.图 3 - 23 Compile Error 对话框5 修改完成后,重新编译项目,直至不再显示错误为止.保存项目文件,为 PCB 文件设计作好准备.小结本章围绕绘制一幅 555 原理图展开对电路设计流程的具体分析,尽管 555 原理图非常简单,但是读者不妨按照本节介绍的具体操作步骤,另找一份比较复杂的原理图试着绘制自己的第一张原理图,就能基本上领会原理图设计的基本方法和技巧.习题1 .了解 Protel DXP 集成库的概念.2 .通过在原理图库文件中查找元件如 ADC831 熟悉元件库管理器的打开方式以及如何搜索元件、添加删除元件等.3 .打开 Protel DXP 提供的例子如 Analog Amplifier . schdoc ,在同一张原理图图纸上的其他地方重新绘制 UA741 的简单放大电路.达到熟悉元件库的管理和熟练使用绘图工具栏的目的.4 .打开 Protel DXP 提供的例子如 Analog Amplifier . schdoc ,按照3 . 2 节介绍的具体操作方法实现对原理图中元件的选取、删除等操作.。

protel dxp 原理图以及PCB设计

在原理图中放置电源和接地符号,为电路提 供稳定的电源和接地。

原理图的检查与修改

检查原理图的完Leabharlann 性检查原理图是否完整,是否包含了所 有必要的元件和功能模块。

检查连接关系

检查元件之间的连接关系是否正确, 是否有遗漏或错误的连接。

检查电气规则

根据设定的电气规则,检查原理图中 的错误和潜在问题。

06

案例分析

案例一

总结词:简单实用

详细描述:小型电路板通常用于简单的电子设备,如遥控器、计算器等。在 Protel DXP 中,可以使用标准元件库和封装库进 行原理图和 PCB 设计。设计过程相对简单,主要考虑元件布局和布线规则。

案例二

总结词:高集成度

详细描述:复杂多层板通常用于高集成度的电子设备,如手机、平板电脑等。在 Protel DXP 中,需 要使用高级元件库和封装库进行原理图和 PCB 设计。设计过程需要考虑多层布线、信号完整性、电源 完整性等问题,以确保电路性能和可靠性。

高速电路设计规则检查

高速规则检查

Protel DXP 支持高速电路设计规则检查,确保电路板在高速 条件下具有良好的性能表现。通过规则检查,用户可以发现 潜在的信号完整性问题,并进行相应的优化。

信号完整性分析

Protel DXP 还提供信号完整性分析功能,通过仿真分析电路 板的信号质量,帮助用户预测和解决潜在的信号问题。

原理图设计流程

创建新项目

在Protel DXP中创建一个新的 项目,为原理图和PCB设计提 供一个统一的管理环境。

添加注释和说明

在原理图中添加必要的注释和 说明,以清晰地表达设计意图。

确定设计目标

明确原理图设计的目的和要求, 确定所需元件和功能模块。

1原理图设计-单页原理图详解

菜单功能Edit/Move中有Drag和Move两种移动对象的方式,缺省情况下,Drag方 式移动对象时会保持已有的连线连接,Move方式则仅移动该对象而其它对象状态保持 不变。

18

开始→设置图纸大小和环境→放置元件 →原理图布线→输出报表和打印

报表输出

通过菜单命令Design/Create Netlist…打开网络表创建对话框, 点击OK生成原理图网络表(.NET文件)。网络表描述了各器件是如何 连接的,它为后续的电路板设计作准备。网络表文件是文本文件。

从元件库面板中选取与门元件的示范: 1. 首先在面板上的Library栏中选取 Miscellaneous Devices.lib (此库存了一些常规元件) 2. 在Components In Library栏中利用滚动条找到 AND并选定它。(也可在Filter输入栏中输入元 器件名称*AND*直接查找) 3. 单击Place按钮,此时屏幕上会出现一个浮动 的可随鼠标移动的AND元件符号(元件处于浮 动状态时按空格键可旋转元件,按下X或Y键可 在X方向或Y方向镜像,按Tab键可打开编辑元 件属性对话框),将AND元件符号移到适当的 位置后单击鼠标左键放置元件到绘图页上。

14

开始→设置图纸大小和环境→放置元件 →原理图布线

连接线路(3)

每根导线和每个元件引脚的电气连接点都可以指定一个网络标识 (NetLabel),同名的网络标识之间是连接起来的。 若原理图中两点直接连线不方便,可以在两条待连接的导线上指 定相同的网络标识。(使用画原理图工具栏中的网络标识按钮,将网 络标识名添加到导线上)

9

开始→设置图纸大小和环境→放置元件

设置元件属性

在将元件放置到绘图页之前(元件处于浮 动状态时)按下Tab键,或放置后对该元件双击 鼠标左键,就可打开如图所示的Part对话框。 常用的“Attributes”选项卡中的选项: (1)Lib Ref 在元件库中定义的元件名称,不 会显示在绘图页中。 (2)Footprint 封装形式。应输入该元件在 PCB元件库里的封装名称。(若指定错误则 将会影响后续的PCB设计) (3)Designator 元件标识,如U1、R1。 (4)Part Type 显示在绘图页中的元件名称, 默认值与元件库中名称Lib Ref一致,一般修 改为该元件在电路中的具体型号、阻值、电 容值、电感值等。 (5)Sheet Path 该元件为绘图页元件时,指 明它对应的绘图页文件的路径和文件名。 (6)Part 所使用的子元件的序号,如与门器件 的第一个逻辑门为1,第二个为2,等等。 (7)Selection 切换元件被选中/未选中状态。 10 (8)Hidden Pins 是否显示元件的隐藏引脚。

原理图设计规范

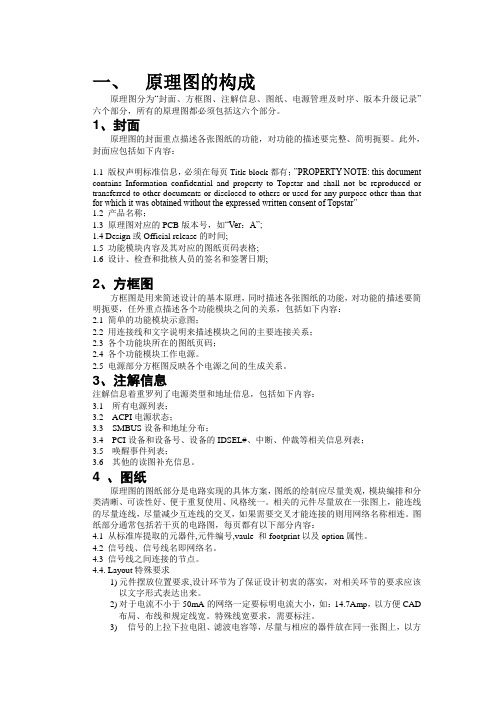

一、原理图的构成原理图分为“封面、方框图、注解信息、图纸、电源管理及时序、版本升级记录”六个部分,所有的原理图都必须包括这六个部分。

1、封面原理图的封面重点描述各张图纸的功能,对功能的描述要完整、简明扼要。

此外,封面应包括如下内容:1.1 版权声明标准信息,必须在每页Title block都有;”PROPERTY NOTE: this document contains Information confidential and property to Topstar and shall not be reproduced or transferred to other documents or disclosed to others or used for any purpose other than that for which it was obtained without the expressed written consent of Topstar”1.2 产品名称;1.3 原理图对应的PCB版本号,如“Ver:A”;1.4 Design或Official release的时间;1.5 功能模块内容及其对应的图纸页码表格;1.6 设计、检查和批核人员的签名和签署日期;2、方框图方框图是用来简述设计的基本原理,同时描述各张图纸的功能,对功能的描述要简明扼要,任外重点描述各个功能模块之间的关系,包括如下内容:2.1 简单的功能模块示意图;2.2 用连接线和文字说明来描述模块之间的主要连接关系;2.3 各个功能块所在的图纸页码;2.4 各个功能模块工作电源。

2.5 电源部分方框图反映各个电源之间的生成关系。

3、注解信息注解信息着重罗列了电源类型和地址信息,包括如下内容:3.1 所有电源列表;3.2 ACPI电源状态;3.3 SMBUS设备和地址分布;3.4 PCI设备和设备号、设备的IDSEL#、中断、仲裁等相关信息列表;3.5 唤醒事件列表;3.6 其他的读图补充信息。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验中可能会出现的问题

1、进入虚拟机时,可能会出现“The disk “D:\Linux_2.6\Centos-1.vmdk” has internal consistency errors…”,点击“Yes”即可。 2、进入虚拟机后,打开一个终端,如果不出意外的话,会 出现listtools将实验室EDA软件一一列出,个别机器出现 “Your nfs system not be mounted…”,此时先检查一下自己 的网络: 切换到root用户,keyword:root 键入命令/usr/sbin/netconfig 选择DHCP (空格键,tab ) /etc/init.d/network restart 若无错误 source /etc/rc.local ls /opt 看看是否有内容了(内含 cadence、synopsys等目录) (若没有则把/lab目录mount到本机/opt目录: mount –t nfs 192.168.10.2:/lab /opt)

接着添加vdd 与gnd

添加管脚,使用快捷键p,Pin Names 为in, Direction 为input,Usage 为schematic,然后在原 理图编辑窗口空白处点击一下鼠标,会出现输入 管脚in 。

使用相同的方法,添加输出管脚out,此时Pin Names 为out,Direction 为output,Usage 为 schematic 。

接下来出现如下图对话框,点击OK

删除绿线框,但红线框要保留。@instanceName与 @partName可以保留,也可以删除。

把红线框拉大点,:Add-shape,利用下面的形状把symbol 修改成你所需要的形状。

画图方法,选中所需要的图形,鼠标左键点一下,然后移 动鼠标,不用按住鼠标左键不放移动鼠标来画图。画完后 图形如下:

主要用于原理图绘制时的快捷键和版图的验证使 用 如图所示:

5、为了能使用Cadence自带的一些库(如analogLib), 需要添加一些IC自带的常用库: 在asic_design中建立工艺库文件cds.lib,并设置库文件的搜 索路径 vi cds.lib 添加以下内容: INCLUDE /opt/cadence/IC5141/share/cdssetup/cds.lib (包含了一些基础库) 退出保存 wq 这样在自己的工作目录下总共有四个文件,分别为 035ms.tf,.cdsinit (是隐藏文件), cds.lib, display.drf 。 用 ls –a 确认一下。 6、启动cadence 在asic_design目录下输入以下命令(注意一定要在自己的工 作目录下): icfb & (加上&是为了让其在后台工作,不影响其他程序执行)

左图NMOS,右图PMOS

二、原理图设计与符号图的生成

1、创建新库(library)、新单元(cell)以及新视图 (view) 主窗口分为信息窗口CIW、命令行以及主菜单。 library, cell, view的关系。 library(库)的地位相当于文件夹,它用来存放一整个设计 的所有数据,比如一些子单元(cell)以及子单元的多种视 图( view)。Cell可以是一个简单的单元,像一个非门,也 可以是比较复杂的单元(由symbol搭建而成)。View则包含 多种类型,常用的有schamatic,symbol,layout等等。

Yes

Laker Calibre Calibre Calibre Hspice

No

OK? Tape out

实验流程:

Cadence 实验

一、实验环境搭建

二、 Schematic (原理图设计与生成符号图) 三 、Pre-simulation(前仿真) 四 、Layout(版图设计) 五、Verification(验证) 六、Post-simulation(后仿真)

创建视图单元/原理图(cell view):在主窗口中 Tools->Library Manager,在 Library中单击 mylib(刚才建立的新库),在 Library Manager 窗 口,然后选择File->New->Cell View,设置Cell Name为inv,View Name为schematic,Tool为 Composer-Schematic,点击OK ,弹出Schematic Editing的空白窗口。 注:给cell起名时,避免使用数字开头的名称,特 别是会影响以后hspice仿真。 (hspice的命名规范:对数字开头的字符串处理 是忽略后面的字符,只保留数字。)

摆放元件并连线,使用快捷键w或使用左面的按 钮 ,注意此时不需要用粗线按钮 来 连线,要用细线来连接。最后的原理图如图所示:

也可以这样画

画完之后,保存并检查文件,点击窗口左上角第一个按钮Check and Save。若有错误 ,会在出错的地方打叉,而且闪动。如下图在vdd的 地方出错了,在那有打叉。

一、实验环境搭建

1、在家用户目录下(/home/edauser目录)新建一个工作目 录:mkdir asic_design(可自定义),将TSMC035.tgz包复制 到该目录下: cp /mnt/hgfs/CentOS_share/TSMC035.tgz ./asic_design 然后 cd asic_design, 解压 TSMC035.tgz :tar –xzf TSMC035.tgz 2、将用到的工艺文件和显示文件(在TSMC035/Virtuoso 下面)拷贝至工作目录asic_design下 。 工艺文件:035ms.tf 显示文件:display.drf cp TSMC035/Virtuoso/035ms.tf ./ cp TSMC035/Virtuoso/display.drf ./ 3、拷贝IC工具自带的.cdsinit文件到工作目录asic_design下 面 cp /opt/cadence/IC5141/tools.lnx86/dfII/cdsuser/.cdsinit ./ (区分大写I和小写L) 这样,在原理图和版图界面中就可以使用快捷键了。

4、vi .cdsinit 在文件的最后一行的上面添加如 下内容(添加内容的前面没有分号) : load(“/opt/mentor/calibre/lib/calibre.skl”) load(“/opt/mentor/calibre/lib/calibre.4.3.skl”) load("/opt/synopsys/hspice-D-2010.03SP1/interface/HSPICE.ile")

工艺库选择

http://192.168.10.2/viewthread.php?tid=1 349&highlight=TSM下载后将TSMC035.tgz放到

D:\linux Shares\linux_26\

实验环境

WinXP+虚拟机linux_2.6

username:edauser

Байду номын сангаас

keyword:edauser IP:192.168.174.100 ftp账号:soc_fanxuesheng 密码:1234567890 下载文件:TSMC035、集成电路课件

选中元器件,按q即可以修改属性 (将鼠标放在对话框下 沿可拉伸对话框大小),Model name为pch,Width 为 1.2u (后面不用加M,系统会自动的添加上M,1.2和u之间 不要有空格),Length为400.0n( 或0.4u),修改完属性 后点击OK。如下图所示:

Model name为自定义,写成pch 是因为p代表PMOS,ch 代表schematic原理图。PMOS管的长度与宽度值为经典值。 用同样的方法在原理图编辑窗口添加NMOS, Model name 为nch, Width 为400.0n , Length为400.0n 。如下图所示:

PMOS、NMOS符号图的介绍

PMOS的符号图

NMOS的符号图 说明:不论PMOS、NMOS带箭头的一端代

表源极,相对应的一端代表漏极,在左面 单独的一端代表栅极,中间的一端代表衬 底。

开始绘制原理图,添加元件(instance)使用快捷键“i” 快速调出元器件库,或使用左边相应的按钮

出现的主窗口如下图所示:

CMOS、PMOS简介:

PMOS横切图: Source 源极 , Gate 栅极,Drain 漏极 , Body 衬底 右下角符号图

NMOS横切图 Source 源极 ,Gate 栅极,Drain 漏极 , Body 衬底 右下角符号图

另一个角度的横切图

Cadence软件工具,在本设计中主要用到:

schematic:

simulation: layout: verification:

virtuoso spectre & hspice

virtuoso calibre (off-line)

完整为主: 必须包含: spectre & hspice 库、 diva 规则文件、dracula & Calibre规则文件 最好能包含: assura (版图验证工具)规则文件 台湾教学大多用 CIC TSMC035,pad信息不全,流片时由CIC 负责替换 //实验中所用的工艺为TSMC035 ,

查错方法:使用快捷键“g”,弹出错误对话框,按照提示 改正 。 此处的错误是画了两个vdd,两个vdd叠放在一起了。

另一种方式,是通过主窗口对话框来查错

如何改错,先删掉黄色的叉号,再对相应

的位置进行修改。

生成符号图(symbol view)