达芬奇平台DM6446介绍

基于DM6446达芬奇平台的人脸识别系统

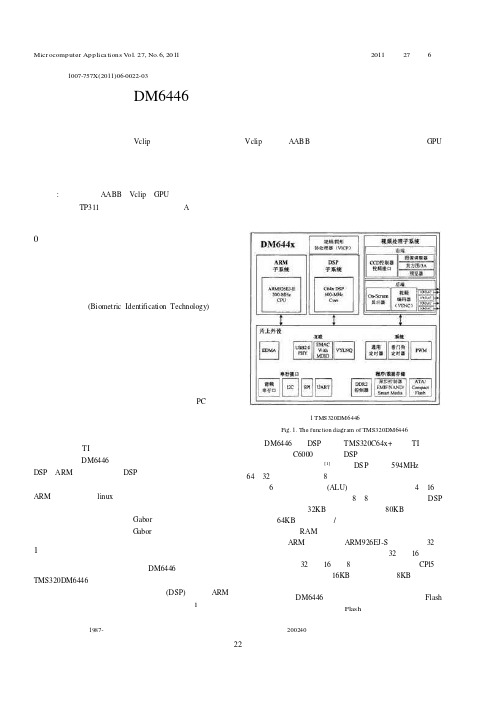

Micr ocomputer Applica tions V ol.27,No.6,2011研究与设计微型电脑应用2011年第27卷第6期文章编号:1007-757X(2011)06-0022-03基于DM6446达芬奇平台的人脸识别系统刘昆摘要:文章提出了一种基于Vclip的优化碰撞检测算法,利用Vclip算法对AABB包围盒进行底层碰撞检测计算,用GPU 的遮挡查询等特性进行三角形相交测试,以提高对虚拟物体进行碰撞检测的精确性与实时性。

算法已成功应用于课题组自行研制的六自由度小型工业机器人的仿真控制系统中,实验结果表明,其算法具有高效、精确、实时性高等特点,能使控制系统对工业机器人的控制更为流畅。

关键词:碰撞检测;AABB;Vclip;GPU;机器人仿真中图分类号:TP311文献标志码:A0引言身份认证是人类社会日常生活中的基本活动之一。

目前我们大多依赖于身份证、钥匙、密码等传统的标识物来完成身份认证过程,但传统的身份认证手段存在的缺点也是显而易见,便捷可用性差,安全性不足。

而基于人体生物特征的生物识别技术(Biometric Identification Technology)可以从根本上杜绝伪造和窃取,具有更高的可靠性、安全性和可用性。

人脸识别作为生物识别技术的一个分支,是指利用计算机对人脸图像进行分析,从中提取有效的识别信息,进而用来分辨身份的一门技术。

作为近年来生物识别领域的一个热门研究方向,人脸识别具有操作方便,用户易于接受,事后追踪能力强等优点。

由于人脸识别算法的复杂度高、运算量大等缺点,目前大多数的人脸识别系统是基于PC平台开发的。

而随着各行各业中对人脸识别系统的便携性的要求,在嵌入式平台上对人脸识别算法进行移植与优化,进而实现嵌入式人脸识别系统具有现实意义。

本文选用TI公司专为视频图像处理推出的达芬奇数字多媒体处理器DM6446作为中央处理单元,其内部集成了DSP与ARM双核。

达芬奇技术简单介绍

达芬奇(DaVinci™)技术是一种专门针对数字视频应用、基于信号处理的解决方案,能为视频设备制造商提供集成处理器、软件、工具和支持,以简化设计进程,加速产品创新。

目录∙达芬奇技术产品系列∙达芬奇技术开发工具∙达芬奇技术简化数字视频设计∙面向数字视频的达芬奇技术达芬奇技术产品系列∙TMS320DM644x 数字媒体处理器——基于ARM926 处理器与TMS320C64x+DSP内核的高集成度。

TMS320DM6446、TMS320DM6443 和TMS320DM6441 处理器适用于视频电话、车载信息娱乐以及IP机顶盒(STB)等应用和终端设备。

TMS320DM643x 数字媒体处理器——基于C64x+TM DSP 内核TMS320DM6437、TMS320DM6435、TMS320DM6433 和TMS320DM6431 处理器是低成本应用领域的最佳解决方案,适用于车道偏离、防碰撞系统等车载市场应用、机器视觉系统、机器人技术和视频安全监控系统等。

TMS320DM647/TMS320DM648 数字媒体处理器——专门针对多通道视频安全监控与基础局端应用进行了优化,这些应用包括数码摄像机(DVR)、IP 视频服务器、机器视觉系统以及高性能影像应用等。

DM647 和DM648 数字媒体处理器具有全面可编程性,能够为要求极严格的流媒体应用提供业界领先的性能。

TMS320DM6467 数字媒体处理器——一款基于DSP 的SoC,专为实时多格式高清晰度(HD) 视频代码转换精心打造,能在前代基础上以仅十分之一的价格实现10倍的性能提升。

DM6467 集成了ARM926EJ-S 内核、C64x+ DSP内核,并采用高清视频/影像协处理器(HD-VICP)、视频数据转换引擎与目标视频端口接口。

DM6467 可充分满足HD 转码方面的市场要求,非常适用于企业及个人市场的媒体网关、多点控制单元、数字媒体适配器、数字视频服务器以及安全监控市场记录器与IP 机顶盒等应用。

TI最新达芬奇处理器DM6467 — TMDXEVM6467

TI最新达芬奇处理器DM6467 — TMDXEVM6467德州仪器(TI)最新推出了一款能够在多种应用间进行视频转码的新型达芬奇技术数字媒体处理器,这些应用包括媒体网关、多点控制设备、数字媒体适配器、视频安全监控DVR 以及IP 机顶盒等。

新型TM S320DM6467达芬奇处理器是一种基于DSP的片上系统(SoC),特别适合实时多格式高清(HD)视频编解码,并配套了完整的开发工具及数字多媒体软件。

该芯片集成了ARM926EJ-S内核与600MHz C64x+ DSP内核,并采用了高清视频协处理器、转换引擎与目标视频端口接口,在执行高清H.264 HP@ L4(1080p 30fps、1080i 60fps、720p 6 0fps)的同步多格式编码、解码与转码方面,比前代处理器性能提升了十倍。

实时多格式高清转码技术DM6467专为应对商业及消费类电子市场的高清转码挑战而设计的,通过其多内核设计,能够实现较前代数字媒体处理器高十倍的性能。

DM6467 处理器集成了ARM与DSP内核,并采用高清视频/影像协处理器(HD-VICP)、视频数据转换引擎以及目标视频端口接口。

HD-VICP 通过面向HD 1080i H.264 high profile 转码的专用加速器,实现了超过3GHz 的DSP处理能力,同时视频数据转换引擎还能管理包括垂直下调节(downscaling)、色度采样(chroma samp ling) 以及菜单覆盖(menu overlay) 等功能在内的视频处理任务。

不到300MHz的DSP内核可用于管理多格式视频转码,并为其它应用预留了足够的空间。

DM6467 可满足媒体网关与MCU 等需要转码技术的市场要求,但其强大的灵活性与高效性对要求同时进行高清编码与解码的应用来说也非常具有吸引力,如视频语音或视频安全等对于多通道标清编码要求较高的市场。

该器件的连接外设中还包括标准PCI 总线及千兆以太网。

达芬奇解码视频或音频或语音文件

2017/4/21

青岛理工大学

通信学院

3

main.c

main.c:只要算法实现了XDM(标准)接口,就需 要一个main.c的程序去初始化CE,然后用其他 配置脚本来创建一个服务器镜像*.x64P. 在 main.c里面除了调用CERuntime_init()初始化 CE外,就是对于trace相关函数的初始化和处理 。

2017/4/21

青岛理工大学

通信学院

4

XDC相关文件

package.xdc /*--------------声明包名-----------------*/ package server{}

package.bld 声明所必须包含的包,链接命令脚本,tcf文件和一些源文 件,定义编译属性、平台和对象等.

2017/4/21

青岛理工大学

通信学院

15

Decode.cfg

/* Load support for the Codec Engine */ var osalGlobal = eModule( 'ti.sdo.ce.osal.Global' ); /* Configure CE to use it's DSP Link Linux version */ osalGlobal.runtimeEnv = osalGlobal.DSPLINK_LINUX;

解码视频或音频或语音 文件

程雷雷

Codec Server

编解码服务器(CS)就是一个二进制文件,它集成了编解码器, 框架组件和一些系统代码,当CS运行在DSP上时,它使用了 DSP/BIOS作为其内核.CS同时包括了对客户请求的相关 DSP/BIOS线程.CS可以代表实际的DSP硬件、导入到DSP上 的镜像文件以及正在运行的任务,其配置需要两个步骤: 通过TCF脚本语言配置DSP/BIOS; 通过XDC配置剩下的组件,比如:FC组件、DSP/BIOS Link、 Codec Engine等.配置完成的服务器镜像文件是在引擎配置 文件(ceapp.cfg)中使用的,如demoEngine.server = "./encodeCombo.x64P";

基于TMS320DM6446的H.264视频编码器的实现及优化

[ 中图分 类 号 ] T N 9 1 9 [ 文献标 志 码 ] A [ 文 章编 号 ] 1 6 7 3— 8 0 0 4 ( 2 0 1 3 ) 0 5— 0 l l 3一 O 6

第3 2卷

第 5期

基于 T M S 3 2 0 D M 6 4 4 6的 H . 2 6 4 视频编码器的实现及优化

宋 雪亚 , 王 传 安

( 安徽科技学院理学院 ,安徽 凤阳 2 3 3 1 0 0 )

[ 摘

要] 文章为实现基于 T M S 3 2 0 D M 6 4 4 6的 H . 2 6 4 视频编码 器的实时性能, 提 出一 系列优化

如 何将 繁冗 的 H . 2 6 4编 码 算 法 移植 到 D M 6 4 4 6 中去. 本 文讨 论 的是 H. 2 6 4实 时编 码 的实现 , 因

此 只对 X 2 6 4的基 本 档 次 ( b a s e l i n e p r o i f l e ) 的 移

植 做说 明. 移 植工 作 主要 分 3个 步骤进 行 : ( 1 ) 提 取 出相关 代 码 , 重新 建 立 起 程 序 框 架 , 在 V C 下 编译 调试 通过 后 作 相 应 修 改 使 其 能 在 目标 编译

器C C S ( C o d e C o mp o s e r S t u d i o ) 上编译通过 ; ( 2 )

所以具 有专 用 集成 芯 片专 用 性 的一 面. 同时 ,

达芬奇技术介绍

达芬奇技术介绍第一讲:达芬奇技术总体概述达芬奇技术(DaVinci™)简言之就是包含有针对数字音视频优化的基于DSP的系统解决方案,其中有四个基本组成,即处理器、软件、开发工具套件和支持,如图三所示。

图三:达芬奇系统构成达芬奇处理器是一个单片系统,集成有TI高性能C64+核心DSP和ARM9核心处理器以及视频前端处理器和视频加速器,还有非常丰富的外围设备,如数字视频、数字音频、高速网络、DDR2高速存储器、ATA硬盘和多种存储卡等接口。

在软件方面达芬奇全面支持由底层到高层的软件系统。

达芬奇在嵌入式操作系统方面对Linux的支持极为完善,也有支持WinCE的能力;在数字视频、影像、语音和音频上可以支持H.264、MPEG4/2、H.263、VC1、JPEG、G.711/G.723、MP3、WMA 等多种编解码器;通过多媒体框架结构进行数字视频软件系统的集成,并提供API驱动程序支持,同时有助于实现处理器间的通信。

达芬奇有多种开发工具套件以满足各种需求,其中评估模块和参考设计将有益于硬件设计,而数字视频开发平台和Green Hills开发工作将对缩短软件系统集成有很大帮助。

达芬奇的支持体系很强大,其中既有来自TI授权软件提供商(ASP)的支持,也有更为广泛的第三方网络的支持。

所有的数字视频类产品都有机会采用达芬奇技术,这里不仅有众所周知的产品,如数码相机或摄像机、个人媒体播放器、数字机顶盒、IP可视电话、数字媒体网关、数字视频服务器、IP网络摄像机、数字硬盘录相机等,还有未来创新的数字视频,如包含汽车智能视觉在内的新产品,当然还有更多的产品有待脱颖而出。

在达芬奇技术研讨会上,对第一批达芬奇芯片DM6446/6443的内部结构和应用的讲解集中在ARM与DSP的高速通信、外围高速扩展接口的使用、视频前端处理器(VPSS)的配置、中心交换资源(SCR)的调度等技术细节,并且深入地分析了不同开发工具的特点和在达芬奇软件系统开发中的作用。

Davinci平台(DM644x)软件编程培训

Analysis Control Intelligent Applications

B/W:1Mbits/s B/W: 12 Mbits/s B/W: 32 K bits/s

Audio Capture Capture

Audio Coding

AAC/WMA

TI/DaVinci components Customer components TI/MontaVista/ Open Source

application layer Enables varying levels of abstraction from DSP multimedia processing functionality No dependencies on DSP/BIOS, Link - xDM codecs can work in any framework

Video/Audio Analytics

B/W: 16 Mbytes/s D1: 30 FPS YUV422

Central office

Motion detection Event detection Object tracking Object recognition

Image Coding

B/W : 96 K bytes/s, mono JPEG B/W: 1.2 Mbytes/s QVGA: 15 FPS , Y

MP3+

MPEG4

H.264 AAC+

MP3+

MP3 Node H.264 BIOS JPEG PSP

Component- ware

TI Provides

Config kit “How-to” Methodology for creating Custom Combos

北科大信号系统与信号处理综合实验

北京科技大学《信号系统与信号处理综合实验》实验报告专业班级:学生姓名:学号:指导教师:实验成绩:年月日计算机与通信工程学院目录一、SEED-DTK6446 CCS 平台实验 (2)1、DDR2 SDRAM 实验 (2)2、Audio 音频实验 (6)3、RS232实验 (5)4、结论及思考 (8)二、Linux 平台实验 (10)1、入门实验 (10)2、OSD图像叠加实验 (14)3、视频采集回放实验........................................................................... 错误!未定义书签。

4、结论及思考 (15)三、自主设计实验 (16)四、总结与收获 (25)五、教师评语 (25)一、SEED-DTK6446 CCS 平台实验1、DDR2 SDRAM 实验实验目的1. 了解SEED-DVS6446 外部存储器DDR2 SDRAM;2. 了解TMS320DM6446 芯片DDR2 存储器控制器的特点;3. 熟悉DDR2 SDRAM 的读取操作。

实验内容1. 系统初始化;2. 外部接口的初始化;3. DDR2 SDRAM 的读写操作。

实验报告要求1. 将ddr 工程运行结果截图。

2. 分别在ddr_test.c 中的第20 行、21 行设置断点,将memory browser 窗口截屏,地址栏为0x80000000。

3. 分析第ddr_test.c 中的20 行、21 行代码的作用,将memory browser 窗口截屏。

第20行代码:retcode |= memaddr32(ddr_base, ddr_size );作用:memaddr32函数分为读操作和写操作两个部分,/* Write Pattern */for ( i = start; i < end; i += 4 ) {*( volatile Uint32* )i = i; }写入部分操作是将操作数i存入寄存器中。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

VENC 的数字LCD 控制器(DLCD)有如下特性: 时钟可编程,最高可达75MHz 支持多种数字视频输出格式 16-位YCbCr 8-位YCbCr BT.656 24-位RGB 用于数字RGB 输出的低通滤波器 可编程时序发生器 支持主/从操作方式 内部产生彩色条(100/75%)

连接性 VLYNQ EMAC With MDIO

系统 General- Watchdog PWM Purpose Timer PWM PWM Timer 程序/数据存储 DDR2 Controller (16b/32b) ATA/ Async EMIF/ NAND/ Compact SmartMedia Flash MMC/ SD

理后的视频图像通过OSD模块可以进行字幕和图标的添加,通

过视频编码(VENC)可将原始视频信号处理为特定格式的模拟 视频数据和数字视频数据。

视频处理前端(VPFE)

CCD 控制器从传感器(CMOS 或CCD)接收原始图像/视频数据或者从 视频解码装置接收YUV 格式视频数据。 预览器将从传感器(CMOS 或CCD)接收的原始的未处理的图像/视频 数据转化成YCbCr 422 格式的数据。预览器的输出可以用于视频压缩, 或者外部显示设备,如NTSC/PAL 模拟编码器或数字LCD。 图像缩放装置从硬件实现图像大小的缩放。可以从预览器或者DDR2 接 收输入的图像/视频数据,输出到DDR2。 H3A 模块是提供自动白平衡、自动对焦、自动曝光的控制环路。包含两 个主要模块: VENC 的模拟/DACs 接口有如下特性: 自动对焦(AF)引擎装置 自动曝光(AE)与自动白平衡(AWB)引擎装置 柱状图模块依靠输入的颜色像素和提供的统计需求来执行不同的3A 算法, 最后调整最终的图像和视频输出。柱状图模块的数据源一般为 CCD/CMOS 传感器(通过CCDC 模块)或者DDR2.

DSP 子系统

ARM926EJ-S 300 MHz CPU

C64x+TM DSP 600 MHz Core

后端

屏幕菜单式 视频 调节 (OSD) 编码器 (VENC) 10b DAC 10b DAC 10b DAC 10b DAC

资源交换中心 (SCR)

外设

EDMA USB 2.0 PHY 串行接口 Audio Serial Port I2 C SPI

目录

1.

DM6446整体结构 VPSS视频处理子系统

一个简单的视频处理实例

2. 3.

4.软件架构(扩展)

DDR

Flash

LCD显示器 摄像头 TVP5150

DM6446

ATA

视频采集回放框图

TMS320DM6446提供了VPSS视频处理子系统,包括视频处理前端 (VPFE)和视频处理后端(VPBE),分别用于外部图像输入设备和视 频输出设备。

在进行寄存器(0x00~0x8F)配置时,TVP5150 需要一段延时来完成当 前的配置,此时TVP5150 保持SCL 为低,通知DM6446 配置尚未完成。 在编程时,一般不用查询当前的SCL 的状态,而是配置需要的最大延时 64us。示例如下:

void tvp5150_init( ) // TVP5150初始化,设置5150的寄存器 { DAVINCIEVM_waitusec( 1000 ); tvp5150_rset( 0x00, 0x00 ); // 配置视频输入源选择寄存器,寄存器地址为0x00,寄存器数据为0x00(选择了符合视频1通道,查看5150 的数据手册)Input Video: CVBS : VI_2_B tvp5150_rset( 0x03, 0x6d); //查看5150的数据手册,寄存器地址0x03是混杂寄存器,8位寄存器配置数据0x6d每位代表了不同的意思 tvp5150_rset( 0x09, 0x8B); //亮度控制寄存器地址0x09,寄存器值0x8B tvp5150_rset( 0x0a, 0x80 );//色彩饱和度寄存器地址0x0a,寄存器值0x80 tvp5150_rset( 0x0b, 0x00 );//色调调节寄存器0x0b,默认值0 tvp5150_rset( 0x0D, 0x07 ); //输出和数据率选择寄存器YUV output format, Enabling clock & Y/CB/CR input format tvp5150_rset( 0x0F, 0x02 );//配置复用引脚寄存器 tvp5150_rset( 0x15, 0x05 );//同步锁相和实时时钟寄存器 tvp5150_rset( 0x1B, 0x14 );//色差控制寄存器 DAVINCIEVM_waitusec( 1000 ); // 等待1 msec的延迟 wait 1 msec }

UART UART UART

DM6446系统DSP子系统具有以下特性

• 配置594MHZ的C64x+ DSP CPU内核,单时钟周期内能运行8条32位 C64x+指令,运算能力达到4752MIPS • 32KB L1P程序RAM/Cache • 80KB L1D数据RAM/Cache • 64KB统一映射L2 RAM/Cache • 数据对齐模式为小端模式

ARM子系统包含以下特性

• • • • • • • • • • • • • • • ARM926EJ-S RISC处理器 ARMvSTEJ (32/16-bit)指令集 小端模式 CP15协处理器 内存管理单元 16KB指令cache 8KB数据cache 支持写入缓冲区 32位的16KB内部RAM 8KB内部ROM(支持无EMIFA启动选项的ARMbootloader ) 跟踪宏单元(ETM)和嵌入式跟踪缓冲区(ETB) ARM中断控制器 PLL控制器 电源与体眠控制器(PSC) 系统组件

DM6446特点

(1)高性能

DM6446采用低功耗、高性能的32位C64+内核和ARM内核,工作频率分别达 到594MHz和297MHz,具有很强的运算处理能力和事物控制能力。

(2)专用的视频处理子系统

视频处理子系统包括1个视频前端输入接口和1个视频末端输出接口,视频前端 输入接口用于接收外部视频解码器输入的视频数据,视频末端输出接口则可以直接 输出DM6446处理后的视频数据到SDTV, LCD, HDTV等显示屏上。

(3)大存储容量

DM6446支持256MB的32位DDR2 SDRAM存储地址空间;支持128MB的16位 FLASH存储地址空间;DM6446同时具有ATA控制器,可外接大容量硬盘。

DM6446特点

(4)众多的外设

DM6446具有64通道EDMA控制器;串行端口(3个UART, SPI, ASP); 3个64位通 用定时器;10/100M以太网卡模块;USB2.0端口;3个PWM端口;多达71个通用I/O口;支 持MMC/SD/CF卡等。

视频输入 SEED-DVS6446 视频输入接口选用了解码芯片

TVP5150PBS。它是一款高性能的视频解码器,可将NTSC、

PAL 视频信号转换成数字色差信号(YUV422),支持两个复合 视频或一个S 端子输入。不仅如此,TVP5150PBS 还具备了封 装小(32 脚的TQFP)、功耗小(<150mV)的特点,因此, 非常适用于便携、批量大、高质量和高性能的视频产品。

视频处理后端(VPBE)

OSD 模块的主要功能是在硬件上实现图形、字符叠加。同时支持2 个视 频窗和2个图形、字符(OSD)窗口,支持8 种视频窗数据与OSD 窗数 据混合的方法。图形、字符数据从外部存储器读入,一般为DDR2。 OSD 通过控制和参数寄存器编程实现其功能。 VENC 的模拟/DACs 接口有如下特性: 支持480P/576P NTSC/PAL 标准模拟视频输出 4-通道10-位D/A 输出,可产生各种组合的模拟视频输出 复合视频 超级视频(S-Video):使用2 通道DAC 分量视频(YPbPr 或RGB):用3-通道D/A 复合视频 + 分量视频:用4-通道D/A ������ 内部产生彩色条(100/75%)

TVP5150的写操作

TVP5150的读操作

TVP5150的写操作

DM6446 产生一个起始条件; DM6464发出一个TVP5150 的地址(0xBA或0XB8),并标明写操作, 等待TVP5150响应; 接收到TVP5150 的响应后,DM6446 发出要配置的寄存器的地址,等待 TVP5150响应; 接收到TVP5150 的响应后,发送要配置的数据,等待TVP5150 响应; 接收到TVP5150 的响应后,发送停止位,结束一次配置。

TVP5150

的视频输入

视频解码器TVP5150PSB 可以接受2 路复合视频信号(CVBS)和1 路超 级视频信号(S-Video,Y/C)输入。在本系统使用了两片TVP5150PSB,每 片只使用了1路的复合信号。输入电路如下图所示:

视频编码器TVP5150PBS 的视频信号输入范围为0.75Vpp,而外部视频信 号输入范围一般为1 Vpp,所以外部视频输入与TVP5150PBS 的视频输入之 间串接39Ω 和39Ω 到地分压电阻网络,以达到TVP5150PBS 所需的输入电 平。在使用前一定要将视频信号输入的范围调整到1 Vpp。

视频处理前端(VPFE)包括CCD摄像头控制器(CCDC),预

览引擎,裁放器,支持自动聚焦(Auto-focus}、自动白平衡

(Auto white balance)和自动曝光(Auto exposure)的3A硬件引 擎。视频处理后端(VPBE)包括:画中画显示((OSD)和视频编码 引擎(VENC)。CMOS或CCD摄像头采集的原始视频图像由视 频处理前端进行裁放、直方图均衡、图像优化等预处理,预处