·沈燕飞《基于达芬奇平台的视频应用》PDF

基于达芬奇平台的微光视频处理系统的设计

基于达芬奇平台的微光视频处理系统的设计

何娴

【期刊名称】《山西电子技术》

【年(卷),期】2010(000)005

【摘要】深入研究和分析微光视频增强技术,为了解决微光视频的实时处理能力,结合达芬奇平台的技术特性设计基于TMS320DM6446平台的微光视频实时处理系统的图像增强系统,实现微光视频系统的实时采集、实时处理和实时显示模块,最后通过测试处理结果和实时性两方面进行测试表明系统设计满足要求.

【总页数】3页(P14-16)

【作者】何娴

【作者单位】江苏海事职业技术学院,信息工程系,江苏,南京,211170

【正文语种】中文

【中图分类】TN223

【相关文献】

1.基于达芬奇平台的无线视频智能监控系统设计 [J], 秦华

2.基于达芬奇平台的高清视频监控系统的设计与实现 [J], 何登平;黄凌云;何策

3.基于达芬奇平台的网络视频监控系统设计 [J], 张明明;李庆武

4.基于达芬奇平台嵌入式视频处理系统设计 [J], 王刚;程俊

5.基于达芬奇平台的视频混沌加密系统的设计 [J], 余攀;李文勋;张宝强

因版权原因,仅展示原文概要,查看原文内容请购买。

达芬奇技术的视频应用分析

ARM 双核结构不仅能同时满足视频应用 在 运 算 能 力 和

控制功能上的要求 , 而且大大简化了系统设计的复杂性 , 很有可能成为今后视频应用处理芯片的主流解决方案

2

针对视频应用的达芬奇技术

如图 l 所示 , 达芬奇技术是根据视频应用的各种需

GA 凭借强大并行处理能力和可定制流水线结构 , 非常适

l" 在 内 存 访 问 方 面 # 内 核 开 始 支 持 DDR2 # 数 据 吞

吐量可达 l GByte/S 以上 # 比传统平台所搭载的 SDRAM 数据吞吐量提高了一倍以上 ! 针对视频处理的特点 # 内 核增加了三维的 EDMA 搬移操作 # 并增强了二维 EDMA 操作 的 能 力 ! 新 内 核 还 引 入 了 L1MemOly 空 间 和 IDMA 机制 #能更加灵活地进行内存访问 [2]# 如图 2 所示 !

整地进行视频应用系统的设计 " 从 图 4 可 以 看 出 !DM6446 能 通 过 单 处 理 芯 片 提 供 完整的机顶盒解决方案 " 当然 !DM6443 也可完成一个完 整的视频终端解码系统设计 "

5

小结

本文介绍了 TI 最新推出的达芬奇技 术 及 其 代 表 产

品 DM6446/3 多媒体处理芯片的软硬件技术特点 ! 分析 了 在 视 频 编 解 码 算 法 方 面 !DM6446/3 的 DSP 子 系 统 相 对于传统 DSP 平台所具备的优势 ! 最后介绍了达芬奇技 术的应用现状 ! 并提出了一些现存的问题 " 总的来说 ! 达芬奇技术整合了多项视频应用方面的 前沿技术 ! 针对视频应用的需要对 DSP 子系统进行全面 的增强 ! 而且由于集成了 ARM 和 DSP 双处理核 ! 能给出 一个基于单芯片的完整视频应用解决方案 " 从这方面来 说 !达芬奇技术已经走到了视频应用的前沿 " 参考文献

基于达芬奇平台的微波视频监控系统的软件设计

大 众 科 技

DA ZHONG J KE

2 0 7 0 7.

(u li lN . ) C mu te o9 av y 5

基 于达芬奇平 台的微波视频监控系统 的 软 件 设 计

高 强 ,吕 为 ,胡子衡 ,袁誉 乐 ,王 磊 ,吴 云 ,赵 勇

【 中图分类号】T N 【 文献标识码 】A 【 文章编号 】1 0 — 1 1( 0 7 7 07 — 4 0 8 15 20 )0 - 0 6 0

是 由 M n aV s a公 司提 供 。它 包 括 : o t it

微波站通常位 于高 山上 ,设施被盗,给微波系统 的正常 工作 带来严重 的影 响。如能利用图像 监控系统将微波站 图像 实 时传输到通信 网管中心,就会 大大提高微波站设施 的安全 性 。但通常情况下微波 站都分布在较广阔 的范 围内,利用传 统 的有线连接方式 ,线 路铺 设成 本高 昂。若能利用现有 带宽 的微波信道进行视频信 号的传输 ,则可 以很好地解决这个 问

3 传输协议采用 R P . T

( 广 东电网公 司深圳供 电局 , 东 深圳 58 0 ; . 大学深圳研 究生院 , 东 深圳 58 5) 1 . 广 10 1 2 北京 广 105

【 摘 要】有线电视监控在 生活和 工作 中得到 了广泛的应用 ,然而在某些环境 中,由于成本或地形 所限 ,有 线电视监控无 法实现。无线网络产品的快速发展和视频压缩标准的 日渐完善 对此提供 了较好 的解决方案 。文章 阐述 了达芬奇平 台的特 点, 分析 了软件 系统的组成。在 此基础上 ,提 出了一种基 于达芬奇平台的微 波视频监控 系统的软件设计 ,取得 了良好的效果。 【 关键词】软件设计 ;达芬奇平 台;微 波 ;视频监控 ;H. 4 2 6

达芬奇技术在视频和机器人方面应用案例及技术文献汇总

达芬奇技术在视频和机器人方面应用案例及技术文献汇

总

本文介绍达芬奇技术的解读文献及应用案例,供大家参考。

解读达芬奇技术

达芬奇技术是一种数字图像、视频、语音、音频信号处理的新平台,一

经推出,就受到热烈欢迎,以其为基础的应用开发层出不穷。

该技术是一种内

涵丰富的综合体,包含达芬奇处理器、软件、开发环境、算法库和其他技术支

持等。

正因为涉及的技术面广,因此有比较高的技术门槛。

视频跟踪算法在Davinci SOC 上的实现与优化

本文在基于双核DM6446 的系统平台上,利用改进后的跟踪算法实现了

智能目标跟踪系统。

该算法可以成功跟踪目标,并具有较强的鲁棒性。

该技术

将会在智能视频监控、智能用户接口、基于对象的视频压缩、巡航导弹末端制

导和辅助驾驶等领域有广泛应用前景。

达芬奇视频处理器如何为智能安防系统带来差异化?

随着安防设备向高清化智能化和网络化发展,监控摄像机发挥的作用越

来越大,ISP(image signal processor,图像信号处理器)技术是实现高清网络摄像机差异化、低功耗、低成本的关键,先进的ISP 技术有助于本土品牌在竞争中

中获得更大优势。

达芬奇手术机器人系统介绍

达芬奇机器人手术系统以麻省理工学院研发的机器人外科手术技术为基础。

Intuitive Surgical 随后与IBM、麻省理工学院和Heartport 公司联手对该系统进行了进一步开发。

FDA 已经批准将达芬奇机器人手术系统用于成人和儿

童的普通外科、胸外科、泌尿外科、妇产科、头颈外科以及心脏手术。

基于达芬奇平台的视频编码器实现

基于达芬奇平台的视频编码器实现王宏志;苏令华;王晓红;顾欣【期刊名称】《计算机测量与控制》【年(卷),期】2011(19)5【摘要】H.264 is the most advanced video encoding standard, and its high complexity is the bottleneck in its applications. Based on the DSP of TI' S TMS320DM6446, a X264 encoder is designed. The local average difference of histogram is introduced to the amount determination of reference frames, and the little diamond search algorithm is used in the movement estimation process. Experiment results indicated that, quasi real time encoder of CIF video is achieved, while high image quality is preserved.%H.264协议是目前最先进的视频编码标准,高复杂度是算法推广的最大瓶颈;提出一种采用TI公司多媒体处理器DavinciTMS320DM6446为核心硬件平台的X264编码器实现方案,该方案采用了局部直方图平均差值进行参考帧数确定,运动估计采用小菱形搜索算法;实验结果标明,在保证图像质量条件下,编码器达到了CIF分辨率视频的准实时压缩要求.【总页数】3页(P1158-1160)【作者】王宏志;苏令华;王晓红;顾欣【作者单位】空军大连通信士官学校,辽宁,大连,116600;空军大连通信士官学校,辽宁,大连,116600;空军工程大学,电讯工程学院,陕西,西安,710077;空军大连通信士官学校,辽宁,大连,116600;空军工程大学,电讯工程学院,陕西,西安,710077【正文语种】中文【中图分类】TK428;TP206.3【相关文献】1.基于达芬奇技术的H.264视频编码器的实现 [J], 成嘉;张文雄;李善劲2.基于嵌入式平台的h.264视频编码器的实现 [J], 鲍可进;陈波;杨涛3.基于达芬奇平台的H.264视频编码器设计 [J], 韩文俊;任国强;吴钦章4.基于PNX1300 DSP平台的视频编码器优化实现 [J], 白琳;罗玉平5.基于达芬奇技术的H.264视频编码器的研究与实现 [J], 卢宁;柯熙政;贾贞因版权原因,仅展示原文概要,查看原文内容请购买。

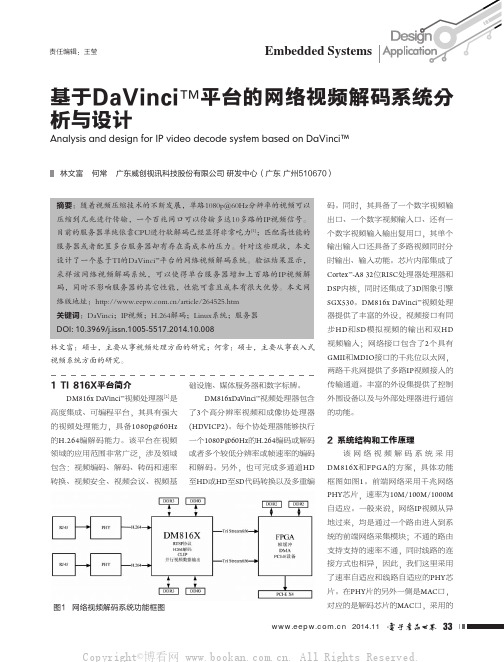

基于DaVinci平台的网络视频解码系统分析与设计

图1 网络视频解码系统功能框图

是千兆通信方式,网络时钟的速率是125MHz。

从带宽上来看,前端网络和显示处理模块。

视频缓冲和显示处理模块主要由

有效位(DE)、行同步信号(HS)、场

同步信号(VS)输给后端FPGA进行处

图2 AVS可调电路

序均有严格要求,因此专门针对该芯片设计了上电时序电路和AVS可调电源。

芯片的上电时序要求为3.3V>1V 由逻辑芯片内存自带的现。

图3 系统软件分层图

使用EVAL-CN0313-SDPZ提供的解决方案,能够有效保护RS-485接口免受真实世界的高压瞬态影响。

将机器人控制网络暴露在电子护栏增能器

图4 三个EMC兼容ADM3485E电路(原理示意图,未显示所有连接)

现业务层模块间的通件的告警/事件信息。

Codec_hdvpss模上接35。

基于达芬奇平台的视频监控系统的设计 丁锐 袁誉乐 赵勇 关键词:达

基于达芬奇平台的视频监控系统的设计丁锐 袁誉乐 赵勇(北京大学深圳研究生院 广东深圳 518055 email:sara.halifa@)摘要:本文中设计并实现了一个基于TI最新的DSP多媒体平台——Da Vinci平台的微波传输无线监控系统。

介绍了新一代双核DSP平台的特性,阐述了基于双核系统的开发方法和流程。

关键词:达芬奇;嵌入式系统; xDAIS; 双核;中图分类号:TP368.1 文献标志码:ADesign and implement of the video surveillance system based on DaVinci platformDing rui, Yuan yule, Zhao yong(Peking university Shenzhen graduate school,Guangdong,518055,chinaemail:sara.halifa@)Abstract:This paper implements a video surveillance system based on the new dual core platform Da Vinci. Describe the detail of the develop method and flow. Keyword: DaVinci; Embedded system; xDAIS; dual-core;1 简介在日常生活中,很多高危险区、无人区需要人们随时监控。

在布线困难的情况下,出现了很多无线监控系统。

然而无线监控系统面临着很多设计挑战例如:稳定性,功耗,带宽不足带来的效果低下等等。

本文中设计和实现了一种新型微波无线视频监控系统。

它的优点主要在于:1 基于TI公司的最新DSP处理系统,有着低功耗,高性能,高稳定性的特点,保证了视频图像处理的高效性;2 采用最新的H.264高效视频压缩算法,使得利用有限带宽传输D1级别的清晰成为可能。

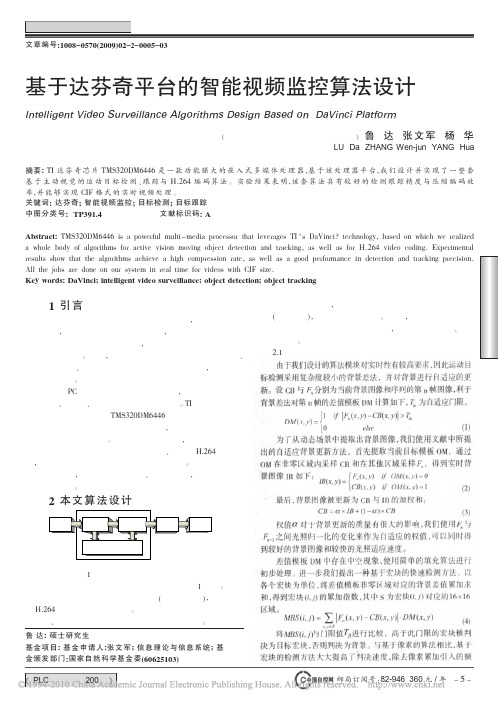

基于达芬奇平台的智能视频监控算法设计

2.2 运动目标跟踪

我们 对 检测 到 的 运动 目 标 进行 进 一 步的 跟 踪 , 并 基 于 主 动 视觉对摄像头云台进行控制。 为了提高算法处理的速度与性 能 , 我 们选 择 使 用 Mean-Shift 算 法 与 卡尔 曼 滤 波相 结 合 的 方 法 进行目标跟踪 。

Mean-Shift 算法作为一种高效的模式匹配 算 法 , 已经 被 成

过快时 , 仅使用该算法容易丢失目标 。

动 方 向 和 运 动 速 度 信 息 ,当 周 围 环 境 存 在 干 扰 、目 标 运 动 速 度

我们引入卡尔曼滤波器来解决这个问题 。 卡尔曼滤波是一 个对 动 态系 统 的 状态 序 列 进行 线 性 最小 方 差 估计 的 算 法 , 其 计 算 复 杂 度 低 ,能 够 较 为 准 确 地 对 目 标 的 运 动 位 置 、速 度 做 出 预

技 术 创 新

测 。 首 先 用 卡尔 曼 滤 波器 预 测 第帧 中 目 标 的 位 置 , 作 为 Mean-

Shift 算 法 中 搜 索 的 起 始 点 ,Mean-Shift 算 法 会 在 该 点 的 领 域 内

找到目标的最优位置 。 再以这个目标位置作为卡尔曼滤波器的 观测值 , 进行下一帧相应的迭代运算 。 对于跟踪中的运动目标, 需要以固定的时间间隔对摄像

摘要 : TI 达 芬 奇 芯 片 TMS320DM6446 是 一 款 功 能 强 大 的 嵌 入 式 多 媒 体 处 理 器 , 基 于 该 处 理 器 平 台 , 我 们 设 计 并 实 现 了 一 整 套 基 于 主 动 视 觉 的 运 动 目 标 检 测 、 跟 踪 与 H.264 编 码 算 法 。 实 验 结 果 表 明 , 该 套 算 法 具 有 较 好 的 检 测 跟 踪 精 度 与 压 缩 编 码 效 率 , 并 能 够 实 现 CIF 格 式 的 实 时 视 频 处 理 。 关键词 : 达芬奇 ; 智能视频监控 ; 目标检测 ; 目标跟踪 中图分类号 : TP391.4 文献标识码 : A

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

18

基于DaVinCi平台的软件开发流程

19

基于DaVinCi平台的软件开发流程

20

xDAIS和xDM算法接口标准

21

Video Acceleration Strategies

Time to Market

(C64+, StarCore, CEVA, Trimedia)

} } }

Codec

HDVICP

Fixed Kernel Functions Header Processing Codec Software

Multi-format support Multi-channel support for sub-HD video High-BW DMA access to MB-level processing buffers for codec expansion

} } }

}

eXpressDSP Configuration Kit TMS320DM644x SoC Analyzer MontaVista’s Linux

} }

Digital Video Evaluation Module TI third party development boards

10

14

目标应用

Trans Code

MPEG2 HD MPEG2 HD MPEG2 SD MPEG2 SD MPEG2 HD MPEG2 HD H.264 HD VC-1 HD H.264 SD VC-1 SD H.264 SD VC-1 SD

HD Decode

MPEG2 HD H.264 HD VC-1 HD

•Multiple DSP with programmable acceleration

m for •DSP+VICP per •DSP+HDVICP her ig H

•Higher Frequency DSPs with Prog. acceleration

•DSP

ly e, ful c rman perfo er High

Trans Rate

H.264 HD VC-1 HD H.264 HD VC-1 HD

SD Encode/Decode

MPEG2 SD H.264 SD VC-1 SD

15

VISA 的基本概念

16

使用 VISA 的优点

17

基于DaVinCi平台的软件开发流程

EDMA SS

PLL PLL CTRL

PLL PLL CTRL

ICEPick

PSC

JTAG

27 MHz

24 MHz

13

DM6467 vs. DM6446

v Addition to DM6447

New New New New New

v PCI (32bit and 33Mhz) v UHPI (16/32 bit mode) v Video Port v Video Data Conversion Engine (VDCE) v Transport Stream Interfaces (TSIF) v Clock Reference Generator (CRGEN) v 2 HDVICP – not covered here v 2 McASP v 3 UART

Algorithm-specific hardware accelerators Multi-format All fixed kernel functions accelerated All programmable functions in DSP High-BW DMA data exchange Full HD Decoding (all profile) 720p single-silicon encoding (baseline profile) Multi-silicon scalability Minimum processing delay variation Full API support Command-driven, no assembler needed Configurable via register control MB-level codec control

DVSDK工具链

}

eXpressDSP Configuration Kit } TI’s video, imaging, speech and audio codecs } Custom codecs that comply with TI’s eXpressDSP™ Digital } Media (xDM) algorithm standard } TI’s codec engine framework } DSP/BIOS™ real-time kernel } TI’s DSP/BIOS Link inter-processor communication } technology TMS320DM644x SoC Analyzer } system interaction } load distribution } bottlenecks in data throughput } other types of behavior

}

11

DVSDK工具链

DVEVM允许开发者为ARM编写即将投入 生产的应用程序代码和使用DaVinci API访问DSP内核,从而立即开始针对 DM6443和DM6446器件的应用开发。

12

DM6467 Block Diagram

PCI-32 (33MHz)

DSP

General Processor (Intel/ARM)

GP/DSP With Coprocessors

Energy Efficiency

Flexibility

Programmable Accelerators Reconfigurable Accelerators

(Stretch)

Hard-wired ASIC

e mabl ogram pr

23

HDVICP Overview

}

Architecture

} } } } }

Codec DSP

Fixed Kernel Functions Header Processing Codec Software Coding Parameter Controls

OR

ARM SS

ARM INTC ARM9 ICECrusher

DSP SS

C64x+ (594 MHz) L1 I-Cache L1 D-Cache 32K 32K L2 Cache 128K

UHPI-32

OR

SCR 150 MHz

ARM926-EJS (297 MHz) I-Cache D-Cache 16K 8K TCM RAM Boot ROM 32K 8K

}

Performance

} } } }

Codec

HDVICP

Fixed Kernel Functions Header Processing

}

Programming

} } } }

We Are Here

DSP

Codec Software Coding Parameter Controls

}

Scalability

HDVICP0 SS ARM968-ES (150/300 MHz) TCM RAM ME IPE MC LF CALC ECD HDVICP1 SS ARM968-ES (150/300 MHz) TCM RAM MC LF CALC ECD

GPIO McASP 1-channel McASP 4-channel I2C SPI PWM x2 Timer64 x3 UART x3 DDR2 PHY / DLL / IOs 300 MHz TSIF

Hale Waihona Puke v ARM (32KB RAM, 8KB ROM, 16KB I-Cache, and 8 KB D-Cache) vGEM (64KB L1P ROM, 32KB L2D, and 128KB L2) v SCR (297 Mhz VBUSM, 148.5 MHz VBUSP and CFG bus) v DDR2 (297 MHz) v 1Gbit Ethernet Mac v EDMA (4 TC)

(MPEG-2 Decoders)

22

System Cost Efficiency

Summary of TI Video Processing Past

ce, an

Today

her hig

icie eff

ncy

Future

•DSP+IVA-HD

•Improved DSP Core

DSP

Coding Parameter Controls

24

HDVICP Capability

(based(full 1080i) Decoding on DM6467 Implementation) HDTV

MPEG2 (MP) H.264 (BP) VC1 (AP), WMV9 720P@30 fps HD Encoding MPEG2 (MP) H.264 (BP) VC1 (AP), WMV H.263, MPEG-4 (SP/ASP) SDTV Simultaneous Encode/Decode MPEG2 (MP) H.264 (MP) VC1 (AP), WMV H.263, MPEG4 (SP/ASP) Transcoder MPEG2(MP@HL) à H.264 HP Level4, MPEG2(MP@HL) à H.264 MP Level3, MPEG2(MP@ML) ßà H.264 MP Level3, MPEG2(MP@ML) ß H.264 HP Level4,