【高级资料】数字电子技术基础第四版

合集下载

数字电子技术基础(第四版)阎石第4章

CP

CP S R Qn Qn1

0 t

0

0 1 1

X

X 0 0

X

X 0 0

0

1 0 1

0

1 0 1

RD

0 S 0 R 0 Q 0 t t

1

1 1 1 1 1

1

1 0 0 1 1

0

0 1 1 1 1

0

1 0 1 0 1

1

1 0 0 1* 1*

t

Q

0

t

在CLK

1期间,Q和Q可能随S、R潍坊学院 信息与控制工程学院 变化多次翻转

潍坊学院 信息与控制工程学院

《数字电子技术基础》第四版

主从SR触发器的 表4.2.4 特性表如表4.2.4所示, CP S R 和电平触发的SR触发 × × × 器相同,只是CP作用 0 0 的时间不同

0 0 0 1 0 1 1 0 0 1 1

Q × 0 1 0 1 0 1 0 1

Q* Q 0 1 0 0 1 1 1* 1*

0

1 1 1 0 0 0* 0*

S D和R D同时为0 Q ,Q同为 1

潍坊学院 信息与控制工程学院

《数字电子技术基础》第四版

4.2.2 同步RS触发器的电路结构与动作特点

在数字系统中,常常要求某些触发器在同一时刻动作,这 就要求有一个同步信号来控制,这个控制信号叫做时钟信号 (Clock pulse),简称时钟,用CP表示。这种受时钟控制的 触发器统称为时钟触发器。 一、电路结构与工作原理 图5.3.1所示为电平触发SR触发器(同步SR触发器)的基 本电路结构及图形符号。

潍坊学院 信息与控制工程学院

《数字电子技术基础》第四版

2. 主从 JK触发器 为解除约束 即使出现 S R 1的情况下, Q n 1也是确定的

CP S R Qn Qn1

0 t

0

0 1 1

X

X 0 0

X

X 0 0

0

1 0 1

0

1 0 1

RD

0 S 0 R 0 Q 0 t t

1

1 1 1 1 1

1

1 0 0 1 1

0

0 1 1 1 1

0

1 0 1 0 1

1

1 0 0 1* 1*

t

Q

0

t

在CLK

1期间,Q和Q可能随S、R潍坊学院 信息与控制工程学院 变化多次翻转

潍坊学院 信息与控制工程学院

《数字电子技术基础》第四版

主从SR触发器的 表4.2.4 特性表如表4.2.4所示, CP S R 和电平触发的SR触发 × × × 器相同,只是CP作用 0 0 的时间不同

0 0 0 1 0 1 1 0 0 1 1

Q × 0 1 0 1 0 1 0 1

Q* Q 0 1 0 0 1 1 1* 1*

0

1 1 1 0 0 0* 0*

S D和R D同时为0 Q ,Q同为 1

潍坊学院 信息与控制工程学院

《数字电子技术基础》第四版

4.2.2 同步RS触发器的电路结构与动作特点

在数字系统中,常常要求某些触发器在同一时刻动作,这 就要求有一个同步信号来控制,这个控制信号叫做时钟信号 (Clock pulse),简称时钟,用CP表示。这种受时钟控制的 触发器统称为时钟触发器。 一、电路结构与工作原理 图5.3.1所示为电平触发SR触发器(同步SR触发器)的基 本电路结构及图形符号。

潍坊学院 信息与控制工程学院

《数字电子技术基础》第四版

2. 主从 JK触发器 为解除约束 即使出现 S R 1的情况下, Q n 1也是确定的

数字电子技术基础(第四版)-第4章-组合逻辑电路解析

1

Y (Y1Y2Y3) ' (( AB) '(BC) '( AC) ') '

2

Y AB BC AC

9

最简与或 表达式

3

真值表

4

电路的逻 辑功能

Y AB BC AC

3

ABC 000 001 010 011 100 101 110 111

Y

当输入A、B、

0

C中有2个或3

第四章 组合逻辑电路

学习要点

了解组合逻辑电路的特点和工作原理。 掌握组合逻辑电路的分析、设计方法。 了解组合逻辑电路中的竞争冒险现象。

1

4.1 概 述

2

数字电路

组合逻辑电路:t时刻输出仅与t时刻 输入有关,与t以前的 状态无关。

时序逻辑电路:t时刻输出不仅与t时刻 输入有关,还与电路过 去的状态有关。

编码器:把指令或状态等转换为与其对应 的二进制信息代码的电路。

普通编码器 优先编码器

22

23

一、二进制编码器

设:编码器有M个输入,在这M个输入中, 只有一个输入为有效电平,其余M-1个输入 均为无效电平。有N个输出。则二者之间满 足M≤2N的关系。

二进制编码器——将一般信号编为二进制代 码的电路。

Y F( A)

5

组合电路的特点: 1. 输出仅由输入决定,与电路之前状态无关; 2. 电路结构中无反馈环路(无记忆); 3. 能用基本门构成,即任何组合逻辑电路都能

用三种基本门实现。

6

4.2 组合逻辑电路的 分析和设计

7

4.2.1 组合逻辑电路的分析

8

逻辑图 例1:

1

逻辑表 达式

《数字电子技术基础》(第四版)

CPLD结构特点

CPLD(复杂可编程逻辑器件)是一种基于乘积项的可编程逻辑器件,具有简单的结构和较快 的处理速度。它采用与或阵列(AND-OR Array)来实现逻辑功能,适用于中小规模的数字 电路设计。

FPGA与CPLD比较

FPGA和CPLD在结构、性能和适用场景上有所不同。FPGA具有更高的逻辑密度和更灵活 的可编程性,适用于大规模的数字电路设计和复杂的算法实现;而CPLD则具有更简单的 结构和更快的处理速度,适用于中小规模的数字电路设计和控制应用。

容量和提高存取速度

应用实例

如计算机的内存条就是采用RAM 存储器进行扩展的;而一些嵌入 式系统中则采用ROM存储器来

存储固件和程序代码等

发展趋势

随着科技的不断发展,存储器的 容量不断增大,存取速度不断提 高,功耗不断降低,未来存储器 将更加智能化、高效化和绿色化

05 可编程逻辑器件与EDA技 术

PLD可编程逻辑器件概述

要点一

PLD定义与分类

可编程逻辑器件(PLD)是一种通用集 成电路,用户可以通过编程来配置其逻 辑功能。根据结构和功能的不同,PLD 可分为PAL、GAL、CPLD、FPGA等类 型。

要点二

PLD基本结构

PLD的基本结构包括可编程逻辑单元 、可编程互连资源和可编程I/O单元 等。其中,可编程逻辑单元是实现逻 辑功能的基本单元,可编程互连资源 用于实现逻辑单元之间的连接,可编 程I/O单元则负责与外部电路的连接 。

逻辑代数法

利用逻辑代数化简和变换电路 表达式

图形化简法

利用卡诺图化简电路

பைடு நூலகம்

状态转换表

列出电路的状态转换过程,便 于分析和理解电路功能

状态转换图

以图形方式表示电路的状态转 换过程,直观易懂

CPLD(复杂可编程逻辑器件)是一种基于乘积项的可编程逻辑器件,具有简单的结构和较快 的处理速度。它采用与或阵列(AND-OR Array)来实现逻辑功能,适用于中小规模的数字 电路设计。

FPGA与CPLD比较

FPGA和CPLD在结构、性能和适用场景上有所不同。FPGA具有更高的逻辑密度和更灵活 的可编程性,适用于大规模的数字电路设计和复杂的算法实现;而CPLD则具有更简单的 结构和更快的处理速度,适用于中小规模的数字电路设计和控制应用。

容量和提高存取速度

应用实例

如计算机的内存条就是采用RAM 存储器进行扩展的;而一些嵌入 式系统中则采用ROM存储器来

存储固件和程序代码等

发展趋势

随着科技的不断发展,存储器的 容量不断增大,存取速度不断提 高,功耗不断降低,未来存储器 将更加智能化、高效化和绿色化

05 可编程逻辑器件与EDA技 术

PLD可编程逻辑器件概述

要点一

PLD定义与分类

可编程逻辑器件(PLD)是一种通用集 成电路,用户可以通过编程来配置其逻 辑功能。根据结构和功能的不同,PLD 可分为PAL、GAL、CPLD、FPGA等类 型。

要点二

PLD基本结构

PLD的基本结构包括可编程逻辑单元 、可编程互连资源和可编程I/O单元 等。其中,可编程逻辑单元是实现逻 辑功能的基本单元,可编程互连资源 用于实现逻辑单元之间的连接,可编 程I/O单元则负责与外部电路的连接 。

逻辑代数法

利用逻辑代数化简和变换电路 表达式

图形化简法

利用卡诺图化简电路

பைடு நூலகம்

状态转换表

列出电路的状态转换过程,便 于分析和理解电路功能

状态转换图

以图形方式表示电路的状态转 换过程,直观易懂

数字电子技术基础 第4版 第6章 半导体存储器和可编程逻辑器件

《数字电子技术基础(第4版)》教学课件

3. 片选和读/写控制电路

若在RAM的端加低电平,则该RAM就被选中,可以读/写操作,否则该RAM不工作,相 当于与存储系统隔离。RAM被选中后,是读是写,由读/写R/来控制。

图6-3 一种RAM的片选和读/写控制电路

第6章半导体存储器和可编程逻辑பைடு நூலகம்件

6.2.2 RAM的存储单元

场合;而MOS存储器具有集成度高、功耗小、价格低的特点,主要用于大容 量存储系统。

第6章半导体存储器和可编程逻辑器件

《数字电子技术基础(第4版)》教学课件

2. 按照存取功能分为ROM和RAM ROM在正常工作时,只能从中读取数据,而不能写入数据,故属于数

据非易失存储器。分为掩模式ROM、可编程ROM、可擦除可编程ROM等 几种类型。

当位线处于高电平期间,如果地址译码器输出XI和YJ 同时为1,则门控管V3、V4、V7、 V8均导通,此时内部所存数据被读出。例如,设存储单元为0状态,即V1管导通、V2管截止, 位线电容CB将通过V3、V1管放电,使位线B 变为低电平。同时因V2管截止,故位线仍保持高 电平。这样就把存储单元的0状态读到B和上。由于此时V7、V8管也导通,所以位线B和的数 据上了数据线D和。

由于存储器位线上连接的存储单元数目很多,使CB远大于 CS,所以位线上读出的电压信号幅度很小,且读出操作过后, 因为电荷的损失,所以CS上的电压很低。在DRAM中设有灵敏 再生放大器,一方面将读出信号放大,另一方面在每次读出后,

1. 静态存储器(SRAM)的存储单元

《数字电子技术基础(第4版)》教学课件

图6-4 6管CMOS存储单元的电路图

第6章半导体存储器和可编程逻辑器件

数字电子技术基础(第四版)阎石第2章

自由电子和空穴使本征半导体具有导电能力,但很微弱。 潍坊学院 信息与控制工程学院

《数字电子技术基础》第四版 数字电子技术基础》

半导体基础知识(2 半导体基础知识(2)

• 杂质半导体 • N型半导体 多子:自由电子 少子:空穴

潍坊学院 信息与控制工程学院

《数字电子技术基础》第四版 数字电子技术基础》

潍坊学院 信息与控制工程学院

《数字电子技术基础》第四版 数字电子技术基础》

以NPN为例说明工作原理: NPN为例说明工作原理: • 当VCC >>VBB • be 正偏, bc 反偏 正偏,

IE=ICN + IBN + IEP=IEN+ IEP IC = ICN + ICBO IB=IEP+ IBN-ICBO

• 2.2.2 半导体三极管的开关特性

(参考清华大学童诗白版模拟电子第四版—1.3、1.4) 参考清华大学童诗白版模拟电子第四版 、 )

潍坊学院 信息与控制工程学院

《数字电子技术基础》第四版 数字电子技术基础》

2.2.1 半导体二极管的结构和外特性 (Diode) Diode) • 二极管的结构: PN结 + 引线 + 封装构成 PN结

潍坊学院 信息与控制工程学院

《数字电子技术基础》第四版 数字电子技术基础》

半导体基础知识(3 半导体基础知识(3)

• PN结的形成 PN结的形成

• • • • • 电子和空穴浓度差形成多数载流子 电子和空穴浓度差形成 多数载流子 的扩散运动。 的扩散运动。 扩散运动形成空间电荷区—— PN 扩散运动形成空间电荷区 耗尽层。 结,耗尽层。 空间电荷区正负离子之间电位差 Uho —— 电位壁垒; 电位壁垒; —— 内电场;内电场阻止多子的扩 内电场; 散 —— 阻挡层。 阻挡层。 内电场有利于少子运动—漂移 漂移。 内电场有利于少子运动 漂移。

数字电子技术基础第四版

《数字电子技术基础》第四版

《数字电子技术基础》(第四版)教学课件 辽宁石油化工大学 杨冶杰

联系地址:辽宁石油化工大学电工电子教学系 邮政编码:113001 电子信箱:syuckso@ 联系电话:(0413)6865171

辽宁石油化工大学 电工电子教学系

《数字电子技术基础》第四版

第一章 逻辑代数基础

AB+AC+BC=AB+AC A B + A C + B CD = A B + A C

A AB = A B; A AB = A

辽宁石油化工大学 电工电子教学系

1.4 逻辑代数的基本定理

《数字电子技术基础》第四版

• 1.4.1 代入定理

------在任何一个包含A的逻辑等式中,若 以另外一个逻辑式代入式中A的位置,则等 式依然成立。

辽宁石油化工大学 电工电子教学系

《数字电子技术基础》第四版

辽宁石油化工大学 电工电子教学系

《数字电子技术基础》第四版

• 卡诺图

• EDA中的描述方式 HDL (Hardware Description Language)

VHDL (Very High Speed Integrated Circuit …) Verilog HDL

《数字电子技术基础》第四版

• 7–4=3 • 7 + 8 = 3 (舍弃进位) • 4 + 8 = 12 产生进位的模 • 8是-4对模数12的补码

辽宁石油化工大学 电工电子教学系

• 1110 – 0110 = 1000 (14 - 6 = 8)

• 1110 + 1010 = 11000 =1000(舍弃进位)

Y1 Y2 …. 输出对应的取值

《数字电子技术基础》(第四版)教学课件 辽宁石油化工大学 杨冶杰

联系地址:辽宁石油化工大学电工电子教学系 邮政编码:113001 电子信箱:syuckso@ 联系电话:(0413)6865171

辽宁石油化工大学 电工电子教学系

《数字电子技术基础》第四版

第一章 逻辑代数基础

AB+AC+BC=AB+AC A B + A C + B CD = A B + A C

A AB = A B; A AB = A

辽宁石油化工大学 电工电子教学系

1.4 逻辑代数的基本定理

《数字电子技术基础》第四版

• 1.4.1 代入定理

------在任何一个包含A的逻辑等式中,若 以另外一个逻辑式代入式中A的位置,则等 式依然成立。

辽宁石油化工大学 电工电子教学系

《数字电子技术基础》第四版

辽宁石油化工大学 电工电子教学系

《数字电子技术基础》第四版

• 卡诺图

• EDA中的描述方式 HDL (Hardware Description Language)

VHDL (Very High Speed Integrated Circuit …) Verilog HDL

《数字电子技术基础》第四版

• 7–4=3 • 7 + 8 = 3 (舍弃进位) • 4 + 8 = 12 产生进位的模 • 8是-4对模数12的补码

辽宁石油化工大学 电工电子教学系

• 1110 – 0110 = 1000 (14 - 6 = 8)

• 1110 + 1010 = 11000 =1000(舍弃进位)

Y1 Y2 …. 输出对应的取值

教材情况数字电子技术基础第四版清华大学电子学教研组编阎石(精)

嘉应学院电子信息工程系

二、其他常用逻辑运算 1.与非 ——由与运算和非运算组合而成。口诀:全1出0,有0出1

A 0 B 0 L=A· B 1

第 & A 0 1 1 L=A· B 一 B 1 0 1 章 1 1 0 逻 (b) (a) 辑 代 2.或非 ——由或运算和非运算组合而成。口诀:有1出0,全0出1 数 A B L=A+B 基 0 0 1 础 ≥1 A 0 1 0

嘉应学院电子信息工程系

2.十进制转换成二进制 例1.2.2 将十进制数23转换成二进制数。 解:(整数部分)用“除2取余”法转换:(原理:书中1.1.6式)

第 一 章 逻 辑 代 数 基 础

2 23 2 11 2 5 2 2 2 1 0

………余1 ………余1 ………余1 ………余0 ………余1

b0 b1 b2 b3 b4 读 取 次 序

一章交一次作业,作业是平时成绩的主要依据。

嘉应学院电子信息工程系

第一章 逻辑代数基础

1.1 概述 1.2 逻辑代数中的三种基本运算 1.3 逻辑代数的三种基本公式和常用公式

第 一 章 逻 辑 代 数 基 础

1.4 逻辑代数的基本定理

1.5 逻辑函数及其表示方法

1.6 逻辑函数的公式化简法

1.7 逻辑函数的卡诺图化简法

嘉应学院电子信息工程系

下图所示为三个周期相同(T=20ms),但幅度、脉冲宽度及占空 比各不相同的数字信号。

V (V) 5

第 一 章 逻 辑 代 数 基 础

(a) 0 t (ms)

10 V (V)

20

30

40

50

(b)

3.6

0 10 (c)

10 V (V)

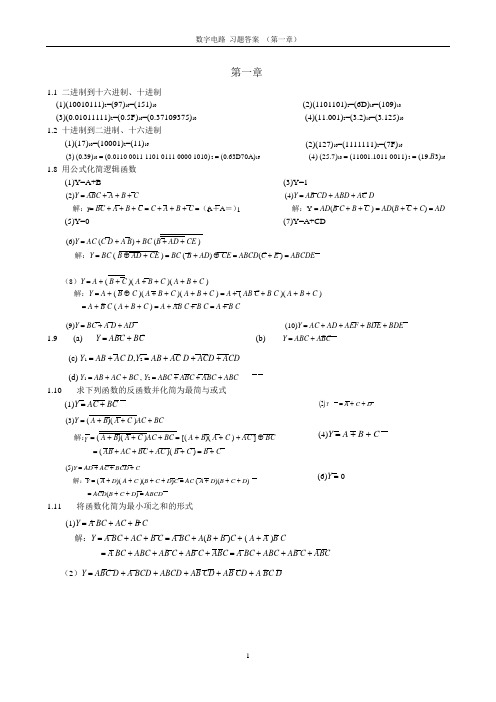

数字电子技术基础. 第四版. 课后习题答案详解

1.8用公式化简逻辑函数

(1)Y=A+B

(2)YABCABC

解:BCABCCABC(A+A=)

(5)Y=0

(2)(1101101)2=(6D)16=(109)10

(4)(11.001)2=(3.2)16=(3.125)10

(2)(127)10=(1111111)2=(7F)16

(4) (25.7)10(11001.1011 0011)2(19.B3)16

1.12

将下列各函数式化为最大项之积的形式

(1)Y(ABC)(ABC)(ABC)

(3)YM0⋅M3⋅M4⋅M6⋅M7

(5)YM0⋅M3⋅M5

(2)Y(ABC)(ABC)(ABC)

(4)YM0⋅M4⋅M6⋅M9⋅M12⋅M13

1.13

用卡诺图化简法将下列函数化为最简与或形式:

(3)Y(AB)(AC)ACBC

(2)Y

ACD

解:(AB)(AC)ACBC[(AB)(AC)AC]⋅BC

(ABACBCAC)(BC)BC

(5)YADACBCDC

解:Y(AD)(AC)(BCD)CAC(AD)(BCD)

ACD(BCD)ABCD

(4)YABC

(6)Y0

1.11

将函数化简为最小项之和的形式

(3)Y=1

(4)YAB CDABDAC D

解:YAD(B CBC)AD(BCC)AD

(7)Y=A+CD

(6)YAC(C DA B)BC(BADCE)

解:YBC(B⋅ADCE)BC(BAD)⋅CEABCD(CE)ABCDE

(8)YA(BC)(ABC)(ABC)

解:YA(B⋅C)(ABC)(ABC)A(AB CB C)(ABC)

(1)Y=A+B

(2)YABCABC

解:BCABCCABC(A+A=)

(5)Y=0

(2)(1101101)2=(6D)16=(109)10

(4)(11.001)2=(3.2)16=(3.125)10

(2)(127)10=(1111111)2=(7F)16

(4) (25.7)10(11001.1011 0011)2(19.B3)16

1.12

将下列各函数式化为最大项之积的形式

(1)Y(ABC)(ABC)(ABC)

(3)YM0⋅M3⋅M4⋅M6⋅M7

(5)YM0⋅M3⋅M5

(2)Y(ABC)(ABC)(ABC)

(4)YM0⋅M4⋅M6⋅M9⋅M12⋅M13

1.13

用卡诺图化简法将下列函数化为最简与或形式:

(3)Y(AB)(AC)ACBC

(2)Y

ACD

解:(AB)(AC)ACBC[(AB)(AC)AC]⋅BC

(ABACBCAC)(BC)BC

(5)YADACBCDC

解:Y(AD)(AC)(BCD)CAC(AD)(BCD)

ACD(BCD)ABCD

(4)YABC

(6)Y0

1.11

将函数化简为最小项之和的形式

(3)Y=1

(4)YAB CDABDAC D

解:YAD(B CBC)AD(BCC)AD

(7)Y=A+CD

(6)YAC(C DA B)BC(BADCE)

解:YBC(B⋅ADCE)BC(BAD)⋅CEABCD(CE)ABCDE

(8)YA(BC)(ABC)(ABC)

解:YA(B⋅C)(ABC)(ABC)A(AB CB C)(ABC)