xilinx平台DDR3设计教程之综合篇_中文版教程

FPGA综合详细教程

4. Xilinx专用参数选项

(3)寄存器复制(Register Duplication) Register Duplication参数仅对FPGA有效,用于指定 是否允许进行寄存器复制(Register Duplication)。

2.XST综合属性

(3)综合约束文件(Synthesis Constraint File) Synthesis Constraint File 用于指定综合约束文件的 所在路径。 (4)使用综合约束文件(Use Synthesis Constraint File) 如果设计中有综合约束文件,那么在指定综合约 束文件的所在路径后在此参数后打上勾,使XST在综 合时受到综合约束文件的约束。

(4)等效寄存器删除(Equivalent Register Removal) Equivalent Register Removal参数用于指定是否把寄 存器传输级功能相等的寄存器删除,以减少资源占 用。

4. Xilinx专用参数选项

(5)寄存器配平(Register Balancing) Register Balancing参数仅对FPGA有效,用于指 定是否需要寄存器配平。寄存器配平是使较长路径 缩短,较短路径加长,使其达到平衡从而提高工作 频率的一种技术。

XST的综合约束文件是XCF(XST Constrain File),

5.1.1 XST的综合属性

XST是内嵌在ISE中的,使用起来也非常方便。XST 综合是自动完成的,但是用户可以对其相关的参数进 行设置。参数设置的目的是使 XST根据设计者的需要 完成综合过程,以便达到设计要求。

Xilinx fpga 设计培训中文教程-10_1

在当前源文件进程窗口 点击靠近实现设计进程的 + 以展开该进程 展开布局布线进程 展开生成布局布线后静态时序报告进程 双击布局布线后静态时序报告

图 10b-1. 布局布线后静-XLX-CLAS

Ch.10b-4

? 1. 多少路径约束是失败的 时序错误的数目 本实现的时序积分是多少

图 10b-6. 端口选项卡

实现选项实验

1-877-XLX-CLAS

Ch.10b-8

点击 I/O 配置选项选择框. 一些附加的列将出现在窗口的上部 你也许需要将它们向 右翻以便查看

确定信号名称按照字母顺序排列 如果不是 点击端口名称方框以将这些信号名称按 字母排序

向下翻并点击 rd_data<0>

在当前源文件进程窗口 右击布局布线 Place & Route 性 Properties (图 10b-2)

然后从菜单中选择属

图 10b-2. 当前源文件进程窗口

在进程属性对话框中 点击靠近布局布线尝试级别的方框 一个箭头将出现在方框的 右边 指示着下拉的一系列选项

实现选项实验

1-877-XLX-CLAS

过程

你可以利用给定的约束文件(myucf.ucf)及缺省的软件选项来开始实现一个项目 然后你 可以通过调整进程属性和 I/O 配置选项来改进设计性能 注意 当使用 Toolwire 执行本实验时 所有的软件程序 文件以及项目都放在卷标 U:\ 下面而不是 C:\下面

实现选项实验

1-877-XLX-CLAS

欲退出时序分析器 可以选择下列方法中的一个 选择文件 File → 退出 Exit , 并点击出现的弹出式对话框中的 Yes 点击时序分析器窗口右上角的 X 并点击出现的弹出式对话框中的 Yes

Xilinx FPGA 中文手册-《Platform Flash PROM User Guide》中文版

《Platform Flash PROM User Guide》中文版FPGA的配置分为主串行和从串行两种,差别在于时钟源不同。

nCF为高时PROM的DO数据有效,nCE和OE使能。

P24和26介绍了接线图和引脚功能。

原型开发优势每写一次可以有4套不同的程序进行测试。

板子测试配置或安全升级设计的版本中写有诊断程序,如果发现原程序不满足要求,可以调用符合要求的程序重新执行,节省了调试时间。

PlatForm具有备份程序的功能。

防止不完整或损坏数据FPGA的所有IO口在DONE为低电平时均不可用,PlatForm满足这个要求。

为什么使用内部解压或晶振Platform PROM片上解压使得用户可以多存储50%的数据。

Platform PROM提供20MHz或者40MHz(默认)的时钟用于将配置数据从PROM送入FPGA。

内部晶振,特别是40MHz的操作只应用于解压模式。

否则,FPGA的CCLK或者外部晶振会用于驱动。

PROM的解压输出数据速率为内部时钟的一半,换言之,解压数据流配置时间是非压缩数据流的两倍。

如果需要快速配置,FPGA的BitGen-g compress方式可以作为压缩模式。

时钟CLKOUT信号在配置过程中,且在nCE低、OE/nRESET高时有效;无效时呈高组态并且需要外部上拉以避免不确定状态。

时钟速率可以配置,默认为1MHz,可以为1,3,6,12等,XCFxxS最大为33MHz。

PROM文件生成和烧写.bit(Bitstream)文件为输入数据流,.mcs文件为输出数据,.cfi文件为配置格式信息文件。

.bit文件为FPGA使用的二进制数据,.mcs文件为PROM运行文件,.cfi(Configuration format information)文件名字与前两者根目录相同。

标准的PROM文件为前两者。

在XCFxxP系列PROM使用多版本程序设计、CLKOUT、解压缩等功能时还需要使用.cfi文件。

xilinx使用步骤

Xilinx软件使用步骤目录基本操作1. 打开xilinx2. open project3. New project4. 创建新的 .vhd文件5. 建立波形文件6. 综合7. 仿真8. 下载程序到电路板中需要注意的问题1.生成顶层原理图2.建立.ucf文件3. implement时出错的原因4.仿真时的问题基本操作1. 打开xilinx图1 打开xilinx界面2. open project图2 open project图3 查找要打开的.ise文件单击打开后,出现在左侧box中。

图4 open project3. New project顶层文件类型,原理图类型选Schematic,否则选择HDL;单击下一步,通过右侧value各项目,配置器件类型,即FPGA 型号。

注意:此处配置错误的话,综合时会出现放不下或者些不进去的错误。

配置完成后,单击下一步,出现创建源文件对话框如下图所示。

不需做设置更改,直接点击下一步,出现添加现有源对话框如下图所示。

不需做任何设置,直接单击下一步,出现New project information对话框,如下图所示。

确认信息无误后,单击完成,创建的新的project即出现在主页面左侧Sources in project中,如下图所示。

4. 创建新的 .vhd文件右击主页面左侧Sources in project中xc2s200-5pq208,在右键菜单中选择New source,如下图所示;出现New source对话框;左侧选择VHDL Module,右侧输入文件名,如下图所示,单击下一步;出现define vhdl source对话框,输入端口名,输入输出类型和MSB,LSB, 如下图所示,然后单击下一步,出现信息对话框,如下图所示,确认无误后,单击完成。

然后主页面如下图所示:5. 建立波形文件在主页面,编程之后保存。

在如下图所示位置右击.vhd文件,选择new source选项。

精品课件-Xilinx FPGA设计基础-第3章

实体中所有的端口信号都要在“port();”语句的括号内 声明。端口的声明包含三个部分:端口名称、端口模式和数据 类型。相同端口模式和数据类型的端口信号可以作为一组信号 联合声明,信号之间用逗号“,”隔开,不同组的信号声明之 间用分号“;”隔开,但是要注意声明最后一组信号后不需要 再加分号,端口声明的结构如下:

第3章 VHDL硬件描述语言

3.3.1 实体 设计一个模块,首先要给模块起一个名字作为这个模块的

标识,称为实体名称。这个名字通常与模块的功能有密切关系, 例如2.2节实验中的AND_OR。

模块命名后,就要确定这个模块的外部接口参数,即模块 有哪些输入信号,有哪些输出信号,信号的名称和类型是什么, 在确定了这些参数之后,我们就完成了对实体的描述。

第3章 VHDL硬件描述语言

1.端口名称 一般一个模块实体包含不止一个端口,为了区别不同的端 口,给端口命名时通常不会采用上面例子中的方式,而会将端 口的含义包含在名称中。例如,常用的端口名称“clk”表示 时钟信号等。 2.端口模式 端口模式用于定义模块端口的数据传输模式。VHDL的端 口模式有五种,如表3.1所示。

第3章 VHDL硬件描述语言

VHDL只是给工程师提供了一个描述规范,用这种规范进 行描述可以使众多工程师之间传递信息更加简洁、准确。学习 VHDL就是学习如何利用这些规范进行描述,因此,我们在学 习VHDL之前,要在思维中假想一个现成的芯片,学习的过程 中,对照芯片不断完善对芯片的描述。

VHDL不仅可以对芯片的接口和行为参数做详尽的描述, 而且可以作为一门编程语言对可编程逻辑器件进行编程配置。 目前,可编程逻辑器件的EDA工具都支持以VHDL代码作为工程 设计的输入。

xilinx V6 DDR3调试成功经验分享

DDR3 调试DDR3配置:时钟输入400M ,芯片V6 lx240t -2 ff1156 ,突发模式为BL=8,长度为64。

仿真:新建工程,添加用xilinx 生成DDR3核的sim_tb_top 等文件。

进行仿真。

traffic_gen 是xilinx 自带的一个测试DDR 的模块随机的读写DDR ,然后校验读取和写入的数值是不是一样。

如果有错,会拉高tg_compare_error 来报警。

而我们要做的就是自己看懂traffic_gen 向DDR 模块发送的时序,然后去重新编写一个模块来代替traffic_gen 。

traffic_gen 写数据时序图:traffic_gen 读数据时序图:设计读写模块:由于需要代替traffic_gen 模块,所以需要设计数据发送模块(cad_gen_1),命令时序模块(cad_gen_2)和数据校验模块(data_compare ),另外增加异步读写FIFO 来保证读写稳定不出错。

系统模块间信号连接图如下:Example_topDDR3_COREwr_fifoCad_gen_1Wr_endindout Cad_gen_2App_en App_wdf_wren App_wdf_end App_cmdApp_addrPhy_init_done App_rdy App_wdf_rdyRd_enrd_fifodin Wr_enRd_enData_co mparedataRd_en子模块功能cad_gen_1模块负责产要写入DDR3的数据。

先将数据存入写FIFO中。

cad_gen_2模块负责产生命令(app_com),地址(app_addr),控制器写数据有效使能(app_en),写数据使能(app_wdf_wren),写数据结束信号(app_wdf_end)。

data_compare模块负责将从的DDR3核中读出的数据与写入的数据相比较。

从而得出误码率。

子模块接口Cad_gen_1模块信号位宽方向描述Clk 1 Input 外部时钟rst 1 input 复位信号app_rdy 1 Input 由DDR3核输出的核ready信号app_wdf_rdy 1 Input 由DDR3核输出的接收数据ready信号phy_init_done 1 Input 核初始化成功时置1,只有初始化完成以后才能进行相应的读写操作。

xilinx平台DDR3设计教程之设计篇_中文版教程3

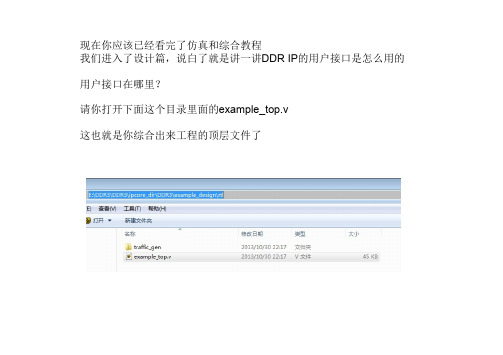

现在你应该已经看完了仿真和综合教程我们进入了设计篇,说白了就是讲一讲DDR IP的用户接口是怎么用的用户接口在哪里?请你打开下面这个目录里面的example_top.v这也就是你综合出来工程的顶层文件了我们来理一理这个文件的结构吧开头部分,全是介绍,你删了都关系然后是各种参数的设定这里有bank,row,column,rank,等等各种设置其实你不用动它们这些都是你之前选条子的时候已经选好了的不记得自己选什么条子了?乖乖,你不如再翻翻仿真教程先?各种仿真延迟参数也跟你选的条子有关你也别管了我都不管这些和DDR条子的各种接口你要知道,用户接口是个内部接口,你这里当然看不到了。

如果之前选了“use system clock”的话这里就看不到clk_ref相关的参考时钟管脚了。

这里顺便提一下column和row地址是在ddr3_addr里面复用的。

column一般是10bit宽度。

row一般14-16bit宽度。

ddr3_ba是选bank的,一般是3bit宽度,对应8个bank。

ddr3_cs_n是选rank的,有几个rank就有几个bit的宽度,因为要考虑啥都不选的情况,和之前几个参数不一样的。

各种参数配置相互之间的关系换算,选择继续和你没有关系作为设计者的你,可以继续无视这些部分各种wire定义你有兴趣研究不?我是没兴趣终于开始实例化DDR3了看见DDR3 右边的#号了没?这说明下面这些都不是管脚,而是配置用的参数。

你继续不用改这都六百多行了,你还是啥也不用改。

唉呀妈呀,DDR3实例化的实体总算找到了,就叫做u_DDR3找到没,我这里是747行接下来你要改动的,其实只有区区几行那就是769行Application interface开始的几个ports从770行的app_addr开始到775行的app_wdf_wren结束一共六行此外,因为你之前选了data mask,所以790行有个app_wdf_mask这一行的赋值你可以直接改成零。

Xilinxfpga设计培训中文教程7.pdf

解答

• 如果箭头涵盖的部分是约束的路径 那么在此电路中路径终点 是什么 是否所有的寄存器都有相同点

– 路径终点是触发器

– 触发器的时钟都为同一个信号 以此网络为参考的约束将会约束 在此设计中的所有寄存器之间的时延路径

ADATA

CLK BUFG

FLOP1 DQ

– 这个设计的最高系统时钟频 率为50 MHz

全局时序约束 - 7-6

© 2002 Xilinx公司版权所有

有时序约束的情况

• 同一个设计 只是用约束编 辑器输入了三个全局时序约 束

• 最高系统时钟频率达60 MHz • 注意一下 大部分的逻辑都

离器件中分配了管脚的那一 侧更近

全局时序约束 - 7-7

© 2002 Xilinx公司版权所有

更多关于时序约束

• 时序约束应该被用来定义你的性能目标

– 加较紧的时序约束会增加编译的时间 – 加不现实的约束会导致实现工具停止运行 – 在布局布线前 利用综合工具的时序估计能力或映射后静态时

序报告 以确定你的时序约束是否现实 参见“获取时序逼近I” 模块

全局时序约束 - 7-8

全局时序约束

© 2002 Xilinx公司版权所有

目标

完成此模块的学习后 你将会 • 为一个简单的同步设计加全局时序约束 • 用约束编辑器加全局时序约束和管脚配置

全局时序约束 - 7-3

© 2002 Xilinx公司版权所有

概览

• 简介 • 周期约束与管脚-到-

管脚约束 • 偏置 OFFSET 约束 • 约束编辑器 • 总结

全局时序约束 - 7-4

© 2002 Xilinx公司版权所有

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

你已经看过我写的仿真教程,并且按照步骤都做成功了吧?

现在要做综合?来个一图流就行了——看明白了吗?编译已经成功,bit文件生成了。

什么?没看明白?下面分开讲吧~

之前仿真教程里面讲过过traffic_gen,现在派用场了

看这个工程里面的顶层文件,不是我写的

其实这工程里面所有的文件都不是我写的

只要你生成好了IP core,管脚分配好(你也可以让core gen自动分配,用默认值就行,还是参见仿真教程)

你要做的事,就是这么区区几步:

1,建立一个ISE工程,FPGA型号和封装选对就可以了

2,加入example_design/rtl下面的 example_top.v 以及其他所有.v文件

(什么,你写VHDL的?乖乖,不知道现在写VHDL的很难找工作?)

3,加入user_design/rtl下面的rtl下面的所有.v文件

4,加入example_design/par 下面的example_top.ucf文件

然后你就开始跑编译吧~

文件全部加完了之后就是这样的,都是绝对路径显示

多展开几级,来个壮观点儿的

其实就是把这两个目录下的*.v都加进去,最后别忘了加上example_design/par 下面的example_top.ucf文件,就可以了

只要你在core gen的时候分配好了管脚,就不可能编译不成功。

这张图还记得吗?

万一做板子的人把按键和LED灯的管脚给你分配到了这里不能选的地方,你就得留意下一页的内容了。

/support/documentation/ip_documentation/mig_7series/v1_5/ug586_7Series_MIS.pdf 在上面这个文档,也就是xilinx MIG的用户手册里面的132页,

有这么一段:

管脚电平可以用planAhead来设置。

推荐你综合完了之后用post-synthesis(综合后)的选项来重设管脚属性,

这个比pre-synthesis(综合前)有说服力,行不行还是得看你综合完了之后不是?

但是实际上你打开了之后会发现不是那么回事儿

这为啥LVCMOS都是2.5V,SSTL都是1.35V,编译也通过了?

可能待会儿上电了下载还正常跑。

那我告诉你,这个例子里SSTL都是1.35V,跟core gen的时候选的sodimm条子款式有关,有些条子就是1.35V的,比如我这里选的这根儿就是。

电压或许可以和1.5V有所区别,但是SSTL和LVCMOS的区别不能搞混,否则可能map不过去。

SSTL和LVCMOS有啥区别的呢

SSTL是针对DDR之类的高速管脚的电平

LVCMOS就是常用的默认电平

只要知道,DDR的高速打数据,尤其是双沿动作的管脚,都得是SSTL 的电平;而按键指示灯之类的慢速控制管脚,应该是lvcmos电平,就可以了。

如果你在planAhead里面选择好管脚属性保存之后没有立即提示错误,也不代表你后面map和par就能通过。

DDR设计的原则之一就是,别去改哪些你想当然认为肯定没事的东西。

先全部用默认值生成一个DDR工程,编译通过,保存好,然后再在这个工程里改动。

在编译出问题的时候,仔细核对你改动的部分和原先的初始工程有什么区别,项目才能比较顺利的做下去。

最后大致讲一下traffic gen

这个貌似DDR2里面没有

只有DDR3有

功能之前讲过了,就是写数据进DDR,读出来看和写进去的是不是一致,不一致的话就报错,拉高tg_compare_error

很不幸的是,这东西虽然用了DDR core用户接口,但是代码写得基本没有通用性,你不可能在这个基础上修改修改就拿来自己用。

所以要做DDR设计,你得自己重新写一个控制DDR用户接口的代码。

最典型的例子就是从一个fifo里面读数据,然后写进DDR

这个例子我之后再讲了。

现在,先动手建一个工程吧。

在ISE14.2和以上版本,可以直接进example_design\par文件夹,

运行create_ise.bat,然后工程会自动生成。

其实这个过程和你手动建立工程是一样一样的,聊胜于无吧,嘿嘿~。