基于DSP_FPGA的高速数字信号处理平台

基于FPGA+DSP的高速基带信号处理平台的设计

第 3期

ห้องสมุดไป่ตู้

2 0 1 4年 1月

科

学

技

术

与

工

程

Vo 1 . 1 4 N o . 3 J a n .2 0 1 4

1 6 7 1 —1 8 1 5 ( 2 0 1 4 ) 0 3 — 0 2 3 9 — 0 5

S c i e n c e T e c h n o l o g y a n d E n g i n e e r i n g

出 了一种改进高速基 带信号处理平 台的硬件 设计方 案。该 方案采 用 F P G A+D S P的处理 架构 , 依托 高性 能 的器 件和 高速接 口, 搭建 了一个高性 能的通用 基带信号处理平 台。该平 台直接实现对 中频数 字信号 的处 理 , 融合数 字上 下变频 与基 带算法于

一

的处理器 , 其优势在于 : ①充分结合了 D S P和 F P G A 各 自的优点 , 更好地发挥 了性能 ; ②结构灵活、 通用 性强 、 适用 于模块化设计 ; ③对不同结构的算法都有 较强 的适应能力 , 尤其适合实时信号处理; ④算法执 行效 率高 、 开 发周 期短 、 系 统易 于维 护和 扩展 等 。 结合各类无线通信 系统实际算 法需求 , 低层信 号预处理算法的数据 为符号级数据 , 虽然数据量大 但运 算结 构 相对 比较 简单 , 适 于用 F P G A 进 行 硬 件 实现。高层处理算法的数据 为比特型数据 , 其特点

一

是数据量较少 , 但算法的控制结构复杂 , 适于用 D S P 来 实 现 。F P G A 具 有 明 显 的 并 行 处 理 优 势 和 灵 活 性, D S P运算 速度 快 、 寻址 方 式 灵 活 , 二 者 均 能 满 足 处 理 复 杂算 法 的要 求 , 这样以 F P G A +D S P的架 构 为核 心 , 借 助 于高性 能 的器件 和高 速接 口 , 设计 了一 个 高性 能 信 号 处 理 硬 件 平 台 J 。该 平 台具 有 灵 活 的处理 结构 , 对 不 同结 构 的算 法都 有 较 强 的适 应 能 力, 尤其适合实时信号的处理。

基于DSP和FPGA的数字信号处理系统设计

Vo 1 . 31 N o .1

J a n .2 O l 7

文 章 编 号 :2 0 9 5 — 6 9 9 1 ( 2 0 1 7 ) 0 1 ~ 0 0 6 5 — 0 3

基 于 DS P和 F P GA 的 数 字 信 号 处 理 系统 设 计

宋 劲松 , 杨 凯 。

( 1 . 宿 州 市 广 播 电视 台 , 安徽 宿州 2 3 4 0 0 0 ; 2 . 宿州 学 院 信 息工 程 学 院 , 安徽 宿州 2 3 4 0 0 0 )

变大 , 严 重 影 响了 电子设 备 的有效 运行 . 目前 , F P GA 和 DS P在 市 场上 广 泛用 于 高 速 处 理 器件 口 ] . F P GA 具 有 高 度 并行 体 系结 构 、 高 数 据率 以及 处 理 时 间可 控 等 优 点 , 但 其 不 能 实 现 很 复 杂 的算 法 . 而 DS P处 理 能 力 强 , 能 够 实 现 算

F P G A 的数字信号处理系统. 首先 设 计 了 系 统 的 总 体 结 构 和 工 作 流 程 , 然后对 系统 的主要硬 件 D S P和 F P GA 进 行 了设 计 , 最 后 设 计 了 系统 的软 件 部 分 . 经过测试 , 本系统能够正常工作 , 具 有较 好 的 信 号 处 理 能 力 . 关键词 : 数字信号处理 ; DS P ; F P GA

图 2 系 统 工 作 流 程 图

作者简介 : 宋劲 松 ( 1 9 6 9 一 ) , 男, 安徽 宿州人 , 工程师 , 主要 研 究 方 向为 多 媒 体 技 术 、 信号处 理. E - ma i l : 1 1 4 7 6 0 0 3 0 2 @

qq .c o n. r

基于DSP和FPGA的通用数字信号处理系统设计

p e r f o r m d a t a p r o c e s s i n g a n d a c c o mp l i s h t h e c o n t r o l o f US B i n t e r f a c e,ADC ,DA C,e t c .r e s p e c t i v e l y .Th e s y s t e m c a n i m— p l e me n t s p e c t r a l a n a l y s i s ,d i g i t a l f i l t e r d e s i g n a n d o t h e r c l a s s i c d i g i t a l s i g n a l p r o c e s s i n g a l g o r i t h ms .Ha r d wa r e d e b u g r e —

Ab s t r a c t :I n n o wa d a y s ,t h e f u n c t i o n a n d s t r u c t u r e o f e l e c t r o n i c e q u i p me n t a r e b e c o mi n g i n c r e a s i n g l y c o mp l i c a t e d .Th e r e —

s u h s s u g g e s t t h a t i t me e t s t h e d e s i g n r e q u i r e me n t s , a n d c o u l d b e i mp l e me n t e d t o r e a l p r o j e c t a n d d i g i t a l s i g n a l p r o c e s s i n g

基于DSP和FPGA的高速数据采集处理系统[实用新型专利]

![基于DSP和FPGA的高速数据采集处理系统[实用新型专利]](https://img.taocdn.com/s3/m/2f0d2f3884254b35eefd34e9.png)

专利名称:基于DSP和FPGA的高速数据采集处理系统专利类型:实用新型专利

发明人:凌雁波,刘宇芳,陈祥,张鹏宙,张茜,苗丰,李勇申请号:CN201220334118.4

申请日:20120711

公开号:CN202838339U

公开日:

20130327

专利内容由知识产权出版社提供

摘要:本实用新型提供一种基于DSP和FPGA的高速数据采集处理系统,包括传感器接口、模/数转换模块、DSP处理器、FPGA处理器、数字控制电路、通讯接口、屏幕键盘模块。

主要通过FPGA将模/数转换模块的数字结果送到FPGA内部构建的双口RAM中,再由DSP通过DMA的方式读取采样数据进行计算处理,并将计算结果写入双口RAM,再通过FPGA控制外部器件;传感器接口电路对采集的模拟量进行调理后再送入模/数转换模块进行转换;数字控制电路提供了状态量的24V干接点输入、24V继电器驱动电路和PWM驱动电路;通讯接口提供DSP和上位机的接口;提供了屏幕键盘接口,可以进行一些重要数据的实时显示和简单的现场操作。

申请人:南京国电环保科技有限公司

地址:210061 江苏省南京市高新技术开发区永锦路8号

国籍:CN

代理机构:南京汇盛专利商标事务所(普通合伙)

代理人:张立荣

更多信息请下载全文后查看。

基于DSP和FPGA的数字化中频处理平台

信号处理芯片, 在要求低功耗的便携式设备中, 主要使用低 功耗的T S2c0o M 30 50 系列芯片; 对功耗要求不高的设备中主

要使用 T S 2C 00系列 芯片 , S M 30 60 D P芯片主要 完成 各种 信号

通用的硬件平台, 以使各种相关 的通信任务能够用软件完 成, 从而构成一个具有高度灵活性 、 开放性 的通信系统。 采用 DP FG S 和 P A的数字信号处理平台显示出了其优越 性, 该平台可以把两者的优点结合在一起, 既兼顾速度和灵

活性 , 又具有较强的通用性 , 适于模块化设计 , 易于维护 系统 和扩展, 非常适合于高速信号处理。

bsdO ra adMD,1 I pe S dF G a iBodBn e l lg edD Pa P A,Sf a o ,ul so stui r l fx it adCm il s n ow r icr fl w nv s , eily n O — t es e yh i s e a l b i '

T NG l- n NI A l g pi U H AN /o d n Xa -o g

A s at hsppr noue iil F cs p tr ae isf aer i t ho g . " sp tr bt c T i ae tdcsad t es l o bs O owr a o e nl y 3 i l o r ir ga I a m f d l t d c o h a m f

图 1 以 D P和 F A为 中心的数字化 中频处理平 台 S W, 其中超大规模 FG I A芯片 和高速 的 D P芯片是 系统 的核 】 S

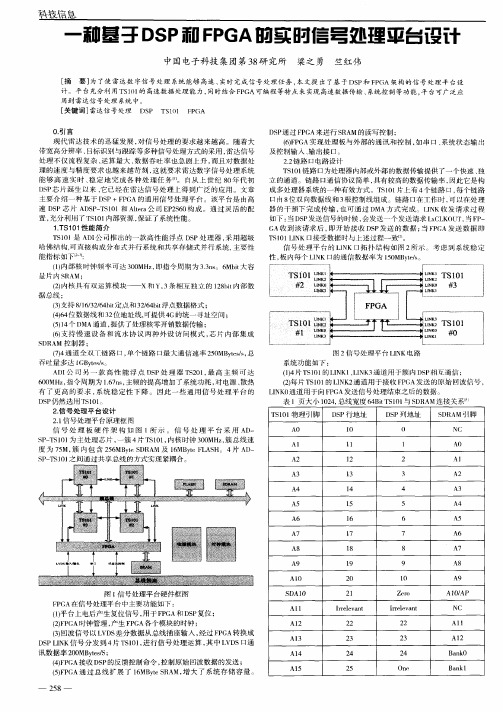

一种基于DSP和FPGA的实时信号处理平台设计

T 1 1是 A I 司推 出的一款 高性能浮点 D P处理器 . s0 D公 S 采用超级 哈佛结构 , 可直接构成 分布式并行 系统 和共享存储式并 行系统, 主要性 能 指 标 如 21 F1 : - 3 () 1内部核时钟频 率可达 30 z 即指令周 期为 33 s 内核 具有 双运算模 块——x和 Y, 条相互 独立 的 18 i内部数 3 2 bt 据 总线 ; () 3支持 81/26 bt /63/4 i 定点和 3 /4 i 26 bt 浮点数据格式 ; ()4 46 位数据线 和 3 位 地址线, 2 可提供4 G的统一寻址空 问; ()4 DMA通道 , 51 个 提供 了处理 核零开销数据传输 ; () 6支持 慢速 设 备和 流水 协议 两种 外设 访 问模式 , 芯片 内部 集成 SR D AM 控 制 器 ; ()通 道全双T链路 V , 74 I单个链路 V最大通信速率 20 ye/, I 5 MB ts 总 s

用到 雷 达 信 号 处 理 系统 中。

[ 关键词 ] 雷达信 号处理

O 引 言 .

DS T 11 F G P S 0 P A D P通过 F G S P A来进行 S M的读写控制 ; RA ()P 6F GA实现 处理板与外 部的通讯 和控制 , 如串 口 、 系统 状态输 出 及 控 制 输 入 、 出接 口 。 输 22 路 口 电路 设 计 .链

T 1 1物 理 引 脚 D P行 地 址 S0 S

A0

A1

21 .信号处理平 台原理框 图 信 号 处 理 板 硬 件 架 构 如 图 1 示 。信 号 处 理 平 台 采 用 A 所 D— s — s 0 为 主 处 理 芯 片 , 簇 4片 T 1 1 内 核 时 钟 3 0 P T l1 一 S0 , 0 MHz簇 总 线 速 , 度 为 7 M, 内包 含 2 6 yeS AM及 1MB t F A H。4片 A 5 簇 5 MB t DR 6 ye L S D— S — SIl P T 之间通过共享总线 的方式实现 紧耦合 。 O

基于DSP和FPGA的高速数据采集处理系统

125105,China)

on

Abstract:In order to acquire the data accurately and rapidly,a multi—channel real-time acquisition system based programmable gates

DSP,field controlled

words:data

a

prospect of application.

acquisition;DSP;FPGA;ADS8364

0引言

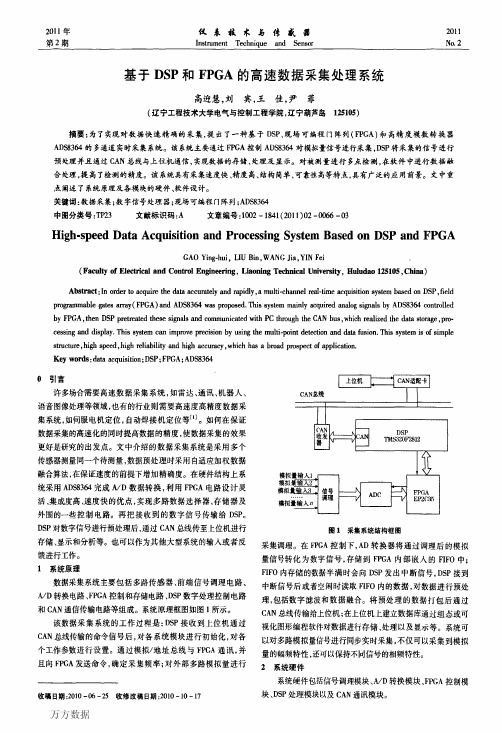

许多场合需要高速数据采集系统,如雷达、通讯、机器人、

语音图像处理等领域,也有的行业则需要高速度高精度数据采 集系统,如伺服电机定位,自动焊接机定位等…。如何在保证 数据采集的高速化的同时提高数据的精度,使数据采集的效果 更好是研究的出发点。文中介绍的数据采集系统是采用多个 传感器测量同一个待测量,数据预处理时采用自适应加权数据 融合算法,在保证速度的前提下增加精确度。在硬件结构上系 统采用ADS8364完成A/D数据转换,利用FPGA电路设计灵 活、集成度高、速度快的优点,实现多路数据选择器、存储器及 外围的一些控制电路。再把接收到的数字信号传输给DSP。 DSP对数字信号进行预处理后,通过CAN总线传至上位机进行 存储、显示和分析等。也可以作为其他大型系统的输入或者反 馈进行工作。 1系统原理 数据采集系统主要包括多路传感器、前端信号调理电路、

V

CAN通信模块设计 系统可利用TMS320F2812 DSP内部自带的CAN控制器,

无需另外添加。只需另加一个CAN收发器就能组成CAN总线 网络,选用PCA82C250,该器件对总线提供差动发送能力并对 CAN控制器提供差动接收能力,是使用最广泛的CAN收发器。 CAN总线通讯模块主要作用是将上位机的命令传输给DSP,并 且将采集到的数据传输给上位机,用于数据存储和处理。 3系统软件设计 系统软件采用模块化、结构化的编程方法。包括数据采集 模块、DSP处理模块、CAN总线接口的通讯模块。 3.1数据采集模块软件设计 数据采集模块主要是FPGA控制,FPGA内部编程有时钟 脉冲产生器、控制器、FIFO存储器等设计。在软件设计中可设 置FIFO的参数、各种标志和控制位,如深度、宽度,空满、半满 全满、可编程满等标志位,写使能、读使能等控制位,以便实现 与DSP的逻辑接口H1。当接到DSP信号后,初始化各个子程 序模块和ADS8364,包括AD采样的速率、参考电压的设定、时 钟的初值和分频比以及控制器的初值。 初始化完成后,FPGA输出时钟信号给AD8364并且提供 HOLD保持信号,启动转换。等待AD8364转换完成后产生中断

基于FPGA的高性能数字信号处理器设计与实现

基于FPGA的高性能数字信号处理器设计与实现随着科技的不断发展,数字信号处理(Digital Signal Processing,DSP)在各个领域得到了广泛的应用,例如通信、音频处理、图像处理等。

为了满足高性能和低功耗等需求,基于FPGA(Field-Programmable Gate Array,可编程门阵列)的数字信号处理器(DSP)逐渐受到关注和采用。

本文将介绍基于FPGA的高性能数字信号处理器的设计与实现。

一、引言随着移动通信、无线网络、人工智能等技术的迅速崛起,对数字信号处理器的性能要求越来越高,传统的通用处理器已经无法满足需求。

而FPGA作为一种可编程硬件设备,可以通过重新编程来实现各种不同的功能,因此成为了设计高性能数字信号处理器的重要选择。

二、FPGA的特点与优势1. 可编程性:FPGA采用可编程逻辑单元,可以根据应用的需要进行重新编程,实现各种功能。

2. 并行处理能力:FPGA内部拥有大量的可编程逻辑单元和片上存储器,可以同时处理多个数据流,提高运算效率。

3. 低功耗:相比于传统的通用处理器,FPGA在相同运算量下具有更低的功耗。

4. 实时性能:FPGA采用硬件并行处理方式,具有优异的实时性能,适用于对于响应时间要求较高的应用场景。

三、基于FPGA的数字信号处理器设计与实现的关键技术1. 数据流架构设计:数字信号处理器的核心是对数据流的处理,需要将各个功能模块进行合理的设计与连接,实现数据的流动。

2. 算法优化:针对不同的应用场景,需要对算法进行优化,减少计算复杂度和资源占用,提高处理性能。

3. 存储器设计:数字信号处理器需要使用大量的存储器来存放数据和中间结果,在FPGA中,需要合理分配片上存储器和外部存储器。

4. 时序约束与时钟分配:在FPGA中,设计时需要考虑时序约束和时钟分配,保证各个模块在时钟信号的控制下正常运行。

5. 性能评估与优化:设计完成后,需要进行性能评估,对于不满足要求的地方进行优化,提高数字信号处理器的性能。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

术,该平台还具有一定的开放性和可

示意图与图2相似,只是核电压不同。

程序与数据存储器 F L A S H 采用 扩展性,可以很好地满足设计的完善、

由超大规模FPGA芯片和高速的DSP芯 Intel公司的E28F320,其存储容量为 功能的扩充及程序的更改。

片组成系统的核心,是为了发挥两者 32Mbit。由 DSP 的供电芯片TPS70348

图2 DSP芯片的供电示意图

表 1 FPGA 芯片与 DSP 芯片的比较

F P G A 芯片

编程方式

V H D L 、A H D L 语言及图形编程等,

实现容易

资源重复利用性

通过外部处理器动态配置

硬件资源结构

可实现并行的乘法器/加法器操作

处理速度

并行运算速度快,只受硬件结构限制

适合的信号处理运算 高速并行处理

的优势。FPGA 芯片与 DSP 芯片相比, 为其一起供电,TPS70348芯片的复位

系统的软件设计流程

由于其结构上的优势,FPGA芯片更适 信号 /RESET为 FLASH 和 DSP的共同复

本文设计的平台通过动态配置可

w w w . e e p w . c o m . c n 电子产品世界 2004.10 /下半月 91

式中:SNR为输出信号的信噪比; B 为比特分辨数,即A/D 的转换位数; 为采样速率;输入模拟信号的最高频

理技术已在通信、信息、电子、自动控

总体硬件框架

制、航天及军事等领域中得到广泛应

图1为本文要介绍

用。

的高速数字信号处理平

以现代通信理论为基础,以数字 台的硬件框图,主要包

信号处理为核心的软件无线电技术是 括五个功能块:高速A/

D S P 芯片 C、汇编语言编程等, 实现容易 改变 M E M O R Y 内容重复利用 M A C 单元的重复操作 受 MAC 单元操作速度的限制 串行顺序操作

超大规模 FPGA 芯片

合完成并行处理、重复性强、速度要求 位信号。

本文设计高速数字信号处理平台 高的数字信号处理运算;而DSP芯片更

高速 A/D 及 D/A 变换

ቤተ መጻሕፍቲ ባይዱ

FPGA+DSP 的结构来实现高速数字信号处理。该方案采用先进的FPGA

高速的数字信号处理需要A/D器

和 DSP芯片,借鉴了软件无线电的思想,通过DSP 芯片对 FPGA芯片的 件具有较高的采样速率和工作带宽,

动态配置来实现具有通用性、可扩充性的硬件平台,并对其硬件结构和 同时为适应复杂的电磁环境和特殊的

的 FPGA 芯片均采用ALTERA 公司 APEX 适合完成串行顺序处理。两者比较如

动态配置技术

系列。其中用于完成数字信号处理算 表 1所示。

由 DSP+FPGA 芯片及总线的结构

法的芯片为EP20K400E,由它完成DSP

组成高速数字信号处理平台,可以充

芯片前端高速、复杂的数字信号处理。

接口 FPGA 及 FLASH 模块

对信息的需求越来越大,对信息的处 来构造一个具有通用性、可扩充性、灵 下式:

理速度也越来越快。信号处理理论与 活的多功能高速数字信号处理平台。

技术的飞速发展直接导致 A/D、D/A、 FPGA及DSP等电子集成产品的高速发 展与更新,使许多复杂、高速的信号处 理运算的实现成为可能。数字信号处

该平台通过动态配置可以进行多模式 工作,能够应用在无线接收、卫星接收、 图象处理和信号分析等多个领域。

初始化,DSP 通过初始 程序对 FPGA 芯片进行 配置,系统开始进行数 据的收发,并送往计算 机或主控设备。当计算 机或主控设备需要更改 工作模式时,将变换工 作模式的命令送DSP 芯 片,DSP 芯片接收到该 命令后,通过预置在 FLASH 的程序对 FPGA 芯片进行重新配置,并 转换工作模式,系统重 新开始数据的收发。其 软件流程如图3所示。

计。动态配置技术为同一硬件平台上 实现不同的功能需求、不同的工作模 式提供了可能。

本文介绍一种高速数字信号处理

是系统的核心,用来完成高速数字信 号处理算法。下面就如图所示的各部 分作介绍。

率。本文介绍的高速数字信号处理平 台的 A/D转换器采用AD9235芯片,转 换位数为 12 比特,采样率最高可达 65MSPS;D/A转换器采用AD9765芯片,

结语 本文介绍一种高速数字信号处理 平台的实现方案,借鉴了软件无线电 技术,通过FPGA 和 DSP芯片来构造一 个具有通用、可扩充、灵活的多功能高

速数字信号处理平台。该平台可以在 软定义无线电结构、图象处理和信号 分析等多个领域进行应用。■

参考文献: 1.David B‘. Performance of an IF Sampling ADC in Receiver Applications. International IC -China-Conference Proceedings’,2001. 2.Cummings M, Haruyama.‘FPGA in the software radio’,‘IEEE Communications Magazine’, 1999,37(2) 3.杨小牛等.‘ 软件无线电原理与 应用’,北京,电子工业出版社,2001. 4. 徐以涛,沈良,王金龙.‘FPGA 技术在软件无线电中的应用’,电信科学, 2001,17(11). 5.张雄伟,曹铁勇‘. DSP芯片的原理 与开发应用’,北京,电子工业出版社,2000.

近几年通信与电子领域最引人注目的 D 及 D/A 变换、超大规

话题。软件无线电技术突破了以功能 模 FPGA 芯片、高速DSP

单一、可扩充性差的硬件为核心的设 芯片、程序与数据存储

计局限性,强调以开放性、扩充性和软 器、FPGA完成的接口模

件编程硬件为通用平台,利用系统可 块。其中超大规模FPGA 升级、可重复配置来实现多功能的设 芯片和高速的DSP芯片 图1 高速数字信号处理平台的硬件框图

分发挥软件的重要作用。该平台可以

ALTERA 公司的 EP20KE 系列芯片核电

接口 FPGA 芯片采用 EP20K100E, 通过 DSP的控制,发挥FPGA芯片的动

压为1.8V,采用的I/O电压为3.3V,也 由它完成高速数字信号处理平台与计 态配置技术,实现了硬件资源动态分

需要双电压供电。设计中采用的供电 算机或其它主控设备的连接。该芯片 配。在同一个硬件平台上,通过动态地

上接 89 流,把 VREF 与 VBIAS 之 间的差被除以 RG便可。注意:要使电 路正常工作,VBIAS 必须小于 VREF。 对于 10µA 的光电二极管电流,RG 为 20.0K½。PN200A PNP 晶体管的基极电 流受到一个 4.7K½ 的电阻器限制,将 电流限制设定约为 1mA。 该晶体管具有 约为 100 的电流放大系数, 所以晶体管 能提供的最大电流约为 100mA,这将 超过微型 SOT-23 封装的热耗散。为防 止晶体管中的热逸散,与 LED 或激光 二极管串连的电阻器将集电极电流限 制为二极管的最大工作值。如果需要 更多的电流,应该联合使用具有较大

图 2 原型控制电路 图 3 控制电路的具体实施方式

92 2004.10 /下半月 电子产品世界 w w w . e e p w . c o m . c n

集电极电流的晶体管和诸如 SOT-223 的 较大封装。为了限制电路的带宽从而 保持稳定,可使用一个与光电二极管 电容(大约为 15pF,VBIAS 为 1.2)并 联的 15pF 电容,使放大器在约 250KHz 处工作。

软件工作流程进行了阐述。

系统要求,器件还应具有较大的信噪

关键词: 软件无线电;动态配置;FPGA;DSP

比动态范围。这就要求A/D器件同时具

有高的采样速率和大的比特分辨数,

引言

平台的实现方案,该方案借鉴了软件 因为这两项性能指标直接影响输出信

随着科学技术的快速发展,人们 无线电的思想,通过FPGA 和 DSP芯片 号的信噪比动态范围,三者的关系如

芯片为TI公司的TPS70351芯片,该芯 的核电压为1.8V,采用的I/O电压为 调用不同的软件程序,来实现多功能、

片 5V输入,1.8V和 3.3V双电压输出, 3.3V,采用的供电芯片也为TI公司的 多模式工作。由于采用了动态配置技

专为 DSP和 FPGA等需求设计。供电的 TPS70351芯片。

90 2004.10 /下半月 电子产品世界 w w w . e e p w . c o m . c n

E m b e d d e d S y s t e m s 嵌入式系统

输入数据率可达125MSPS,转换位数为 12比特。

高速 DSP 芯片 本文设计的高速数字信号处理平 台中采用的DSP芯片为——TI公司的 T M S 3 2 0 C 6 2 0 3 B 芯片,由于 TMS320C6000系列芯片的开发环境比 较完善,特别是C语言的编译可以达到 很高效率,因此对缩短软件开发周期 很有利;同时 TMS320C6000 系列芯片 速度高,可以应付复杂的数字信号处 理技术。TMS320C6203B芯片的核电压 为1.5V,采用的I/O电压为3.3V,需要 双电压供电。设计中采用的供电芯片 为TI公司的TPS70348芯片,该芯片5V 输入,1.5V和 3.3V双电压输出,专为 DSP 和 FPGA等需求设计。供电的示意 图如图2所示。

E m b 嵌入式系统 e d d e d S y s t e m s

基于 DSP+FPGA 的高速数字信号处理平台

High-Speed Digital Signal Processing Platform Based on DSP and FPGA

总参第六十三研究所 陈勇 李桂伦

摘 要: 本文介绍了一种高速数字信号处理平台的实现方案,主要是基于

E m b 嵌入式系统 e d d e d S y s t e m s