实验一 半加器设计

实验一、半加器、全加器实验报告

(7)编程下载 (tools/programmer)

2.验证半加器、全加器的真值表。

根据管脚锁定的方案,操作仪器,记录数据。

半加器: 全加器:

输入

a

b

0

0

0

1

1

0

1

1

输出

sh

ch

输入

a

b

ci-1

0

0

0

0

0

1

0

1

0

0

1

1

1

0

0

1

0

1

1

1

0

1

1

1

输出

si

ci

思考组合逻辑电路的特点: 六、实验总结(总结本次实验收获,实验中应该注意的事项)

实验一、 半加器 全加器设计 实验报告

专业班级:

学号:

姓名:

一、实验目的

1.初步掌握 Quartus 开发系统的使用 2.掌握原理图的设计方法 3.掌握组合逻辑电路的设计方法,理解组合电路的特点 二、实验原理

加法运算是计算机中最基本的一种算术运算。能完成两个一位二进制数的相加运算并

求得“和”及“进位”逻辑电路,称为半加器。全加器是完成两个一位二进制数相加,并考虑低 位来的进位,即相当于将三个一位二进制数相加的电路。

工程文件必须保存在

,建立工程文件时注意选择使用的器件的 device family

是

, devicBiblioteka 名称是。(2)在工程文件中添加源文件(file/new)

在出现的对话框中,选择 Design Files 中的选择

(Block Diagram/Schematic File /

组合逻辑电路实验报告(半加器全加器及逻辑运算)

实验目的 1、 掌握组合逻辑电路的功能测试。 2、 验证半加器和全加器的逻辑功能。 3、 学会二进制数的运算规律。 实验步骤 半加器: 组合逻辑功能路功能测试。 用两片 74LS00 组成图 2-3 所示的逻辑电路。 用两片 74LS00 按左图在实验箱上连接好电路。 图中 A、B、C 分别接电开关,Y1、Y2 接发光二极管并观察。 记录实验测量数据: A 0 0 0 0 1 1 1 1 B 0 0 1 1 0 0 1 1 C 0 1 0 1 0 1 0 1 Y1 0 0 1 1 1 1 1 1 Y2 0 1 1 1 0 1 0 0

全加器: 具体实验步骤: 1. 在实验箱上用 74LS86(异或门)和 74LS00 按左图连接电路。 2. 图中 A、B 接电平开关,Y、Z 接发光二极管显示。 3. 通电,并按 A、B 不同的电平低得出பைடு நூலகம்下结论: A B Y Z 0 0 1 1 0 1 0 1 0 1 1 0 0 0 0 1

实验一 半加器全加器的设计

实验一半加器和全加器EDA设计一、实验目的1.熟悉利用MAX+plusⅡ的原理图输入方法设计简单组合电路,掌握层次化设计的方法;2.通过半加器和全加器的设计把握利用原理图输入设计电子线路的详细流程。

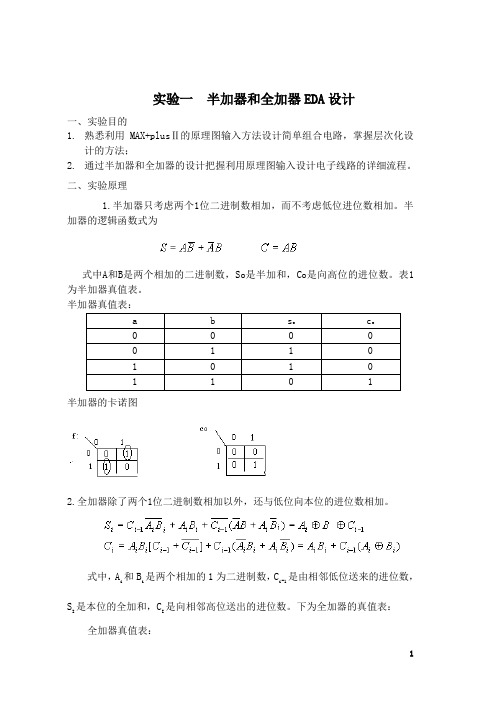

二、实验原理1.半加器只考虑两个1位二进制数相加,而不考虑低位进位数相加。

半加器的逻辑函数式为式中A和B是两个相加的二进制数,So是半加和,Co是向高位的进位数。

表1为半加器真值表。

半加器真值表:a b so c o0 0 0 00 1 1 01 0 1 01 1 0 1半加器的卡诺图2.全加器除了两个1位二进制数相加以外,还与低位向本位的进位数相加。

式中,Ai 和Bi是两个相加的1为二进制数,Ci-1是由相邻低位送来的进位数,S I 是本位的全加和,CI是向相邻高位送出的进位数。

下为全加器的真值表:全加器真值表:a b Cf co10 0 0 0 00 0 1 1 00 1 0 1 00 1 1 0 11 0 0 1 01 0 1 0 11 1 0 0 11 1 1 1 1全加器的卡诺图四、实验内容和步骤1.(1)打开MUXPLUS错误!未找到引用源。

,选择”File”→”New”,在弹出的”New”对话框中选择”File Type”中为原理图编辑输入项”Graghic Editor file”,按”OK”后将打开原理图输入编辑窗。

(2)在原理图编辑窗中的任何一个位置右击鼠标,将快捷菜单,选择其中的输入元件项”Enter Symbol”。

(3)用鼠标双击元件库”Libraries”中的c:\muxplus2\max2lib\prim项(假设Muxplus2安装在C盘)。

在”Symbol Files”窗口即可看到基本逻辑元件库prim中的所有元件。

为了设计半加器,分别调入元件and2,not,xnor,input和output并连接好。

如图8-3,8-4所示。

然后分别在input和output的PINNAME 上双击使其变黑色,再用键盘分别输入各引脚名:a,b,co,so。

实验一:半加器与全加器实验

实验一:半加器与全加器实验(1)实验目的与任务目的:理解半加器、全加器原理;掌握加法器Verilog编写方法;熟悉基于Quartus II软件的Verilog代码文本输入设计流程。

任务:基于Quartus II软件和EDA实验箱完成全加器的设计、仿真与硬件测试。

(2)实验设备带有windows操作系统和Quartus II软件的PC机一台;EDA实验箱一台(包含电源线和下载线)。

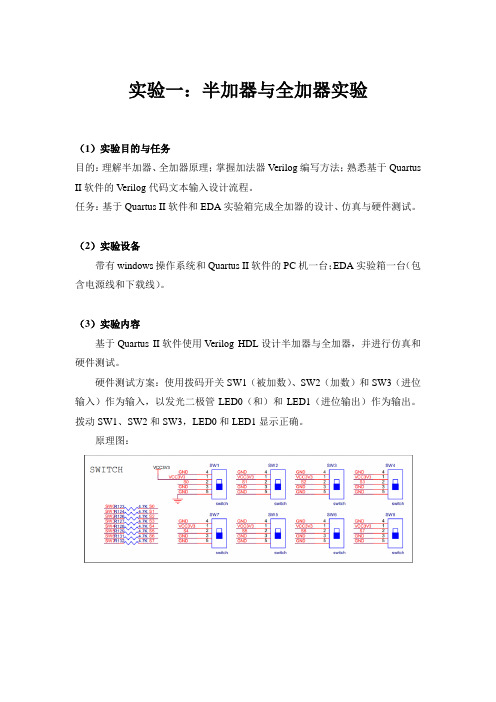

(3)实验内容基于Quartus II软件使用Verilog HDL设计半加器与全加器,并进行仿真和硬件测试。

硬件测试方案:使用拨码开关SW1(被加数)、SW2(加数)和SW3(进位输入)作为输入,以发光二极管LED0(和)和LED1(进位输出)作为输出。

拨动SW1、SW2和SW3,LED0和LED1显示正确。

原理图:注意:原理图中的SW0、SW1、SW2应该为实验箱上的SW1、SW2、SW3。

(4)实验步骤①运行Quartus II软件,编写半加器和全加器的Verilog代码,并保存(半加器保存为h_adder.v,全加器保存为f_adder.v)。

②创建工程,工程名为f_adder,把h_adder.v和f_adder.v添加到工程中,选择目标芯片为Cyclone III系列的EP3C120F780C8,不使用第三方EDA工具。

③编译。

④使用Quartus II自带的仿真工具对全加器进行时序仿真(打开波形编辑器,设置仿真时间50us,波形文件存盘f_adder.vwf,将工程f_adder的端口信号节点选入波形编辑器中,总线数据格式设置和参数设置,编辑输入波形数据,启动仿真器,观察仿真结果)。

⑤引脚锁定。

⑥编译文件(产生JTAG编程文件f_adder.sof(掉电丢失);并通过转换得到JTAG间接编程文件f_adder_file.jic(掉电不丢失))下载,硬件测试,随意拨动实验箱中的SW1、SW2和SW3,观察LED0和LED1的变化。

组合逻辑电路(半加器全加器及逻辑运算)实验报告

电子通信与软件工程系2013-2014学年第2学期《数字电路与逻辑设计实验》实验报告--------------------------------------------------------------------------------------------------------------------- 班级:姓名:学号:成绩:同组成员:姓名:学号:---------------------------------------------------------------------------------------------------------------------一、实验名称:组合逻辑电路(半加器全加器及逻辑运算)二、实验目的:1、掌握组合逻辑电路的功能调试2、验证半加器和全加器的逻辑功能。

3、学会二进制数的运算规律。

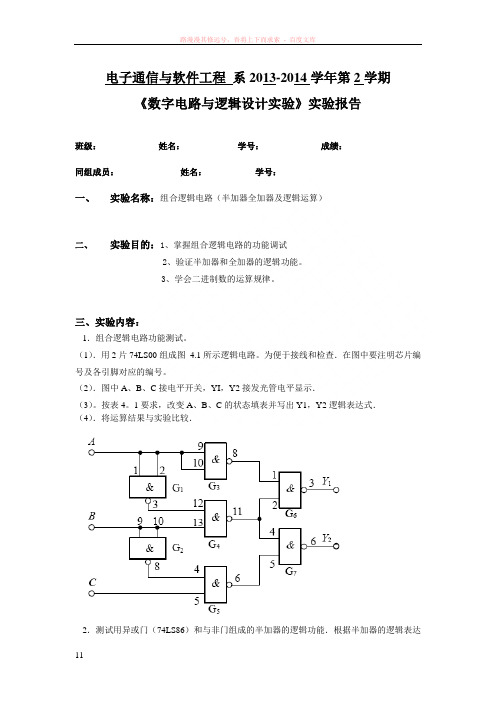

三、实验内容:1.组合逻辑电路功能测试。

(1).用2片74LS00组成图4.1所示逻辑电路。

为便于接线和检查.在图中要注明芯片编号及各引脚对应的编号。

(2).图中A、B、C接电平开关,YI,Y2接发光管电平显示.(3)。

按表4。

1要求,改变A、B、C的状态填表并写出Y1,Y2逻辑表达式.(4).将运算结果与实验比较.2.测试用异或门(74LS86)和与非门组成的半加器的逻辑功能.根据半加器的逻辑表达式可知.半加器Y是A、B的异或,而进位Z是A、B相与,故半加器可用一个集成异或门和二个与非门组成如图4.2.(1).在学习机上用异或门和与门接成以上电路.接电平开关S.Y、Z接电平显示.(2).按表4.2要求改变A、B状态,填表.3.测试全加器的逻辑功能。

(1).写出图4.3电路的逻辑表达式。

(2).根据逻辑表达式列真值表.(3).根据真值表画逻辑函数S i 、Ci的卡诺图.(4).填写表4.3各点状态(5).按原理图选择与非门并接线进行测试,将测试结果记入表4.4,并与上表进行比较看逻辑功能是否一致.实验结果:表4.1输入输出A B C Y1 Y20 0 0 1 1 1 1 0 0111111111111111111Y1=A+B Y2=(A’·B)+(B’·C)表4.2输入端 A 0 1 0 1B 0 0 1 1输出端Y 0 1 1 0Z 0 0 0 1 表4Ai BiC1 i Y Z X1 X2 X3 S i C i0 0 0 0 0 1 1 1 0 00 1 0 1 0 1 0 1 1 01 0 0 1 0 1 0 1 1 0 1 1 0 0 0 1 1 1 0 1 0 0 1 0 1 1 1 0 1 00 1 1 1 1 0 1 1 0 11 0 1 1 1 0 1 1 0 1 1 1 1 0 1 1 1 0 1 1表4.4输入端Ai0 0 0 0 1 1 1 1Bi0 0 1 1 0 0 1 1C1 i0 1 0 1 0 1 0 1输出端Ci0 0 0 1 0 1 1 1Si0 1 1 0 1 0 0 1 Y=A’B+AB’Z=CX1=A’B+C’+AB X2=A’B’+AB+C X3=A’B+AB’+C’Si=A’B’C+A’BC’+AB’C+ABC Ci=AC+AB+BC实验总结:此实验中因本就缺少一块74LS00的芯片导致线路不完整,原本打算用74LS20来代替74LS00,但电路还是出现了问题,原以为是电路接线的问题,也重新接线过,但是情况毫无变化。

计算机组成原理-半加器实验报告

课程设计报告课程设计名称:计算机组成原理课程设计课程设计题目:半加器和全加器设计开发院(系):专业:班级:学号:姓名:指导教师:完成日期:目录1.1实验目的 (3)1.2 实验内容 (3)1.3 实验仪器及元件 (3)2.1 实验原理及电路图 (3)2.2 实验过程及结果记录 (4)2.3 实验结果分析 (6)3.1 思考 (6)3.2 收获感想 (6)B A B A⊕=1.1 实验目的1、掌握MAX +PLUS Ⅱ开发软件的安装和使用方法,能够初步运用此软件进行程序的编写、编译、逻辑综合和优化,以及进行功能和时序仿真2、掌握利用此软件进行程序的下载和适配以及与EDA 实验开发箱相结合进行硬件验证的方法3、掌握半加与全加的原理1.2 实验内容1、熟知MAX+plusII 设计流程2、设计一个半加器和一个全加器1.3 实验仪器及元件半加器:2个input A 、B ;一个AND2;一个XOR ;两个output 。

全加器:3个input ain 、bin 、cin ;两个设计好的半加器元件;一个OR2;两个output 。

2.1 实验原理及电路图半加器原理:只求本位和,不考虑低位的进位。

实现半加操作的电路叫做半加器。

状态表A 、B 为两个加数,C 为向高位的进位,C=AB , S 为半加和。

全加器原理:加数、加数以及低位的进位三者相加称为“全加”,实现全加操作的电路叫做全加器。

Ci-1:来自低位的进位 Ci :来自高位的进位2.2 实验过程及结果记录半加器基本实验步骤:为本项工程设计建立文件夹(文件夹名不能用中文和空格),文件夹取名adder ; 打开MAX+PLUS II ,输入设计项目和存盘,新建设计文件,选择打开原理图编辑器;点击鼠标右键,出现窗口选择“Enter Symbol ”输入一个元件,在接下来的窗口中输入元件名,点击OK 就可以出现实验所需的元件;将得出的元件在原理编辑窗口连接好,成为一个半加器;下面给出我实验中做出的半加器原理图:将半加器原理图存盘(存在第一步新建的文件夹中)、将设计项目设置成工程文件并对其进行Ai B iC i-C iS i编译。

(VHDL实验报告)一位半加器,全加器的设计

A

10

五、实验步骤

(一)半加器的设计

4、对设计文件进行仿真

4)编辑输入端口波形,即指定输入端口的逻辑电平变化,在波形编辑窗 口中,选择要输入波形的输入端口。以 b 端口为例,右键单击 b ,依次选 择value--clock--period,将时间改为1us。然后重复此过程将 a 的时间改 成 2us (a的周期是b的2倍),再将输入端的D0--D3选择不同的周期(一次 要有所差别)。最后选择软件的 Fie>Save进行保存。

3)加入输入、输出端口,在波形编辑器窗口左边的端口名列表 区点击鼠标右键,在弹出的右键菜单中选择 Insert Node or Bus… 命令,在弹出的 Insert Node or Bus 对话框界面中点击 Node Finder…按钮。在出现的 Node Finder 界面中的 Filter 列表中选 择 点击 List,在 Nodes Found 窗口出现所有信号的名称,点击中 间的按钮则 Selected Nodes 窗口下方出现被选择的端口名称。双击 OK按钮,完成设置,回到 Insert Node or Bus 对话框,双击OK按钮 ,所有的输入、输出端口将会在端口名列表区内显示出来。

5)按默认选项,点击NEXT出现新建工程以前所有的设定信息, 再点击FINISH完成新建工程的建立。

A

7

五、实验步骤

(一)半加器的设计

2、建立文本设计文件

1)选择File--New--Device Design Files--VHDL File,点击OK按钮,打开进入文本编辑器对话框。

2)在文本编辑器中输入对应VHDL程序代码,如下图 所示:

全加器的设计采用“元件例化语句”,故需建立两个VHDL文 本编辑对话框(一个顶层文件,一个底层文件)。在相应的编辑框中 输入相应的VHDL语句,再分别以各自的实体名进行保存。注意的是顶 层文件名应必须与工程名一致。此次实验底层文件为半加器VHDL语句 ,顶层文件为全加器VHDL语句,其语句分别如下两图所示:

半加器和全加器实验报告

半加器和全加器实验报告数电实验报告半加全加器实验二半加/减器与全加/减器一、实验目的:(1)掌握全加器和半加器的逻辑功能。

(2)熟悉集成加法器的使用方法。

(3)了解算术运算电路的结构。

二、实验设备:1、74LS00(二输入端四与非门)2、74LS86(二输入端四异或门)3、数字电路实验箱、导线若干。

(74LS00引脚图)三、实验原理:两个二进制数相加,叫做半加,实现半加操作的电路,称为半加器。

A表示被加数,B表示加数,S表示半加和,Co 表示向高位的进位。

全加器能进行加数、被加数和低位来的信号相加,并给出该位的进位信号以及和。

四、实验内容:用74LS00和74LS86实现半加器、全加器的逻辑电路功能。

(一)半加器、半减器M=0时实现半加,M=1时实现半减,真值表如下:(74LS86引脚图)(半加器图形符号)2、S?B?A?A?BC?B(A?M)(二)全加器、全减器S?A?B?Ci-1Ci?BCi-1?(M?A)(B?C)五、实验结果半加器:S?B?A?A?B C?B(A?M)全加器:S?A?B?Ci-1Ci?C1M?C2M其中C1?(A?B)Ci?1?AB,C2?(AB)Ci?1?AB为了方便,以下Ci?1用C表示CI?(AB?AB)CM?(AB?AB)CM?ABM?ABM?ABCM?ABCM?ABCM?ABCM?ABM?ABM?ABCM?ABCM?ABCM?ABCM?(ABCM?ABCM?ABCM?ABCM ?BC?ABCM?ABCM?ABCM?ABCM?(M?A)(B?C)(BC)则Ci?BCi-1?(M?A)(B?C)六、心得体会本次实验做的是半加/减器和全加/减器两个电路,比上次实验复杂很多,因此充满了挑战性。

实验过程中,我认识到了在利用给定的电子元件进行实验设计来实现某一种或多种功能时,对电路的化简非常重要,而且要符合给定元件的限定条件,只有将电路化简成为能够与给定元件相符的情况下才能达到实验目的。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验一半加器设计

一、实验目的

1、了解和学习Quartus II 5.1软件设计平台。

2、了解EDA的设计过程。

3、通过实例,学习和掌握Quartus II 5.1平台下的图形输入法

4、学习和掌握半加器的工作和设计原理。

二、实验仪器

PC机,操作系统为Windows2000/XP,本课程所用系统均为WindowsXP(下同),Quartus II 5.1设计平台。

三、实验原理

加法器是构成算术运算器的基本单元,有来自低位的进位将两个1位二进制数相加,称为半加。

实现半加运算的电路叫做半加器。

按照二进制加法运算规则可以列出如表1-1所示的半加器真值表。

其中A、B是两个加数,S是相加的和,CO是相加高位的进位。

将S、CO、和A、B的关系写成逻

辑表达式如下:

S⊕

=

+

A

=

A

B

B

B

A

CO=

AB

表1-1 半加器的真值表

四、实验步骤

1、启动Quartus II 5.1:在Windows操作系统下,单击“开始”,选择“程序”,再选择“altera”选项下的“Quartus II 5.1”命令。

2、新建工程:在File菜单中选择New Project Wizard…,弹出对话框如图1-1所示

图1-1

在这个对话框中,第一行是需要你指定项目保存的路径,支持含中文字符的路径,第二行是需要你为这个项目取一个名称,第三行是需要你为这个项目的顶层实体取个名称,如实验不需要使用芯片,这三个设定好后,点击“finish”。

(如何使用芯片及各参数设定将在实验3中讲到)出现如下界面

3、新建文件在File菜单中选择New,出现一个对话框如图 1-2

图1-2

选择Block Diaqram/Schematic File ,然后点击“OK”。

图1-3

4、保存文件:选菜单File\Save,在弹出的Save As对话窗口中,指定存放文件类型、

文件夹和文件名。

这一步也可以放在图形设计完成后进行。

5、原理图设计输入:

(1)元器件符号放置

通过Edit->Insert Symbol插入元器件或点击图板左侧的快捷键Symbol,或双击图板

图1-4

在左侧Name下输入你要找的元器件的名称

图1-5

点击“OK”将元器件拖入图板,

(2)元器件复制

按住Ctrl 选中元器件,拖动即可。

(3)元器件移动

用鼠标单击并拖动元器件符号至相应地方即可。

若要同时移动多个元器件符号,可以按住鼠标左键画一个将所有要移动的符号包括在内的大矩形,然后用鼠标点中矩形内任意一点就可随意移动。

(4)元器件转动

右击需转动元器件符号,可对元器件符号作水平镜像转动(Flip Horizontal)和垂直镜像转动(Flip Vertical),也可按90︒、180︒、270︒转动(Rotate by Degrees)。

也可点击图板左侧的快捷键

(5)元器件删除

单击选中元器件符号后,用键盘上的Delete键删除该符号。

(6)管脚的命名

绘制完所有的元器件符号后,此时所有输入、输出管脚的默认名为PIN_NAME,用鼠标左键双击PIN_NAME,使其变为黑底白字显示,然后可直接键入管脚名。

本实验的输入分别是A、B;输出是S和CO。

(7)在元器件之间添加连线

①直接相连:把鼠标移到元器件引脚附近,鼠标光标会自动由箭头变为十字形,按住鼠标左键拖动,即可画出连线。

②引线命名:先点击左侧菜单栏中的A,再点击命名的引线使其成为高亮线,然后输入引线名即可。

相同引线名的所有引线表示连接在一起。

注意:与输入、输出管脚相连的引线名即为管脚名,不能再给输入、输出管脚的引线取其它名称,完成后的半加器如图1-6所示.

图1-6 半加器图形设计图

5、保存原理图

选菜单File\Save或单击工具栏中的按钮。

点击保存。

6、编译

如果有多个文件要把这个文件设为当前顶层实体,这样软件编译时就只编译这个文件。

点击projet->Set as Top-level EntityCtrl+Shift+J

接下来进行编译,点击processing->Start Compilation ,见下图

7、逻辑器件符号的生成:执行File\Create/_update->Create Symbol Files for

Current File

点击File->Open ,在文件类型中将文件后缀名设为.bsf,选择*.bsf的文件,打开

五、问题讨论与提高

1、思考在该实验基础上,如何设计一个全加器?

2、如在编译过程中产生错误如何查错与解决?

3、试用VHDL语言设计本实验中的半加器。