东北大学数字电路第二章例题

数字电路与数字逻辑(高起专)-东北师范大学考试及答案

Y2= X3⊕X2

Y1= X3⊕X2⊕X1

Y0= X3⊕X2⊕X1⊕X0

三、画图题

1.用两个74LS138设计一个4-16的译码器。(提示:在74LS138的示意图上直接连线即可)

(10分)

G1Y0

G2AY1

G2BY2

Y3

Y4

A Y5

B Y6

C Y7

G1Y0

G2AY1

G2BY2

Y3

Y4

A Y5

3.电路具有两个稳定状态,在无外来触发信号作用时,电路将(保持原状态不变)

4.用二进制码表示指定高散电平的过程称为(编码)

5.下列逻辑电路中为时序逻辑电路的是(数码寄存器)

6.随机存储器具有(读/写)功能

7.一个容量为512*1的静态RAM具有(地址线9根,数据线1根)

8.随机存储器具有(读/写)功能

3.把下列4个不同数制的数(76.125)D、(27A)H、(10110)B、(67)O按从大到小的次序排列((27A)H)>(76.125)D)>((67)O )>((10110)B )。

4.对于D触发器,欲使Qn+1=Qn,输入D=(Qn),对于T触发器,欲使Qn+1=Qn,输入T=(1)

5.一个512*8位的ROM芯片,地址线为(9)条,数据线为(8)条。

15.余3码01101001.01110011转换为十进制数是:(36.40)

16.将二进制数1011110.0100101转换为十六进制数是:(5E.45)

17.组合电路是由(门电路构成)

18.时序逻辑电路的特点是(任意时刻电路的输出不但取决于这一时刻的输入信号,而且还与电路输入信号前的状态有关)

白中英数字逻辑习题答案

C

AB

00 0 1 1 1 01 1 1 1 11 10 1 1

(4) F=AB+(A+B)(A+C) +A(A+C) =AB+A(A+C)+B(A+C) = A+B+C

1-10 用卡诺图法化简下列各式。

(5) F(A,B,C) = Σm (1,3,5,7) = C (6) F(A,B,C,D) = Σm(3,4,5,6,9,10,12,13,14,15)

AB 0 1 AB CD 00 00 1 0 01 1 0 11 1 0 10 1 0 00 01 11 10 1

01

11 1

10 1

1 1 1

C

1-10 用卡诺图法化简下列各式。 AB 00 0 1 1 01 1 1 11 1 1 10 1 1

C

(3) F=AB+AB+BC+AC = A+B+C

S1 S0

F1 = A + BS0 + BS1 F2 = ABS2 + ABS3 F = F1F2 = A + BS0 + BS1

T2.4 分析下图所示逻辑电路,列出真值表,说明其逻辑功能。 [ 解]

A F1

F1 = ABC + ABC + ABC + B C = A BC + ABC + ABC = A(B + C) + ABC 当B≠C时, F1=A; 当B=C=1时,F1=A;

= A+B+C + A+B+C + A+D + C+D

《数字电路-分析与设计》1--10章习题及解答(部分)_北京理工大学出版社

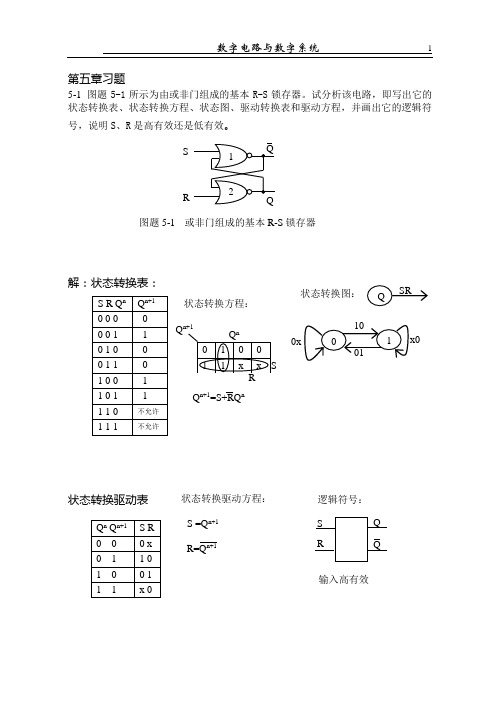

第五章习题5-1 图题5-1所示为由或非门组成的基本R-S 锁存器。

试分析该电路,即写出它的状态转换表、状态转换方程、状态图、驱动转换表和驱动方程,并画出它的逻辑符号,说明S 、R 是高有效还是低有效。

解:状态转换表:状态转换驱动表5-2 试写出主从式R-S 触发器的状态转换表、状态转换方程、状态图、驱动转换表和驱动方程,注意约束条件。

解:与R-S 锁存器类似,但翻转时刻不同。

5-3 试画出图5.3.1所示D 型锁存器的时序图。

解:G=0时保持,G=1时Q=D 。

图题5-1 或非门组成的基本R-S 锁存器S R状态转换方程:Q n+1Q n+1=S+RQ n状态转换图: S =Q n+1R=Q n+1 状态转换驱动方程: 逻辑符号: 输入高有效 G D Q图题5-3 D 型锁存器的时序图5-4试用各种描述方法描述D锁存器:状态转换表、状态转换方程、时序图、状态转换驱动表、驱动方程和状态转换图。

5-5锁存器与触发器有何异同?5-6试描述主从式RS触发器,即画出其功能转换表,写出状态方程,画出状态表,画出逻辑符号。

5-7试描述JK、D、T和T'触发器的功能,即画出它们的逻辑符号、状态转换表、状态转换图,时序图,状态转换驱动表,写出它们的状态方程。

5-8试分析图5.7.1(a) 所示电路中虚线内电路Q’与输入之间的关系。

5-9试分析图5.7.1(b)所示电路的功能,并画出其功能表。

5-10试用状态方程法完成下列触发器功能转换:JK→D, D→T, T→D, JK→T, JK→T’, D→T’。

解:JK→D:Q n+1=JQ+KQ,D:Q n+1=D=DQ+DQ。

令两个状态方程相等:D=DQ+DQ =JQ+KQ。

对比Q、Q的系数有:J=D,K=D逻辑图略。

5-11试用驱动表法完成下列触发器功能转换:JK→D, D→T, T→D, JK→T, JK→T’, D→T’。

解:略。

5-12用一个T触发器和一个2-1多路选择器构成一个JK触发器。

东北大学20年春学期《数字电子技术基础Ⅰ》在线作业3(资料答案)

20春学期《数字电子技术基础Ⅰ》在线平时作业3

学校:奥鹏东北大学

一、单选题 (共 20 道试题,共 80 分)

1.对于T触发器,若原态 Qn=0,欲使新态Qn+1=1 ,应使输入T= ( )。

[[A.]]以上都不对

[[B.]]Q

[[C.]]1或/Q

[[D.]]1

作答提示

√选择是:C

2.和八进制数(166)8等值的十六进制数和十进制数分别为()。

[[A.]]E6H,230D

[[B.]]76H,142D

[[C.]]76H,118D

[[D.]]74H,116D

作答提示

√选择是:C

3.当内存储器系统中内存储器芯片较少时,其片选信号可以采用()[[A.]]与门

[[B.]]74SL138

[[C.]]74LS245

[[D.]]74LS244

作答提示

√选择是:A

4.要构成容量为4K×8的RAM,需要______片容量为256×4的RAM。

[[A.]]8

[[B.]]4

[[C.]]2

[[D.]]12

作答提示

√选择是:D

5.下列电路,具有脉冲幅度鉴别作用的电路是()。

[[A.]]施密特触发器

[[B.]]多谐振荡器

[[C.]]双稳态振荡器

[[D.]]单稳态触发器

作答提示。

数字电路-第2章习题解答PPT课件

解:设vBE=0V时,三极管T截止。T截止

时,IB=0。此时

VCC +10V

vI 00(10)

2

10

vI=2V

vI

R1 2kΩ

1R0CkΩvOT临界饱和时,vCE=0.7V。此时

6

2-8 在用或非门时,对多余输入端的处理方 法同与非门处理方法有什么区别?

A& B

A ≥1 B

F =A ·B 与非:接高电平; 或非:接低电平。

F =A +B

7

2-9 异或门能作为非门使用吗?为什么?

A =1 B

F F AB AB B 1, F A B 0, F A

所以一端接高电平即可构成非门电路。

端提升,为高电平;与非门输出

FA

FCAB

A B

当C=0时,三态门高 C

&

CMOS &F

阻,与非门输出F=1

EN

20kΩ

F C FCCABC

40

练习题2

•试判断如图所示电路能否按各图所要求的逻 辑关系正常工作?若不能正常工作,请做相 应的改动。若电路接法有错,改电路;若电 路正确但给定的逻辑关系不对,则写出正确 的逻辑表达式。能正常工作的在图中括号内 打“√”,否则打“×”。已知TTL门的 IOH/IOL=0.4mA/10mA,VOH/VOL=3.6V/0.3V, CMOS门的VDD=5V,VOH/VOL=5V/0V, IOH/IOL=0.51mA/0.51mA。

错误。 ⒉A=0,无论B、C取何值,AB=AC=0 ,故运算

错误。 ⒊1+B=1,A=B=1时,AB=1,故运算正确。

[东北大学]20秋学期《数字电子技术基础Ⅰ》在线平时作业2-资料答案

![[东北大学]20秋学期《数字电子技术基础Ⅰ》在线平时作业2-资料答案](https://img.taocdn.com/s3/m/48179141f61fb7360a4c6580.png)

[东北大学]20秋学期《数字电子技术基础Ⅰ》在线平时作业2

试卷总分:100 得分:100

一、单选题 (共 20 道试题,共 80 分)

1.用二进制异步计数器从0做加法,计到十进制数178,则最少需要()个触发器。

[选项]A.2

[选项]B.6

[选项]C.7

[选项]D.8

【正确答案是】:D

2.由555定时器构成的施密特触发器,改变控制电压Vco时,则()。

[选项]A.改变输出Uo的幅值

[选项]B.改变低电平的UOL数值

[选项]C.改变高电平UOH的数值

[选项]D.改变回差电压 {图}

【正确答案是】:D

3.一只四输入端与非门,使其输出为0的输入变量取值组合有__________种。

[选项]A.15

[选项]B.8

[选项]C.7

[选项]D.1

【正确答案是】:D

4.一位8421BCD码译码器的数据输人线与译码输出线组合是____ 。

[选项]A.4:16

[选项]B.1:10

[选项]C.4:10

[选项]D.2:4

【正确答案是】:C

5.逻辑函数{图}的对偶式{图}

[选项]A.{图}

[选项]B.{图}

[选项]C.{图}

[选项]D.{图}

【正确答案是】:B

6.欲使D触发器按{图} 工作,应使输入D= ( )。

[选项]A.0

[选项]B.1

[选项]C.Q

[选项]D.{图}。

数字电子技术-东北大学-信息科学与工程学院

2018年硕士研究生统一入学考试《数字电子技术》第一部分考试说明一、考试性质数字电子技术是信息科学与工程学院电路与系统、微电子学与固体电子学专业硕士生入学考试的专业基础课。

考试对象为参加东北大学信息学院2018年全国硕士研究生入学考试的准考考生。

二、考试形式与试卷结构(一)答卷方式:闭卷,笔试(二)答题时间:180分钟(三)考试题型及比例简答题 30%分析、计算及设计题 70%(四)参考书目(1)李景宏主编《数字逻辑与数字系统》第4版,电子工业出版社 2012年出版第二部分考查要点(一)数字逻辑基础1.数制的表示及转换;2.逻辑代数的定律与规则;3.逻辑函数的化简。

(二)逻辑门电路1.CMOS逻辑门电路的原理及特性;2.TTL逻辑门电路的原理及特性;3.CMOS与TTL电路的接口。

(三)组合逻辑电路1.组合逻辑电路特点;2.小规模组合逻辑电路的分析与设计;3.常用的中规模集成电路(译码器、编码器、数据选择器、数值比较器)的原理、分析及应用设计;4.算术运算电路及奇偶校验电路的分析与设计;5.竞争-冒险的概念及判断。

(四)时序逻辑电路1.时序逻辑电路特点;2.触发器的原理及分析;3.由触发器构成的时序逻辑电路的分析与设计;4.常用的中规模集成电路(寄存器、计数器)的原理、分析及应用设计;5.顺序脉冲发生器的原理、分析及设计。

(五)半导体存储器和可编程器件1.半导体存储器的分类,各类存储器的原理及存储器的扩展;2.通用阵列逻辑GAL的原理及VHDL程序设计。

(六)脉冲波形的产生与整形1.集成555定时器的原理及应用;2.门电路构成的矩形波发生器及整形电路。

(七) 数/模及模/数转换器1.数/模转换器原理、分析及应用;2.模/数转换器原理、分析及应用。

东北大学《数字电子技术基础》期末考试必备真题集(含答案)66

东北大学继续教育学院数字电子技术基础复习题一、单项选择题(在备选答案中选出一个正确答案)01、表示一位十六进制数需要二进制数的位数为:(B)A.1位B.2位C.4位D. 16位02.十进制数25用8421BCD码表示为:(B)101 010103.与十进制数()10等值的数或代码为:(A)A.(01018421BCD B.16C.2D.804. 当逻辑函数有n个变量时,变量取值组合共有:(D)A. nB. 2nC. n2D. 2n05.欲使D触发器按Q n+1=Q n工作,应使输入D=(D)D.Q06.多谐振荡器可产生:(B)A.正弦波B.矩形脉冲C.三角波D.锯齿波07.一个16选一的数据选择器,其地址输入(选择控制输入)端个数为:(C)08.下列逻辑电路中为时序逻辑电路的是A.变量译码器B.加法器C.数码寄存器D.数据选择器(C)09、图1-1所示电路,输出F为:(A)A、ABB、A+BC、A⊙BD、A÷B图图图10、图1-2所示电路,输出F 为: (C) A 、A ⊙B B 、AB C 、A+B D 、A ÷B11、图1-3电路为NMOS : (B)A 、与非门B 、异或门C 、与或非门D 、或非门12、图1-4所示电路,当EN=1时: (A)A 、 M 为输入N 为输出B 、 N 为输入M 为输出C 、 N 为输入EN 为输出D 、 M 为输入EN 为输出13、图1-5所示TTL 电路,A=0则Y 1= (C)A .A+V CCB .AC .1D .014、图1-6所示TTL 电路,Y 2= (C) A .A+V CC B .1 C .0 D .A15、图1-7所示TTL 电路,当1、2端都加低电平(逻辑0)时Q n+1= (C)图图图图A.Q n+1 B.0 C.Q n D.116、若将图1-7所示电路构成D触发器,应将(A)A.1、3端相连、2、4端相连并将2端作为D输入端B.1、5端相连、2、4端相连并将5端作为D输入端C.1、3端相连、2、6端相连并将6端作为D输入端D.2、4端相连、1、3端相连并将1端作为D输入端17、图1-8所示电路,该电路产生波形的周期为(B)A、(R1+R2)C B、(R1+2R2)CC、(R1+2R2)C D、(R1+R2)C18、单稳态触发器用途之一是(C)A、自动产生方波B、用做比较器C、定时D、自动产生三角波19、用RAM2114(1024×4位)构成4096×8位RAM,需(B)A、4片;B、8片;C、24片;D、12片20、用户对ROM编程后觉得不满意,还要改写,应选用:(B)A、固定ROMB、E2PROMC、PPROMD、PRAM21、图2-2所示电路,D3D2D1D=0000,B加高电平,(C)C与A相连所构成的加法计数器是A、10进制B、5进制C、11进制D、6进制22、2-2所示电路,D3D2D1D=0010,A加高电平,C与B相连所构成的加法计数器是(A)图A 、10进制B 、8进制C 、6进制D 、9进制23、2-2所示电路,D 3D 2D 1D 0=0010,B 加高电平,C 与A 相连所构成的加法计数器是 (B) A 、10进制 B 、9进制 C 、6进制 D 、8进制24、2-2所示电路,D 3D 2D 1D 0=1000,A 加高电平,C 与B 相连所构成的加法计数器是 A 、10进制 B 、3进制 C 、6进制 D 、12进制 (A)25、2-2所示电路,D 3D 2D 1D 0=1000, B 加高电平,C 与A 相连所构成的加法计数器是 (B) A 、10进制 B 、3进制 C 、6进制 D 、12进制26、图2-3所示电路为 (B) A 、 异步时序电路 B 、 同步时序电路 C 、 同步组合电路D 、 异步组合电路27、图2-3所示电路,FF0和FF1都为 (B)A 、下降沿触发B 、上升沿触发C 、高电平触发D 、低电平触发28、图2-3所示电路,Q 0n+1= (A)29、图2-3所示电路,Q 1n+1= (C)A 、Q 0n Q 1nB 、Q 0n +Q 1nC 、Q 0n ⊕Q 1nD 、Q 0n ⊙Q 1n30、图2-3所示电路,F= (A)图A 、Q 0n Q 1nB 、Q 0n +Q 1nC 、Q 0n ⊕Q 1nD 、Q 0n ⊙Q 1n31、图2-3所示电路,其状态转换图为 (B)32、图2-3所示电路的逻辑功能为 (B) A 、4进制减法计数器 B 、4进制加法计数器 C 、6进制加法计数器 D 、8进制减法计数器33、图2-4所示可变进制加法计数器电路 ,当MN=00时该加法计数器为 (B) A 、 11进制加法计数器 B 、 10进制加法计数器 C 、 12进制加法计数器D 、 13进制加法计数器34、图2-4所示可变进制加法计数器电路 ,当MN=01时该加法计数器为 (D) A 、13进制加法计数器 B 、12进制加法计数器 C 、 14进制加法计数器 D 、11进制加法计数器图35、图2-4所示可变进制加法计数器电路,当MN=11时该加法计数器为(A)A、14进制加法计数器B、12进制加法计数器C、11进制加法计数器D、13进制加法计数器36. 图7所示电路为( B )。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

解:由上拉电阻计算公式可求得

因此0.38 kΩ ≤ Rp ≤2.1 kΩ,取其中间标 称值即可。

例10:如图所示TTL电路驱动CMOS电路 的实例,试计算上拉电阻RL的取值范围。 TTL与非门在VOL≤0.3V时,IOLmax=8mA; 输出端T5管截止时IOH=50μA,CMOS或 非门的高电平输入电流最大值和低电平输 入电流最大值均为1μA, 要求加到CMOS 或 非门输入端的电压 满足VIH>4V, VIL≤0.3V,VDD=5V。

例

4:试计算 74S00 与非门接成如图所示电 路时的扇出系数。已知输出电流IOH=-1mA, IOL=20mA,输入电流 IIH=0.05mA,IIL=-2mA。 若将图中与非门换成或非门 74S02,参数不变, 试计算或非门的 扇出系数。

解:分别考虑输出高低电平两种情况。 与非门的扇出系数分别为

解(1)F的逻辑功能为

(2)与非门无论有几个输入端并联在一起, 总的低电平输入电流都等于一个输入端 接低电平的时的电流IIL。当输入高电平 时,总输入电流等于各个输入端电流之 和,因为T1 管此时处于倒置工作状态, 多发射结反偏。因此 当OC 门输出高电平时,

当OC门输出低电平

因此R的取值范围为0.575~2.85 kΩ之间。

2、要保证D发光,需要保证其正常工作电流。 当T饱和时,Rc两端压降为 5-1.4-0.3-0.3=3V, 要求流过的电流为5~10mA,因此 Rc的范围为 3V/10mA~3V/5mA,即0.3kΩ~0.6kΩ。 3、若 Rc取 0.2kΩ,则此时三极管饱和集电极电 流为

基极电流为

若要三极管饱和需要满足 IB>IBS=ICS/β,故 β 至少应为 15/0.2=75。

(a)

(b)

解:该题目考查TTL 门电路输入端负载特性, 而CMOS 门电路不具有输入端负载特性。 当2 个门电路都是CMOS 门时,由于MOS 管栅极是绝缘的,栅极电流近似为0,所以输 入端通过电阻接地,无论电阻取何值,只要 不是无穷大,其输入端为地电位,因此图所 示与非门输出均为高电平,即 F1=F2=A⋅B⋅0=1。 当2个门都是TTL门电路时,根据TTL与非门 电路原理图,得出ROFF和RON的计算公式:

因此与非门扇出系数为 10。 或非门的扇出系数分别为

因此或非门扇出系数为 5。

例5:(1)某TTL逻辑电路的 VOLmax=0.3V,VOHmin=2.4V,VILmax=0.8V, VIHmin=2.0V。求其噪声容限 VNL和 VNH。

(2)已知CMOS与非门CD4011静态参数 VOLmax=0.05V,VOHmin=4.95V,VILmax=1V, VIHmin=4V。求其噪声容限 VNL和 VNH。

分别计算得ROFF≈685 Ω;RON≈2.6 kΩ。

(a)中R<ROFF,该输入端为低电平F1

=A⋅B⋅0=1;

(b)中R>RON,该输入端为高电平 F=A⋅B。

例12:已知图所示TTL门电路中,OC门输 出管截止时,漏电流IOH≤100μA,输出管 导通时允许通过的最大负载电流为 ILM≤15mA,输出F 的高低电平分别为 VOH≥3V,VOL≤0.4V。G1~G5 的输入特性如 图(b)所示。(1)F 的逻辑功能是什么? (2)求R 的取值范围,并写出表达式。

(1)当输入低电平时,

晶体管满足截止条件,能可靠截止。 当输入为高电平时,

IB>IBS,晶体管满足饱和条件,能可靠饱和导通。

(2)在输入高电平时,要使三极管工作于 饱和状态,需满足IB≥IBS,即

代入相应数据后求得β≥13.2。因此,为使三 极管在输入信号为高电平时能可靠饱和, 三极管的β值最小应大于 14。

例13:已知如图电路中,其中图(a),(b) 为TTL门电路,图(c),(d)为CMOS门 电路,判断四个电路能否正常工作。

解:图(a)TTL 的OC 门电路可以直接实 现线与,但无电阻和电源,无法正常工作。 图(b)TTL 的与非门不能线与,无法正常 工作。 图(c)CMOS门电路,三态门可以直接线 与,但须满足任一时刻只有一个三态门工 作。E=0时,G1门工作,传输门导通,F3= AB 。E=1 时,G2门工作,但此时传输门 TG截止,F3无信号输出,故F 3= E· AB 图(d)CMOS门电路,C=0时,F=A, C=1时,高阻,故F= C· A

例8:已知74LS系列门电路参数 VOLmax=0.5V,VOHmin=2.7V;74HCT 系列参数VILmax=0.8V,VIHmin=2V; 74HC 系列VIHmin=3.5V,VILmax=1.5V。 试判断能否用TTL 电路直接驱动 CMOS 电路?若不能应采取什么措施?

解:主要考虑逻辑电平是否兼容、驱动门 和负载门必须满足VOHmin≥VIHmin; VOLmax≤VILmax。TTL 驱动74HCT 时,满足 逻辑电平关系,可以直接相连;TTL 驱动 74HC时,不满足VOHmin≥VIHmin 的逻辑电 平关系,在TTL输出端与5V电源间接一个 上拉电阻RP,以提高TTL 输出高电平。 TTL电路输出级T5管截止时的漏电流,IO 和IIH都很小,VOH=VDD-RP(IO+nIIH),故只 要RP不是很大,VOH≈VDD,电路如图所示。

解:根据驱动门是否能给负载门提供足够的灌电 流和拉电流,判断逻辑电平是否兼容。 (1)驱动门和负载门的逻辑电平必须满足 VOHmin≥VIHmin;VOLmax≤V ILmax;驱动门 VOLmax=0.33V,VOHmin=3.84V;负载门 VILmax=0.8V,VIHmin=2V。因此HC 系列门与74LS 系列门电路逻辑电平匹配。 (2)驱动门输出低电平时,74HC04的 IOLmax=4mA,6 个74LS的系列门电路总的输入电 流ILtotal=6×0.4mA=2.4mA,故满足IOLmax≥IILtotal; 驱动门输出高电平时74HC04 门电路的 IOHmax=4mA,负载门电路总的输入电流 IIHmax≥IIHtotal;一个74HC04 反相器可以驱动6 个 74LS系列门电路。

(3)在输入低电平时,要使三极管工作 与截止状态,需满足VBE≤0,即

代入相应数据后求得VBB≥1.1V。因此, 为使三极管在输入信号为低电平时可靠截 止, VBB应不小于 1.1V。

例 3:电路如图所示,G1和 G2均为TTL门电路, 其输出高电平VOH=3V,低电平VOL=0.3V,最大 允许拉电流IHM=0. 4mA,最大允许灌电流 负载电流ILM=30mA,三极管β=40,工作于 开关状态,导通时VBE=0.7V,饱和时 VCES=0.3V,最大允许集电极电流 ICM=100mA,发光二极管D 的正向导通压降VD=1.4V, 发光时正向电流ID=5~10mA。

例 2:如图所示电路中,已知 R1=4.3kΩ, R2=16kΩ,Rc=1.5kΩ,VCC=12V,VBB=8V, VC1=5V,输入电压 VIH=5.5V,VIL=0.3V,请 问 (1)当晶体管 β=30 时晶体管能 否可靠地饱和截止? (2) 为保证晶体管在输入信号为 高电平时能可靠饱和,晶体管 的 β 值最小是多少? (3) 为保证晶体管在输入信号 为低电平时能可靠截止,VBB 的最小值是多少

例7:试判断能否用74HC04 中的一个反 相器驱动6个74LS系列门电路。已知HC 系列的参数为IOLmax=4mA;IOHmax=4mA, VOLmax=0.33V,VOHmin=3.84V。74LS 系 列的参数:IILmax=0.4mA;IIHmax=0.02mA, VILmax=0.8V,VIHmin=2V。

例9:用4个74系列OC 与非门的输出端 并联,驱动4个74系列与非门的6个输入 端。已知OC门高电平输出时的漏电流 IOH=250μA,IOLmax=16mA; VOLmax=0.4V,VOHmin=2.4V。与非门的 参数IIH=40μA,IIL=1mA。 试计算上拉电阻RP 的取值范围。

解:根据门电路的噪声容限概念, (1)输入低电平噪声容限 VNL=VILmax VOLmax = 0.8V-0.3V=0.5V;输入高电平噪声容 限 VNH= VOHmin- VIHmin=2.4V -2.0V=0.4V。

(2)输入低电平噪声容限 VNL=VILmax VOLmax =1V- 0.05V=0.95V;输入高电平噪声 容限 VNH=VOHmin- VIHmin=4.95V -4V=0.95V

例6:已知TTL与非门和负载的连接如图所示。

与非门的有关参数为;输入短路电流IIL=1mA, 输入漏电流为IIH=40μA,输出低电平为 VOL=0.1V,输出高电平为VOH=3.2V,最大输入 低电平VILmax=0.4V,最小输入高电平VIH=2.4V, 高电平输出电流为IOH=500μA,低电平输出电 流 IOL=10μA,问负载电阻最小值是多少? 如果与非门输出端又连接了2个同样的与非 门,为保证电路工作正常,负 载电阻是增大还是减小?

解:根据VIH>4V 的要求及已知的TTL 门 电路输出高电平时的漏电流和CMOS 电路 的高电平输入电流,即可求得RL的最大允 许值:

根据VIL≤0.3V的要求及TTL 门电路低电平 时输出电流最大值和CMOS电路的低电平 输出电流,即可求得RL的最小允许值

例11:判断CMOS、TTL 输入端通过电阻 接地时的逻辑电平。如图所示逻辑门均为 5V电源供电,分别讨论电路是CMOS 和 TTL 情况下的输出是什么?TTL门电路为 74LS 系列,VIL=0.8V;VIH=2V。