模拟CMOS集成电路设计课件

CMOS 模拟集成电路课件完整

VTHN VTHN0

2qsi Na Cox

VGS 1 0 1.0 VDS 2 0 5

.op .dc vds 0 5 .2 Vgs 1 3 0.5 .plot dc -I(vds) .probe

*model .MODEL MNMOS NMOS VTO=0.7 KP=110U +LAMBDA=0.04 GAMMA=0.4 PHI=0.7

.end

Systems

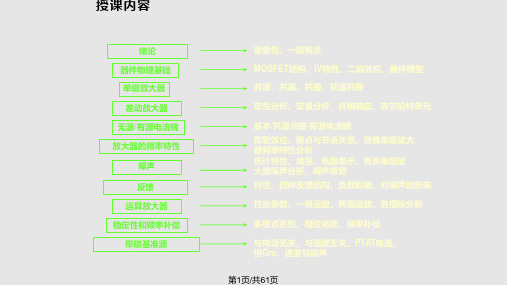

Ch13 开关电容电路

Ch14 DAC/ADC

complex Ch10 运算放大器 Ch7 频率响应

Ch11 稳定性和频 率补偿

Ch8 噪声

Ch12 比较器 Ch9 反馈

Ch3 电流源电流镜 simple Ch4 基准源 Circuits

Devices

Ch5 单级放大器 ch2 MOS器件

*Output Characteristics for NMOS M1 2 1 0 0 MNMOS w=5u l=1.0u

VGS 1 0 1.0 VDS 2 0 5

设计

属性/规范

系统/电路1

系统/电路2 系统/电路3

……

一般产品描述、想法 系统规范要求的定义

系统设计 电路模块规范定义

电路实现 电路仿真

否

是否满足系统规范

是 物理(版图)设计

物理(版图)验证

寄生参数提取及后仿真

否

是否满足系统规范

模拟CMOS集成电路设计单级放大器PPT课件

Av0

Gm Rout

gm 1 gm RS

RD

RD RS

(gmRS 1)

Amplifiers Ch.3 # 25

第25页/共55页

带源极负反馈的共源级(3)

Rup Rdown

Gm

gm 1 gmRS

Rup RD

Rdown gm1ro1RS

Rout Rup || Rdown RD (Rdown Rup )

第3页/共55页

放大器的性能指标

• 增益 • 速度(带宽、转换速率) • 功耗 • 电源电压、电源电压抑制比 • 线性度 • 噪声 • 输入摆幅、输出摆幅 • 输入/输出阻抗

北大微电子:模拟集成电路原理

Amplifiers Ch.3 # 4

第4页/共55页

模电设计中的八边形法则

北大微电子:模拟集成电路原理

信号放大

• 为什么信号需要放大? • 信号太弱,不能驱动负载:阻抗匹配 • 降低后续噪声影响 • 用于反馈电路

• 放大前后信号可同量纲,也可不同量纲

• 同量纲时放大倍数可大于1,也可小于1

北大微电子:模拟集成电路原理

Amplifiers Ch.3 # 1

第1页/共55页

放大器的种类

电流放大器

V-V

Rup

1 gm2

Rdown ro1

Rout

Rup

||

Rdown

1 gm2

|| ro1

ro1 1 gm2ro1

1 gm2

(

1 gm2

ro1 )

Av0

Vout Vin

g R m1 out

gm1 gm2

Amplifiers Ch.3 # 16

第16页/共55页

CMOS模拟集成电路分析与设计 ppt课件

如果栅电压为负,则耗尽层变薄,栅 与衬底间电容增大。

对于大的负偏置,则电容接近于CGC。

PPT课件

24

1.2 MOS管的极间电容(1)

G

S

C1

C2 C4

C3

Cbs

反型层 耗尽层

d

L

d

p型衬底

D

Cbd

PPT课件

25

1.2 MOS管的极间电容(2)

栅与沟道之间的栅氧电容:

C2=WLCox,其中Cox为单位面积栅氧电容εox/tox;

CMOS模拟集成电路分析与设计

主讲教师:吴建辉 Tel:83795677

E-mail:wjh@

PPT课件

1

教材及参考书

教材:

吴建辉编著:“CMOS模拟集成电路分析与设 计”(第二版),电子工业出版社。

参考书:

Razavi B: Design of analog CMOS integrated circuits

11

1、有源器件

主要内容:

1.1 几何结构与工作原理 1.2 极间电容 1.3 电学特性与主要的二次效应 1.4 低频及高频小信号等效模型 1.5 有源电阻

PPT课件

12

1.1 MOS管几何结构与工作原理(1)

B p+

G

tox

S

D

G D

n+

n+

p+

n阱 p型衬底

(a)

S

B

p+

n+

W

多晶

d p+接触孔

PPT课件

3

模拟电路与模拟集成电路

分立元件音频放大电路

晶体管数 匹配性 电阻值 电容值 寄生效应影响

CMOS-模拟集成电路课件-电流源与电流镜

+ VTHN+2VOD

W/(4L)

VB

-

M4

VDD

W/L

M0

W/L

M1

IREF

Z +

VOUT IOUT=IREF

W/L +

VOD -

M3

VOD -

+

W/L

+

VOD -

M2

VOD -

例4:自偏置 增加R使得 IREFR = VOD,

VGS1 = VTHN + VOD 这样,

VB= VTHN + 2VOD

IOUT

(W (W

/ L)2 / L)1

I REF

IOUT与IREF的比值由器件尺寸的比率决定,不受工艺 和温度的影响。设计者可以通过器件的尺寸比来调整 输出电流的大小。

在λ=0的情况下 !

2024/10/19

8

• 例子:

– 在电流镜电路的实际设计中,通常采 用叉指MOS管,每个“叉指”的沟道 长度相等,复制倍数由叉指数决定, 减小由于漏源区边缘扩散所产生的误 差,以减小器件的失配造成的电流失 配。.

2024/10/19

VDD IREF

+ VOD R

-

VB = 2VOD +VTHN VOUT

IOUT=IREF

+

M0 X

VOD

M3

Y+

VGS = +

VOD

M1 VOD +VTHN M2

-

16

-

小结

• 工作在饱和区的MOS晶体管可以充当电流源 • 基本电流镜—基于电流复制 • 共源共栅电流镜—提高复制精度 • 大输出摆幅共源共栅电流源—使得输出的下限等

模拟cmos集成电路设计拉扎维MOS器件物理基础PPT课件

第23页/共61页

跨导gm

VGS对IDS的控制能力 IDS对VGS变化的灵敏度

gm ID VGS VDS cons tant

• 直流关系式-I/V特性 • 交流关系式-小信号电路中的参数

第6页/共61页

MOS管简化模型

简化模型——开关 由VG控制的一个开关

第7页/共61页

MOS管的结构

Bulk(body)

源漏在物理结构上是完全对称的,靠什么区分开?

提供载流子的端口为源,收集载流子的端口为漏

最重要的工作区域?

受VG控制的沟道区

• 小信号模型 • 信号相对于偏置工作点而言比较小、不会显著影响偏置工作点时用该模型简化计算 • 由gm、 gmb、rO等构成低频小信号模型,高频时还需加上 CGS等寄生电容、寄生电阻(接触孔电阻、 导电层电阻等)

沟道电荷的产生

当VG大到一定 程度时,表面势 使电子从源流向 沟道区 VTH定义为表面电 子浓度等于衬底 多子浓度时的VG

第12页/共61页

阈值电压

0 栅与衬底功函数差

COX

OX

TOX

常通过沟道注入把VTH0调节到合适值 工艺确定后,VTH0就固定了,设计者无法改变

第13页/共61页

I/V特性-沟道随VDS的变化

第3页/共61页

掌握器件物理知识的必要性

• 数字电路设计师一般不需要进入器件内部,只把它当开关用即可 • AIC设计师必须进入器件内部,具备器件物理知识

• MOS管是AIC的基本元件 • MOS管的电特性与器件内部的物理机制密切相关,设计时需将两者结

CMOS模拟集成电路设计ch绪论实用PPT课件

模 拟 集 成 电 路 的 设 计 开 发 流 程

8

第8页/共16页

电路 设计

版图 设计

封装 测试

电路设计

9

第9页/共16页

版图设计

10

第10页/共16页

Why CMOS?

与双极工艺(BJT)相比 • 优点

• 输入阻抗大,加工成本低,低功耗,易于按比例缩小,易于实现数模混合电 路(是SOC较佳选择),设计自由度大(小信号特性依赖于器件尺寸和直 流偏量,双极只依赖于直流偏量)

15

第15页/共16页

感谢您的欣赏!

16

第16页/共16页

— 模拟电路的重要性和应用领域

自然界信号 (模拟量)

信号太小 时需要先 放大

4

滤除信号频带外的干扰

第4页/共16页

高速度、 高精度、 低功耗的 模数转换器

模拟集成电路的应用

5

第5页/共16页

结论

• 模拟电路是现代电路系统中必不可少的部分 • 数字电路无法完全取代模拟电路 • 电子产业需要大量优秀的模拟电路设计师

6

第6页/共16页

模拟电路设计的难点

• 设计关注点多:包括速度、功耗、增益、精度、电源 电压等;数字电路主要是速度、功耗

• 高精度模拟电路对低噪声、低串扰、抗干扰等要求很 高;数字电路在这方面要求低很多

• 器件的二阶效应对电路性能影响大;对工艺参数变化 的敏感度比数字电路高很多

• 设计的自动化程度低,很多靠手工设计;数字电路设 计自动化程度高

• 缺点 • 低增益,速度慢(在改善,几十GHz),噪声大(也在改善)

11

CMOS集成电路设计课件

鲁棒设计

鲁棒设计

电路性能随工艺、电源电压、温度而变化

器件模型参数的改变

阈值电压、二级效应参数 工艺角参数 TT、FF、SS、FNSP、SNFP 鲁棒设计电路性能随工艺、源压温度而变化器件模型

电源电压对器件工作区的影响

电压变化范围:20%

温度的范围

室温:25度、或50度 民品、军品

简单电路

单级放大器、差动放大器、电路偏置、电流镜电路

器件

CMOS工艺、器件物理、器件Spice参数、 *版图设计、*电路模拟

模拟集成电路设计步骤

设计要求描述

电路设计

与设计指标比较

模拟集成电路设计步骤要求描述定义与指标比

设计定义 执行设计

仿真

物理层设计 芯片设计

物理层设计 物理层验证 提取寄生参数

芯片制造

磁盘驱动器中的模块电路(C/filter …

磁盘驱动器中的模块电路(3)写发送扰码、RL编

小结

什么是模拟集成电路设计,模拟集成电路设计和分立模拟 电路与数字电路设计的区别,设计的难点。 设计步骤和直观的、层次的、鲁棒的设计。 模拟集成电路的应用、不同的信号带宽和工艺对模拟电路 的影响。 模拟信号处理系统设计和各种典型的模拟电路模块 小结什么是模拟集成电路设计,和分立 VLSI混合模拟信号电路设计举例

考核标准和联系方式

考核标准 平时作业 设计课题 期中练习 期末 联系方式

15% 15% 15% 55%

%5考核标准和联系方式1

导论

1.1 模拟集成电路设计的特点

层次化设计 设计步骤 鲁棒(robust)设计

1.2 模拟集成电路的应用 导论1.模拟集成电路设计的特点层次化2 1.3 模拟信号处理 1.4 混合信号电路举例

模拟CMOS集成电路设计(毕查德·拉扎维著,陈贵灿等译,西安交通大学出版社) 绪论课件

模拟CMOS集成电路设计教材n模拟CMOS集成电路设计,毕查德.拉扎维著,陈贵灿等译,西安交通大学出版社参考资料n半导体集成电路,朱正涌,清华大学出版杜n CMOS模拟电路设计(英文),P.E.Allen,D.R.Holberg,电子工业出版社n模拟集成电路的分析与设计,P.R.Gray等著,高等教育出版社半导体集成电路发展历史n1947年BELL实验室发明了世界上第一个点接触式晶体管(Ge NPN)半导体集成电路发展历史n1948年BELL 实验室的肖克利发明结型晶体管n1956年肖克利、布拉顿和巴丁一起荣获诺贝尔物理学奖n50年代晶体管得到大发展(材料由Ge→Si)半导体集成电路发展历史n1958年TI公司基尔比发明第一块简单IC。

n在Ge晶片上集成了12个器件。

n基尔比也因此与赫伯特·克勒默和俄罗斯的泽罗斯·阿尔费罗夫一起荣获2000年度诺贝尔物理学奖。

半导体集成电路发展历史n19世纪60年代美国仙童公司的诺依斯开发出用于IC的平面工艺技术,从而推动了IC制造业的大发展。

半导体集成电路发展历史n60年代TTL、ECL出现并得到广泛应用n1966年MOS LSI发明(集成度高,功耗低)n70年代MOS LSI得到大发展(出现集成化微处理器,存储器)n80年代VLSI出现,使IC进入了崭新的阶段。

n90年代ASIC、ULSI和巨大规模集成GSI等代表更高技术水平的IC 不断涌现,并成为IC应用的主流产品。

n21世纪SOC、纳米器件与电路等领域的研究已展开n展望可望突破一些先前认为的IC发展极限,对集成电路IC的涵义也将有新的诠释。

集成电路用半导体工艺,或薄膜、厚膜工艺(或这些工艺的组合),把电路的有源器件、无源元件及互连布线以相互不可分离的状态制作在半导体或绝缘材料基片上,最后封装在一个管壳内,构成一个完整的、具有特定功能的电路、组件、子系统或系统。

模拟集成电路n1967年国际电工委员会(IEC)正式提出模拟集成电路的概念,它包括了除逻辑集成电路以外的所有半导体集成电路。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

PPT学习交流

6

5

2、集成电路工艺

速度高, 功耗大, 集成度低

最早MOS工 艺,速度低

超高速、高频 IC

光电集成器件

主流工艺,集 成度高、功耗 低、速度快、 抗干扰性强

PPT学习交流

7

6

CMOS工艺

B

S

G

D

B

S

G

D

n+

n+

p+

p+

p 型衬底

n 型阱

n 阱CMOS工艺

B

S

G

D

20

沿沟道x点处的电荷密度为: 沟道x点的电势,以源级为参考点

电流为:

载流子为电子,电荷为负,电荷运动方向与电流 方向相反

其中: 得到:

v=μE μ为载流子的迁移率,E为电场 E=-dV(x)/dx

PPT学习交流

22

21

在整个沟道长度内积分得:

由于ID沿沟道方向是常数,因此:

电流随VGS的 增大而增加

漏极的反型层消失,出现由耗尽层

构成的夹断区。

➢电子沿沟道从源极向漏极运动,达

到夹断区边缘时,受夹断区强电场

的作用,很快漂移到漏极。 B

➢VDS的变化主要体现在夹断区上,

p+

对沟道长度和沟道内的场强影响不

大,因此可以近似认为沟道电流保

p-

持恒定。

VDS

-+

-+

VGS

G

S

D

n+

n+

夹断区

PPT学习交流

20

19

2、NMOS 管IV特性推导与分析

(1)IV特性推导

Id

载流子从源级运动至漏极,设沟道中的电流为I,沿电流 方向的的电荷密度为Qd(C/m),电荷移动的速度为v (m/s),则

当VGS=VTH时,开始形成反型层,其电荷密度正比于VGS- VTH 。

单位长度总电荷

单位长度总电容 PPT学习交流

21

(2)IV特性分析

过驱动 电压

沟道长度

沟沟道道宽宽度度

PPT学习交流

13

12

PPT学习交流

14

13

1.3 MOS管工作原理

PPT学习交流

15

14

(一)NMOS管工作原理

1、工作原理 D

(1)VGS =0

-两个有源区被衬底分 隔,等效于背靠背的

B

v

D

+

S

-

G

+ -

vS GS

v DS

-+

vGS

-+

G

两个PN结

B

S

D

-源极和漏极之间没有

B

p+

➢VGS电压越大,电场EV越强,吸引的电

子越多,导电沟道就越厚。

p-

➢导电沟道出现后,若VDS=0,还不能 产生沟道电流。

VDS -+

-+ VGS

G

S

D

n+

n+

反型层

PPT学习交流

18

17

(3)当VGS>0,VDS>0

➢如果VDS >0,则电子从源极向漏 极移动,产生了沟道电流ID。

➢同时,由漏极沿沟道至源极将产生

p+

电流。

p-

n+

n+

耗尽层

PPT学习交流

16

15

(2)当VGS>0,VGB>0,VDS=0

➢ 衬底中的电子受到吸引,向衬 底表面运动;空穴受到排斥,向 衬底内部运动。向上运动的电子 与表面的空穴复合,形成了一层 耗尽层,形成一个栅极指向衬底 的垂直电场EV 。

➢随着VGS的升高,电场EV越来越

强,表面层吸引的电子越来越多, B

压降,栅极与沟道中各点的电压差

不再相等,栅极与源极之间的电压

VGS最高,和漏极之间的电压VGD最 B

低。

p+

➢沟道中垂直方向的电场EV沿源极到 p漏极的方向逐渐变弱,导致沟道越

来越窄。

VDS -+

VGS S

n+

+ G

EH

D n+

ID

PPT学习交流

19

18

➢漏极电位进一步上升, 当

VDS≥VGS-VTH时,即VGD<VTH,

耗尽层也越来越厚。

p+

p-

VDS -+

-+

VGS

G

S

D

n+

n+

EV

PPT学习交流

17

16

➢当VGS 增大到一定值时,在耗尽层和绝

缘层之间形成一个N型薄层,称为“反

型层”。

➢该反型层将漏极和源极两个N+有源区 连通,构成了源漏之间的导电沟道。

➢刚好产生反型层所需的VGS电压称为阈

值电压或开启电压(Vth)。

电子(便携)设备的需求 —减小尺寸、重量 —降低功耗 —提高可靠性

系统集成的需求 —SOC (System on a chip) —模拟/混合信号集成电路设计的需要

PPT学习交流

5

4

(3)模拟/混合信号IC发展趋势和主流应用方向

发展趋势: —高速 —高精度 —低功耗 —小尺寸

主流应用方向 无线通信系统、蜂窝手机、数字电视、数码相机、

综合 门级仿真 自动布局布线 物理验证 后 仿真 制版流片 封装测试

单元库

逻 辑 及 电 路 单元库 设 计

版 图 设 计

数字ASIC设计流程

PPT学习交流

10

9

1.2 金属氧化物半导体晶体管(MOSFET)

PPT学习交流

11

10

MOSTET,导电性由电容控制的器件。

◦ 电容上的电压用来控制导电沟道电流强度。

◦ 氧化层构成控制电容

栅极

源极

L

S

G

D

n+ p

衬底或(硅)体B

CGC

CBC

氧化层

导电沟道 Leff

n+ 耗尽层

漏极

当Vgs>Vth时, 形成一个N型的 反型层(少子), W 构成导电沟道。

通过Vgs、Vds 电压控制导电沟 道中的电流强度。

NMOS管结构

PPT学习交流

12

11

MOS晶体管的版图和电路符号

B

S

G

D

n+ p 型阱

n+ p 阱CMOS工艺

p+

p+

n 型衬底

双阱工艺(集成N阱、P阱),提高器件密度,抑制

寄生晶体管影响以及闩锁现象。

PPT学习交流

8

7

3、 模拟集成电路设计流程

设计目标和性能要求 确定电路拓扑结构和初始

器件参数

仿真验证电路性能

版图设计 版图参数提取

测试方案设计

芯片制造 测试与分析

模拟CMOS集成电路设计

Design of Analog CMOS Integrated Circuit

PPT学习交流

1

Institute of VLSI Design, Hefei U.of Tech

第一讲 基础知识

PPT学习交流

2

1

1.1 概 述

PPT学习交流

3

2

1、为什么需要模拟集成电路?

(1)为什么需要模拟电路

处理自然界信号

自然界的信 号大多是模

拟信号

—信号的采集、接收、放大、滤波

(传感器、无线射频接收器、放大器、模拟滤波器)

数字信号处理链路必需且重要的器件

—模拟信号到数字信号的转换,如ADC

—数字信号到模拟信号的转换,如DAC

模拟集成电路的重要性

PPT学习交流

4

3

(2)为什么要集成

电路设计

仿真占用大量设计 时间

需要对工艺、器件、 修 改 电 路 参 数 、 拓 扑 电路的深入理解

பைடு நூலகம்

在各个不同的设计

阶段都需要知识和

工

经验

艺

模拟集成电路设计

是基于电路知识和

经验之上的艺术创

造

PPT学习交流

9

8

系统要求

系统设计和

系

功能划分

统

及

功

系统仿真

能

级

寄存器传输

设

级(RTL)设计

计

功能仿真