I 2C总线在数据采集器的FPGA实现

基于FPGA中I 2C总线模块的情确懈统

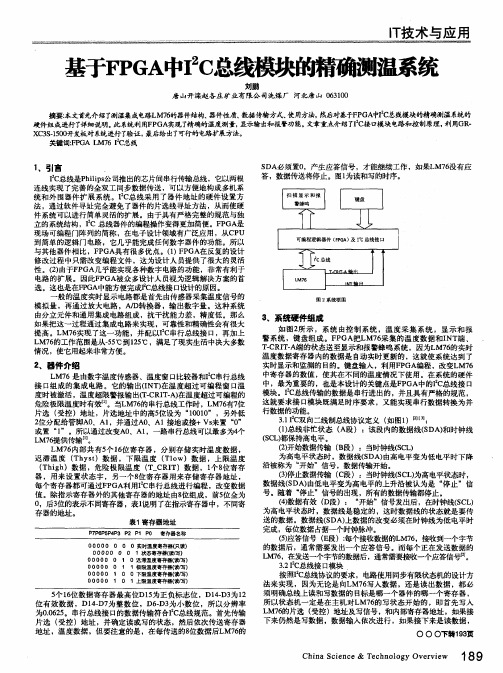

S DA必须 置0 ,产生 应答 信号 ,才 能继 续 工作 ,如果 L 6 有应 M7 没 答 ,数 据传送 将停 止 。图1 为读和 写 的时序 。

扫 描 显 示和报

警 蜂 鸣

键Hale Waihona Puke T 可编程逻辑器件 ( P A 及 I F G ) ℃总线接 口

可 。 总 线

L 6 M7

X 3 。 0 开发板对系统进行了 证, C S1 0 5 验 最后给 出了 可行的 电路扩展方法。 关键词: G M7 C F A L 6 I 总线 P 2

1 引言

I 总线是 P i p ̄ 推 出的芯 片间 串行传输 总线 ,它 以两根 2 C hl s i 连 线 实现 了完善 的全 双 工 同步数 据 传送 ,可 以方 便 地构 成 多机 系 统 和 外 围器 件扩 展 系 统 。I 总 线 采 用 了 器件 地址 的硬 件 设 置方 2 C 法 ,通过 软 件寻 址 完全 避免 了 器件 的片 选线 寻址 方 法 ,从而 使硬 件 系统 可以 进行 简 单灵 活的 扩展 。由于 具有 严格 完 整 的规范 与 独 立 的系统 结构 ,I 总 线器 件的 编程操 作变 得更加 简便 。F G 是 2 C P A 现场 可 编程 门阵 列 的简 称 ,在 电子 设计 领域 有广 泛应 用 ,从CP U 到 简单 的逻 辑 门 电路 , 它几乎 能完 成 任何数 字 器 件的 功能 。所 以 与 其他 器件 相 比 ,F GA 有 很多优 点 。() P 在 反 复的设 计 P 具 1 F GA 修 改过 程 中 只需 改变 编程 文件 ,这为 设计 人 员提 供 了很 大的 灵活 性 。() 2 由于F G P A几乎 能 实现 各种 数 字 电路 的功 能 ,非 常有 利于 电路 的 扩展 。因此 F G P A被 众多 设 计人 员视 为 逻辑 解 决 方案 的首 选 。这 也是  ̄F G E P A中能方 便完成 托 总 线接 口设计 的原 因。 般 的温 度 实时 显示 电路 都是 首先 由传 感 器采集 温 度信 号的 模 拟 量 ,再 通过 放 大 电路 ,A D转换 器 ,输 出数 字 量 。这 种 系统 / 由分立 元 件和 通用 集 成 电路组 成 ,抗 干扰 能 力差 ,精 度 低 。那 么 如果把这一过程通过集成电路来实现 ,可靠性和精确性会有很大 提 高 。L 6 M7 实现 了这一 功能 ,并 配以I 串行 总 线接 口,再加 上 2 c L 6 工作 范 围是 从一52 15 ,满 足 了现实 生活 中决大 多数 M7 的 5 X ̄ 2 E 情 况 ,使它用 起来 非常方 便 。

基于FPGA的I2C控制器的实现

I mp l e me nt a t i o n o f 1 2 C Co n t r o l l e r Ba s e d o n FPGA

W ANG Lo n g-f e i , LANG Ba t—h ua

( S c h o o l o f E l e c t r o n i c I n f o r ma t i o n E n g i n e e r i n g , X i ’ a l l T e c h n o l o g i c a l U n i v e r s i t y , X i ’ a n 7 1 0 0 2 1 机 技 术 与 发 展

COMPU TER TEC HNOLOGY AND DEVEL 0P MENT

2 0 1 3年 3月

Vo1 . 2 3 No . 3 Ma r . 20l 3

基于 F P GA 的 1 2 C控 制器 的 实现

王龙飞 , 郎宝华

i n i t i l a i z a i t o n s t a t e r t ns a i t i o n d i a g r a m, i f n l a l y u s e t h e Qu a r t u s s o f t w re a f o r s i mu l a t i o n , he t e x p e r i me n t s s h o w t h a t d a t a r t ns a m i s s i o n c o mp l i e s

Ab s t r a c t : Th e p u r p o s e i s t o s t u d y t h e I 2C b u s , i t h a s he t i nt e r f a c e c a b l e a n d c o n ro t l s i mp l e d e v i c e s a r e pa c k a g e d i n s ma l l , h i g h e r c o ml n u- n i c a t i o n s p e  ̄ . . d。 e r e, s o s e l e c t t he S AA7 1 1 3 a s v i d e o d e c o d e r c h i p. I t g i ve s a矾 e f a c c o u n t o f he t d a t a t r a n s mi s s i o n t i mi n g o f t h e I 2 C b us p r o t o c o l 。 he t b a s i c f u n c t i o n s o f he t a n a l o g v i d e o d e c o d i n g c h i p S AA71 1 3 wo r k s a nd a s s o c i a t e d r e g i s t e r s e t , nd a p r e s e n t s a S AA7 1 1 3 i n i — t i li a z a t i o n a p p r o a c h ba s e d o n F P GA , o v e r v i e ws e a c h mo d u l e o f he t I 2 C b u s i n d e t a i l , nd a i s g i v e n i n he t r e g i s t e r c o n ig f u r a t i o n o f he t c h i p

基于PCI和FPGA的高速数据采集系统

新技术·新业务DOI:10.3969/j.issn.1006-6403.2023.08.014基于PCI和FPGA的高速数据采集系统[张四维 王勋志 谭静波]为了准确、实时地采集工业现场快速变化的数据,设计了一种基于外设部件互连标准(Peripheral Component Interconnect,PCI)和FPGA的高速数据采集系统,系统主要包括高线性度模拟光耦模块、高速模数转换模块、同步动态随机存储器控制模块、PCI通信模块、FPGA及其软件系统等。

系统把PCI总线具有的兼容性强,数据传输快等特点和FPGA具有的灵活可编程性结合起来,并引入了高线性度的模拟光耦模块和具有流水线结构的高速模数转换器(THS1206),使系统具有传输速率高、数据处理能力强和抗电磁干扰能力强等特点,仿真和实验结果验证了设计的正确性。

张四维湖南省交通规划勘察设计院有限公司,本科毕业于郑州轻工业大学,主要研究方向为嵌入式系统设计。

王勋志湖南省交通规划勘察设计院有限公司,硕士毕业于中南大学,主要研究方向为嵌入式系统设计。

谭静波湖南省交通规划勘察设计院有限公司,本科毕业于湖南科技大学,主要研究方向为嵌入式系统设计。

关键词:数据采集线性光耦 THS1206 FPGA PCI摘要1 引言在信号处理技术中,数字信号的处理是主流及趋势;而在数字信号处理技术中起关键性作用的就是前期的数据采集工作。

工业现场常常有一些快速变化的数据需要采集,根据香农采样定理,采样频率应该不小于模拟信号频谱中最高频率的2倍,故要求数据采集系统要有高的采集速率。

与此同时,高速采集到的大量数据也需要及时或是实时进行处理,这对采集系统的数据处理器的性能有高的要求。

外设部件互连标准(Peripheral Component Interconnect,PCI)总线是目前最先进的计算机总线之一,具有兼容性强、功能全、传输速率快等特点,它不受限制于具体的处理器,可以为高速的外围设备与中央处理器(CentralProcessing Unit,CPU)之间提供高性能、高吞吐量的数据通路[1]。

基于FPGA的I 2G总线接口实现方法

B_ 【

罔 I C标 准 城 L协 议 F l I 2 6 半导薄 裢 末茅 1 7誊 苇 ! 期

维普资讯

杰 自 由 } 售芒 At。 o 设 与 现 回Tn , 计 实 b F c锄 r a

:

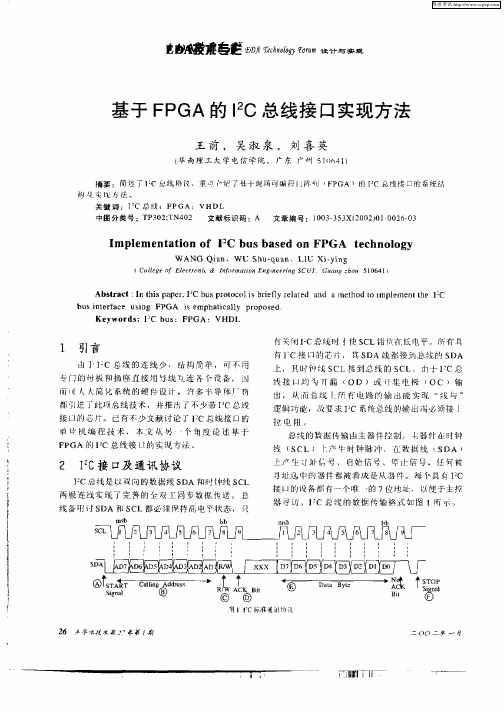

器 发 出 启 始 信 号 后 S CL 为 高 u

上 , 其 时 钟 线 S L 接 到 总 线 的 S L 由十 l 总 C C ! c 线 接 u均 为 丌 漏 ( 0D ) 域 行 集 电 极 ( C ) 输 0 出 , 从 而 总 线 所 有 电 路 的 输 出 能 实 现 “ 与 ” 线 逻辑功 能 ,一要求 I : C系 统 总 线 的 输 出 端 必 须 接 』

A bsr c : n t i a e IC bu r t oli re l e a e a d eho oi p e e tt IC t a t I h sp p r 2 sp o oc sb i fy r lt d n am t d t m l m n he 2 bu n e f c usn FPG A i m p tc ly si t r a e ig se ha i a l pr p e o os d Ke ywor : 1 C ds bus: FPG A ; V H DL 2

s DA

块 :IC控制模 块 和 I ! C数 据 传输模 块 。为 实现 计 R 的 数 据 , 方 面 网 c 语 言编 写 对 S NS E OR 写 控 制 数 据 和 读 sEN so R 状 态 信 息 的 界 面 程 序 , 另 一 方 面 用 VHDL编 实 现 1 总 线 协 议 的程 序 。 根 据 1C通 2 C 2 讯 协 议 和 S NS R 的 技 术 资 料 I 计算 机 通 过 I A E O , S 插 槽 往 S NS R 控 制 数 据 的 顺 序 足 : 先 送 S N E O ; E . S OR 的 器件 地 址 , 再 送 S N OR 内部 某 个 寄 存 器 E S 的地址 ,最后送 控 制数据 。 为 木 系 统 是 + , 的 从 I 总 线 系 统 , 分 配 3个 计算 机 的 I 口 ( 3 0 ℃ / O 0 0 H、 0 1 、 0 0 H )给 F GA 上 的 IC 控 制 模 块 , 3 H 0 2 3 P

基于FPGA技术的电子式互感器数据采集系统的实现方法

基于 F G P A技术的电子式互感器数据采集系统的 实现 方法

李俊 ’刘 淮 霞 ’朱 丹 贺 曼

(. 徽理 工大 学 电气 与信 息 工程 学 院 安徽 淮 南 220 ;2西安 交通 大 学 电 气工程 学院 陕 西 西安 70 4) 1 安 301 . 109

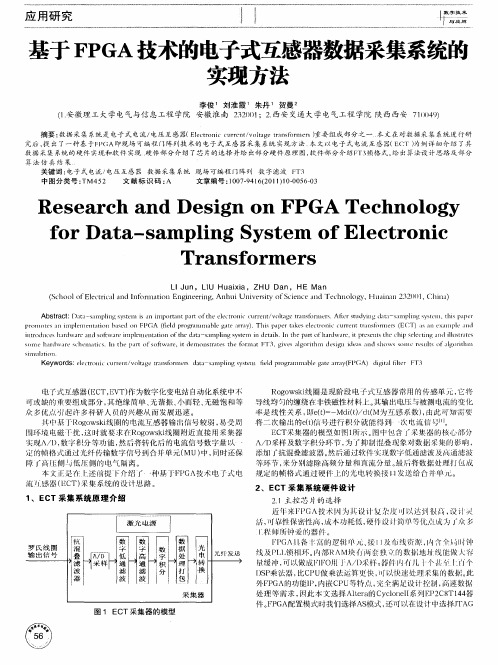

摘 要 : 据 采集 系统是 电子式 电流 / 数 电压 互感 a Ee t ncc r n / o a et n ̄rlr ) g l r i ur tv l g r s) l s 重要 组成部 分之 一 本 文在 对数据 采 集 系统进 行研 ( co e t a le 究后 , 出了一 种基 于F G 提 P A即现 场 可编 程 f 阵 列技 术的 电子 式互 感 器采 集 系统 实现方 法 本 文以 电子 式 电流 互 感器( C ) 详细 介绍 了其 1 E T 为例 数据 采 集 系统的硬 件 实现和 软件 实现 硬件 部 分介 绍 了芯 片的选择 并给 出部 分硬 件原 理 图 , 软件 部 分介 绍F 3 T 帧格 式 , 出算 法设计 思路 及部 分 给 算 法 仿 真 结 果 关键 词 : 电子式 电流/ 电压互 感 器 数据 采 集 系统 现 场可编 程 门阵 列 数 字滤 波 F T3

i to uc sh r wa e al o t r n p e 1 ntt0 ft e d t —s l ln y t m n dea l n t a t h r wa e i pr s nt t e c i e e tn ll l sr t s n r d e a d r ld s fwa e i l l c i n o h aa anp i g s se i t i I hep r of a d r , t e e s h h p s lc i g ̄ d i u ta e 1 、 s l l S} 1 r {1 C ha dwa e s he a i s n t a tofs fwa e td l O ta e h m na T3 i s ago ih de i n i e s a lO V {l e r s t l ort 1 r c m tc .I he p r o t r ,i e l nsr t s t e G l t F ,g ve l rt m sg d a nd sI \ S S} l e ul ofag i } s hm

基于FPGA的数据采集系统设计与实现

了异步传输 中跨时钟域造成的亚稳态问题 [ 5 1 。在本 数据采集系统的设计中采用异步 FF IO的方式来解

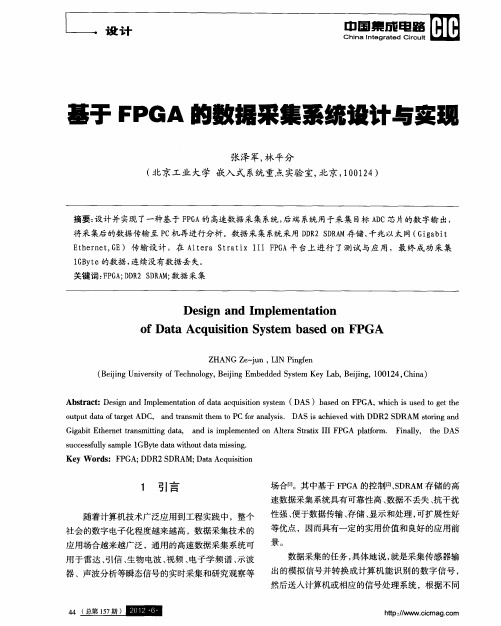

图 2 数 据 采 集 系统 数 据 流 程

决跨时钟域 的数据传输 问题 。因为本数据采集系统 是针对 A C芯片的测试所用的, D 因此数据采集接 口 的数据率不是 固定 的 10 H x4i 而 D R 控制 5M z5b , D 2 t 器的用户接 口和 G E控制器接 口数据率是 固定的 , 分别为 10 H x 1b 和 15 z 2i 5 M zl2i t 2MH x b ,所 以选用 3 t 异步 FF IO可以使 系统更加灵活。

基于 F GA的数据采集系统设计与实现 P

张 泽 军 , 平 分 林

( 北京工业 大学 嵌入式 系统重点 实验 室, 北京, 1 4 102 ) 0

摘要 : 设计 并 实现 了一种基 于 FG P A的 高速 数据 采 集 系统 , 端 系统 用于采 集 目标 A C芯 片 的数 字输 出, 后 D 将 采集后 的数据传 输 至 P C机再 进行 分析 。数据 采 集 系统 采用 DR D A 储 、 兆 以太 网 ( ia i D 2SRM存 千 G gb t

数据传输及控制。同时 , 模块还负责 G I F E控制器、

图 1数 据 采 集 系统 框 图

D R D 2控制 器 的用户 总线及 外 部数 据采 集 接 口之间

h¨ n . h n nA 、 ,m a , , n / s A i, ;、 1 、

L一设 — 计

巾国集成电路

Chi na nt I eg r ed icu i at C r t

块 ,其 功 能 相 当 于 一 个 D MA ( i c M m r Dr t e oy e

毕业设计(论文)-利用VHDL语言在FPGA上实现I2C总线控制器的功能模板

摘要随着微电子技术的发展,现场可编程逻辑门阵列FPGA(Field Programmable Gate Array)可以实现数字电路系统设计的功能。

尤其现场可编程逻辑门阵列FPGA具有集成度高的优点,受到工程界高度的重视。

I2C 总线以接口简单,成本底,可扩展性好在数字系统中得到了广泛的应用。

硬件描述语言是数字系统高层设计的核心,是实现数字系统设计新方法的关键技术之一。

本课题正是利用VHDL语言在FPGA上实现I2C总线控制器的功能。

首先研究了I2C总线的规范,又简要介绍了QuartusⅡ设计环境以及FPGA 的设计流程。

在此基础上,重点介绍了I2C控制器的总体设计方案,以及在QuartusⅡ平台上的时序仿真。

关键词Quartus II;I2C总线控制器;现场可编程逻辑门阵列;时序仿真AbstractWith the development of micro electric and EDA(electronic design automation)technology, FPGA(field programmable gates array) can realize the function of digital circuit system design .FPGA have the merit of filed programmability and High integration rate ,therefore is highly recognized for engineering.I2C bus is widely applied in the digital system as simple interface ,expedient use ,low cost and good expansibility .VHDL is considered as a core of digital system design and a key technique of implement digital system.The design realizes the function of I2C bus interface on the FPGA .At first the thesis deeply research I2C bus specification ,then briefly introduce the Quartus II design environment and the design method ,as well as FPGA design flow .In this foundation,I2C bus controller design scheme and the timing simulation under Quartus II is particularly introduced.Key words Quartus II;I2C bus controller ;FPGA ;timing simulation目录摘要 (I)Abstract .................................................................................................................. I I 第1章绪论.. (5)1.1 课题背景 (5)1.2 I2C总线的产生及发展 (6)1.3 FPGA的现状与展望 (6)1.4 相关工作 (6)第2章I2C总线技术的研究 (8)2.1 I2C总线的概念 (8)2.2 I2C总线的传输 (9)2.2.1 数据的有效性 (9)2.2.2 I2C总线数据传送的开始和停止条件 (9)2.2.3 I2C总线传输过程中的应答信号 (10)2.2.4 I2C总线数据传送的重复开始条件 (11)2.2.5 I2C总线的传输过程中的字节格式 (11)2.2.6 I2C总线的器件子地址 (11)2.2.7 I2C总线传输信号的时序 (12)2.3 本章小结 (14)第3章VHDL语言的基础知识 (15)3.1 VHDL语言的概述 (15)3.2 VHDL语言的特点 (15)3.3 VHDL语言的程序结构 (16)3.3.1 VHDL程序的库 (16)3.3.2 包集合 (16)3.3.3 实体说明 (17)3.3.4 构造体 (18)3.3.5 配置 (18)3.4 本章小结 (18)第4章设计工具和设计方法 (19)4.1 设计工具 (19)4.2 基于FPGA的数字电路的设计流程 (20)4.3 本章小结 (21)第5章I2C总线的功能设计 (23)5.1 I2C总线完成的功能 (23)5.2 用VHDL语言实现写操作时的串行转并行 (24)5.3 用VHDL语言实现顺序读操作时的并行转串行 (24)5.4 I2C总线控制器的顶层设计 (25)5.5 本章小结 (26)第6章I2C总线的硬件时序仿真 (27)6.1 器件的选择 (27)6.2 硬件仿真 (28)6.2.1 用VHDL语言实现写字节周期 (29)6.2.1 用VHDL语言实现顺序读字节周期 (30)6.2.3 用VHDL语言实现选择性读字节周期 (30)6.3 本章小结 (31)结论 (32)致谢 (33)参考文献 (34)第1章绪论1.1 课题背景近年来,随着社会的发展,电子产品越来越多的进入人们的生活和工作中,成为了我们生活中必不可少的一部分,随着计算机的普及,以及电子设备之间相互沟通的更加频繁,为了更方便的实现器件与器件之间的通信,研发人员从消费者电子、电讯和工业电子中许多看上去不相关的设计中寻找到了他们的相似之处,例如几乎每个系统都包括:(1)一些智能控制,通常是一个单片的微控制器。

用FPGA实现低成本高性能数据采集和控制卡

E PF G C P A中独特 的 D P S 模块

在 分析 寅际 应 用 结 卞1S GA 中 的独 特 灵 活 的 l t EC — ) P FP ie i

D P 块 足很 有帮 助 的 . 种模 块经 过配 呵 以 S模 . 这

维普资讯

0U TLO O K

用F G P A实现低成本高性能数据采集和控

制卡

法 当今f场的 力迫使数据采集干控制 卜的 订 I I 几论哪种 ‘ ,都会人大地增 电路板的成本。 供 商 住增加数据采集 的墒道数 提高采样 数据采集和控制卡的基本结构 频率的同l , { 还晏号虑降低成本。l时应使 } l 『 I i 】 、 的 实际功能可 生产或行 系统配置时决定 . 木 _ 义挺 f 的体 系结 构 能够 在给定 的 D P “ S

0 I t j I \ ( C 0 \ J、 } i 1 I【 、 I l )I i \ 、 I \ l { I( I { t I 』l】f \ \ t 、 、《l t

,

图 1 数 据采 集

芯 ”) 崩 功 能 为强 大的处 器 来 实现 或使 H

通信等1 r,任r新增 的处 要求 只能 l F ・ 1 u 』 i ~ 代 I

的 、 备 r 昂贵的 D PC U的数抛采集 卡来 S P

完 成 J 种 l选 案 是通 过 减 少 输 入通道 数 一 1 J ‘ 来处 额 外 的 _作 r

衍号分析 、 视频处叫 、压缩等实际 I P ) 功能泊 采样数槲 .从 边 "始。多个高频模 拟信 弓被 S 0 时 就越 少 J A C板块 化,涵过一个 I D 棱 l被传送到 D i _ S h V l l I 下 I P处 理 擀不 得 小从 一 个通 道 切换 刨 } ) I S FG P A巾 F ( 通过 1 将数掂 接传送圳连 P ) MA 下一个通道 , 闪此 , 高速缓存器将进一步降低町 任 DS P 的 S AM I I PC U川来 处理 PC I J R ) P S

基于FPGA的I2C SLAVE模式总线的设计方案

基于FPGA的I2C SLAVE模式总线的设计方案

0 引言

由于在嵌入式系统开发中越来越多的应用到FPGA,而一些嵌入式CPU,比如STM32 为了降低成本,减小封装尺寸,没有外接专门的CPU 读写总线,而只提供了一些如SPI 和I2C 的接口。

而且在应用中经常有数据要配置到FPGA 中,如FPGA 中的应用配置寄存器,和配置表项等,都需要CPU 配置。

这些数据的数据量不大,速度也不要求很高,很适合用I2C 总线来配置。

I2C 总线是Philips 公司设计的一种控制和配置内部IC 双向两线的串行总线。

主要特点是接口信号线较少,但是其数据的传送速率不是很高,其高速模式下为3.4Mb/s.应用于配置FPGA 比较适合。

在通常的应用中嵌入式CPU 作为MASTER 模式的主器件,FPGA 作为SLAVE 模式的从器件。

通过使用I2C 总线,减少了CPU 和FPGA 的连线,而且嵌入式CPU 一般有内含I2C总线控制器,使得CPU 和FPGA 间的通讯硬件电路简化。

1 I2C SLAVE 模式整体结构的分析设计。

PCI总线协议的FPGA实现及驱动设计

PCI总线协议的FPGA实现及驱动设计摘要:采用FPGA技术,在ALTERA公司的FLEX6000系列芯片上实现了从设备模式PCI总线的简化协议,并给出了Windows9x系统下的虚拟设备驱动程序,提供了与应用程序的接口。

实现结果表明:该设备结构灵活,功能可靠,有利于与其它模块实现单片集成应用。

本系统已应用在数据采集和处理、图像处理等方面。

关键词:PCI总线协议现场可编程门阵列虚拟设备驱动目前,许多公司都提出了新型的计算机高速总线,如Arapahoe总线标准和HyperTransport技术,但各协议互不兼容,没有形成统一标准。

作为传统的通用局部总线,PCI总线仍然占据着主流个人电脑市场,具有顽强的生命力。

现在市面上存在着各种PCI接口芯片,如AMCC公司的S5933,PLX的9080系列等。

专用芯片可以实现完整的PCI主设备与从设备模式的接口功能,将复杂的PCI总线接口转化相对简单的用户接口,但系统结构受接口芯片的限制,不能灵活地设计目标系统,且成本较高。

本文使用符合PCI电气特性的FPGA芯片进行简化的PCI接口逻辑设计,实现了33MHz、32位数据宽度的PCI从设备模块的接口功能,节约了系统的逻辑资源,且可以将其它用户逻辑集成在同一块芯片,降低了成本,增加了设计的灵活性。

另外,还给出了Windows9x系统下的设备驱动程序,可以与应用程序接口,形成一个完整的系统。

目前,本系统已经被印染企业应用在数据采集和处理等方面。

1 系统构成与功能描述系统的总体框图如图1所示。

由图1可见,系统的硬件平台为一块PCI卡。

此卡的结构十分简洁,主要由FPGA芯片、RAM芯片和输出接口三部分组成。

其中,FPGA 芯片集成了PCI接口模块和数据处理模块。

PCI接口模块实现了33MHz工作时钟、32位总线宽度的接口功能,支持I/O空间、内存空间及配置空间的读写和PCI中断功能。

由于简化的PCI接口占用的逻辑资源较少,可在同一块芯片中集成其他用户逻辑。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

作 者 简 介 : 垣 , 18 一) 上 海 大 学 机 电工 程 与 自 动 化 学 院 硕 士 研 究 范 (9 1 . 生 . 究方 向 : 研 电机 控 制 ; 渝 曾 , 海 大 学 机 电 工 程 与 自动 化 学 院 教 李 上 授 . 究方 向 : 制理 论 与 控 制 工 程 。 研 控

() 6 4 : 8—7 . 1

[ ]张少军 , 1 杜金城. 交流调速原 理及应用 [ . M] 北京 : 国电力 中 出版社 ,03 20 . [] 2 王树. 变频调速 系统设计与应用 [ . M] 北京 : 机械工业 出版社 ,

20 0 5,8 4—1 4. 0

[] 3 王妍 ,杜军 红.基于 D P 的空间 电压矢 量法 P S WM 的 研究 [] 电机与控制学报 , 0 4 ( ) 9 — 0 . J. 2 0 ,2 :8 1 1 [ 4]周卫平 , 吴正圈等.V WM的等效算法及 S P SP V WM与 S WM的本 P 质联 系 []中 国电机 工程学 报 , O , 6 2 )13—1 . J. 2 6 2 (6 :3 3 O 7

维普资讯

口应用 实例口

参考文献

仪 器仪 表用户

[] 5 熊健,康勇 ,张凯 . 电压 空间矢量 凋制 与常规 S WM 的 比较 P 研究 [ 电力电子技术 ,19 ( ) 2 2 . J. 9 9,1 : 5— 8 [] 6 田亚菲 , 何继爱 ,黄智武 . 电压空间欠量 脉宽 凋制 ( V WM) SP 算法仿真研究及分析[ ] 电力系统及其 自动化学报 , 0 4 J. 20 ,

收 稿 日期 :0 7—1 20 2—1 ( 0 6) 2 83

文章编 号:6 1 8 o 0 7 0

1 C 总线 在 数 据 采 集 器 的 F G 实 现 2 P A

罗 华 阳

( .湖南铁路 科技职 业技 术学 院 ,湖南株 洲 4 2 0 2 1 1 0 0; .湖南 大学 电气 与信 息工 程学院 , 湖南 长沙 4 0 8 ) 1 0 2

摘 要 : 于 A im D s nr 发 平 台 。 基 hu ei e 开 g 采用 原 理 图 实 现顶 层 模 块 及 主 电

路 图 . HD V L语 言 实现 控 制 电路 和 各 部 分 接 口 电 路 两 级 设 计 的方 法 实

j ≥

j i;

…

I

…

( .C H g f lcr a a dIfr t nE gneig 1 o e eo et cl n noma o n ier , E i i n

Hu a i e s y,Ch n s a 4 0 8 Ch n n n Un v r i t a g h 0 2, i a; 1 2 Hu a i y P o e so l c n lg l g , . n n Ral wa r f s ina Te h o o y Col e e

LU0 ua y H - ang

主器件 发出启 始信号后 ( C S L为高时 ,D S A出现下 降沿) , 接着 发送 寻址 信号( 7位的从器件 地址 和数据 方 向位 H w 由 / 组成 , 其中 R W =O 明数据发送 到从器件 ; / =1表 明主 / 表 RW 器件读取 从器 件 的数 据 ) C 。A K为应 答信 号 , 时 主 器件 在 此 S L线上产生一 个应 答脉 冲 , C 当被选 中的从器 件 接收 到数据 后, 从器件将 S A线拉低 , D 这时主器件町以继 续发送数据 。当 从器件 由于某 种 原 因不 产生 应答 信 号或 全部数 据 传送 结 束 后 , 控 器 可 产 生 一 个 停 止 信 号 来 终 止 总 线 数 据 传 输 。 此 时 主

} { I 【

… 一 ‘ “

I

~

一

现数据采集器 . 其中 A D、 / / D A转换芯片与 系统主控电路采用 IC总线 2 方式实现。文章给 出了主体硬 件图和 1C总线的部分实现程序 。

关 键 词 :hu einrIC总 线 :P A A im D s e: g FG

Zh z o 2 0 Chn u h u41 0 0, i a)

Ab ta t s rc :Un er t m sin 6 0d v op nt af r .te m ut d i Alu De g er. e el me tom pl h l- i c a e t c iions se i o o e h nn l daa a qust y tm sprp s d,whcht — v due i i op l el e mo l r ale ys h e i d b c emai d c n rl i uta d itra eci utr ale z t an o to r i n ne c r i e i d c cc f c z b y VHDL.Th e mai rwa e cr ian h o a me o C u n had r i t d te prgrm cu fI b s ar e e t nt i ap . e prs ned i hs p er K r s:AIu Desgn . eyWO d t m i i er I b s;FPGA C u

一 一

l

3

j 最

j

。

?

§

{

中图分类号 : P 7 T 2 4+. 2

文献标识码 : B

图 1 通过 Ic读 时序 图

图 2 通 过 Ic 写 时 序 图

A e lz to fI C s i da a a q iii n r ai a i n o bu n t c u sto ba e n FPGA sd o