VHDL合肥工业大学期末试题(含答案)2007-2008A

EDA技术与VHDL期末考试试卷

一、单项选择题:(20分)1. IP核在EDA技术和开发中具有十分重要的地位;提供用VHDL等硬件描述语言描述的功能块,但不涉及实现该功能块的具体电路的IP核为__________。

DA .瘦IP B.固IP C.胖IP D.都不是2.综合是EDA设计流程的关键步骤,在下面对综合的描述中,_________是错误的。

DA. 综合就是把抽象设计层次中的一种表示转化成另一种表示的过程;B. 综合就是将电路的高级语言转化成低级的,可与FPGA / CPLD的基本结构相映射的网表文件;C. 为实现系统的速度、面积、性能的要求,需要对综合加以约束,称为综合约束;D. 综合可理解为一种映射过程,并且这种映射关系是唯一的,即综合结果是唯一的。

3.大规模可编程器件主要有FPGA、CPLD两类,下列对FPGA结构与工作原理的描述中,正确的是__C__。

A. FPGA全称为复杂可编程逻辑器件;B. FPGA是基于乘积项结构的可编程逻辑器件;C. 基于SRAM的FPGA器件,在每次上电后必须进行一次配置;D. 在Altera公司生产的器件中,MAX7000系列属FPGA结构。

4.进程中的信号赋值语句,其信号更新是___C____。

A. 按顺序完成;B. 比变量更快完成;C. 在进程的最后完成;D. 都不对。

5. VHDL语言是一种结构化设计语言;一个设计实体(电路模块)包括实体与结构体两部分,结构体描述___________。

BA. 器件外部特性;B. 器件的内部功能;C. 器件的综合约束;D. 器件外部特性与内部功能。

6.不完整的IF语句,其综合结果可实现________。

AA. 时序逻辑电路B. 组合逻辑电路C. 双向电路D. 三态控制电路7.子系统设计优化,主要考虑提高资源利用率减少功耗(即面积优化),以及提高运行速度(即速度优化);指出下列哪些方法是面积优化_________。

B①流水线设计②资源共享③逻辑优化④串行化⑤寄存器配平⑥关键路径法A. ①③⑤B. ②③④C. ②⑤⑥D. ①④⑥8.下列标识符中,__________是不合法的标识符。

合肥工业大学试卷参考答案(A卷)

又因 N 必须为 2 的整数幂 所以一个记录中的最少点数为 N=210=1024。 二. 简答题(共 40 分,10 分/题) 1. 采用 FFT 算法,可用快速卷积实现线性卷积。现欲计算两个长度分别为 N1 和 N2 的有限 长序列 x(n)、 h(n)的线性卷积 x(n)*h(n), 试写出该快速卷积算法的计算步骤 (注意说明点数) 。 M 1 将序列 x(n)、h(n) 补零至长度 N,其中:N≥N1+N2−1 且 N=2 (M 为整数) 答:○ ; 2 利用 FFT 算法分别计算序列 x(n)、h(n)的 N 点离散傅里叶变换 X(k)、H(k); ○ 3 计算频谱 X(k)、H(k)的乘积,即 ○

Y (k ) = X (k ) H (k )

4 计算 Y(k)的 IFFT 变换,则求得序列 x(n)、h(n)的 N 点线性卷积 x(n)*h(n),即 ○

x(n) ∗ h(n) = y (n) = IFFT [ X (k ) H (k )]

此快速卷积过程如图所示,图中,N≥N1+N2-1,且 N=2M(M 为整数) 。

−π

π

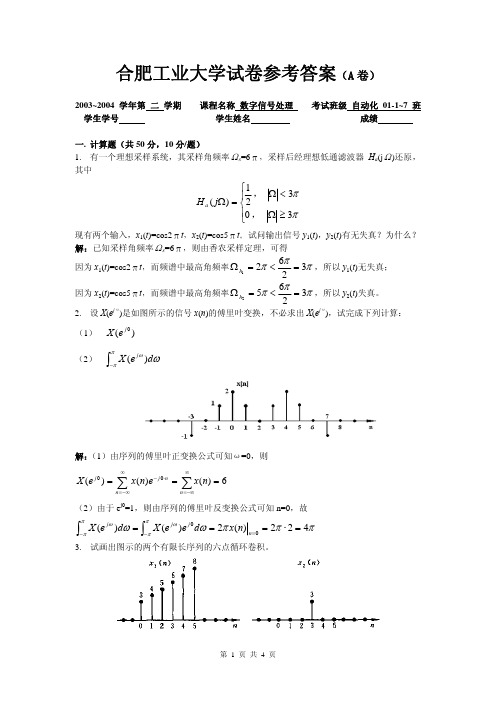

3. 试画出图示的两个有限长序列的六点循环卷积。

第 1 页 共 4 页

解:由循环卷积的定义,可知

6 x ( n) = [ x (( n)) ○ * x ((n )) ]R ( n) y (n) = x1 (n) ○ 2 1 6 2 6 6 * 3δ ((n − 3)) ]R ( n) = [ x1 ((n)) 6 ○ 6 6

第 3 页 共 4 页

∑

n =0

N −1

x (n) =

2

1 N

∑ X (k )

k =0

N −1

2

证:由 DFT 的定义,可知

合肥工业大学微机原理与接口技术2007~2008年第一学期期末考试.

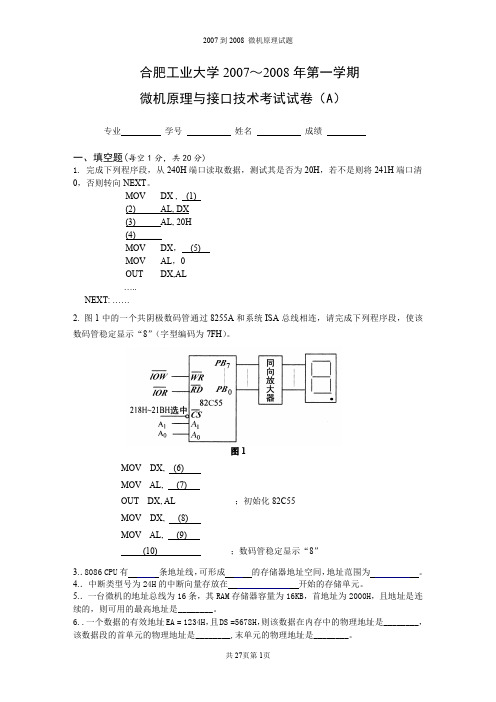

合肥工业大学2007~2008年第一学期微机原理与接口技术考试试卷(A)专业学号姓名成绩一、填空题(每空1分,共20分)1.完成下列程序段,从240H端口读取数据,测试其是否为20H,若不是则将241H端口清0,否则转向NEXT。

MOV DX,(1)(2)AL,DX(3)AL,20H(4)______MOV DX,(5)MOV AL,0OUT DX,AL…..NEXT:……2.图1中的一个共阴极数码管通过8255A和系统ISA总线相连,请完成下列程序段,使该数码管稳定显示“8”(字型编码为7FH)。

图1MOV DX,(6)MOV AL,(7)OUT DX,AL;初始化82C55MOV DX,(8)MOV AL,(9)(10);数码管稳定显示“8”3..8086CPU有条地址线,可形成的存储器地址空间,地址范围为。

4..中断类型号为24H的中断向量存放在开始的存储单元。

5..一台微机的地址总线为16条,其RAM存储器容量为16KB,首地址为2000H,且地址是连续的,则可用的最高地址是________。

6..一个数据的有效地址EA=1234H,且DS=5678H,则该数据在内存中的物理地址是________,该数据段的首单元的物理地址是________,末单元的物理地址是________。

7.若当前堆栈指针SP指向2006H单元,则向堆栈中压入5个字的内容后,SP应指向________。

8.若8086CPU引脚状态是M/IO=1,RD=1,WR=0,则此时执行的操作是________。

二、综合题(80分)1.(10分)一个异步串行通信口,通过TXD发送一帧数据的字符格式如图2的实线所示:图2如果线路上传送的字符格式包括7位ASCII码数据,一位奇偶校验位,一位停止位。

要求:(1)写出该帧字符所传送的数据值,并说明是奇校验还是偶校验。

(2)如果波特率为600bps,请计算传送上面这一帧数据所需要的时间。

VHDL5套试卷标准答案

填空题:1、一般将一个完整的VHDL程序称为设计实体2、VHDL设计实体的基本结构由(库)、(程序包)、(实体)、(结构体)和(配置)组成。

3、(实体)和(结构体)是设计实体的基本组成部分,它们可以构成最基本的VHDL 程序。

4、根据VHDL语法规则,在VHDL程序中使用的文字、数据对象、数据类型都需要(事先声明)。

5、在VHDL中最常用的库是(IEEE)标准库,最常用的数据包是(STD_LOGIC_1164)数据包。

6、VHDL的实体由(实体声明)部分和(结构体)组成。

7、VHDL的实体声明部分指定了设计单元的(输入出端口)或(引脚),它是设计实体对外的一个通信界面,是外界可以看到的部分。

8、VHDL的结构体用来描述实体的(逻辑结构)和(逻辑功能),它由VHDL 语句构成,是外界看不到的部分。

9、在VHDL的端口声明语句中,端口方向包括(输入)、(输出)、(双向)和(缓冲)。

10、VHDL的标识符名必须以(字母开头),后跟若干字母、数字或单个下划线构成,但最后不能为(下划线)11、VHDL的数据对象包括(常量)、(变量)和(信号),它们是用来存放各种类型数据的容器。

12、为信号赋初值的符号是(:=);程序中,为变量赋值的符号是(:=),为信号赋值的符号是(<=)13、VHDL的数据类型包括(标量类型)、(复合类型)、(存储类型)和(文件类型)。

14、在VHDL中,标准逻辑位数据有(九)种逻辑值。

15、VHDL的操作符包括(逻辑)、(算术)、(关系)和(并置)四类。

选择题:1、IEEE于1987年公布了VHDL的(A)语法标准。

A、IEEE STD 1076-1987;B、RS232;C、IEEE STD_LOGIC_1164;D、IEEE STD 1076-1993;2、IEEE于1987年公布了VHDL的(D)语法标准。

A、IEEE STD 1076-1987;B、RS232;C、IEEE STD_LOGIC_1164;D、IEEE STD 1076-1993;3、VHDL的设计实体可以被高层次的系统(D ),成为系统的一部分。

vhdl期末考试题库及答案

vhdl期末考试题库及答案VHDL期末考试题库及答案一、选择题1. VHDL是一种用于电子设计自动化的硬件描述语言,主要用于描述什么?A. 软件程序B. 硬件电路C. 数据库D. 操作系统答案:B2. 在VHDL中,哪个关键字用于定义一个进程?A. processB. procedureC. functionD. package答案:A3. 下列哪个不是VHDL的预定义数据类型?A. bitB. integerC. realD. boolean答案:A4. VHDL中,哪个属性用于获取信号的稳定值?A. 'stable'B. 'event'C. 'quiet'D. 'transaction'答案:A5. 在VHDL中,以下哪个是合法的信号赋值语句?A. signal a : integer := 5;B. signal a : integer is 5;C. signal a <= 5;D. signal a : integer = 5;答案:C二、简答题1. 简述VHDL中的并发语句和顺序语句的区别。

答案:并发语句用于描述多个独立操作同时发生,如进程和并行块;顺序语句描述操作的顺序执行,如if语句、case语句等。

2. 解释VHDL中的时序仿真和功能仿真的区别。

答案:时序仿真考虑了信号的时序特性,如延迟和时间,用于验证设计在实际工作条件下的行为;功能仿真则不关心时序,只验证设计的功能正确性。

三、编程题1. 编写一个VHDL程序,实现一个简单的二进制加法器。

答案:```vhdlentity adder isport(A, B : in bit_vector(1 downto 0);Sum : out bit_vector(1 downto 0);Carry : out bit);end entity adder;architecture behavior of adder isbeginprocess(A, B)begincase A iswhen "00" => Sum <= "00"; Carry <= '0';when "01" => Sum <= "01"; Carry <= '0';when "10" => Sum <= "01"; Carry <= '0';when "11" => Sum <= "10"; Carry <= '1';end case;end process;end architecture behavior;```四、论述题1. 论述在VHDL中使用测试平台(testbench)的重要性。

【免费下载】合肥工业大学2007年复变函数与积分变换期末考试试题A

)已知函数是解析函数,则, .)设的级数为,则该级数)已知,则 .)计算 .)设则 .)若在区域内可导,则在区域内解析。

)若在点解析,,则在区域内可导。

)若在点连续,则在点可导。

)若在点可导,则在点解析。

)将平面上的曲线映射成平面上的图形为()。

)。

)。

)设为正向圆周,则积分()))))(4)级数()(A)敛散性不定。

(B)发散。

(C)条件收敛。

(D)绝对收敛。

(5)是函数的()(A)非孤立奇点。

(B)可去奇点。

(C)一级极点。

(D)本性奇点。

三、(12分)验证在右半平面内是调和函数,并求以此为虚部的解析函数,且使.四、计算下列各题(本小题共6小题,每小题5分,满分30分)(1);(2),其中,取正向;(3),其中,取正向;(4),其中,取正向;(5),其中,取正向;(6)。

五、(12分)将函数分别在下列圆环域内展开成洛朗级数:(1);(2);(3)六、(12分)用积分变换解微分方程,.七、(4分)设在上解析,且,证明 .合肥工业大学2007年《复变函数与积分变换》试题解答一、(1)-3,1,-3;(2);(3);(4)(5).二、(1)A;(2)D;(3)C;(4)B;(5)C.三、由方程,又,故有,.所以,由得,所以.四、(1)原式(2)因为在上及内部解析,由Cauchy-Coursat基本定理,原式=0.(3)原式(4)原式(5)原式(6)令,则原式记,则Res,Res原积分.五、.(1)在内,(2)在内,(3)在内,六、记,对方程两边取Laplace变换,解得七、设曲线,取正向。

由导数公式,因为所以。

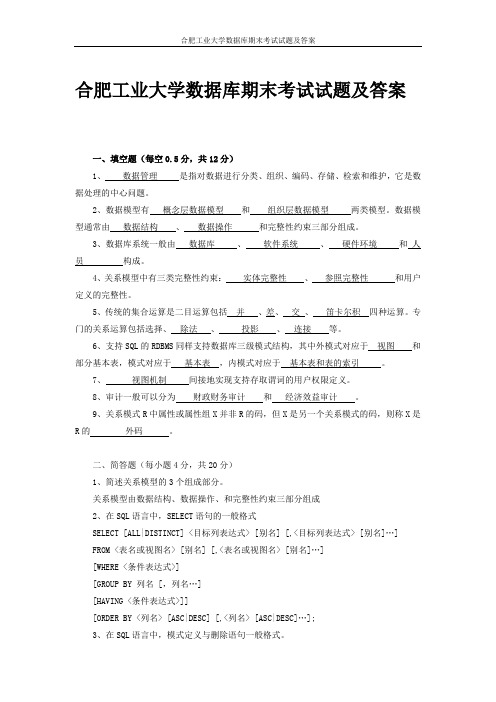

合肥工业大学数据库期末考试试题及答案

合肥工业大学数据库期末考试试题及答案一、填空题(每空0.5分,共12分)1、数据管理是指对数据进行分类、组织、编码、存储、检索和维护,它是数据处理的中心问题。

2、数据模型有概念层数据模型和组织层数据模型两类模型。

数据模型通常由数据结构、数据操作和完整性约束三部分组成。

3、数据库系统一般由数据库、软件系统、硬件环境和人员构成。

4、关系模型中有三类完整性约束:实体完整性、参照完整性和用户定义的完整性。

5、传统的集合运算是二目运算包括并、差、交、笛卡尔积四种运算。

专、连接等。

6、支持SQL的同样支持数据库三级模式结构,其中外模式对应于视图和,内模式对应于基本表和表的索引。

7、视图机制间接地实现支持存取谓词的用户权限定义。

8、审计一般可以分为财政财务审计和经济效益审计。

9、关系模式R中属性或属性组X并非R的码,但X是另一个关系模式的码,则称X是R的外码。

二、简答题(每小题4分,共20分)1、简述关系模型的3个组成部分。

关系模型由数据结构、数据操作、和完整性约束三部分组成2、在SQL语言中,SELECT语句的一般格式SELECT [ALL|DISTINCT] <目标列表达式> [别名] [,<目标列表达式> [别名]…]FROM <表名或视图名> [别名] [,<表名或视图名> [别名]…][WHERE <条件表达式>][GROUP BY 列名 [,列名…][HAVING <条件表达式>]][ORDER BY <列名> [ASC|DESC] [,<列名> [ASC|DESC]…];3、在SQL语言中,模式定义与删除语句一般格式。

CREATE SCHEMA <模式名> AUTHORIZATION<用户名> DROP SCHEMA<模式名>4、在SQL 语言中,插入数据、修改数据、删除数据语句一般格式。

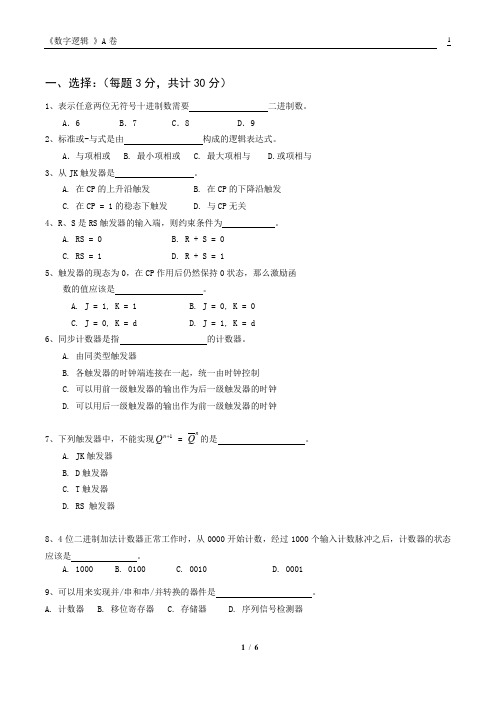

合工大数电期末试卷

一、选择:(每题3分,共计30分)1、表示任意两位无符号十进制数需要 二进制数。

A .6B .7C .8D .9 2、标准或-与式是由 构成的逻辑表达式。

A .与项相或 B. 最小项相或 C. 最大项相与 D.或项相与 3、从JK 触发器是 。

A. 在CP 的上升沿触发B. 在CP 的下降沿触发C. 在CP = 1的稳态下触发D. 与CP 无关4、R 、S 是RS 触发器的输入端,则约束条件为 。

A. RS = 0B. R + S = 0C. RS = 1D. R + S = 15、触发器的现态为0,在CP 作用后仍然保持0状态,那么激励函数的值应该是 。

A. J = 1, K = 1 B. J = 0, K = 0 C. J = 0, K = d D. J = 1, K = d6、同步计数器是指 的计数器。

A. 由同类型触发器B. 各触发器的时钟端连接在一起,统一由时钟控制C. 可以用前一级触发器的输出作为后一级触发器的时钟D. 可以用后一级触发器的输出作为前一级触发器的时钟7、下列触发器中,不能实现1n Q = nQ 的是 。

A. JK 触发器B. D 触发器C. T 触发器D. RS 触发器8、4位二进制加法计数器正常工作时,从0000开始计数,经过1000个输入计数脉冲之后,计数器的状态应该是 。

A. 1000B. 0100C. 0010D. 00019、可以用来实现并/串和串/并转换的器件是 。

A. 计数器 B. 移位寄存器 C. 存储器 D. 序列信号检测器10、设计一个四位二进制码的奇偶位发生器(假定采用偶检验码), 需要 个异或门。

A .2 B. 3 C. 4 D. 5二、填空:(每题2分,共10分)1、(48)10 =(_________)16 =(______________)2 。

2、集成触发器三种结构: 、 的和 。

3. 函数的反函数= 。

4、时序逻辑电路的功能表示方法有: 、 、和 。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

合肥工业大学2007/2008 学年第一学期末考试试题答案及评分标准(A卷)一、填空题(20分,每空格1分)1、VHDL是否区分大小写?不区分。

2、digital_ _8标识符合法吗?不合法。

12_bit标识符合法吗?不合法。

signal标识符合法吗?不合法。

3、结构体有三种描述方式,分别是数据流、行为、和结构化。

4、请分别列举一个常用的库和程序包library ieee 、use ieee.std_logic_1164.all 。

5、一个信号处于高阻(三态)时的值在VHDL中描述为‘Z’。

6、将一个信号width定义为一个4位标准逻辑向量为signal width : std_logic_vector(3 downto 0) 。

7、/=是不相等操作符,功能是在条件判断是判断操作符两端不相等。

8、设D0为'0', D1为'1', D2为'1', D3为'0', D3 & D2 & D1 & D0的运算结果是“0110”,(D3 or D2)and(D1 and not D0)的运算结果是:‘1’。

9、赋值语句是(并行/串行)并行执行的,if语句是(并行/串行)串行执行的。

10、请列举三种可编程逻辑器件: EEPROM 、 GAL 、 FPGA 。

二、简答(20分,每小题5分)1、简述VHDL程序的基本结构。

程序包(2)实体(3)结构体(5)若答出配置也可加1分2、简述信号与变量的区别。

信号延时赋值,变量立即赋值(2)信号的代入使用<=,变量的代入使用:=;(4)信号在实际的硬件当中有对应的连线,变量没有(5)3、简述可编程逻辑器件的优点。

●集成度高,可以替代多至几千块通用IC芯片–极大减小电路的面积,降低功耗,提高可靠性(1)●具有完善先进的开发工具–提供语言、图形等设计方法,十分灵活–通过仿真工具来验证设计的正确性(2)●可以反复地擦除、编程,方便设计的修改和升级(3)●灵活地定义管脚功能,减轻设计工作量,缩短系统开发时间(4)●保密性好(5)4、试比较moore状态机与mealy状态机的异同。

Moore输出只是状态机当前状态的函数(3)Mealy输出为有限状态机当前值和输入值的函数(5)三、判断题(10分)library ieee;use ieee.std_logic_arith.all;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;以上库和程序包语句有无错误?有,有的话请在原程序相应位置改正。

(2)entity rom isport(addr: in std_logic_vector(0 to 3);ce: in std_logic;data:out std_logic_vector(7 downto 0);)end rom;以上port语句有无错误?有,有的话请在原程序相应位置改正。

(4)architecture behave of rom isbeginprocess(ce,addr)(6)beginif ce='0' thencase addr iswhen "0000"=>data<="10001001";when "0001"=>data<="10001010";when "0010"=>data<="10001011";when "0011"=>data<="10001100";when "0100"=>data<="10001101";when "0101"=>data<="10001110";when "0110"=>data<="10001111";when "0111"=>data<="10010000";when "1000"=>data<="10010001";when "1001"=>data<="10010010";when "1010"=>data<="10010011";when "1011"=>data<="10010100";when "1100"=>data<="10010101";when "1101"=>data<="10010110";when "1110"=>data<="10010111";when others=>data<="10011000"; end case;elsedata:="00000000"; --data <= “00000000”; (8)end if; (10)end process;end behave;以上architecture中有哪些错误?请在原程序相应位置改正。

四、编程(共50分,除特殊声明,实体可只写出PORT语句,结构体要写完整)1、用IF语句编写一个二选一电路,要求输入a、b, sel为选择端,输出q。

(本题10分)Entity sel2 isPort (a,b : in std_logic;sel : in std_logic;q : out std_logic);End sel2; (3)Architecture a of sel2 isbeginif sel = ‘0’ thenq <= a; (6)elseq <= b; (9)end if;end a; (10)2、编写一个4位加法计数器VHDL程序的进程(不必写整个结构框架),要求复位信号reset 低电平时计数器清零,变高后,在上升沿开始工作;输入时钟信号为clk,输出为q。

(本题10分)Process(reset,clk) (2)beginif reset = ‘0’ thenq <= “0000”; (4)elsif clk’event and clk = ‘1’ then (6)q <= q + 1; (9)end if;end process; (10)3、填写完成一个8-3线编码器的真值表(5分),并写出其VHDL程序(10分)。

8 -3线编码器真值表entity eight_tri isport(b: in std_logic_vector(7 downto 0);en: in std_logic;y: out std_logic_vector(2 downto 0));end eight_tri; (3)architecture a of eight_tri issignal sel: std_logic_vector(8 downto 0); (4)beginsel<=en & b;y<= “000” when (sel=”100000001”)else“001” when (sel=”100000010”)else“010” when (sel=”100000100”)else“011” when (sel=”100001000”)else“100” when (sel=”100010000”)else“101” when (sel=”100100000”)else“110” when (sel=”101000000”)else“111” when (sel=”110000000”)else(9)“zzz”;(10)end a;4、根据已给出的全加器的VHDL程序,试写出一个4位逐位进位全加器的VHDL程序。

(本题15分)library IEEE;use IEEE.std_logic_1164.all;use IEEE.std_logic_arith.all;use IEEE.std_logic_unsigned.all;entity adder isport (a,b,c: in std_logic;carr: inout std_logic;sum: out std_logic);end adder;architecture adder_arch of adder isbeginsum <= a xor b xor c;carr <= (a and b) or (b and c) or (a and c);end adder_arch;entity full_add isport (a,b: in std_logic_vector (3 downto 0);carr: inout std_logic_vector (4 downto 0);sum: out std_logic_vector (3 downto 0));end full_add; (5)architecture full_add_arch of full_add iscomponent adderport (a,b,c: in std_logic;carr: inout std_logic;sum: out std_logic);end component; (10)begincarr(0)<='0';u0:adder port map(a(0),b(0),carr(0),carr(1),sum(0));u1:adder port map(a(1),b(1),carr(1),carr(2),sum(1));u2:adder port map(a(2),b(2),carr(2),carr(3),sum(2));u3:adder port map(a(3),b(3),carr(3),carr(4),sum(3));end full_add_arch; (15)五、附加题(10分,本题可产生附加分,全卷不能超过100分)完成下面moore状态机程序,该设计为一个存储控制器状态机。