版图设计实例PPT课件

合集下载

版图设计实例ppt课件

分割输入器件实现四方交叉:将M3变为M3a和M3b,M4变 为M4a和M4b,就可以实现四方交叉,保证输入器件的对称 性。

经营者提供商品或者服务有欺诈行为 的,应 当按照 消费者 的要求 增加赔 偿其受 到的损 失,增 加赔偿 的金额 为消费 者购买 商品的 价款或 接受服 务的费 用

由于全部电流都要通过输入晶体管中的每一个,例如,有时整个电 流完全在M3,当差分信号关断时,M3关断M4接通,整个电流又完全在 M4,信号每摆动一次就切换一次,为了承受这一电流,在M3和M4之间 的金属线需要达到一定的宽度,采用二条金属线连接M3和M4的源极,并 且从M4b和M3b的中间向下,这样,M3导通时电流将通过M3a和M3b, 即它的两半把电流向下送到中心导线。

经营者提供商品或者服务有欺诈行为 的,应 当按照 消费者 的要求 增加赔 偿其受 到的损 失,增 加赔偿 的金额 为消费 者购买 商品的 价款或 接受服 务的费 用

4. CMOS放大器

经营者提供商品或者服务有欺诈行为 的,应 当按照 消费者 的要求 增加赔 偿其受 到的损 失,增 加赔偿 的金额 为消费 者购买 商品的 价款或 接受服 务的费 用

1. CMOS门电路

(1) 反相器

电路图

版图1

版图2

版图1特点:多晶栅竖直排列,MOS管源区面积小,因而反相器面积也小。 版图2特点:多晶栅水平排列,MOS管漏极金属与电源、地金属线之间的 空档允许其它金属线通过,因水平尺寸较大而使面积稍大一些。

经营者提供商品或者服务有欺诈行为 的,应 当按照 消费者 的要求 增加赔 偿其受 到的损 失,增 加赔偿 的金额 为消费 者购买 商品的 价款或 接受服 务的费 用

2.MOS管并联(并联是指它们的源和源连接,漏和漏连接,各 自的栅还是独立的。) (1)栅极水平放置,节点X和Y可用金 属连线连接(图b);也可用有源区连接(图c)。

经营者提供商品或者服务有欺诈行为 的,应 当按照 消费者 的要求 增加赔 偿其受 到的损 失,增 加赔偿 的金额 为消费 者购买 商品的 价款或 接受服 务的费 用

由于全部电流都要通过输入晶体管中的每一个,例如,有时整个电 流完全在M3,当差分信号关断时,M3关断M4接通,整个电流又完全在 M4,信号每摆动一次就切换一次,为了承受这一电流,在M3和M4之间 的金属线需要达到一定的宽度,采用二条金属线连接M3和M4的源极,并 且从M4b和M3b的中间向下,这样,M3导通时电流将通过M3a和M3b, 即它的两半把电流向下送到中心导线。

经营者提供商品或者服务有欺诈行为 的,应 当按照 消费者 的要求 增加赔 偿其受 到的损 失,增 加赔偿 的金额 为消费 者购买 商品的 价款或 接受服 务的费 用

4. CMOS放大器

经营者提供商品或者服务有欺诈行为 的,应 当按照 消费者 的要求 增加赔 偿其受 到的损 失,增 加赔偿 的金额 为消费 者购买 商品的 价款或 接受服 务的费 用

1. CMOS门电路

(1) 反相器

电路图

版图1

版图2

版图1特点:多晶栅竖直排列,MOS管源区面积小,因而反相器面积也小。 版图2特点:多晶栅水平排列,MOS管漏极金属与电源、地金属线之间的 空档允许其它金属线通过,因水平尺寸较大而使面积稍大一些。

经营者提供商品或者服务有欺诈行为 的,应 当按照 消费者 的要求 增加赔 偿其受 到的损 失,增 加赔偿 的金额 为消费 者购买 商品的 价款或 接受服 务的费 用

2.MOS管并联(并联是指它们的源和源连接,漏和漏连接,各 自的栅还是独立的。) (1)栅极水平放置,节点X和Y可用金 属连线连接(图b);也可用有源区连接(图c)。

版图设计课件 PPT

一、双极集成电路工艺的基本流程

实现选择性掺杂的三道基本工序

(3)掺杂:在半导体基片的一定区域掺入一定浓度的杂质 元素,形成不同类型的半导体层,来制作各种器件。掺 杂工艺主要有两种:扩散和离子注入。

扩散:在热运动的作用下,物质的微粒都有一种从高浓 度的地方向低浓度的地方运动的趋势。在IC生产中,扩 散的同时进行氧化。

结论:对采用PN结隔离的双极IC基本工艺,与制作NPN 晶体管的基本工艺相比,只需增加外延工艺,当然工艺步 骤要增加不少。

一、双极集成电路工艺的基本流程

PN结隔离双极IC工艺基本流程

衬底材料(P型硅)- 埋层氧化-埋层光刻 -埋层掺杂(Sb)外延 (N型硅)隔离氧化-隔离光刻 -隔离掺杂(B)- 基区氧化-基区光刻 -基区掺杂(B)和发射区氧化-

一、双极集成电路工艺的基本流程

工艺类型简介

按照制造器件的结构不同可以分为: 双极型:由电子和空穴这两种极性的载流子作为在有源

区中运载电流的工具。 MOS型:PMOS工艺、NMOS工艺、CMOS工艺 BiCMOS集成电路:双极与MOS混合集成电路

按照MOS的栅电极的不同可以分为: 铝栅工艺、硅栅工艺(CMOS制造中的主流工艺)

(2) 光刻2:场氧光刻,又称为有源区光刻。将以后作为有源区区域的 氧(3化) 氧层化和氮层化生硅长层。保在留没,有其氮余化区硅域层的保氧护化的层区和氮化硅全部去除。 域(即场区)生长一层较厚的氧化层。图中 表面没有氧化层的区域即为有源区。

三、CMOS集成电路工艺流程

3. 生长栅氧化层和生成多晶硅栅电极 确定了有源区以后,就可以制作MOS晶体管。首先按下述步骤生长栅 氧化层和制作栅电极。 (1) 生长栅氧化层。去除掉有源区上的氮化硅层及薄氧化层以后,生长 一层作为栅氧化层的高质量薄氧化层。 (2) 在栅氧化层上再淀积一层作为栅电极材料的多晶硅。 (3) 光刻3:光刻多晶硅,只保留作栅电极以及起互连作用的多晶硅。 光刻后的剖面图如图所示。

北大集成电路版图设计课件_第9章集成电路版图设计实例

R3 1 3 2 3 1 3 2 3

2

1

2

1

2

3

1

3

2

3

1

3

R1和R2的共质心结构版图设计

加入R3后的共质心版图设计

49

9.7带隙基准源版图实例

总体版图实例

比例电阻

运算放大器

1:8 晶体管

50

9.8芯片总体设计

首先,在总体版图的布局上,尽量将数字部分远离模拟部分,如果 总体电路中模拟部分偏多,则在版图设计中将数字部分放在靠边的位 置,而且把模拟部分中最容易被数字干扰的部分放到离数字部分最远 的位置,同时在数字部分和模拟部分中间用接地的衬底接触来进行隔 离,反之亦然。 其次,采用隔离环设计,对每个单元模块都用一层接地的衬底接触, 一层接电源的N阱构成的隔离环来进行隔离。对于整个模拟部分和数 字也分别采用相同的隔离环隔离,数字电路的隔离环可以吸收数字电 路的衬底噪声,从而可以减少通过衬底串扰到模拟电路的衬底噪声。 隔离环包的层数越多,理论上吸收衬底噪声效果越好。但是要避免数 字电路的p隔离环紧靠模拟电路的p型隔离环,因为在这种情况下数字 地的噪声会串扰到模拟地。从而使模拟地受到干扰。

1.反相器-并联反相器的版图

直接并联

共用漏区

7

9.2 数字版图设计实例

2.与非门

VCC A Q1 Q2 OUT B Q3

Q4

按电路图转换

MOS管水平走向设计

8

9.2 数字版图设计实例

3.或非门

VCC A Q1

B

Q2 OUT Q3 Q4

按电路图转换

MOS管水平走向设计

9

9.2 数字版图设计实例

4.传输门

25

9.5静电保护电路设计实例

2

1

2

1

2

3

1

3

2

3

1

3

R1和R2的共质心结构版图设计

加入R3后的共质心版图设计

49

9.7带隙基准源版图实例

总体版图实例

比例电阻

运算放大器

1:8 晶体管

50

9.8芯片总体设计

首先,在总体版图的布局上,尽量将数字部分远离模拟部分,如果 总体电路中模拟部分偏多,则在版图设计中将数字部分放在靠边的位 置,而且把模拟部分中最容易被数字干扰的部分放到离数字部分最远 的位置,同时在数字部分和模拟部分中间用接地的衬底接触来进行隔 离,反之亦然。 其次,采用隔离环设计,对每个单元模块都用一层接地的衬底接触, 一层接电源的N阱构成的隔离环来进行隔离。对于整个模拟部分和数 字也分别采用相同的隔离环隔离,数字电路的隔离环可以吸收数字电 路的衬底噪声,从而可以减少通过衬底串扰到模拟电路的衬底噪声。 隔离环包的层数越多,理论上吸收衬底噪声效果越好。但是要避免数 字电路的p隔离环紧靠模拟电路的p型隔离环,因为在这种情况下数字 地的噪声会串扰到模拟地。从而使模拟地受到干扰。

1.反相器-并联反相器的版图

直接并联

共用漏区

7

9.2 数字版图设计实例

2.与非门

VCC A Q1 Q2 OUT B Q3

Q4

按电路图转换

MOS管水平走向设计

8

9.2 数字版图设计实例

3.或非门

VCC A Q1

B

Q2 OUT Q3 Q4

按电路图转换

MOS管水平走向设计

9

9.2 数字版图设计实例

4.传输门

25

9.5静电保护电路设计实例

版图设计及举例教学课件

一个版图应该有一个主要的 焦点,以避免混乱和不清晰 的信息表达。

原则: 对称性

对称性可以帮助创建平衡和 稳定感,使版图更加美观和 整齐。

原则: 平衡性

平衡性是指在版图中平衡各 个元素的重量和空间分布。

原则: 重复性

通过重复使用某些元素,可以增加版图的统一 性和可读性。

原则: 简洁性

简洁性是指通过精练的信息和简单的设计元素 来传达清晰的信息。

PPT是一个简便实用的工具,可以于制作简单而有效的版图设计。

制作一个版图设计的教学PPT

通过详细讲解PPT基本操作、选择场景和主题、制定版图设计要素和原则、 界面元素的选择与搭配以及制作过程中的技巧和注意事项,让观众学会制作 精美的版图设计教学PPT。

结束语

总结版图设计的重要性和作用,告诉观众掌握版图设计技能的必要性。 感谢观众的收听和观看!

版图设计的要素和原则

要素: 布局

布局是指将内容元素有机地组合在一起,创造 出视觉上的平衡和整体感。

要素: 色彩

色彩可以增加版图的视觉吸引力,并传达特定 的情感和氛围。

要素: 字体

字体的选择和排版可以影响版图的可读性和视 觉效果。

要素: 图片与图标

图片和图标可以增加版图的信息量和吸引力。

原则: 单一性

实例:版图设计要素和原则

通过选取一个场景,分析其版图设计要素和原则,并呈现一些成功的版图设计案例。

版图设计的实现方法

Photoshop、Illustrator、Sketch等工具

可以使用专业设计软件进行版图设计和编辑。

在线版图设计工具

有一些在线工具可以让您快速创建精美的版图设计。

使用PPT制作版图

版图设计及举例教学课件 PPT

原则: 对称性

对称性可以帮助创建平衡和 稳定感,使版图更加美观和 整齐。

原则: 平衡性

平衡性是指在版图中平衡各 个元素的重量和空间分布。

原则: 重复性

通过重复使用某些元素,可以增加版图的统一 性和可读性。

原则: 简洁性

简洁性是指通过精练的信息和简单的设计元素 来传达清晰的信息。

PPT是一个简便实用的工具,可以于制作简单而有效的版图设计。

制作一个版图设计的教学PPT

通过详细讲解PPT基本操作、选择场景和主题、制定版图设计要素和原则、 界面元素的选择与搭配以及制作过程中的技巧和注意事项,让观众学会制作 精美的版图设计教学PPT。

结束语

总结版图设计的重要性和作用,告诉观众掌握版图设计技能的必要性。 感谢观众的收听和观看!

版图设计的要素和原则

要素: 布局

布局是指将内容元素有机地组合在一起,创造 出视觉上的平衡和整体感。

要素: 色彩

色彩可以增加版图的视觉吸引力,并传达特定 的情感和氛围。

要素: 字体

字体的选择和排版可以影响版图的可读性和视 觉效果。

要素: 图片与图标

图片和图标可以增加版图的信息量和吸引力。

原则: 单一性

实例:版图设计要素和原则

通过选取一个场景,分析其版图设计要素和原则,并呈现一些成功的版图设计案例。

版图设计的实现方法

Photoshop、Illustrator、Sketch等工具

可以使用专业设计软件进行版图设计和编辑。

在线版图设计工具

有一些在线工具可以让您快速创建精美的版图设计。

使用PPT制作版图

版图设计及举例教学课件 PPT

集成电路版图设计 ppt课件

WW

top-metal (18 mOhm/sq)

MMeetatal -l1

WW

ILD WW

WW

A-Si

PSD

PSD

PSD

NSD

NSD

VTP PAPT

NAPT

Nwell

Pwell

WW

WW

MMeetatal-l3 WW

WW WW

Poly

NSD

Trench oxide

P Substrate 6

8.2 版图几何设计规则

导电层作为下电极 绝缘层作为平板电容两电极间的介质 导电层作为上电极 电容计算公式:

Ctotal [ fF ] Carea [ fF / m2 ]* area[ m2 ] C fringe[ fF / m ]* perimeter[ m ]

电阻的可变参数:电阻宽度(width)、电阻值(R)。

19

多晶硅电阻

2.0

3.0

2.0

2.0

2.0

Poly

Metal1

Xd

Xd

1.0

1.5

Contact

图8.7 第一层多晶硅电阻俯视图

3.0

Electrode

Metal1

Contact

Xd 1.0

2.0

图8.8 第二层多晶硅电阻俯视图

20

多晶硅电阻(续)

MOS管的可变参数为:栅长(gate_length)、栅宽(gate_width) 和栅指数(gates)。

栅长(gate_length)指栅极下源区和漏区之间的沟道长度,最 小值为2lambda=0.4μm。

栅宽(gate_width)指栅极下有源区(沟道)的宽度,最小栅宽为 3 lambda=0.6μm。

版图设计课件

隔离光刻

隔离扩散

ICCAD

版图.21

一、双极集成电路工艺的基本流程

IC管芯中的特殊问题

(2) NPN晶体管集电区埋层的引入:

因为在集成电路中各元件的端点都从上表面引出,并 在上表面实现互连,所以集电极电流在集电区是横向流动 的,而为了保证集电结可以承受足够高的反向击穿电压, 外延层的电阻率又不能选得很低,这就形成较大的集电极 串联电阻。为了减小集电极串联电阻,在晶体管的外延层 和衬底之间需要增加N+埋层。

二、双极IC中的基本元器件

小结:集成化线路的特点(以双极IC为例) (1) IC中制备大容量的电容比较困难,高阻值电阻精度差 ,因此放大电路中多以差分对为基本单元,同时采用恒流 源、有源负载等电路结构。 (2)双极IC工艺流程是围绕如何使NPN晶体管具有最佳特 性安排的,在这同时形成其他元器件。因此双极IC中PNP 晶体管特性比NPN晶体管特性差得多,例如PNP晶体管的 电流放大系数只有几到20左右。一般情况下尽量少用PNP 晶体管。如果需要特性好的PNP晶体管,就要增加工艺流 程。

ICCAD 版图.34

二、双极IC中的基本元器件

小结:集成化线路的特点(以双极IC为例)

(3) 由于下述原因,集成化电路中应少用电阻、电容,尽 量改用晶体管。

*双极IC中制备NPN晶体管比制备电阻、电容要方便经 济得多(晶体管占用面积小)。 *晶体管参数一致性和对称性都很好。 *容易实现各种特殊的晶体管结构,如复合晶体管、达 林顿晶体管、可控增益PNP晶体管等。 (4) IC工艺中制备的电阻阻值绝对误差大,但是电阻阻值 之比的精度比阻值绝对值的精度好一个数量级。设计电路 时,应尽量使电路特性与阻值之比关系密切,而与阻值大 小的关系较弱。

数字后端版图设计ppt课件

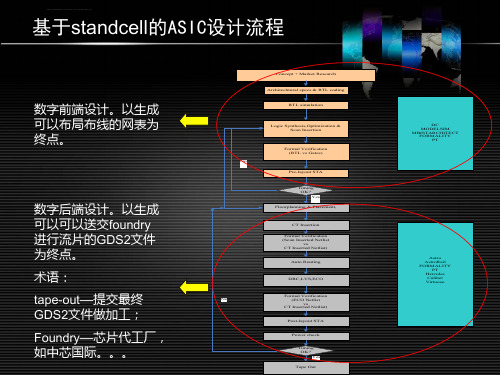

数字后端设计流程-8

布线

采用PP管及配件:根据给水设计图配 置好PP管及配 件,用 管件在 管材垂 直角切 断管材 ,边剪 边旋转 ,以保 证切口 面的圆 度,保 持熔接 部位干 净无污 物

数字后端设计流程-8

布线

采用PP管及配件:根据给水设计图配 置好PP管及配 件,用 管件在 管材垂 直角切 断管材 ,边剪 边旋转 ,以保 证切口 面的圆 度,保 持熔接 部位干 净无污 物

芯片中的时钟网络要驱动电路中所有的时序单元,所以 时钟源端门单元带载很多,其负载延时很大并且不平衡, 需要插入缓冲器减小负载和平衡延时。时钟网络及其上 的缓冲器构成了时钟树。一般要反复几次才可以做出一 个比较理想的时钟树。

采用PP管及配件:根据给水设计图配 置好PP管及配 件,用 管件在 管材垂 直角切 断管材 ,边剪 边旋转 ,以保 证切口 面的圆 度,保 持熔接 部位干 净无污 物

数字后端设计流程-2

哪些工作要APR工具完成? 芯片布图(RAM,ROM等的摆放、芯片供电网络配置、 I/O PAD摆放) 标准单元的布局 时钟树和复位树综合 布线 DRC LVS DFM(Design For Manufacturing)

采用PP管及配件:根据给水设计图配 置好PP管及配 件,用 管件在 管材垂 直角切 断管材 ,边剪 边旋转 ,以保 证切口 面的圆 度,保 持熔接 部位干 净无污 物

布图

这是一个小电路,电源 规划比较简单,对于一 个复杂的电路,还需要 横竖添加stripes,降低 IRdrop。

采用PP管及配件:根据给水设计图配 置好PP管及配 件,用 管件在 管材垂 直角切 断管材 ,边剪 边旋转 ,以保 证切口 面的圆 度,保 持熔接 部位干 净无污 物

数字后端设计流程-5

布线

采用PP管及配件:根据给水设计图配 置好PP管及配 件,用 管件在 管材垂 直角切 断管材 ,边剪 边旋转 ,以保 证切口 面的圆 度,保 持熔接 部位干 净无污 物

数字后端设计流程-8

布线

采用PP管及配件:根据给水设计图配 置好PP管及配 件,用 管件在 管材垂 直角切 断管材 ,边剪 边旋转 ,以保 证切口 面的圆 度,保 持熔接 部位干 净无污 物

芯片中的时钟网络要驱动电路中所有的时序单元,所以 时钟源端门单元带载很多,其负载延时很大并且不平衡, 需要插入缓冲器减小负载和平衡延时。时钟网络及其上 的缓冲器构成了时钟树。一般要反复几次才可以做出一 个比较理想的时钟树。

采用PP管及配件:根据给水设计图配 置好PP管及配 件,用 管件在 管材垂 直角切 断管材 ,边剪 边旋转 ,以保 证切口 面的圆 度,保 持熔接 部位干 净无污 物

数字后端设计流程-2

哪些工作要APR工具完成? 芯片布图(RAM,ROM等的摆放、芯片供电网络配置、 I/O PAD摆放) 标准单元的布局 时钟树和复位树综合 布线 DRC LVS DFM(Design For Manufacturing)

采用PP管及配件:根据给水设计图配 置好PP管及配 件,用 管件在 管材垂 直角切 断管材 ,边剪 边旋转 ,以保 证切口 面的圆 度,保 持熔接 部位干 净无污 物

布图

这是一个小电路,电源 规划比较简单,对于一 个复杂的电路,还需要 横竖添加stripes,降低 IRdrop。

采用PP管及配件:根据给水设计图配 置好PP管及配 件,用 管件在 管材垂 直角切 断管材 ,边剪 边旋转 ,以保 证切口 面的圆 度,保 持熔接 部位干 净无污 物

数字后端设计流程-5

第14章集成电路版图设计PPT课件

• 完成一个反相器的版图设计

2020/9/21

25

2020/9/21

26

2020/9/21

27

2020/9/21

28

2020/9/21

29

2020/9/21

30

2020/9/21

31

2020/9/21

32

版图设计中的相关主题

1. Antenna Effect 2. Dummy 的设计 3. Guard Ring 保护环的设计 4. Match的设计

2020/9/21

层次表示 含义

Nwell

N阱层

Active

N+或P+有源 区层

Poly 多晶硅层

Contact 接触孔层

Metal Pad

金属层

焊盘钝化 层

标示图

15

2020/9/21

16

2020/9/21

17

2020/9/21

Hale Waihona Puke N阱设计规则编 描 述尺

目的与作用

号

寸

1.1 N阱最小宽 (1μ0m.) 保证光刻精度和器

• 设计规则是各集成电路制造厂家根据本身的工艺特点和技术水平而制定的。 因此不同的工艺,就有不同的设计规则。

• 掩膜上的图形决定着芯片上器件或连接物理层的尺寸。因此版图上的几何图

形尺寸与芯片上物理层的尺寸直接相关。

2020/9/21

13

版图几何设计规则

• 版图设计规则:是指为了保证电路的功能和一定的成品率而提出的一 组最小尺寸,如最小线宽、最小可开孔、线条之间的最小间距。

• 1.设计规则检查(DRC) • 2.版图寄生参数提取(LPE) • 3.寄生电阻提取(PRE) • 4.电气规则检查(ERC) • 5.版图与线路图比较程序(LVS)

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

18

(2列的方向只要求相邻单元位

线的间距符合设计规则;行的布局合并了公共区域,即Vdd和

Vss共用。

19

3. CMOS D触发器 (1) 无置位和复位端的D触发器

电路图

电路图中,用钟控反相器代替反相器和传输门(TG2)串联。

20

版图

特点:1)版图为4行结构,中间两行构成反相器,多晶从第2行延伸到第3行就 形成反相器。

2)第1行和第4行构成传输门,虽然被第2、3行分隔开,但这两行MOS管不需 要多晶共用,只用金属进行源漏连接,即使这些金属连线跨过中间两行有源区,也 不会形成寄生MOS管。

3)CP多晶放在Vdd线下,CPb多晶沿Vss水平布线,在中央部位,这两条多晶 都从有源区的空隙分别延伸到Vdd和Vss线附近,与传输门器件的栅级连接。

9

版图2特点:或非门和与或非门分开布局,P管和N管各占一行。

10

(3)二输入端与门(and2)

特点:与门由与非门和反相器串联而成,采用合并公共区域 的技巧,将P管接电源的有源区公用,N管接地的有源区公用, 器件的排列很紧凑,面积很小。

11

(4) 与或非门(AOI)

提示:设计AOI或OAI的版图,一定要熟练掌握MOS管串联和 并联的画法后进行,看清每个MOS管的输入信号,用棍棒图画 出草图后再画版图。

4)主触发器采用钟控反相器,节省一根金属连线。

21

(2) 带置位端的D触发器

电路图 版图

特点:器件仍分 为4层,CP和CPb也 位于上下两边,并且 在CP多晶的上方增 加一条水平的多晶作 为复位(R)。CPb 线在水平和垂直方向 的连接采用金属过渡。 主触发器采用钟控或 非门,节省一根金属 连线。

(a) 电路图

(b) N1版图 (c) N0版图 (d) N1和N0串联版图

(2) 任意个MOS管串联。例如3个MOS管串联的版图。

(a)电路图

(b) 版图

5

2.MOS管并联(并联是指它们的源和源连接,漏和漏连接,各 自的栅还是独立的。) (1)栅极水平放置,节点X和Y可用金 属连线连接(图b);也可用有源区连接(图c)。

版图设计实例

1

MOS 场效应管的版图实现

单个MOS管的版图实现

1. MOS管的结构和布局

① MOS管的四种布局图

2

③ 源区、沟道区和漏区合称为MOS管的有源区(Active),而有源区之外 的区域定义为场区(Fox)。有源区和场区之和就是整个芯片表面。

Fox + Active = Surface

7

1. CMOS门电路

(1) 反相器

电路图

版图1

版图2

版图1特点:多晶栅竖直排列,MOS管源区面积小,因而反相器面积也小。 版图2特点:多晶栅水平排列,MOS管漏极金属与电源、地金属线之间的 空档允许其它金属线通过,因水平尺寸较大而使面积稍大一些。

8

(2) 异或门

版图1特点:多晶栅竖直放置;MOS管排成4行,第2和第4行构 成或非门,第1和第3行构成与或非门.整个版图较高。

芯片表面包含有源区和场区两部分

④ N阱CMOS集成电路使用P型衬底,NMOS管直接制作在 P型衬底上,PMOS管做在N阱内。

3

⑤ 完整的MOS管版版图必须包含两个部分:a)由源、栅和 漏组成的器件;b)衬底连接。

4

5.1.2 MOS管阵列的版图实现

1.MOS管串联

(1) 两个MOS管的串联。 N1的源、漏区为X和Y,N0的源、漏区为Y和Z。Y是它们的公共区域,如 果把公共区域合并,得到图5.7(d)所示的两个MOS管串联连接的版图。 从电流的方向可以决定,当MOS管串联时,它们的电极按S-D-S-D-S-D方 式连接。

25

26

M3和M4的宽长比很大,M3a、M3b、M4a和M4b都采用多管并联的结构。这四 个MOS管的源已经连接到Metal1导线,为了避免和Metal1交叉短路, M3和M4的漏极 要用Metal2连接。Metal2有很多通孔和很宽的导线,使电流能够顺利通过。

22

4. CMOS放大器

23

分割输入器件实现四方交叉:将M3变为M3a和M3b,M4变 为M4a和M4b,就可以实现四方交叉,保证输入器件的对称 性。

24

由于全部电流都要通过输入晶体管中的每一个,例如,有时整个电 流完全在M3,当差分信号关断时,M3关断M4接通,整个电流又完全在 M4,信号每摆动一次就切换一次,为了承受这一电流,在M3和M4之间 的金属线需要达到一定的宽度,采用二条金属线连接M3和M4的源极,并 且从M4b和M3b的中间向下,这样,M3导通时电流将通过M3a和M3b, 即它的两半把电流向下送到中心导线。

(2)栅极竖直方向排列,节点连接既可用金属导线(图b),也 可用有源区进行连接(图c)。

6

(3)三个或三个以上MOS管并联。 ① 全部用金属进行源的连接和漏的连接(图a),称为叉指形结构; ② 分别用金属和有源区进行源和漏的并联连接; ③ 金属连接和有源区连接联合使用(图b)。

3.MOS管的复联 复联是MOS管先串后并和先并后串的连接。

12

(5) 或与非门(OAI)

提示:对比AOI和OAI电路图和版图的区别和画法,巩固和 熟练掌握CMOS复联电路版图的画法。

13

(6) 全加器

14

版图

15

2019/12/22

16

特点: ① 和异或门相似,几个输入信号被几乎所有的器件公用, 设计版图时要充分注意这一特点。 ② 版图把A、B、C多晶分成二段且排成二列,A线在上面 (靠近Vdd)转折连接,B线在下面(靠近Vss)转折连接,C线二段 不能直接连接,在Vss附近用金属连接。 ③ 用左面一列A、B、C多晶布局器件的串并联,右面一列A、 B、C多晶布局器件的串联。整个电路分为4行,第2和第3行组 成进位电路的前级,第1行和第4行组成求和电路的前级。 ④ 进位与求和的输出反相器采用较大的宽长比。 ⑤ 在版图中间一条横的金属线阻挡了进位部分串并联电路 的输出从上至下进行连接,用多晶从该金属线下穿过将这段输 出金属连接。

17

2. CMOS RAM单元及阵列 (1)CMOS RAM单元

特点:版图用双层金属设计。两个反相器共源,它们的 交叉连接和衬底连接都用金属1,两条位线也用金属1作为连 线。Vdd、Vss和W用金属2作为导线。门管的多晶栅和金属1 连接,然后金属1经过通孔连接到用字线。阱和衬底的接触也 经过通孔连接到Vdd和Vss。

(2列的方向只要求相邻单元位

线的间距符合设计规则;行的布局合并了公共区域,即Vdd和

Vss共用。

19

3. CMOS D触发器 (1) 无置位和复位端的D触发器

电路图

电路图中,用钟控反相器代替反相器和传输门(TG2)串联。

20

版图

特点:1)版图为4行结构,中间两行构成反相器,多晶从第2行延伸到第3行就 形成反相器。

2)第1行和第4行构成传输门,虽然被第2、3行分隔开,但这两行MOS管不需 要多晶共用,只用金属进行源漏连接,即使这些金属连线跨过中间两行有源区,也 不会形成寄生MOS管。

3)CP多晶放在Vdd线下,CPb多晶沿Vss水平布线,在中央部位,这两条多晶 都从有源区的空隙分别延伸到Vdd和Vss线附近,与传输门器件的栅级连接。

9

版图2特点:或非门和与或非门分开布局,P管和N管各占一行。

10

(3)二输入端与门(and2)

特点:与门由与非门和反相器串联而成,采用合并公共区域 的技巧,将P管接电源的有源区公用,N管接地的有源区公用, 器件的排列很紧凑,面积很小。

11

(4) 与或非门(AOI)

提示:设计AOI或OAI的版图,一定要熟练掌握MOS管串联和 并联的画法后进行,看清每个MOS管的输入信号,用棍棒图画 出草图后再画版图。

4)主触发器采用钟控反相器,节省一根金属连线。

21

(2) 带置位端的D触发器

电路图 版图

特点:器件仍分 为4层,CP和CPb也 位于上下两边,并且 在CP多晶的上方增 加一条水平的多晶作 为复位(R)。CPb 线在水平和垂直方向 的连接采用金属过渡。 主触发器采用钟控或 非门,节省一根金属 连线。

(a) 电路图

(b) N1版图 (c) N0版图 (d) N1和N0串联版图

(2) 任意个MOS管串联。例如3个MOS管串联的版图。

(a)电路图

(b) 版图

5

2.MOS管并联(并联是指它们的源和源连接,漏和漏连接,各 自的栅还是独立的。) (1)栅极水平放置,节点X和Y可用金 属连线连接(图b);也可用有源区连接(图c)。

版图设计实例

1

MOS 场效应管的版图实现

单个MOS管的版图实现

1. MOS管的结构和布局

① MOS管的四种布局图

2

③ 源区、沟道区和漏区合称为MOS管的有源区(Active),而有源区之外 的区域定义为场区(Fox)。有源区和场区之和就是整个芯片表面。

Fox + Active = Surface

7

1. CMOS门电路

(1) 反相器

电路图

版图1

版图2

版图1特点:多晶栅竖直排列,MOS管源区面积小,因而反相器面积也小。 版图2特点:多晶栅水平排列,MOS管漏极金属与电源、地金属线之间的 空档允许其它金属线通过,因水平尺寸较大而使面积稍大一些。

8

(2) 异或门

版图1特点:多晶栅竖直放置;MOS管排成4行,第2和第4行构 成或非门,第1和第3行构成与或非门.整个版图较高。

芯片表面包含有源区和场区两部分

④ N阱CMOS集成电路使用P型衬底,NMOS管直接制作在 P型衬底上,PMOS管做在N阱内。

3

⑤ 完整的MOS管版版图必须包含两个部分:a)由源、栅和 漏组成的器件;b)衬底连接。

4

5.1.2 MOS管阵列的版图实现

1.MOS管串联

(1) 两个MOS管的串联。 N1的源、漏区为X和Y,N0的源、漏区为Y和Z。Y是它们的公共区域,如 果把公共区域合并,得到图5.7(d)所示的两个MOS管串联连接的版图。 从电流的方向可以决定,当MOS管串联时,它们的电极按S-D-S-D-S-D方 式连接。

25

26

M3和M4的宽长比很大,M3a、M3b、M4a和M4b都采用多管并联的结构。这四 个MOS管的源已经连接到Metal1导线,为了避免和Metal1交叉短路, M3和M4的漏极 要用Metal2连接。Metal2有很多通孔和很宽的导线,使电流能够顺利通过。

22

4. CMOS放大器

23

分割输入器件实现四方交叉:将M3变为M3a和M3b,M4变 为M4a和M4b,就可以实现四方交叉,保证输入器件的对称 性。

24

由于全部电流都要通过输入晶体管中的每一个,例如,有时整个电 流完全在M3,当差分信号关断时,M3关断M4接通,整个电流又完全在 M4,信号每摆动一次就切换一次,为了承受这一电流,在M3和M4之间 的金属线需要达到一定的宽度,采用二条金属线连接M3和M4的源极,并 且从M4b和M3b的中间向下,这样,M3导通时电流将通过M3a和M3b, 即它的两半把电流向下送到中心导线。

(2)栅极竖直方向排列,节点连接既可用金属导线(图b),也 可用有源区进行连接(图c)。

6

(3)三个或三个以上MOS管并联。 ① 全部用金属进行源的连接和漏的连接(图a),称为叉指形结构; ② 分别用金属和有源区进行源和漏的并联连接; ③ 金属连接和有源区连接联合使用(图b)。

3.MOS管的复联 复联是MOS管先串后并和先并后串的连接。

12

(5) 或与非门(OAI)

提示:对比AOI和OAI电路图和版图的区别和画法,巩固和 熟练掌握CMOS复联电路版图的画法。

13

(6) 全加器

14

版图

15

2019/12/22

16

特点: ① 和异或门相似,几个输入信号被几乎所有的器件公用, 设计版图时要充分注意这一特点。 ② 版图把A、B、C多晶分成二段且排成二列,A线在上面 (靠近Vdd)转折连接,B线在下面(靠近Vss)转折连接,C线二段 不能直接连接,在Vss附近用金属连接。 ③ 用左面一列A、B、C多晶布局器件的串并联,右面一列A、 B、C多晶布局器件的串联。整个电路分为4行,第2和第3行组 成进位电路的前级,第1行和第4行组成求和电路的前级。 ④ 进位与求和的输出反相器采用较大的宽长比。 ⑤ 在版图中间一条横的金属线阻挡了进位部分串并联电路 的输出从上至下进行连接,用多晶从该金属线下穿过将这段输 出金属连接。

17

2. CMOS RAM单元及阵列 (1)CMOS RAM单元

特点:版图用双层金属设计。两个反相器共源,它们的 交叉连接和衬底连接都用金属1,两条位线也用金属1作为连 线。Vdd、Vss和W用金属2作为导线。门管的多晶栅和金属1 连接,然后金属1经过通孔连接到用字线。阱和衬底的接触也 经过通孔连接到Vdd和Vss。