简单8位模型机设计

基于8位模型机的定点原码一位乘法的实现

K e o ds o putro ga z ton;m od lc y w r :c m e r niai e om p e ; i —org na u t i ai ut r po nt— ii l m li c ton; i r og a pl m c opr rm

嵌入式的8位CISC模型机设计 课程设计

嵌入式的8位CISC模型机设计目录一、设计目的.............................................................................................................................. - 1 -二、设计题目及要求.................................................................................................................. - 1 -三、设计方案.............................................................................................................................. - 1 -1.模型机的总体设计........................................................................................................... - 1 -3. 模型机机器指令格式和指令系统................................................................................. - 2 -4.时序产生器的设计原理及时序波形图........................................................................ - 2 -5. 微程序流程图................................................................................................................. - 3 -6、微程序控制器单元........................................................................................................ - 4 -8、机器语言的源程序........................................................................................................ - 5 -四、设计的过程与步骤.............................................................................................................. - 5 -1、设计各单元电路............................................................................................................ - 5 -ALU单元 .................................................................................................................... - 5 -状态条件寄存器单元.................................................................................................. - 6 -暂存寄存器、通用寄存器、地址寄存器、指令寄存器单元.................................. - 6 -1:2分配器单元......................................................................................................... - 6 -3选1数据选择器单元............................................................................................... - 6 -4选1数据选择器单元............................................................................................... - 6 -程序计数器单元.......................................................................................................... - 6 -主存储器单元.............................................................................................................. - 6 -时序产生器单元.......................................................................................................... - 6 -微程序控制器单元...................................................................................................... - 6 -2、设计CISC模型机的顶层电路图................................................................................. - 7 -五、模型机的各单元VHDL源程序......................................................................................... - 7 ---ALU的VHDL源程序ALU.vhd ............................................................................. - 7 ---状态条件寄存器的VHDL源程序LS74.vhd.......................................................... - 8 --- 8位数据寄存器的VHDL源程序LS273.vhd........................................................ - 9 --- 1:2分配器的VHDL源程序FEN2.vhd ............................................................... - 9 ---3选1数据选择器单元VHDL源程序MUX3.vhd .............................................. - 10 ---4选1数据选择器单元VHDL源程序MUX4.vhd .............................................. - 10 ---程序计数器单元VHDL源程序PC.vhd ............................................................... - 11 ---主存储器单元VHDL源程序ROM16.vhd ........................................................... - 12 ---时序产生器单元的VHDL源程序COUNTER.vhd ............................................. - 12 ---控制存储器CONTROM的VHDL源程序CONTROM.vhd .............................. - 14 ---微命令寄存器MCOMMAND的VHDL源程序MCOMMAND.vhd ................. - 15 ---微地址转换器F2的VHDL源程序F2.vhd .......................................................... - 17 ---微地址转换器F3的VHDL源程序F3.vhd .......................................................... - 17 -六、模型机的单元电路图及系统顶层电路图........................................................................ - 18 -七、模型机的功能仿真和硬件验证........................................................................................ - 23 -1、功能仿真波形图.......................................................................................................... - 23 -2、硬件验证...................................................................................................................... - 24 -八、设计总结............................................................................................................................ - 24 -九、参考文献............................................................................................................................ - 24 -课程设计题目:组成原理课程设计嵌入式的8位CISC模型机设计一、设计目的通过课程设计加深对计算机各功能部件的理解;掌握数据信息流和控制信息流的流动和实现过程,建立起整机概念;培养设计、开发和调试计算机的能力。

第3讲—简单模型机设计(微程序实现)

4、微程序编写

编写程序

MOV1

MOV2 ADD

MOV3

HALT

05#,R0 01#,R1 R0, R1 R1,(FA#)

(2)操作码二进制代码

MOV1:0001

MOV2:0010 ADD : 0011

MOV3:0100

HALT: 0101

基本字长 8位 7 4 3 2 1 0 指令格式 操作码OP 寻址方式 寄存器号 寻址方式 寄存器号 源操作数

30↓ R0 +R1 →R1 ↓ PC → MAR ↓ JP

40↓ ↓ PC→ MAR G=1 ↓ PC+1→ PC ↓ RAM → MAR ↓ R1→ RAM ↓ PC → MAR ↓ JP

(5)编制微程序

根据指令流程和微指令格式就可以开始编制

微程序。 指令流程中每一个流程对应一条微指令,结 合总体结构框图图1,写出这个流程所对应的 数据通路的控制命令。 例RAM→IR所需的控制命令是MA, , CPIR并在表3-1中的相应位置填写上“1”, 不需要的命令填写“0”。 另外每一条微指令都要确定下条微指令地址 的生成方式。

图9中的 后继地址形成电路

功能:多路选择器 当JP=1,QJP=0时,Y7Y6Y5Y4Y3Y2Y1Y0 = μIR15 μIR14 μIR13 μIR12 μIR11 μIR10 μIR9 μIR8 当JP=0,QJP=1时,Y7Y6Y5Y4Y3Y2Y1Y0 = IR7 IR6 IR5 IR4 0000 链接时, Y7Y6Y5Y4Y3Y2Y1Y0连接µPC的D7~D0, µPC的RE接高电 平vcc。

操作码OP共4位,最多可定义16条指令。

8位模型计算机的设计

BUS←RAM,DR1←BUS

OUT←DR1

(5)JMP 指令

无条件转移指令 JMP,以紧跟在操作码后的字节的内容作为转移地址。将该

二. 指令系统结构及其功能确定 ..................... 5 1.模型及指令系统 ................................ 5 2.模型机的微指令 ................................ 6 3.微程序设计方法 ................................ 7

AR←PC, PC←PC ;以 AR 的内容作为去操作数的地址 BUS←RAM,AR←BUS ;AR 指向存放操作数的 ARM 单元 BUS←RAM,DR2←BUS ;RAM 中的数据通过 BUS 送 DR2

将 R0 中的数据送 DR1,即 DR1←R0

在 ALU 中进行加法运算,运算结果送 R0,即 R0←(DR1)+(DR2)

(3)STA 指令 向 RAM 写数据操作的 STA 指令已紧跟在操作码后的字节作为存放操作数的地

址,将 R0 中的数据存入该地址单元。首先将紧跟在操作码后的字节的内容送地 址寄存器 AR:

AR←PC,PC←PC+1 ;以 PC 的内容作为存数据的地址 BUS←RAM,AR←BUS ;AR 指向存放操作数的 RAM 单元 然后将 R0 的内容写入该地址的 RAM 单元中: BUS←R0,RAM←BUS (4)OUT 指令 输出指令 OUT,以紧跟在操作码后的字节作为读出数据的地址,将该单元的 内容通过 DR1 输出到 OUT 端口。首先将紧跟在操作码后的字节的内容送给地址 寄存器 AR: AR←PC,PC←PC+1 ;以 PC 的内容作为取数据的地址 BUS←RAM,AR←BUS ;AR 指向存放操作数的 RAM 单元 然后将 RAM 单元的内容读出到 DR1,并送往输出端口 OUT:

基于8位模型机的定点原码一位乘法的实现

基于8位模型机的定点原码一位乘法的实现摘要:本文介绍了基于8位模型机的定点原码一位乘法的实现方法。

首先介绍了定点原码乘法的基本概念,然后详细讲解了实现过程中所需的寄存器、逻辑电路和运算流程,并给出了具体的示例。

最后,对该方法的优缺点进行了讨论,并提出了改进方法。

关键词:定点原码乘法;8位模型机;寄存器;逻辑电路;运算流程;优缺点;改进方法一、引言定点原码乘法是数字电路设计中的基本运算之一,其实现方法多种多样。

本文介绍了基于8位模型机的定点原码一位乘法的实现方法,该方法具有简单、直观、易于理解等优点,适合初学者学习。

二、定点原码乘法的基本概念定点原码乘法是指两个定点数相乘的运算。

定点数是指小数点位置固定的数,一般用二进制表示。

定点数可以分为无符号数和有符号数两种。

无符号数是指没有正负之分的数,而有符号数则包含正负两种情况。

在定点原码乘法中,两个数的小数点位置相同,相乘后的结果的小数点位置也相同。

在计算机中,定点原码乘法通常使用加法器和移位器实现。

三、实现过程1. 寄存器实现定点原码乘法需要使用多个寄存器,主要包括乘数寄存器、被乘数寄存器、积寄存器、进位寄存器等。

乘数寄存器用于存储乘数,被乘数寄存器用于存储被乘数,积寄存器用于存储乘积。

进位寄存器用于存储进位信号,通常为1或0。

2. 逻辑电路实现定点原码乘法需要使用多个逻辑电路,主要包括加法器、移位器、比较器等。

加法器用于实现乘法中的加法操作,移位器用于实现乘法中的位移操作,比较器用于判断乘积是否溢出。

3. 运算流程定点原码乘法的运算流程如下:(1)将乘数和被乘数分别存入乘数寄存器和被乘数寄存器中;(2)将积寄存器清零;(3)按位乘法的规则,将乘数的最低位与被乘数相乘,并将结果加到积寄存器中;(4)将乘数右移一位,被乘数左移一位;(5)重复步骤3和步骤4,直到乘数的所有位数都处理完毕;(6)判断乘积是否溢出,若溢出则进行相应的处理。

4. 示例以乘数为1011,被乘数为1101为例,演示定点原码乘法的实现过程。

8位模型机设计-指令系统及通用寄存器设计

东北大学秦皇岛分校计算机与通信工程学院计算机组成原理课程设计专业名称计算机科学与技术班级学号学生姓名指导教师设计时间2014.12.22~2015.1.2课程设计任务书专业:计算机科学与技术学号:学生姓名(签名):设计题目:8位模型机设计-指令系统及通用寄存器设计一、设计实验条件综合楼808实验室二、设计任务及要求总的设计目标是:设计一个8 位的模型机,其组成为:总线结构:单总线,数据总线位数8位、地址总线8位;●存储器:内存容量64K*8bit●控制器:用硬联线控制器实现26位微操作控制信号●运算器:单累加器,实现加、减等8种操作外设:●输入:用开关输入二进制量●输出:7段数码管和LED显示指令系统规模:64 条指令,7种类型,5种寻址方式本组任务是:1.设计12、15、22、32号指令;2.模型机的通用寄存器R1设计;3.BCD编码器的设计。

三、设计报告的内容1.设计题目与设计任务(设计任务书)设计内容如下:1、指令系统设计:ADDC A, #II 将立即数II加入累加器A中带进位SUB A, EM 从A中减去存储器EM地址的值AND A, @R? 累加器A“与”间址存储器的值MOV A, #II 将立即数II送到累加器A中2、模型机硬件设计:通用寄存器R13、逻辑电路设计:BCD码编码器2.前言(绪论)(设计的目的、意义等)1.融会贯通计算机组成原理课程的内容,通过知识的综合运用,加深对计算机系统各个模块的工作原理及相互联系的认识;2.学习运用VHDL进行FPGA/CPLD设计的基本步骤和方法,熟悉EDA的设计、模拟调试工具的使用,体会FPGA/CPLD技术相对于传统开发技术的优点;3.培养科学研究的独立工作能力,取得工程设计与组装调试的实践经验。

3.设计主体(各部分设计内容、分析、结论等)【系统设计】1、模型机逻辑框图图1 模拟机整体逻辑框图图2 XCV200芯片引脚图3 CPU逻辑框图2、指令系统设计:ADDC A, #II 将立即数II加入累加器A中带进位助记符:ADDC A, #II类型:算数运算指令寻址方式:立即数寻址指令格式:第一字节001011XX第二字节立即数:SUB A, EM 从A中减去存储器EM地址的值助记符:SUB A, EM类型:算数运算指令寻址方式:存储器直接寻址指令格式:第一字节001110XX第二字节存储地址:AND A, @R? 累加器A“与”间址存储器的值助记符:AND A, @R?类型:算数运算指令寻址方式:寄存器间接寻址指令格式:第一字节010101XX:MOV A, #II 将立即数II送到累加器A中助记符:MOV A, #II类型:数据传送指令寻址方式:立即数寻址指令格式:第一字节011111XX第二字节立即数3、微操作控制信号:外部设备读信号,当给出了外设的地址后,输出此信号,从指定外设读数据。

计算机硬件课程设计(微程序)

三、设计模型计算机的思路

1、确定设计目标:确定所设计计算机的功能和用 途。 2、确定指令系统:确定数据的表示格式、位数、 指令的编码、类型、需要设计哪些指令及使用的 寻址方式。 3、确定总体结构与数据通路:总体结构设计包含 确定各部件设置以及它们之间的数据通路结构, 列出各种信息传送路径以及实现这些传送所需要 的微命令。 4、设计指令执行流程:数据通路确定后,就可以 设计指令系统中每条指令的执行流程。根据指令 的复杂程度。

五、时间安排

第一批:周一上午至周三上午, 本周五下午交报告 第二批:周三下午至周五下午, 下周一下午交报告 上午8:10—11:30 下午2:00—5:00

六、硬件课程设计报告格式

请看样本

七、具体要讲的几个问题

1、指令格式、指令系统:讲各种指令格式,寻址方式,看实验 指导书P33 2、举例讲微操作流程,如ADD RS,RD:看实验指导书P26 3、举例讲微指令编写:看实验指导书的P25 4、微程序的入口地址形成及微指令的后续地址:看实验指导书 的P4 译码电路 5、装载微程序的格式:看实验指导书的P19 6、模型机的时序电路:看实验指导书的P2 7、运行模型机:运行前先要复位(按RESET或拨动CLR开关1-01),按单微指令按钮进行单步调试,按连续按钮进行连续运 行; 8 、模型机电路图:双击CMPP20,在帮助中找到“复杂模型机 图” 9、模型机高度过程中常见问题及解决办法

299移位控制功能表

s1 299-b

0 0 0 1 0 0 任意 0 保持 循环右移s0Biblioteka m功能0 0

0 任意

1 0

0 1

0 1

1 1

1 0

1 任意

带进位循环右移 循环左移

带进位循环左移 装数

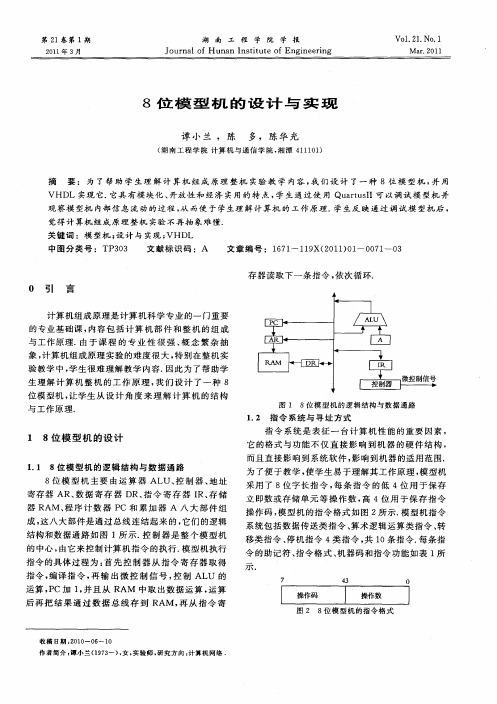

8位模型机的设计与实现

结 构和数 据通 路如 图 1所 示. 制 器 是 整个 模 型 机 控

的 中心 , 由它 来控制 计算 机指 令 的执行 . 型机执行 模 指 令 的具 体过程 为 : 先 控 制器 从 指令 寄 存 器 取得 首 指令, 编译 指 令 , 输 出微 控 制 信 号 , 制 AL 的 再 控 U 运算 , C加 1 并且 从 RAM 中取 出数 据 运算 , 算 P , 运

方式后 , 要掌握 其它类 型 的 寻址 方 式 ( 接寻 址 等) 间 就 比较 容易 了. 由于我 们 设计 模 型 机 的主要 目的 又 是 为 了使 学生掌握 计算机 的工作 原理及 指令在 计算 机 中执行 的流程 , 而不 是 真 正要 实 现一 台计算 机 产 品 , 以我们 只在模 型机 中实现这 两种 寻址方式. 所

觉得 计 算 机 组 成 原 理 整 机 实验 不 再 抽 象 难 懂 . 关 键 词 :模 型 机 ; 计 与 实 现 ; 设 VHDL 中 图 分 类 号 :T 3 3 P 0 文 献 标 识 码 :A 文 章 编 号 : 1 7 一 l 9 ( 0 10 — 0 7 —0 6 1 lX 2 1 )1 0 1 3

立 即数或 存储 单元 等操 作 数 , 4位用 于保 存 指令 高 操 作码 , 模型 机 的指令 格式 如图 2 示. 所 模型 机指令

系统 包括 数据 传送 类指 令 、 术逻辑 运算 类指令 、 算 转 移类 指令 、 停机 指令 4类 指令 , 1 共 0条指令 . 每条 指 令 的助记 符 、 令格 式 、 指 机器码 和指令 功能 如表 1所

存 器读 取 下一 条指令 , 次循 环. 依

0 引 言

计算 机组成 原理是 计算 机科 学 专业 的一 门重 要 的专 业基础 课 , 内容 包 括 计算 机 部 件 和 整 机 的组 成

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

计算机组成原理

课程设计报告

13073210

2015.7. 12

8位模型机总体结构设计

8位模型机数据通路设计

8位模型机具体部件设计图时序发生器

CLK : 时钟信号

HALT: 停机信号

m[7..0] : 输出时序信号

Timer波形

程序计数器

CPPC :上升沿控制信号

PC1 :PC自加一控制信号

PC-BUS :三态门控制

BUS[7..0] : 数据输入/输出

运算器

BUS[7..0] : 数据输入/输

出

CPSA:A暂存器控制信

号

CPSB:B暂存器控制信

号

ALU-BUS :三态门控制

CN :运算信号

M :运算信号

S[3..0] :运算控制信号

通用寄存器组

BUS[7..0] : 数据输入/输出

WE :写入控制信号使能端

WA :寄存器写入控制信号

WB :寄存器写入控制信号

RE:读取控制信号使能端

RA:寄存器读取控制信号

RB :寄存器读取控制信号

主存

BUS[7..0] : 数据输入

/输出

CPMAR : 主存地址写

入控制信号

WRE :主存写入控

制使能端

WR :主存写入控制

信号

RD主存读取控制信

号

RAM-BUS :三态门

控制

CPMDR :主存数据写入控制信号

总线暂存器

BUS[7..0] : 数据

输入/输出

CPBUS :暂存

器输入控制信

号

OUTBUS:暂存

器输出控制信号

uPC

IR

控存

8位模型机机器指令设计

8位模型机微指令表

8位模型机微指令

8位模型机模型机调试波形

MOV A, 88H

MOV B, 66H

ADD A, B

DEC A

AND A, B

INC A

HALT

JMP 80h

8位模型机指令汇总公共取值(小组共同)

MOV A , 88H (小组共同)MOV B , 66H (自己设计)ADD A, B (小组共同)DEC A (自己设计)

AND A, B (小组设计)DEC A (自己设计)

JMP 80H (小组设计)HALT (小组设计)

心得体会

在完成了本次课程设计后,我的感触颇多。

首先,我深刻的体会到了计算机结构的复杂性,感受到这门学科的奥妙和趣味,真正的意识到计算机是人类历史上最伟大的发明。

我已经能够自己模拟制作出一个简单的8位模型机,深刻的学习到了模型机的工作原理,这是课本所无法提供的一种富有意义的实践。