cadence基础学习

Cadence新手简明教程(1)

9

10

11

需要填这两项

12

里面不需要 snap to grid

边框和引脚必须 snap to grid, 保证电气属性

13

14

15

如果需要更改原理图页大小,可以在工程文 件目录中选择相应的原理图页,右键选择 schematic page property

16

17

18

按p调出右侧的 place part窗口 从中选取需要的 元件,双击或 enter或点击面板 上的放置按钮摆 放该元件,可放 任意多个,放完 按ESC退出。

在库中更改了元件,还需要在design cache中选中对应的design cache,右键 选择“update cache”之后才能使用。

29

30

31

32

33

34

网络表文件(连接关系)

物理封装信息及器件属 性、驱动类型(room、value等) 驱动分配文件(电压需求、

替换封装类型及电气特性等)

3.层次块上下层之间可以用hierarchical Port来连接

24

25

26

27

Part可以整个复制过来,然后再局部修改

28

Edit part

Edit part在关闭图页的时候会询问update “current”还是“all”,如果想放弃修改, 点击discard。

这里需要注意一点,即使你在原理图中更 改了part,库中的这个元件仍然没有变化。

1

Cadence公司是一个专门从事电子设计自 动化(EDA)的软件公司,是全球最大的电 子设计技术(Electronic Design Technologies)、程序方案服务和设计服务 供应商。产品涵盖了电子设计的整个流程, 包括系统级设计,功能验证,IC综合及布局 布线,模拟、混合信号及射频IC设计,全定 制集成电路设计,IC物理验证,PCB设计和 硬件仿真建模等。

Cadence基础培训

11-19-2004

Leijianming

模型设定setup— environment…选项,设置如 下

11-19-2004

Leijianming

选择分析 直流扫描

11-19-2004

Leijianming

选择需要plot输出的节点电 压。 此时看到的界面如下图:

11-19-2004

Leijianming

11-19-2004 Leijianming

11-19-2004

Leijianming

画出完整的CMOS反相器电路 原理图以及参数设置

11-19-2004

Leijianming

说明

调用的instance包括: vdd,vss,gnd,nmos4,pmos4,vsin, vdc,cap 所有的instance都在analogLib库中调用 全部选用symbol视图。

启动cadence环境,界面如下 icfb &

11-19-2004

Leijianming

从主菜单tools项中打开library manager 库管理器,如图所示

11-19-2004

Leijianming

11-19-2004

Leijianming

下面开始画CMOS反相器的原理图

从library manager 菜单中选择 file—new— library 建立一个新的库 Training 从library manager 菜单中选择 file—new— cell view 建立一个新的单元 MyInv 选用的工具(tool)为composer- schematic,这样点击OK以后直接进入原 理图编辑界面。

11-19-2004

Leijianming

cadence入门教程

cadence入门教程(一)linux常用命令1、cd“cd FileName”是进入FileName文件夹。

“cd..”是进入上一层目录,主要那里是两个点。

2、ls这是最基本的文件命令,用以显示某一个目录中的文件。

可以在ls后加上所要观察的目录名称或文件的名称,如果你在下ls命令后没有接任何的目录名,它将会显示出目前目录中所有文件。

ls可以带一些参数,给予用户更多相关的信息:-a:在UNIX中若一个目录或文件名字的第一个字元为".",该文件为隐藏文件,使用ls将不会显示出这个文件的名字。

如cshell的初始化文件.cshrc,如果我们要察看这类文件,则必须加上参数-a。

-l:这个参数代表使用ls的长(long)格式,可以显示更多的信息,如文件存取权,文件拥有者(owner),文件大小,文件更新日期,或者文件链接到的文件、文件夹。

-F:给目录、可执行文件、符号链接以特殊的标记,在可执行文件后面加“*”、目录后面加“/”、符号连接后面加“@”,以方便用户区别。

3、cpcp命令用于将一个或多个文件复制成另一个文件或者是将其复制到另一个目录去。

cp有三种基本格式如下:cp source target将文件名为source的文件复制一份为文件名为target的文件。

如果target文件不存在,则产生文件名为target的文件,如果target文件存在,缺省时自动覆盖该文件。

cp file1file2…dir将文件file1file2...都以相同的文件名复制一份放到目录dir里面。

cp-r source target拷贝整个目录,将source目录下的所有文件和文件夹复制到target目录下。

cp命令常用的选项参数有:-i:交互(interactive)模式,当文件名为target的文件存在时,缺省情况下该命令会自动将原来target的内容覆盖掉,加上改选项将询问用户是否覆盖。

用户输入y(yes)则执行复制的动作,否则放弃复制。

cadence基本使用学习

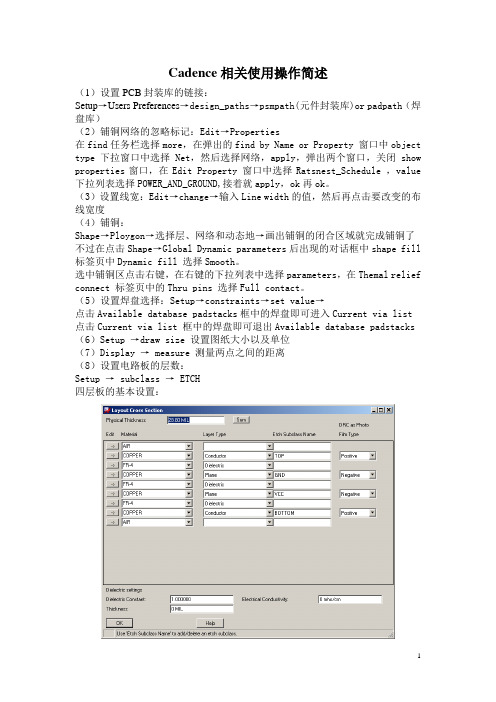

Cadence相关使用操作简述(1)设置PCB封装库的链接:Setup→Users Preferences→design_paths→psmpath(元件封装库)or padpath(焊盘库)(2)铺铜网络的忽略标记:Edit→Properties在find任务栏选择more,在弹出的find by Name or Property 窗口中object type下拉窗口中选择Net,然后选择网络,apply,弹出两个窗口,关闭show properties窗口,在Edit Property 窗口中选择Ratsnest_Schedule ,value 下拉列表选择POWER_AND_GROUND,接着就apply,ok再ok。

(3)设置线宽:Edit→change→输入Line width的值,然后再点击要改变的布线宽度(4)铺铜:Shape→Ploygon→选择层、网络和动态地→画出铺铜的闭合区域就完成铺铜了不过在点击Shape→Global Dynamic parameters后出现的对话框中shape fill 标签页中Dynamic fill 选择Smooth。

选中铺铜区点击右键,在右键的下拉列表中选择parameters,在Themal relief connect 标签页中的Thru pins 选择Full contact。

(5)设置焊盘选择:Setup→constraints→set value→点击Available database padstacks框中的焊盘即可进入Current via list 点击Current via list 框中的焊盘即可退出Available database padstacks (6)Setup →draw size 设置图纸大小以及单位(7)Display → measure 测量两点之间的距离(8)设置电路板的层数:Setup → subclass → ETCH四层板的基本设置:(9)设置好相应的层显示,然后manufacture→artwork→添加相应的层工艺文件详细设置情况见笔记本。

cadence入门教程

Cadence 系列软件从schematic到layout入门一.客户端软件使用及icfb启动要使用工作站上的软件,我们必须在PC中使用xwinpro等工具连接到工作站上。

从开始菜单中,运行xwinpro的xSettings,按照下图设置:点击上图的Settings在出现的窗口中按如下设置(connect host选择为192.168.1.137):设置完后,从开始菜单中运行xwinpro的xsessions,应该就可以进入登陆界面,用户名为user1,密码为root。

二、SchematicCadence系列软件包含了电路图工具Schematic,晶体管级电路仿真工具Spectre,以及版图工具Virtuoso等。

一般来说,我们先用Schematic画好电路原理图然后进行仿真,最后用Virtuoso手动画版图或者直接进行版图综合,最后对版图进行L VS,DRC等验证。

在登陆进工作站后,点击鼠标右键,选择tools——>terminal,在弹出的terminal窗口中敲入命令icfb&就可以启动cadence了。

图1 icfb的主界面我们以建立一个反相器电路为例子:在icfb中,任何一个电路,不论是已经存在的可以引用的库,还是用户新建立的一个电路,都是一个library. 一个library一般有若干个Cell(单元电路),每个cell有若干个schematic(电路原理)和若干个layout(版图)。

所以,我们要做的第一步,就是先创建一个自己的“库”,File菜单->new->library图2 新建一个库的界面从这个新建一个library的界面,我们必须输入新建立的库的名称,并且选择好这个库应该存放的目录,然后注意看右边的三个选项,关于新建立的库是否需要链接到Technology File 的问题。

首先,这个Technology File一般是指工艺库,由Foundry提供。

cadence基本使用学习-推荐下载

删除 fixed 属性

(13)设置 ROOM(注:在原理图设计时应该设定好 ROOM 区,这样才能在 PCB 布 局时加入 ROOM)

Edit→Properties Find by name 选择 Comp(or Pin) →点击 more →添加元件→apply 在 Edit property 选择 Room 输入 Room 名称 ok 确定即可。

(11)设置附加网络的间距: setup→Constrains→attach property ,net 设置附加的网络名 set values 设置布线间距值 Assignment table 改变设置 (同理设置物理规则,设置线宽和孔径)

(12)为元件设置 fixed 属性

使用图标:添加 fixed 属性

(14)使用

(注:在画分割平面的方框区域时要设置 Boundary 的显示) (15)设置过孔显示

Setup→Drawing Option→Display : Display plated holes

分割平面

对全部高中资料试卷电气设备,在安装过程中以及安装结束后进行高中资料试卷调整试验;通电检查所有设备高中资料电试力卷保相护互装作置用调与试相技互术关,系电通,力1根保过据护管生高线产中0不工资仅艺料可高试以中卷解资配决料置吊试技顶卷术层要是配求指置,机不对组规电在范气进高设行中备继资进电料行保试空护卷载高问与中题带资2负料2,荷试而下卷且高总可中体保资配障料置各试时类卷,管调需路控要习试在题验最到;大位对限。设度在备内管进来路行确敷调保设整机过使组程其高1在中正资,常料要工试加况卷强下安看与全22过,22度并22工且22作尽22下可护都能1关可地于以缩管正小路常故高工障中作高资;中料对资试于料卷继试连电卷接保破管护坏口进范处行围理整,高核或中对者资定对料值某试,些卷审异弯核常扁与高度校中固对资定图料盒纸试位,卷置编工.写况保复进护杂行层设自防备动腐与处跨装理接置,地高尤线中其弯资要曲料避半试免径卷错标调误高试高等方中,案资要,料求编试技5写、卷术重电保交要气护底设设装。备备置管4高调、动线中试电作敷资高气,设料中课并技3试资件且、术卷料中拒管试试调绝路包验卷试动敷含方技作设线案术,技槽以来术、及避管系免架统不等启必多动要项方高方案中式;资,对料为整试解套卷决启突高动然中过停语程机文中。电高因气中此课资,件料电中试力管卷高壁电中薄气资、设料接备试口进卷不行保严调护等试装问工置题作调,并试合且技理进术利行,用过要管关求线运电敷行力设高保技中护术资装。料置线试做缆卷到敷技准设术确原指灵则导活:。。在对对分于于线调差盒试动处过保,程护当中装不高置同中高电资中压料资回试料路卷试交技卷叉术调时问试,题技应,术采作是用为指金调发属试电隔人机板员一进,变行需压隔要器开在组处事在理前发;掌生同握内一图部线纸故槽资障内料时,、,强设需电备要回制进路造行须厂外同家部时出电切具源断高高习中中题资资电料料源试试,卷卷线试切缆验除敷报从设告而完与采毕相用,关高要技中进术资行资料检料试查,卷和并主检且要测了保处解护理现装。场置设。备高中资料试卷布置情况与有关高中资料试卷电气系统接线等情况,然后根据规范与规程规定,制定设备调试高中资料试卷方案。

Cadence快速入门教程

Cadence软件不同于Altium Desginer软件,尤其在集成库方面有很大的区别,AD的封装集成库可以包含多个,而Cadence每个元器件的封装是独立的,在绘制封装的过程中,需要先利用Pad Designer添加焊盘,之后利用PCB Editor绘制元件的封装,再在PCB Editor中绘制PCB,过程比较复杂。

其次,AD的一个工程文件即可直接绘制原理图与PCB,而Cadence软件则是独立的,画原理图利用Design Entry CIS,画焊盘利用Pad Designer,画PCB利用PCB Editor。

AD可以直接添加焊盘,而Cadence需要建立封装,再添加,过程较复杂。

但是,Cadence软件的功能十分强大,逻辑性更强,十分值得学习!CONTENTSCONTENTSPARTONE OrCAD Capture原理图设计利用Capture创建原理图工程-以创建一个STM32的最小系统为例:1、点击打开Design Entry CIS (图标如右图1所示),在弹出的Cadence Product Choices 对话框中 选择功能比较强大的OrCAD Capture CIS,单击OK 按钮,启动后的Capture CIS 初始界面如图2所示:2、执行菜单命令File--New--Project,进行新建工程,在弹出的New Project 对话框,在Name 栏输入EXERCISE_SCH ,选中最后一个Schematic 单选按钮,表示绘制原理图,如图3所示:图1软件图标图2OrCAD Capture CIS 的初始界面图3New Project 对话框3、在New Project对话框单击Browse选择文件保存路径,在Drives 处选择工程所在的盘路径,单击Create dir按钮,填入新建文件夹的名称,单击OK按钮,创建文件夹,其中文件夹可提前建好,直接选择路径即可,本例的文件夹名称为EXERCISE。

Cadence基本操作、快捷键、基础知识

一、基本操作(一)电路图绘制1、登陆到UNIX系统。

在登陆界面,输入用户名***和密码***** 。

2、Cadence的启动。

登录进去之后,点击Terminal出现窗口,输入icfb命令,启动Cadence软件。

3、根据设计指标及电路结构,估算电路参数。

4、利用Candence原理图的输入。

(1)Composer的启动。

在CIW窗口新建一个单元的Schematic视图。

(2)添加器件。

在comparator schematic窗口点击Add-Instance或者直接点i,就可以选择所需的器件。

(3)添加连线。

执行Add-Wire,将需要连接的部分用线连接起来。

(4)添加管脚。

执行Add-Pin和直接点p,弹出添加管脚界面。

(5)添加线名。

为设计中某些连线添加有意义的名称有助于在波形显示窗口中显出该条线的信号名称,也可以帮助检查电路错误。

点击Add-Wire Name,弹出新窗口,为输入输出线添加名称。

为四端的MOS器件的衬底添加名称vdd!或gnd!,其中!表示全局变量。

(6)添加电源信号,根据不同的仿真电路设置不同的电源参数。

(7)保存并检查。

点击schematic窗口上的Check and Save按钮,察看是否有警告或者错误。

如果有,察看CIW窗口的提示。

4、利用Candence原理图的输入。

(二)电路图仿真(1)启动模拟仿真环境。

在comparator schematic窗口,选择Tools-Analog Environment,弹出模拟仿真环境界面。

(2)设置模型库。

(3)设置分析类型。

在仿真窗口,点击Choose Analyses按钮,弹出Choose Analyses窗口,该窗口中列出了各种仿真类型,依次进行各种仿真,如ac、dc、tran,进行交流仿真、直流仿真、瞬态仿真。

(4)设置波形显示工具。

Cadence中有两种波形显示工具:AWD和wavescane,在仿真窗口选择Session-assign,在弹出的窗口中可以选择波形显示工具为AWD或wavescane。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

教程实例:DSP最小系统教程内容:1、利用Capture CIS[原理图设计]进行原理图设计2、利用Cadence PCB Editor[PCB编辑器]布局布线3、光绘文件(Artwork)制作,生成Gerber 文件1mil=0.0254mm一原理图放大I 缩小O图纸右下角标注:Design Template[设计模板]1、创建新工程文件库文件2、参考datasheet在库文件中添加新元件:Place pin(画管脚编辑属性,power型visible)、Place pin array(管脚阵列)全部元件在Spreadsheet表中编辑(全选右键单击edit properties)可以在新建元件时选New Part Creation Spreadsheet 通过表格创建多引脚元件常用选项:Option-part properties / package properties[属性]画不规则元件:Preference[优先权]中取消Pointer snap to Grid[指针对齐网格],随意划线,画完再改回去3、分裂原件:homogeneous(完全相同)、heterogeneous(多个功能模块不同)以NE5532 为例Tools-Annotate:给元件编号原理图中多个heterogeneous分裂原件的分组问题:库文件中选中分裂原件,在part properties 中新建new property(name如package不可为group,value为组号123等),分裂原件的多个部分都要执行上一操作;打开原理图,双击分裂原件在property editor 中将package属性设置为相同则为同一组分裂原件;要给之编号还需在annotate[注释]菜单physical packaging栏中将最后一项改为上文中name名大型元件的分割:参考《cadence电路设计案例精析》P184、在工程中添加元件库(自建库、系统库)电容电阻电感变压在discrete库中不知道元件在哪个库可以搜索“放置元件”的意思是:place part 5、元件的连接:直接连、用网络别名连接(在同一原理图页面中place net alias,名称相同表示电气上连接在一起)引脚悬空(末端连Place no connect[没有连接的地方])最好不要在放置元件时就把元件连在一起6、总线:功能类似的信号总线连接:Place-Bus 默认直角拐弯按住shift拉任意转方向画总线命名net alias(规则:XX[起始:结束])拖到总线上连接管脚与总线:place bus entry、按F4连续放置总线入口、信号线(与总线名一致)总线之间的连接:T型交叉有电气连接十字无实际电气连接不同页面之间的连接:place off-page connect 实际上与同一页面连接时net alias相似7、浏览BROWSE-元件parts(容易发现元件编号和大小错误)、网络Nets(双击看某一网络与哪些部分连接)页面之间进行互联的网络:Browse-off page connectors、电气检查中的错误查看DRC搜索Find元件parts、网络nets、Netlist修改元件库后更新元件:replace/update cache工程已经不在的元件在cache中删掉cleanup cache8、给元件添加封装信息:双击元件打开Property Editor,在PCB Footprint中标注封装批量修改封装:多选……在元件库中添加封装信息:打开库,选择元件-option-Package Property,回到项目中选中更改封装的元件-replace cache-选择replace schematic part property生成网表:先元件重编号Annotate、再DRC(design rules check)检查、选中dsn文件-Tools-create netlist-PCB Editor生成元件清单BOM,两种:1)Reports-CIS Bill of Materials-standard2)Tools- Bill of Materials二、PCB高速电路设计流程原则:设计即正确1、工具介绍Allegro PCB Editor用于创建修改设计文件,是主要的设计工具,有两种模式:layout mode和symbol creation mode,进行手工布局布线时,工作在layout mode下,symbol creation mode中可以创建和修改package symbol、mechanical symbol、formal symbol、shape symbol、flash symbol Pad Designer创建及修改焊盘Padstack DBdoctor用于检查设计数据中的错误Allegro Constraint ManagerAllegro约束管理器、布局布线约束规则的创建、管理、评估、检查Allegro PCB Router自动布线工具,对于有复杂涉及规则的高密度电路板处理能力很强Allegro PCB SI/PI信号/电源完整性仿真工具2、PCB设计流程(理论):1) 规划出所设计电子设备的各项系统的规格,包括系统功能、系统的大小、运作情况以及成本2) 做出系统的功能方块图,同时将每个方块之间的关系表示出来3) 根据系统的功能方块图将系统分割成数个PCB,可以缩小系统的尺寸,同时可以使系统具有升级与交换零件的能力4) 决定各PCB使用的技术以及电路数量,决定板子的大小。

在选择技术时要考虑线路图的品质和速度5) 通过原理图绘制工具绘制出PCB电路概图,表示出各零件间的相互连接细节6) 为了确保设计出来的电路图可以正常运作,需要进行初步设计的仿真运作,通过计算机软件读取设计图,显示电路运作的情况7) 布局,根据零件间的连接,一最有效率的方式与路径将各元件放置妥善,使元件间的连接尽可能的短,并且通过的层数尽可能的少。

可以通过计算机软件测试布线的可行性,检查各零件摆放的位置是否可以正确连接,以及能否实现高速运作8) 布线,根据设定好的规定,将电路板上的各元件连接起来,即完成布线操作,可以先手动完成重要原件的布线,然后进行自动布线9) 布线后仿真,为了确定线路在导线后能正常运行,需要通过最后检查,同时可以检查布线过程中是否有错误的连接,仿真过程中测定信号完整性问题及电磁兼容性问题,保证电路板的性能良好10) 建立制作档案,根据设计内容建立包含信号、电源以及地线层的平面图,阻焊层与网板印刷的平面图,还有钻孔与存放等指定档案,提供给制造厂商,便于生产电路板3、两个概念class、Subclass绘制电路板最终在电脑上形成一个数据库,元件线路都是一些数据,cadence利用class和Subclass组织这些数据每放置一个东西都要指定其属于哪个class、Subclass,与windows的类、子类相似在一个PCB中,一个个Subclass的打开,了解各subclass4、不知道选多大焊盘?国际标准IPC7351 参考软件PCB Matrix IPC LP View焊盘制作工具Pad Designer:参考IPC在Begin Layer中设置焊盘形状大小,加焊层PASTEMASK一般与焊盘大小一致,阻焊层SOLDERMASK一般比焊盘大0.1mm就够了元件封装编辑:打开PCB Editor-File-New Drawing(Package Symbol)-Setup- design parameters修改图纸参数-Layout-pin-在option中找到焊盘类型,设置XY方向焊盘个数、间距等参数-放置在页面上(命令窗口输入坐标可确定放置点,eg.x 0 0表示放于原点创建元件必需的:引脚(设置焊盘)、丝印(silkscreen)、图形边框、参考编号(label-ref)、安装区Place Bound(只是一个图形上的区域用来检查元件之间是否有重叠,)装配外框:在Package Geometry-Assembly Top层Add-Line 丝印:Package Geometry-Silkscreen Top层Add-Line安装区:Package Geometry-Place Bound层Add-Line参考编号:Layout-Labels-Ref Des 在Assembly Top层5、创建复杂的BGA封装:?no.22创建自定义焊盘-先创建新图形-分图形、合并Merge-create 添加新创建焊盘、图形的路径:user preference-padpath、psmpathno.25 通孔类元件的封装关于flash焊盘(花焊盘、热风焊盘:在大面积的接地中,常用元器件的引脚与其连接,对连接引脚的处理需要进行综合的考虑,就电气性能而言,元件引脚的焊盘与铜面满接为好,但对元件的焊接装配就存在一些不良隐患如:①焊接需要大功率加热器。

②容易造成虚焊点。

所以兼顾电气性能与工艺需要,做成十字花焊盘,称之为热隔离heat shield,俗称热焊盘Thermal)no.26 带非电气属性引脚的元件封装(再看)6、画电路板new-board边框(Board_Geometry类Outline 子类)——倒角(Manufacture-Dimension-chamfer45角/fillet圆弧角)——允许布线区域(Setup-Area-Route Keepin)——允许摆放区域(Pachage Keepin或者用Z-copy 命令设置与上一边框的距离)7、No.28设置层叠结构Setup-Cross-section添加层-设置层类型Layer Type、材料Material、名Etch Subclass name、正负片positive /negative 内电层铺铜:Z-copy设置好类和子类,选中Create dynamic shape,复制所在区域的边框(GND和Power层都要上述操作)稍后看看完全学习手册的第五章——由原理图到PCB前的准备工作8、No.29布局前的准备工作导入网表:File-Import-Logic栅格点设置:Setup-Grids 可以分层设置Etch电气层Non-Etch非电气层Setup-Drawing option 显示元件摆放状况等9、No.30 手动放置元件:place-manually。