直接数字频率合成器DDS研究设计毕业论文

直接数字频率合成器DDS精度提高方法研究

第22卷第3期Vol.22,No.3滨州学院学报Journal of Binzhou U niversity 2006年6月J un.,2006直接数字频率合成器(DDS )精度提高方法研究收稿日期:20051226基金项目:山东省信息产业厅资助项目(2005R00012)第一作者简介:李建磊(1975—),男,山东惠民人,助理实验师,从事嵌入式系统、分布式计算研究.李建磊,马 震,庄 波,吕凤杰(滨州学院计算机科学技术系,山东滨州256603) 摘要:讨论了直接数字频率合成器(DDS )的工作原理,并根据正弦波的特点对ROM 进行优化.优化的ROM 在Flex10k10的FP GA 芯片上实现,对实验结果进行比较和分析发展,该方案可以有效地改进DDS 的精度. 关键词:数字频率合成器;精度;FP GA 中图分类号:TN 741 文献标识码:A 文章编号:16732618(2006)030043040 引 言 频率合成技术是指利用频率合成的方法,使某一(或多个)基准频率,通过一定的变换和处理后,形成一系列等间隔的离散频率[1].频率合成常用的方法包括直接式频率合成技术、间接式频率合成技术(锁相频率合成技术)以及目前最为典型、应用最广泛的直接数字频率合成器(DDS :Direct Digit 2al Synt hesizer ).与传统的频率合成器相比,DDS 具有低成本、低功耗、高分辨率和转换快速等优点被广泛用于电信和电子仪器领域,是实现设备全数字化的一个关键技术.但与其它数字信号处理器件一样,DDS 也存在精度的问题,而在一些精确的数字通信过程中,特别是在雷达通信中,精度是至关重要的[2].如何提高DDS 的精度是近年来研究的热点问题.根据正弦函数的特点,对ROM 的存储单元进行合理配置,提高计算精度,并对改进效果进行了讨论.1 DDS 原理直接数字频率合成器是从相位概念出发直接合成所需波形的一项频率合成技术.一个直接频率合成器由相位累加器、加法器、波形存储ROM 、D/A 转换器和低通滤波器(L PF )构成[3].其结构图如图1所示:图1 DDS 结构图在直接数字频率合成器中,需要输入的控制参数是频率控制字和相位控制字,分别控制频率和相位.44滨州学院学报第22卷频率控制字作为累加器的输入,每经过一个时钟周期,累加器的输出就增加一个频率控制字,然后再反馈到累加器的输入端.这个累加器的输出输入到加法器,与相位控制字进行一次加法运算,也就是进行一次相移,从而完成相位控制.而相位对应ROM中的一个地址,通过这个地址可以得到当前的数字信号值.最后,信号序列经过D/A和低通滤波器就可以得到模拟信号.下面分别对数字频率合成器中两个重要的模块作一介绍.1.1 累加器累加器由一个N位加法器和一个N位寄存器构成,它在时钟的作用下进行相位累加,这也是DDS的一个基本特征———基于相位概念.累加器的输出可以直接转换为ROM的地址,通过这个地址就可以直接获得数字波形值.相位控制字决定了ROM地址的一个整体偏移,表现在波形的变化上就是一个相移;而频率控制字则是决定了在ROM中地址的增加步长,它的大小直接决定了输出波形的频率.频率控制字和输出波形频率之间的关系可以通过下面的一个线性关系表示:f0=f c×k/2N.从上式可以看出,输出频率f0与基准时钟频率f c成正比,式子中的N就是ROM地址的位数.另外,输出频率与2N是反比关系,N越大则DDS的输出频率越低.1.2 波形存储ROM上面提到ROM是输入累加器的输出数据,进行波形的相位-幅度转换.N位的寻址ROM相当于把0~2π的正弦信号离散成具有2N个样值的序列,若波形ROM有D位数据位,则个样值的幅度以D位二进制数值固化在ROM中,按照地址的不同而输出相应相位的正弦信号的幅度值.2 DDS的精度改进方案从DDS的原理可以看出,ROM地址位数N的多少决定了ROM的精度,而ROM的精度又直接决定了DDS的输出精度.可见,如果N足够大就可以得到很细的频率间隔,也将大大提高DDS的整体精度,但是,如果N太大,则需要更多的ROM存储单元,这就会导致DDS的成本增加.下面对如何利用正弦波形的特点对ROM进行优化配置在不增加成本的条件下增加DDS的精度作一分析.2.1 正弦波特点已知正弦波具有对称性,存在下面的关系sin(α+π)=-sinα,sin(π-α)=sinα.可见,在[π/2,π]、[π,3π/2]、[3π/2,2π]三个区间的波形值都可以通过[0~π/2]区间的波形值转化得到.2.2 ROM优化方案从上面对正弦波形特点的分析可以得出,只存储[0,π/2]区间内的波形就可得到完整的波形.这样,N 位的寻址ROM就不是存储的[0,2π]的2N个正弦信号离散样值序列,而是存储的[0,π/2]的2N个正弦信号离散样值序列,有效的利用了ROM存储空间,提高了存储效率,也相应的提高了DDS的输出精度.ROM优化具体算法如下:IF相位属于[0,π/2]sinα=sinα;EL SIF相位属于[π/2,π]sinα=sin(π-α);EL SIF相位属于[π,3π/2]sinα=-sin(α-π);EL SE第3期李建磊,等 直接数字频率合成器(DDS )精度提高方法研究sin (α)=-sin (2π-α);END2.3 优化算法V HDL 实现在改进后的算法中,数据的位数为8位,存放了[0,π/2]的波形数据.而要把10位地址转换为ROM 中的8位地址,可通过10位数据的高两位来控制是否对低8位地址和数据进行取反运算来实现.以下是算法的V HDL 实现代码:L IBRAR Y IEEE ;U SE IEEE.STD_LO GIC_1164.ALL ;U SE IEEE.STD_LO GIC_UNSIGN ED.ALL ;EN TIT Y xorvh ISPOR T (inA :IN STD_LO GIC ;inB :IN STD_LO GIC_V EC TOR (7DOWN TO 0);q :OU T STD_LO GIC_V EC TOR (7DOWN TO 0));END xorvh ;A RCH ITEC TU RE behave O F xorvh ISSIGNAL temp :STD_LO GIC_V EC TOR (7DOWN TO 0);B EGINIF inA =’1’T H ENtemp <=NO T inB ;END IF ;q <=temp ;END behave ;3 验证数据采用Altera 公司Flex10k10的FP GA 芯片实现DDS [4],在此芯片中内嵌ROM ,可以配置成256×8的存储单元.首先采用未改进的DDS 存储方案,把整个周期波形保存为256个值;然后,采用改进方案把1/4个周期的波形保存在256个存储单元;最后对二者进行比较.3.1 波形比较两种方案得到的波形如图2所示:图2 改进前后方案波形比较从图2可以看出,在0.19π~0.29π之间,未改进的方案用25个样点来表示,而改进方案用100个样点来表示,减少了由于数字信号良好所导致的量化误差,提高了DDS 输出波形的精度.3.2 频谱比较从图3可以看出,改进前的方案在主频率附近有较大泄漏,从而导致主频率分量的能量减少,大约为180;而改进后这一问题得到了很好的解决,几乎没有泄漏,能量集中在主频率处,约为230.54滨州学院学报第22卷4 结 论利用正弦函数的对称性,对ROM 存储单元进行优化分配,从而有效地提高了ROM存储单元的利用图3改进前后频谱比较效率.使用Flex10k10芯片实现DDS 并对输出信号的波形和频谱进行比较和分析发现,该方案可以有效的改进DDS 的精度.参 考 文 献:[1]邓勇,周铎.数字电路设计完全手册[M ].国防工业出版社,2004.[2]费元春,苏广川,米红,等.宽带雷达信号产生技术[M ].北京:国防工业出版社,2002.[3] SCHN EIER B.Applied Cryptograp hy Protocals ,algorit hms ,and source code in C [M ].2nd ed.U SA :John Wiley &Sons Inc ,1996.[4]褚振勇,翁木云.FP GA 设计及应用[M ].西安:西安电子科技大学出版社,2002.R esearch on The Method of DDS πs PrecisionL I Jian Οlei ,MA Zhen ,ZHUAN G Bo ,LV Feng Οjie(Dep artment of Com p uter S cience and Technolog y ,B i nz hou U ni versit y ,B i nz hou 256603,Chi na )Abstract :This paper has discussed t he principle of Direct Digital Frequency Synt hesizer (DDS )and researched on t he met hod of optimizing ROM by t he characteristics of sine wave.The met hod has been implemented in FP GA chip (type Flex10k10),and t he experimental result s has been compared and ana 2lyzed.K ey w ord :DDS ;precision ;FP GA(责任编辑:余艳玲)64。

毕业论文:基于DDS技术实现的频率可跳变的频率合成器设计(终稿)-精品

基于DDS技术实现的频率可跳变的频率合成器摘要:本文首先对频率合成技术现状和未来发展进行了简要说明,同时对直接数字频率合成技术理论作了比较详细的分析,另还对本设计选用的一些芯片进行了介绍。

在此基础上,采用外部输入时钟方式,由控制、电平转换、频率合成、低通滤波、放大等模块构成频率合成器。

在实现过程中,以直接数字频率合器(DDS)为核心,通过单片机对其进行初始化、工作状态设置和实时地向其输入频率控制字和频率更新信号,实现DDS输出频率的跳变,最后再通过滤波和放大,得到一个能满足一定使用要求且频率可跳变频率源。

关键词:频率合成;单片机;直接数字频率合成(DDS);低通滤波;Design of Frequency Synthesizer with Frequency-HoppingBased on DDS TechnologyAbstract: In this paper, the frequency of technical status and future development of a summary statement, the Direct Digital Synthesis techniques of a more detailed analysis, and the other is also on the choice of a number of chip design was introduced.On this basis, the use of external input clock, from control, power conversion, frequency synthesis, low-pass filtering, amplification modules constitute Synthesis. In the process of achieving, with a direct digital frequency (DDS) as the core, through its SCM initialized, the state set-up and real-time control to the input frequency and frequency of updates word signal, the output frequency of DDS Hopping, and then through the filtering and amplification, with a meet certain requirements and the use of frequency hopping frequency source.Keywords: Synthesis; SCM; Direct Digital Synthesis (DDS); low pass filter;第 1 章 绪 论1.1频率合成技术概述随着现代通信与电子系统的发展,对频率合成技术在多个性能方面提出了更高的要求,希望频率源能输出一个更为稳定且在一定频率范围内可跳变频率信号。

论文资料 直接数字频率合成(DDS)基本原理

基于FPGA的直接数字频率合成实现方案直接数字频率合成(DDS)是一种数字合成技术,它通过将数字信号转换为模拟信号来合成所需的波形。

DDS的基本原理是从相位的概念出发,通过相位累加器、波形存储器、数模转换器和低通滤波器等结构,将数字信号转换为模拟信号。

在DDS系统中,相位累加器是核心组成部分之一。

它通过将频率控制字(K)与相位增量(△<1))相加,生成一个相位序列。

该相位序列用于选择波形存储器中的幅度序列,从而生成所需的模拟信号。

波形存储器中存储了不同相位的幅度序列,通过相位累加器的输出选择所需的幅度序列。

然后,数模转换器将选定的幅度序列转换为模拟信号,最后通过低通滤波器去除高频噪声,得到纯净的模拟信号。

DDS系统的频率分辨率和频率范围取决于相位增量(A

Φ)和幅度序列的长度。

通过改变频率控制字(K),可以控制所得离散序列的频率,经保持、滤波之后可唯一地恢复出此频率的模拟信号。

基于FPGA技术实现DDS的方案是,通过VXI接口电路将生成的数据存入固定数据RAM中,然后用FPGA设计的相位累加器来计算并选择RAM中的数据存放地址,最后将数据给定的频率控制字输出,经DAC转换即实现了任意波形输出。

直接数字频率合成器(DDS)的改进设计

直接数字频率合成器(DDS)的改进设计【摘要】本文介绍了一种改进的直接数字频率合成器的设计原理,详细讨论了dds频率合成技术及系统软件、硬件的设计。

【关键词】dds;可控分频器;单片机频率源是雷达、通信、电子对抗等电子系统实现高性能指标的关键。

在现代电子学的各个领域常常需要高精度且频率可方便调节的信号源。

传统的频率合成器已不能适应技术发展的需要,直接数字式频率合成器(direct digital frequency synthesis)简称dds 或ddfs,是随之发展起来的一种新的频率合成技术,它是从相位概念出发直接合成所需波形的一种频率合成技术。

一般采用相位累加器和幅码编址器对存储器进行寻址,过于复杂并且电路调试有一定难度,滤波器精确度要求很高,频率很高时波形不光滑且容易失真。

本文针对这一不足进行了改进。

一、改进的直接数字频率合成器设计框图该系统全面采用数字电路方案,因而工作稳定可靠,利用单片机控制管理,使频率预置和占空比调整等操作可用键盘输入,十分方便,数字频率合成技术使输出频率准确度和稳定度得到提高,频率分辨率为1hz。

二、系统的总体设计思路该系统分为单片机处理与控制部分两大部分,单片机采用89c51,通过一块接口芯片8255与键盘和显示器连在一起,因显示的位数只四位,故采用数码管动态显示,软件译码,采用2*8的键盘进行预置数输入,控制,键盘上共有0—9个数字键、6个功能键;利用单片机的输出来控制可控分频器,然后通过计数器对可控分频器的输出脉冲进行计数,把8位计数器的输出作为一个地址码,将这个地址码作为存储器的读写地址,从存储器中取出预先存放的各种量化数据,经dac0832进行d/a转换,最后通过滤波器输出一个频率受键盘控制的正弦波。

经过对dds的改进后,该系统能产生1hz —9999hz的频率,频率可由键盘进行预制,并且输出频率可通过显示器进行数码显示。

1、单片机控制部分的设计:1)显示器部分的设计显示器采用数码管进行显示,数码管成本低、性能稳定。

直接数字频率合成器DDS的设计

直接数字频率合成器DDS 的设计DDS 的基本原理DDS 技术是一种把一系列数字量形式的信号通过DAC 转换成模拟量形式的信号的合成技术,它是将输出波形的一个完整的周期、幅度值都顺序地存放在波形存储器中,通过控制相位增量产生频率、相位可控制的波形。

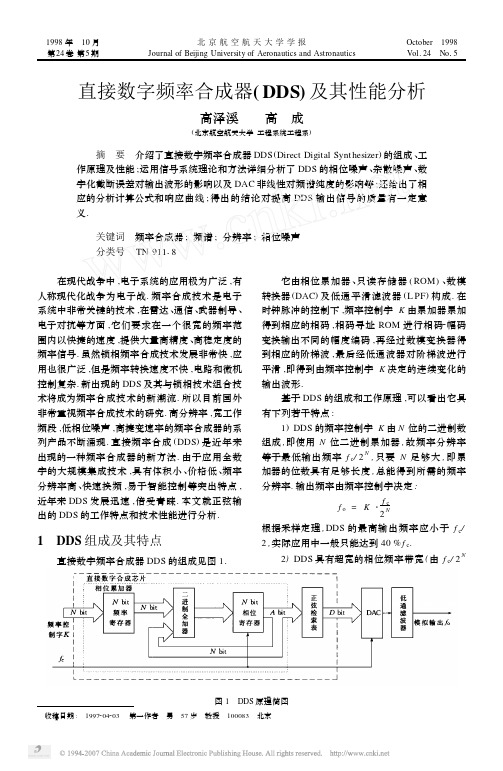

DDS 电路一般包括基准时钟、相位增量寄存器、相位累加器、波形存储器、D/A 转换器和低通滤波器(LPF )等模块,如图1所示。

相位增量寄存器寄存频率控制数据,相位累加器完成相位累加的功能,波形存储器存储波形数据的单周期幅值数据,D/A 转换器将数字量形式的波形幅值数据转化为所要求合成频率的模拟量形式信号,低通滤波器滤除谐波分量。

整个系统在统一的时钟下工作,从而保证所合成信号的精确。

每来一个时钟脉冲,相位增量寄存器频率控制数据与累加寄存器的累加相位数据相加,把相加后的结果送至累加寄存器的数据输出端。

这样,相位累加器在参考时钟的作用下,进行线性相位累加,当相位累加器累加满量时就会产生一次溢出,完成一个周期性的动作,这个周期就是DDS 合成信号的一个频率周期,累加器的溢出频率就是DDS 输出的信号频率。

相位累加器输出的数据的高位地址作为波形存储器的地址,从而进行相位到幅值的转换,即可在给定的时间上确定输出的波形幅值。

图1 DDS 原理图波形存储器产生的所需波形的幅值的数字数据通过D/A 转换器转换成模拟信号,经过低通滤波器滤除不需要的分量以便输出频谱纯净的所需信号。

信号发生器的输出频率fo 可表示为:Ns f M f M f 2..0=∆= ( 1)式中s f 为系统时钟,f ∆为系统分辨率,N 为相位累加器位数,M 为相位累加器的增量。

参数确定及误差分析首先确定系统的分辨率f ∆,最高频率max f ,及最高频率max f 下的最少采样点数min N 根据需要产生的最高频率max f 以及该频率下的最少采样点数min N ,由公式m i n m a x.N f f s ≥ (2)确定系统时钟s f 的下限值。

毕业设计(论文)-直接数字频率合成器设计[管理资料]

![毕业设计(论文)-直接数字频率合成器设计[管理资料]](https://img.taocdn.com/s3/m/fe683c28ce2f0066f433225f.png)

直接数字频率合成器设计The Design of Direct Digital Frequency Synthesizer摘要利用可编程逻辑阵列FPGA(Field Programmable Gate Array)实现DDS专用电路芯片,主要特点是能满足用户对特殊功能的要求,而且在使用过程中也灵活地改变系统结构。

,并不能满足所有的要求。

本文在对现有DDS技术的大量文献调研的基础上,提出了符合FPGA结构的DDS设计。

方案利用QuartusⅡ开发工具在ALTERA FLEX10K系列器件上进行了实现。

关键词直接数字频率合成器单片机数模转换温度漂移补偿AbstractThe main features of realization of dedicated direct digital frequency synthesizer circuit chips using FPGA are the ability to meet user requirements for special functions, but also flexibility change structural of the system in the use of the process. Although commercial DDS dedicated chip circuit provide a lot of opportunities for the designers and meet the needs of many occasions, there are its limitations and cannot meet all the requirements. On a large number of investigation of existing research literature,the papers involves the proposed structure of the direct digital frequency synthesizer FPGA design. The Programmer uses the Quartus II development tool for designing the Altera FLEX10K series devices.Keywords DDS MCU DAC Temperature drift compensation目录前言 (1)第1章设计思路及原理 (2)研究意义 (2)总体设计任务 (2)设计思路及原理 (3)DDS工作原理框图 (3)具体工作过程 (3)第2章系统电路的设计及原理 (5)系统框图 (5)各模块具体实现原理分析和说明 (5)相位累加器模块 (5)ROM查找表模块 (10)单片机输入输出控制模块 (12)温漂误差补偿 (13)D/A转换模块 (18)滤波输出电路模块 (19)软件仿真结果 (19)第3章硬件电路的构建 (21)FPGA芯片的选择与使用 (21)硬件连接电路图 (23)第4章实验开发系统系统 (25)实验开发系统的选择与使用 (25)实验过程与结果分析 (27)总结....................................................................................... 错误!未定义书签。

直接数字频率合成器DDS及其性能分析

电子器件工作速度的提高 ,DDS 的输出频率上限 行傅氏变换 ,得到理想 DDS 输出的频谱表达式 :

∞

也s将e 可以提高. 其二 ,DDS 输出的模拟信号中杂

∑ S (ωn) = π S a

·

散寄生分量大 ,其中输出高频尤甚 ,它无法达到

l=- ∞

PLL 频率合成的频谱纯度. 其三 ,DDS 的n功A耗与

其一 ,根据取样定理 ,输出信号基波的最高频率将

低于参考时钟的一半 ,故若要提高输出频率将受

n = 1 ,2 , …

(1)

到器件 (如 DAC、ROM) 的速度限制. 目前输出频 S ( n) 通过 DAC 和低通滤波器 , 得到 DDS 的输出

率达到 450 M Hz 的 DDS 系统已研制成功. 随着 S ( t) ,显然 S ( t) 是连续时间的周期信号. 对它进

第 5 期 高泽溪等 :直接数字频率合成器 (DDS) 及其性能分析

617

mod 运算定义为

0 ≤ t ≤μTc

(9)

pmod q = p - int ( p/ q) q

通过 S′( t) 的傅氏变换 , 可以得到 S′(ω) 的表达

其中 int (·) 代表取整运算.

式 (略) ,对表达式分析说明 ,波形误差信号包含的

摘 要 介绍了直接数字频率合成器 DDS(Direct Digital Synt hesizer) 的组成 、工 作原理及性能 ;运用信号系统理论和方法详细分析了 DDS 的相位噪声 、杂散噪声 、数 字化截断误差对输出波形的影响以及 DAC 非线性对频谱纯度的影响等 ;还给出了相 应的分析计算公式和响应曲线 ;得出的结论对提高 DDS 输出信号的质量有一定意 义.

一种基于DDS的直接式频率合成器设计与实现

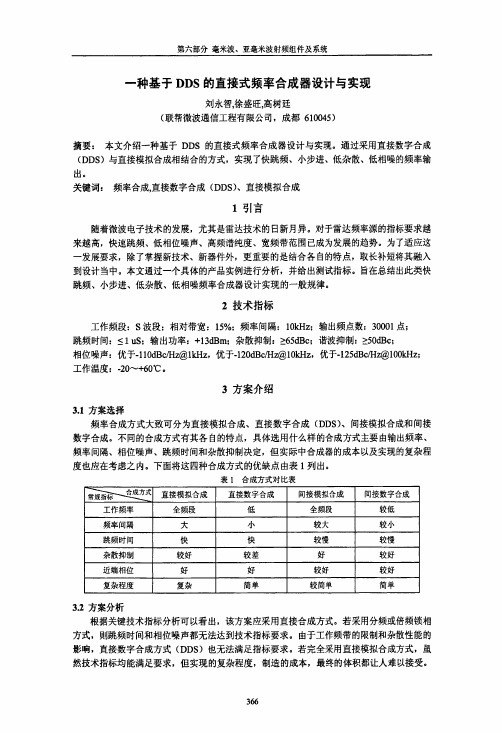

4实验结果及分析

通过以上的分析,设计出具体的电路。利用相位噪声测试仪可测出该频率合成器的输 出相位噪声,图2给出S波段相噪测试曲线。

H孙搬№i铀10.00d吖R西嘞冉抽IB洳

’’_‘~r

一一L

锄.∞.6e.O畦il№}2l土9'll

≈jh啪^h

k}醢

潞∥

7l程 璐裂罟嬲簇勰; 一

耩 :嚣i

一i,,

1引言

随着微波电子技术的发展,尤其是雷达技术的日新月异。对于雷达频率源的指标要求越 来越高,快速跳频、低相位噪声、高频谱纯度、宽频带范围已成为发展的趋势。为了适应这 一发展要求,除了掌握新技术、新器件外,更重要的是结合各自的特点,取长补短将其融入 到设计当中。本文通过一个具体的产品实例进行分析,并给出测试指标。旨在总结出此类快 跳频、小步进、低杂散、低相噪频率合成器设计实现的一般规律。

2技术指标

工作频段:S波段;相对带宽:15%:频率间隔:10kHz;输出频点数:30001点; 跳频时间:5

l

uS;输出功率:+13dBm;杂散抑制:>65dBc;谐波抑制:>50dBc;

相位噪声:优于一1 10dBc/Hz@IkHz,优于-120dBc/Hz@10kHz,优于一125dBc/Hz@100kHz; 工作温度:.20~+60℃。

^屑依

由图1方案可知最终输出频率:Tout=厶慨+等},其中M为谐波发生器的倍频次数。

Z

为了得到密集频率覆盖,要求DDS输出带宽必须大于等于晶振信号频率的一半,即 BWDDS>__fi'/2。其工作过程如下,当频率合成器在同一BWDDS内进行频率转换时,通过控制

367

第六部分毫米波、亚毫米波射频组件及系统

然技术指标均能满足要求,但实现的复杂程度,制造的成本,最终的体积都让人难以接受。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

直接数字频率合成器DDS研究设计毕业论文目录1. 引言 (1)1.1 频率合成器的研究背景 (1)1.2频率合成器的研究现状 (1)2. 频率合成技术 (3)2.1频率合成技术概述 (3)2.2频率合成器的主要指标 (3)2.3频率合成的基本方法 (5)2.4 频率合成器的长期频率稳定度和相位噪声 (5)2.4.1长期频率稳定度 (5)2.4.2 相位噪声 (6)2.4.3噪声来源 (7)3. 直接频率合成(DS)技术 (8)3.1 直接频率合成器的基本原理和组成 (8)3.2直接频率合成器的几个主要组成电路 (9)3.2.1混频器 (9)3.2.2倍频器 (11)3.2.3分频器 (12)3.2.5石英晶体振荡器 (14)4. 直接数字频率合成(DDS)技术 (17)4.1 直接数字频率合成的组成及其特点 (17)4.2 直接数字频率合成的基本原理 (19)4.3 直接数字频率合成的相位噪声和杂散 (20)4.3.1 直接数字频率合成的相位噪声 (20)4.3.2 直接数字频率合成的杂散分析 (21)4.3.3 降低杂散电平的方法 (21)4.4 集成直接数字频率合成器的芯片介绍 (23)5. 直接数字频率合成器的设计 (26)5.1 DDS芯片在跳频系统中应用的总体框图 (26)5.2 控制模块 (26)5.2.1 AT89C51引脚说明 (26)5.2.2 单片机外围电路设计 (28)5.3 频率合成模块 (29)5.3.1 AD9852的引脚说明 (29)5.4电平转换模块 (32)5.5低通滤波模块 (33)5.6 放大电路 (35)结束语 (36)致谢 (37)参考文献 (38)1. 引言1.1 频率合成器的研究背景频率合成(频率综合)是指由一个或多个频率稳定度和精确度很高的参考信号源通过频率域的线性运算,产生具有同样稳定度和精确度的大量离散频率的过程。

实现频率合成的电路叫频率合成器,频率合成器是现代电子系统的重要组成部分。

在通信、雷达和导航等设备中,频率合成器既是发射机的激励信号源,又是接收机的本地振荡器;在电子对抗设备中,它可以作为干扰信号发生器;在测试设备中,可作为标准信号源,因此频率合成器被人们称为许多电子系统的“心脏”。

频率源是雷达、通信、电子系统实现高性能技术指标的关键部分,许多现代电子设备和系统的功能的实现,都直接依赖于所用的频率源的性能,而当今高性能的频率源都是通过频率合成技术来实现的。

频率合成技术大约出现于20世纪30年代,最初产生并进入实现应用的是直接频率合成技术,它具有频率转换时间短、近载频相位噪声性能好等优点,但是,由于采用大量的倍频、分频、混频和滤波环节,直接式频率合成器的结构复杂、体积大、成本高,而且容易产生过多的杂散分量,难以达到较高的频谱纯度。

到60年代末70年代初,相位反馈理论和模拟锁相技术在频率合成领域里的应用,引发了频率合成技术发展史上的一次革命,相参锁相式合成技术就是这场革命的直接产物。

随后数字化的锁相环路器件,如数字鉴相器、数字可编程分频器等器件的出现,以及其在锁相频率合成技术中的应用,标志着数字锁相频率合成技术得以实现。

由于不断吸收和利用脉冲计数器、小数分频器、多模分频器等数字技术发展的新成果,数字锁相频率合成技术日益成熟,锁相式频率合成器具有良好的窄带跟踪特性,可以很好的选择所需频率的信号,抑制杂散分量,并且可避免使用大量滤波器,十分有利于集成化和小型化。

此外,还具有良好的长期频率稳定度和短期频率稳定度。

但是,由于锁相环本身是一个惰性环节,使得频率锁定时间较长,故锁相式频率合成器的频率捷变时间较长。

目前,锁相环频率合成器在各电子领域中获得较为广泛的应用。

1.2频率合成器的研究现状频率合成技术是现代雷达,通信等电子系统实现高性能指标的关键技术之一.传统的频率合成技术包括模拟直接式频率合成和间接式频率合成。

近几年来随着大规模集成电路和高速数字电路技术的日益成熟,以全数字结构为特征的直接数字频率合成技术得到了迅速发展,从而引发了频率合成领域的一次革命。

它突破了传统频率合成器的诸多局限,具有相对带宽很宽,频率分辨率很高,频率捷变速度快,频率变换时输出信号相位保持连续和全球集成化等优点,这些优点是由于DDS的全数字结构所赋予的,但也正是这种全数字结构造成了DDS的主要缺陷,即输出相位噪声和杂散电平高。

2. 频率合成技术2.1频率合成技术概述频率合成器是利用一个或多个标准信号,通过各种技术途径产生大量离散频率信号的设备。

直接数字式频率合成(DDS)技术的出现,导致了频率合成领域的第二次革命。

1971年J.Tierney、C.M.Rader和B.Goid在A Digital Frequency Synthesizer 一文中发表了关于新型数字频率合成的研究成果,第一次提出了具有工程实现可能和实际应用价值的直接数字频率合成的概念。

尽管当时该项技术未能立即得以普遍的重视,但是随着数字集成电路和微电子技术的发展,DDS逐渐充分体现出其具有相对带宽很宽、频率转换时间极短、频率分辨力很高、输出相位连续、可以输出宽带正交信号、任意波形输出能力、数字调制功能、可编程,以及全数字化结构便与集成等优越性能。

DDS的缺点是工作频带的限制和杂散抑制差。

近年来,随着单片锁相式频率合成器等芯片的发展,锁相式、直接数字式,以及直接数字频率合成器(DDS)和锁相环(PLL)相结合所构成的频率合成器,以其容易实现系列化、小型化、模块化、工程化和其优越的性能已逐步成为三中最为典型、用处最为广泛的频率合成器。

更宽的工作频带、更精确的频率分辨力、更低的相位噪声和寄生特性、更宽的频率转换时间,以及减小体积、降低功耗是对现代频率合成器提出的越来越严重的要求。

DDS+PLL混合式频率合成技术将DDS的高频率分辨力和快速转换时间特性与锁相环路的输出频率高、寄生噪声和杂波低的特点有机结合,以尽可能全面的满足各种系统对频率源苛刻的要求。

目前,开发应用最为广泛的一种方法,是采用DDS技术、变频技术和锁相环技术来实现高性能的频率合成器。

当今世界,由于通信、雷达技术的飞速发展,对系统相位噪声的要求越来越高。

DDS 与PLL相结合所构成的频率合成器,以其优越的相位稳定性和极低的颤噪效应,成为比较理想的频率源。

2.2频率合成器的主要指标为了正确理解、使用与设计频率合成器,首先应对它的质量指标进行了解。

频率合成器的使用场所不同,对它的要求也不全相同。

大体说来,有如下几项主要技术指标:频率围、频率间隔、频率稳定度和准确度、频率纯度(杂散输出和相位噪声)、频率转换时间等等。

合成器的体积、重量、功耗与成本等,就是由这些指标决定的。

(1)频率围这是指频率合成器的工作频率围,视用途而定,有短波、超短波微波等频段。

一般包括合成器输出信号的中心频率f o及带宽B。

(2)频率间隔频率合成器的输出频谱是不连续的。

两个相邻频率之间的最小间隔,就是频率间隔。

频率间隔又称为分辨力。

不同用途的频率合成器对频率分辨力有不同的要求。

有的可以达到 MHz 的分辨力,有的可达到kHz 级的分辨力,有的则需要达到Hz 甚至是 MHz 级的分辨力。

(3)频率稳定度和准确度频率稳定度是指在一定的时间间隔,合成器输出频率变化的大小。

频率准确度是指频率合成器的实际输出频率偏离标称工作频率的程度。

频率准确度与稳定度之间有区别又有联系,只有稳定才能保证准确。

因此,常将工作频率相对于标称值的偏差也计入在不稳定偏差之,因此,只需考虑频率稳定度即可。

频率稳定度从时域角度分为长期稳定度、短期稳定度和瞬时稳定度。

其中,长期稳定度是指在年、月等长期时间频率的变化,频率的漂移主要是有石英晶体振荡器老化引起的,属于确定性的变化。

短期稳定性是指日、小时的频率变化,这种频率的变化实际上是晶振老化漂移和频率的随机起伏引起的。

瞬时稳定度是秒,甚至是毫秒时间频率的漂移,这个漂移是随机的,主要由噪声和干扰引起的。

(4)频率转换时间频率合成器从一个频率转换到另一个频率,并且达到稳定所需要的时间称之为频率转换时间。

在雷达、通信以及电子对抗等许多领域,对频率合成器的频率转换时间往往提出了严格甚至苛刻的要求,频率转换时间有时要达到us数量级。

频谱纯度是指合成器信号源输出频谱偏离纯正弦波谱的量度。

影响信号源频谱纯度的因素较多,主要包括:①相位噪声②AM噪声③非谐波相关杂散边带(杂散)④谐波相关带⑤有源器件产生的闪烁噪声⑥分频器的噪声⑦倍频器的噪声上述影响频谱纯度的因素中,起主要作用的是相位噪声和杂散,因此,在讨论频率稳定度和频谱纯度时主要考虑这两个指标。

(5)系列化、标准化和模块化的可实现性。

任何单只频率合成器不可能包含所有频段,因此有系列化要求。

另外,在实现不同频率合成器时,还要考虑所有模块的通用性(在转换频段工作时,需要换模块的品种越少越好)和互换性。

(6)成本、体积及质量。

2.3频率合成的基本方法频率合成法基本上可分为直接合成法和间接合成法。

而在具体实现中又可划分为三种,即通常所说的直接模拟频率合法、间接锁相式合成法、直接数字频率合成法。

对于这三种方法的比较如下。

(1)直接模拟频率合成技术:直接模拟合成利用倍频(乘)、分频(除)、混频(加减)和滤波技术,所需的频率是从一个或多个高稳定度和精确度的参考频率源产生。

它的优点是频率转换时间短,载频相位好等。

缺点是该方法采用了大量的分频、混频、倍频和滤波等模拟元件导致了硬件电路体积大、功耗大且容易产生过多的杂散分量,元件差难以抑制的非线性影响,所以合成的正弦波的幅度、相位等参数难以控制。

(2)间接锁相式(PLL)频率合成技术:该技术能够很好选择频率、抑制杂散分量,而且频率的稳定性很好。

但是,由于锁相环有惰性,该技术中频率转换时间和频率分辨率难找到平衡点,因而该技术一般用于步进较大的频率合成中。

(3)直接数字频率合成法:即DDS技术,该技术采用数字化技术,引入“相位”的概念,是通过控制相位的变化速度来直接产生各种频率的信号。

DDS具有可编程、相位可控、频率转换快、分辨率高、频谱纯度高、频率输出围宽、生成的正弦/余弦信号正交特性好等优良性能,所以在现代频率合成领域中地位日益重要。

而且DDS是全数字化结构,易于集成、功耗低、体积小、重量轻、易于程序控制、灵便实用,性价比很高,故应用广泛。

2.4 频率合成器的长期频率稳定度和相位噪声2.4.1长期频率稳定度频率稳定度发信机的每个波道都有一个标称的射频中心工作频率,用f0表示。

工作频率的稳定度取决于发信本振源的频率稳定度。

设实际工作频率与标称工作频率的最大偏差值为Δf,则频率稳定度的定义为频率稳定度式中为K为频率稳定度。

K=△f/f0公式 (2-1) 一般频率稳定度可以取1×10-5~2×10-5左右。