基于FPGA的数字钟设计

基于FPGA的数字时钟课程设计

西安郵電學院基于FPGA的数字时钟成员:技术规范一、功能定义1、分频:在电子钟的设计中,涉及到的频率有三个:(1):1Hz的秒计时频率,用来进行秒计时;(2):4Hz的按键防抖频率;(3):1000Hz的循环扫描频率;因此在分频模块应实现将芯片中的高频率时钟分频得到上面的三个所需频2、控制:进行正常计时,时间调整,时间复位模式的选择:(1)时间初始复位;(2)选择秒时间调整的模式;(3)选择分时间调整的模式;3、计时:进行调整时间,正常计时;(1)正常计时;(2)调整秒计时;(3)调整分计时;4、选择输出:进行时间高低位的变换及循环扫描输出:(1)进行时间高低位的变换;设计思路:一、总体设计思路图:二、功能引脚定义1、总体引脚(1)K[1]:输入,控制是否进入调整模式,调时模式或调分模式。

(2)K[2]:输入,根据K1的选择进行加1调时。

(3)CLK:输入,1赫兹,控制秒钟的频率。

(4)CLK1K:输入,1K赫兹,控制时间的连续扫描输出。

(5)[7:0]LED:输出,七段显示译码管的输入。

(6)[5:0]SEG:输出,控制六个数码管的是否接通。

(7) SC:输入,时间复位。

2、(1)控制模块:输出控制信号和时分秒计时。

控制信号控制时分秒是否正常计时。

K[1]:输入,控制是否进入调整模式,调时模式或调分模式。

K[2]:输入,根据K1的选择进行加1调时。

SC:输入,时间复位。

[5:0]SEC:复位秒计时。

[5:0]MIN:复位、调时分计时。

[5:0]HOUR:复位、调时时计时。

KEN:控制是否进行正常及时、进入调时复位状态。

(2)计时模块秒计时:输出正常的秒计时或复位计时。

分计时:输出正常的分计时或复位计时或调时计时。

时计时:输出正常的时计时或复位计时或调时计时。

(3)时间扫描模块:利用高频率的时钟不断地循环扫描是分秒计时,以便循环译码;输出控制信号,控制数码管是否有效;此模块同时进行时间的高地位的计算与输出。

基于fpga的数字钟电路设计

基于fpga的数字钟电路设计

随着电子技术和航空电子技术的发展,高精度的电子时钟发挥着越来越重要的作用。

面对众多的时间选择方式,FPGA技术为企业提供了新的解决方案。

本文旨在设计一种基于FPGA技术的数字时钟电路,以满足工业系统时间测量和管理的需求。

数字时钟电路的设计主要分为三个方面:晶振、时钟频率调整以及I/O管脚分配。

首先,选用封装形式为HC49-S的晶振器,其主要特征包括频率精度低至±50ppm、温度范围

宽至−10℃至+70℃、工作温度可升至105℃以及动态特性良好等。

其次,进行时钟频率

调节用FPGA。

FPGA的时钟频率调节模块采用MMC和VCO技术实现时钟频率抢断,可对晶

振的稳定频率进行调节,从而获得高精度的时钟信号。

最后,通过FPGA的I/O管脚分配

完成时钟信号输出,从而将数字信号变换为时间信号,实现时间数据的采集和处理。

基于FPGA技术的数字时钟电路可以有效地满足工业系统实时时间测量和管理的需求,实现工业系统时间计量技术的发展。

该电路具有稳定高效、体积小、功耗低以及现场可实

现调整参数等优缺点,在工业领域具有很高的应用前景。

基于FPGA的数字钟设计

基于FPGA的数字钟设计摘要:现实生活中经常会出现需要用时间测定参数数值的情况,服务日常生活和生产。

基于FPGA设计数字电路产品已经成为当前的重要设计方法。

本文设计选用了Quartus软件环境,运用描述逻辑Verilog HDL,由上至下的模式,基于FPGA完成了数字时钟的设计方案。

本次设计成果采用按键对闹钟的起止点进行控制,能够显示时,分,秒等并且能够实现整点报时。

其中的FPGA技术就是本次试验的亮点之一,其设计易于学习,各个模块分工清晰,在模拟软件上很容易运行,还能够适配于许多种环境,因此总体的系统性能指标还是相当有保证的。

关键词:数字钟;FPGA;Verilog HDL;Quartus1.1 课题研究背景在现代社会,数据集成电路已广泛运用于日常日常生活的各行各业。

数据集成电路也在不停拆换。

从起初的整流管、电子管、大中小型集成电路发展趋势为具备特大型集成电路和独特作用的各类专用型集成电路。

可是,因为微电子技术科技进步的迅猛发展,集成电路设计方案和生产制造工作中再也不会由半导体生产商独立担负。

系统软件室内设计师更喜欢立即设计方案专用型集成电路(ASIC)处理芯片,并马上资金投入具体运用,因而发生了当场可编程逻辑机器设备(FPLD),在其中应用最普遍的是当场可编门阵列(FPGA)。

数字钟是一种选用数字电路设计技术性完成时、分、秒计时的装置,在完成数据与此同时表明时、分、秒的准确时间和精确校正时,体积小、重量轻、抗干扰能力强、对自然环境需要高、高精密、易于开发设计等与在办公系统系统软件等众多行业运用非常普遍的传统式表壳式机械手表对比,数字表更精确、形象化,因为沒有机械设备装置,使用期限长。

1.2 国内外研究现状近些年来已经有许多技术人员针对电子器件以及时钟等技术进行了研究,但真正意义上的数字钟表起源于50年代或60年代。

伴随着在我国数字钟表电源电路销售市场的迅速发展趋势,尤其是十二五阶段经济发展方法这一领土主权主旋律早已明确,与之有关的关键生产制造技术运用和产品研发将变成领域公司关心的焦点。

基于FPGA的数字电子钟的设计与实现

基于FPGA的数字电⼦钟的设计与实现背景:本实验所有结果基于Quartus II 13.1 (64-bit)实现,实验过程采⽤⾃下⽽上⽬录⼀、基本功能设计与思路基本功能:能实现秒、分钟、⼩时的计数,计数结果清晰稳定的显⽰在 6 位数码管上。

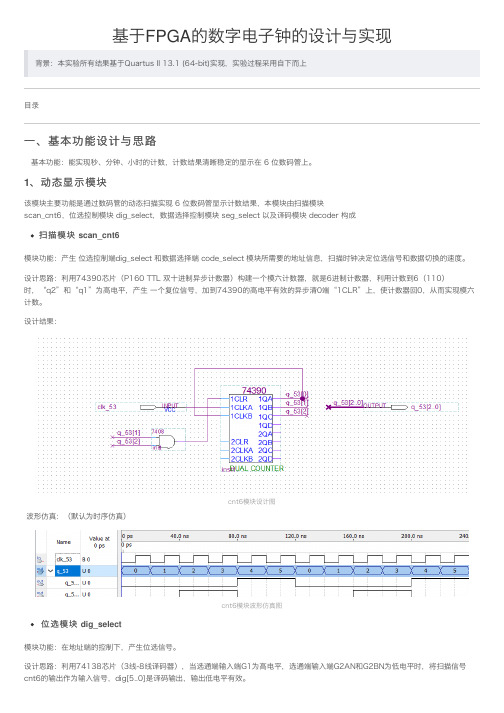

1、动态显⽰模块该模块主要功能是通过数码管的动态扫描实现 6 位数码管显⽰计数结果,本模块由扫描模块scan_cnt6,位选控制模块 dig_select,数据选择控制模块 seg_select 以及译码模块 decoder 构成扫描模块 scan_cnt6模块功能:产⽣ 位选控制端dig_select 和数据选择端 code_select 模块所需要的地址信息,扫描时钟决定位选信号和数据切换的速度。

设计思路:利⽤74390芯⽚(P160 TTL 双⼗进制异步计数器)构建⼀个模六计数器,就是6进制计数器,利⽤计数到6(110)时,“q2”和“q1”为⾼电平,产⽣ ⼀个复位信号,加到74390的⾼电平有效的异步清0端“1CLR”上,使计数器回0,从⽽实现模六计数。

设计结果:cnt6模块设计图波形仿真:(默认为时序仿真)cnt6模块波形仿真图位选模块 dig_select模块功能:在地址端的控制下,产⽣位选信号。

设计思路:利⽤74138芯⽚(3线-8线译码器),当选通端输⼊端G1为⾼电平,选通端输⼊端G2AN和G2BN为低电平时,将扫描信号cnt6的输出作为输⼊信号,dig[5..0]是译码输出,输出低电平有效。

设计结果:dig_select模块设计图波形仿真:dig_select模块波形仿真图数据选择模块 seg_select模块功能:输⼊ 6 组数据,每组数据 4bit,本模块完成在地址端的控制下从6 组数据当中选择 1 组输出。

设计思路:利⽤74151芯⽚(P91 8选1数据选择器),在控制输⼊端GN为低电平时,将扫描信号的选择下,分别选中D[5..0]对应的输⼊信号输出为Y。

基于FPGA数字时钟

基于FPGA的数字时钟设计一、课程设计目的1、进一步熟悉QuartusⅡ的软件使用方法;2、熟悉可编程逻辑器件的开发流程及硬件测试方法;3、熟悉基于FPGA的综合数字系统设计方法;二、设计任务设计一台可以显示时、分、秒的数字钟。

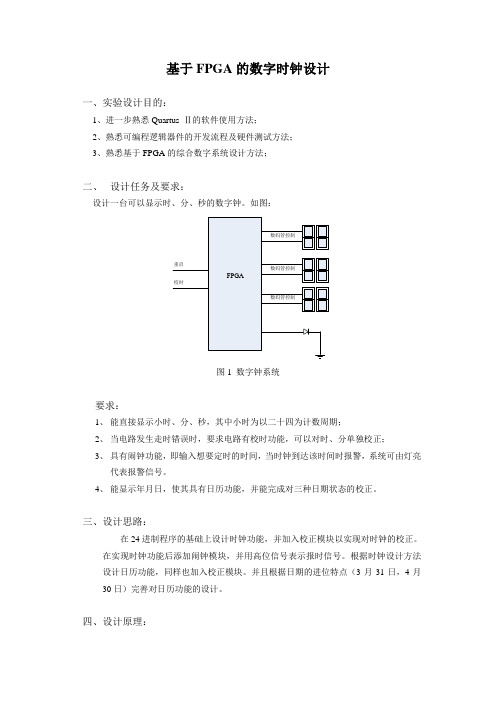

如图1所示为基于FPGA的数字钟设计的系统框图。

图1 数字钟系统三、设计要求1、能直接显示小时、分、秒,其中小时为以二十四为计数周期;2、能够显示日期(即年、月、日),且要求在显示时钟的数码管上显示日期,即时钟数码管与日期数码管复用;3、年、月、日要严格按照实际日期,例如1月31天,4月30天,2月闰年29天等;4、当数字钟发生走时错误时,要求电路有校时功能,可以对时、分单独校正,且校正时间时系统时钟不工作;5、当日期发生错误时,要求有校正日期功能,可以对年、月、日单独校正,且矫正日期时时钟系统仍然工作;6、具有闹钟功能,即输入想要定时的时间,当时钟到达该时间时报警,系统可由灯亮代表报警信号。

四、设计内容1、时间计数模块本次是将秒分时各个模块分开进行设计,用秒的进位作为分模块的脉冲,用分的进位作为是模块的脉冲。

秒进位的仿真波形程序:秒的程序module miao(clk,gdata,ddata,en,cl,clr);input clk;input en;input clr;output [3:0] ddata;output [3:0] gdata;output cl;reg [7:0] q;reg cl;assign ddata=q%10;assign gdata=q/10;always @(negedge clk or posedge clr)beginif(clr==1)q=0;elsebeginif(en==1)beginif(q<59)beginq=q+1;cl=0;endelsebeginq=0;cl=1;endendendendendmodule分模块和时模块的程序一秒程序类似,只是进位计数不一样。

基于FPGA的数字钟设计

摘要伴随着集成电路技术的发展, 电子设计自动化(EDA)技术逐渐成为数字电路设计的重要手段。

基于FPGA的EDA技术的发展和应用领域的扩大与深入,使得EDA技术在电子信息,通信,自动控制,计算机等领域的重要性日益突出。

本设计给出了一种基于FPGA的多功能数字钟方法,采用EDA作为开发工具,VHDL语言和图形输入为硬件描述语言,QuartusII作为运行程序的平台,编写的程序经过调试运行,波形仿真验证,下载到EDA实验箱的FPGA芯片,实现了设计目标。

系统主芯片采用CycloneII系列EP2C35F672C8。

采用自顶向下的设计思想,将系统分为五个模块:分频模块、计时模块、报时模块、显示模块、顶层模块。

用VHDL语言实现各个功能模块, 图形输入法生成顶层模块. 最后用Q uartusII软件进行功能仿真,验证数字钟设计的正确性。

测试结果表明本设计实现了一个多功能的数字钟功能,具有时、分、秒计时显示功能,以24小时循环计时;具有校正小时和分钟的功能;以及清零,整点报时功能。

关键词:EDA技术;FPGA;数字钟;VHDL语言;自顶向下AbstractAccompanied by the developmentof integrated circuit tec hnology, electronic designautomation (EDA) technology is becoming an important meansof digitalcircuitdesign. FPGA EDA technology development and expansion ofapplic ationfields and in-depth,the importance of EDA technologyin the fieldofelectronic information,communication, automatic control, computer, etc.havebecome increasingl yprominent.This design gives aFPGA-basedmultifunctional digi talclock using EDA as a development tool,VHDLlanguage andgraphicalinput hardwaredescriptionlanguage, the QuartusIIasaplatform for runningthe program, written procedures debugging andrunning, thewaveform simulation do wnloaded tothe FPGA chip to achievethe design goals.Themainsystemchip CycloneIIseries EP2C35F672C8. Ado pted a topdwn designideas,thesystem is divided into five modules: frequencymodule,timing module, timermodule, di splay module,the top-levelmodule. WithVHDL various fun ctionalmodules,graphical input method to generate the top-levelmodule. LastQuartusII undersimulation, tover ify the correctness ofthedigitalclockdesign.Thetest results show that thedesign of amultifunctional digitalclock,with seconds time display, 24-hour cyclet iming; has a school,cleared, and the whole pointtimekeeping functions.Key words: EDA technology; FPGA; VHDL language; top-down;di gital clock目录1 绪论............................................................................................. 错误!未定义书签。

基于XilinxFPGA的数字钟设计

基于FPGA的多功能数字钟一、设计题目基于Xilinx FPGA的多功能数字钟设计二、设计目的1.掌握可编程逻辑器件的应用开发技术——设计输入、编译、仿真和器件编程;2.熟悉一种EDA软件使用;3.掌握Verilog设计方法;4.掌握分模块分层次的设计方法;5.用Verilog完成一个多功能数字钟设计;6.学会FPGA的仿真。

三、设计内容设计实验项目九多功能电子钟✧功能要求:利用实验板设计实现一个能显示时分秒的多功能电子钟,具体要求为:基本功能:1)准确计时,以数字形式显示时、分、秒,可通过按键选择指示当前显示时间范围模式;2)计时时间范围 00:00:00-23:59:593)可实现校正时间功能;4)可通过实现时钟复位功能:00:00:00扩展功能:1)定时报:时间自定(不要求改变),闹1分钟(1kHz)---利用实验板LED或外接电路实现。

2)仿广播电台正点报时:XX:59:[51,53,55,57(500Hz);59(1kHz)] ---利用实验板LED或外接电路实现。

3)报整点时数:XX:00:[00.5-XX.5](1kHz),自动、手动---利用实验板LED或外接电路实现。

4)手动输入校时;5)手动输入定时闹钟;6)万年历;7)其他扩展功能;✧设计步骤与要求:1)计算并说明采用Basys2实验板时钟50MHz实现系统功能的基本原理。

2)在Xilinx ISE13.1 软件中,利用层次化方法,设计实现模一百计数及显示的电路系统,设计模块间的连接调用关系,编写并输入所设计的源程序文件。

3)对源程序进行编译及仿真分析(注意合理设置,以便能够在验证逻辑的基础上尽快得出仿真结果)。

4)输入管脚约束文件,对设计项目进行编译与逻辑综合,生成下载所需.bit类型文件。

5)在Basys2实验板上下载所生成的.bit文件,观察验证所设计的电路功能。

四、总体设计思路主体分为分频模块,正常时间模块(包含两个模60计数器和一个模24计数器子模块),闹钟模块(分为一个模60计数器模块,一个模24计数器模块,四个比较器模块),电台报时模块,数码管显示模块(分为模式选择模块,片选信号及扫描程序模块,和译码模块)。

基于FPGA的数字时钟设计

基于FPGA的数字时钟设计一、实验设计目的:1、进一步熟悉QuartusⅡ的软件使用方法;2、熟悉可编程逻辑器件的开发流程及硬件测试方法;3、熟悉基于FPGA的综合数字系统设计方法;二、设计任务及要求:设计一台可以显示时、分、秒的数字钟。

如图:图1 数字钟系统要求:1、能直接显示小时、分、秒,其中小时为以二十四为计数周期;2、当电路发生走时错误时,要求电路有校时功能,可以对时、分单独校正;3、具有闹钟功能,即输入想要定时的时间,当时钟到达该时间时报警,系统可由灯亮代表报警信号。

4、能显示年月日,使其具有日历功能,并能完成对三种日期状态的校正。

三、设计思路:在24进制程序的基础上设计时钟功能,并加入校正模块以实现对时钟的校正。

在实现时钟功能后添加闹钟模块,并用高位信号表示报时信号。

根据时钟设计方法设计日历功能,同样也加入校正模块。

并且根据日期的进位特点(3月31日,4月30日)完善对日历功能的设计。

四、设计原理:1、根据24进制与60进制的进位信号,完成分钟位,小时位的显示,使其构成基本时钟功能。

2、根据24小时的进位信号count,进行年月日功能的实现。

设置K2与K1为日历与时钟的切换键。

3、在时钟电平作用下,设计两个高低电位JZ1与JZ2电平与K2与K1信号同时控制小时位、分钟的校正。

4、用时钟电平clk2作为闹钟的进位信号,设置K2与K1为闹钟和时钟的切换键。

设置MZ1与MZ2控制闹钟的分钟位与小时位,进行闹钟的设定。

5、在K2、K1与使能信号控制下,设置JZ1与JZ2进行对日历的日与月的校正;JZ1与JZ2进行对年份的个位与十位的校正。

6、最终用K1、K2的四种模式控制显示闹钟、时钟与日历的切换显示模块。

五、设计过程:当时间为23:59:59则进位端count为1,此时判别月份与日期,进行相应的日进位与月进位。

模块2:校准与闹钟设置该程序段为分与时校正,当K1=K2=0时,JZ1为1时,进行分校准;JZ2为1时,进行时校准。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

摘要

本设计为一个可调数字钟,具有时、分、秒计数功能,以24小时循环计数。

本设计采用FPGA技术,以硬件描述语言VreilogHDL为系统逻辑描述手段设计文件,在QUARTUS2工具软件环境下,采用自顶向下的设计方法,由各个模块共同构建一个基于CPLD的数字钟。

系统芯片采用6块74160实现了60进制(分、秒)、24进制(小时)的编译,由时钟模块、控制模块、计时模块、数据译码模块、显示模块组成。

最终经过编译和仿真所涉及的程序,在可编程逻辑器件上下载验证,本系统能够完成时、分、秒的分别显示,可以在程序中直接改变初始值。

关键词:数字钟硬件描述语言VerilogHDL FPGA

1.实验目的

本实验主要内容涉及数字逻辑电路的设计、数字电路仿真软件Quartus Ⅱ以及VHDL 设计语言的学习与应用。

实验目的在于让实验者掌握数字逻辑电路的设计方法和过程,并且能够熟练准确地设计出具有特定功能的较复杂数字逻辑电路,此外,实验者还应熟练掌握Quartus Ⅱ软件的设计、仿真以及编译下载的使用方法。

2 .课程要求

用Verilog 硬件描述语言设计数字钟,实现:

1.具有时、分、秒计数显示功能,以二十四小时循环计时。

2.具有调节小时、分钟功能。

3.具有整点报时功能。

3.系统设计总体方案

秒模块 时模块

4.各模块电路具体实现

4.1 时钟分频模块

module div_clk(clk_50MHz,clk_1Hz,clk_1KHz,clk_500Hz);

input clk_50MHz;

output clk_1Hz,clk_500Hz,clk_1KHz;

reg clk_1Hz,clk_500Hz,clk_1KHz;

reg [24:0] cnt1;

reg [24:0] cnt2;

reg [24:0] cnt3;

always @(posedge clk_50MHz)

begin if(cnt1 == 24999999)

begin cnt1<=0;

clk_1Hz=~clk_1Hz;

end

else cnt1<=cnt1+1'b1;

end

always @(posedge clk_50MHz)

begin if(cnt2 == 24999)

begin cnt2<=0;

clk_1KHz=~clk_1KHz;

end

else cnt2<=cnt2+1'b1;

end

always @(posedge clk_50MHz)

begin if(cnt3 == 49999)

begin cnt3<=0;

clk_500Hz=~clk_500Hz;

end

else cnt3<=cnt3+1'b1;

end

endmodule

4.2计数器模块的设计与实现

4.2.1秒显示模块的实现

图4.2.1 秒钟显示模块4.2.2分钟显示模块的实现

图4.2.2 分钟显示模块4.2.3小时显示模块的实现

图4.2.3 时钟显示模块

4.3 数码管显示及译码模块

module decode(clk_1KHz,hour_ten,hour_one,min_ten,min_one,sec_ten,sec _one,dig,seg);

input clk_1KHz;

input [3:0] hour_ten,hour_one,min_ten,min_one,sec_ten,sec_one; output [7:0] dig;

output [7:0] seg;

reg[7:0] seg_reg;

reg[7:0] dig_reg;

reg[3:0] dat_reg;

reg[2:0] count;

always @(posedge clk_1KHz)

begin

if(count ==5)count<=0;

else count<=count+1'b1;

end

always @(posedge clk_1KHz)

begin

case(count)

3'd0 : begin dat_reg<=hour_ten[3:0];dig_reg<=8'b01111111;end 3'd1 : begin dat_reg<=hour_one[3:0];dig_reg<=8'b10111111;end 3'd2 : begin dat_reg<=min_ten[3:0]; dig_reg<=8'b11011111;end 3'd3 : begin dat_reg<=min_one[3:0]; dig_reg<=8'b11101111;end 3'd4 : begin dat_reg<=sec_ten[3:0]; dig_reg<=8'b11110111;end 3'd5 : begin dat_reg<=sec_one[3:0]; dig_reg<=8'b11111011;end default : begin dat_reg<=0;dig_reg<=6'b000000;end

endcase

end

always @(dat_reg)

begin

case(dat_reg)

4'h0 : seg_reg<=8'hc0;

4'h1 : seg_reg<=8'hf9;

4'h2 : seg_reg<=8'ha4;

4'h3 : seg_reg<=8'hb0;

4'h4 : seg_reg<=8'h99;

4'h5 : seg_reg<=8'h92;

4'h6 : seg_reg<=8'h82;

4'h7 : seg_reg<=8'hf8;

4'h8 : seg_reg<=8'h80;

4'h9 : seg_reg<=8'h90;

default : seg_reg<=8'hff;

endcase

end

assign dig=dig_reg;

assign seg=seg_reg;

endmodule

4.4 数字钟电路模块

图4.4.1 数字钟整体模块5 . 系统仿真及硬件下载

5.1系统仿真

图5.1.1 秒钟仿真结果

图5.1.2 分频仿真结果

5.2硬件下载

经下载后,能实现课程设计要求。

但因设计时间匆忙,并未拍摄照片。

6 . 课程总结

通过本次EDA设计,掌握了较为复杂逻辑电路的设计方法,了解了用VHDL语言编程设计电路的一般方法。

同时锻炼了自己的分析理解能力和动手能力,并且加深了对数电相关知识的理解。

实验时需要十分细心,一不小心就容易出错,一旦出现错误,就要马上耐心地检查线路,分析出错原因,找到错误,并加以更正。

如果不是接线问题,那再去思考一下,是不是设计的原理图有问题。

虽然这不是一个容易的过程,但在这个过程中,锻炼了自己的各项能力,令我受益匪浅。

其实,实验的过程也是锻炼耐力的过程。

在添加闹钟功能时,我们曾遇到过困难。

本来我们的报时电路是对的,可加上闹钟功能后,非但闹钟到时刻不响,就连原本的整点报时也不响了,经过一番仔细的盘查,我们发现原来是我们错用了或门,用高电平和发声频率相或,所以才会没有声音。

另外,在给闹钟增加音乐功能时也花了不少力气,刚开始在网上找的相关资料都不能用,最后终于找到了一个可以播放音乐的资料,我们将找到的VHDL源程序输入到自己的工程,终于成功让闹钟播放音乐闹铃了,那一刻,我们相当开心,因为这是我们通过努力才得到的收获。

这次EDA设计锻炼了我很多方面的能力,为将来的继续学习和工作都积累了宝贵的经验。

希望学校能增加这种实践环节来培养我们的动手能力、分析能力,这些都是在理论课上不曾学到的。

参考文献:

〔1〕康华光.电子数字基础:数字部分.4版.北京:高等教育出版社,2000.

〔2〕蒋立平.数字电路.北京:兵器工业出版社,2001.3.

〔3〕康华光,陈大钦.电子技术基础—数字部分(第五版)[M]. 北京:高等教育出版社,2005.

〔4〕谢自美.电子线路设计·实验·测试(第三版)[M].武汉:华中科技大学出版社, 2006.

〔5〕赵保经.中国集成电路大全.国防工业出版社, 1985.

附录:

附录1 分频仿真图

附录2 电路全图。