基于FPGA的数字时钟

基于FPGA的数字钟设计

数字钟的设计一、 设计要求设计一个数字钟,要求用数码管分别显示时、分、秒的计数,同时可以进行时间设置,并且要求在整点的时候能够实现报时功能。

二、 设计原理计数器在正常工作下是对1Hz的频率计数,在调整时间状态下是对调整的时间模块进行计数;控制按键来选择是正常计数还是调整时间,并决定是调整时还是分;时间显示的LED数码管采用动态扫描实现;在整点到达时,还具有整点报时功能。

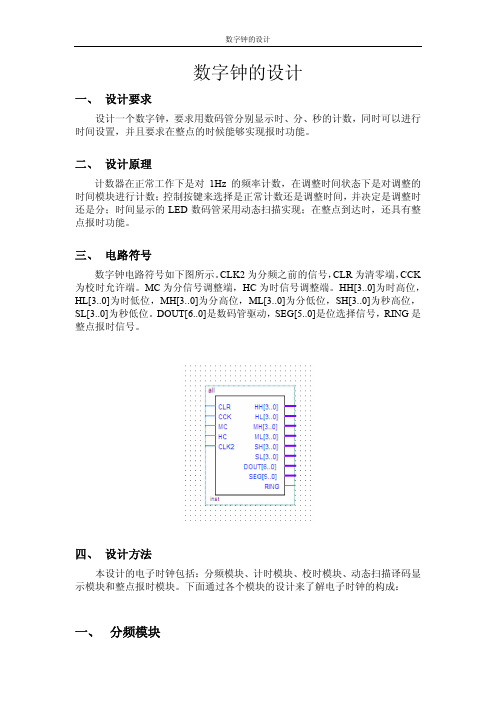

三、 电路符号数字钟电路符号如下图所示。

CLK2为分频之前的信号,CLR为清零端,CCK 为校时允许端。

MC为分信号调整端,HC为时信号调整端。

HH[3..0]为时高位,HL[3..0]为时低位,MH[3..0]为分高位,ML[3..0]为分低位,SH[3..0]为秒高位,SL[3..0]为秒低位。

DOUT[6..0]是数码管驱动,SEG[5..0]是位选择信号,RING是整点报时信号。

四、 设计方法本设计的电子时钟包括:分频模块、计时模块、校时模块、动态扫描译码显示模块和整点报时模块。

下面通过各个模块的设计来了解电子时钟的构成:一、 分频模块程序附录:module clk2clk1s(clk,clk1s); input clk;output clk1s;reg clk1s;reg [3:0] cnt;always@(posedge clk)if(cnt==4'b1111)beginclk1s<=~clk1s;cnt<=0;endelsecnt<=cnt+1; endmodule波形仿真:二、 计时模块六十进制计数器六十进制计数器程序附录:六十进制计数器模块:module m60(clk,clr,qh,ql,cao);input clk,clr;output cao;output[3:0] qh,ql;reg [3:0] qh,ql;reg cao;always @(posedge clk or negedge clr) beginif(clr==0)beginqh<=4'h0;ql<=4'h0;cao<=0;endelse if(ql==9)beginql<=0;if(qh==5)beginqh<=0;cao<=1;endelse qh=qh+1;endelsebeginql<=ql+1;cao<=0;endendendmodule二十四进制计数器模块:module m24(clk,clr,qh,ql);input clk,clr;output[3:0] qh,ql;reg [3:0] qh,ql;always @(posedge clk or negedge clr) beginif(clr==0)beginqh<=4'h0;ql<=4'h0;endelse if(qh==2)beginql<=ql+1;if(ql==3)beginqh<=0;ql<=0;endendelse if(ql==9)beginqh<=qh+1;ql<=0;endelseql<=ql+1; end endmodule波形仿真:清零清零正常计时三、 校时模块四、 动态译码显示模块CCK 为0不支持校时,有进位信号时产生分(时)脉冲程序附录:1、位扫描信号(HH,HL,MH,ML,SH,SL逐位扫描,并输出)module sel(clk,hh,hl,mh,ml,sh,sl,out);input clk;input [3:0] hh,hl,mh,ml,sh,sl;output [3:0] out;reg [3:0] out;reg [3:0] ss=0;always @(posedge clk)beginif(ss<4'b0101)ss<=ss+1;elsess<=0;endalways @(posedge clk)begincase(ss)4'd0:out<=sl;4'd1:out<=sh;4'd2:out<=ml;4'd3:out<=mh;4'd4:out<=hl;4'd5:out<=hh;endendmodule仿真图:2、段扫描信号(选择数码管点亮哪一位)module seg(clk,seg);input clk;output [5:0] seg;reg [5:0] seg;reg [3:0] ss=0;always @(posedge clk)beginif(ss<4'b0101)ss<=ss+1;elsess<=0;endalways @(posedge clk)begincase(ss)4'd0:seg<=6'b111110;4'd1:seg<=6'b111101;4'd2:seg<=6'b111011;4'd3:seg<=6'b110111;4'd4:seg<=6'b101111;4'd5:seg<=6'b011111;default:seg<=6'b111111;endcaseend3、4—7译码module decode4_7(decodeout,indec); output[6:0] decodeout;input[3:0] indec;reg[6:0] decodeout;always @(indec)begincase(indec)4'd0:decodeout=7'b1111110;4'd1:decodeout=7'b0110000;4'd2:decodeout=7'b1101101;4'd3:decodeout=7'b1111001;4'd4:decodeout=7'b0110011;4'd5:decodeout=7'b1011011;4'd6:decodeout=7'b1011111;4'd7:decodeout=7'b1110000;4'd8:decodeout=7'b1111111;4'd9:decodeout=7'b1111011;default: decodeout=7'b0000000;endcaseendendmodule五、 整点报时模块六、 数字钟仿真图数字钟的设计注:动态扫描的时钟频率尽量要快。

基于FPGA的数字钟设计

基于FPGA的数字钟设计摘要:现实生活中经常会出现需要用时间测定参数数值的情况,服务日常生活和生产。

基于FPGA设计数字电路产品已经成为当前的重要设计方法。

本文设计选用了Quartus软件环境,运用描述逻辑Verilog HDL,由上至下的模式,基于FPGA完成了数字时钟的设计方案。

本次设计成果采用按键对闹钟的起止点进行控制,能够显示时,分,秒等并且能够实现整点报时。

其中的FPGA技术就是本次试验的亮点之一,其设计易于学习,各个模块分工清晰,在模拟软件上很容易运行,还能够适配于许多种环境,因此总体的系统性能指标还是相当有保证的。

关键词:数字钟;FPGA;Verilog HDL;Quartus1.1 课题研究背景在现代社会,数据集成电路已广泛运用于日常日常生活的各行各业。

数据集成电路也在不停拆换。

从起初的整流管、电子管、大中小型集成电路发展趋势为具备特大型集成电路和独特作用的各类专用型集成电路。

可是,因为微电子技术科技进步的迅猛发展,集成电路设计方案和生产制造工作中再也不会由半导体生产商独立担负。

系统软件室内设计师更喜欢立即设计方案专用型集成电路(ASIC)处理芯片,并马上资金投入具体运用,因而发生了当场可编程逻辑机器设备(FPLD),在其中应用最普遍的是当场可编门阵列(FPGA)。

数字钟是一种选用数字电路设计技术性完成时、分、秒计时的装置,在完成数据与此同时表明时、分、秒的准确时间和精确校正时,体积小、重量轻、抗干扰能力强、对自然环境需要高、高精密、易于开发设计等与在办公系统系统软件等众多行业运用非常普遍的传统式表壳式机械手表对比,数字表更精确、形象化,因为沒有机械设备装置,使用期限长。

1.2 国内外研究现状近些年来已经有许多技术人员针对电子器件以及时钟等技术进行了研究,但真正意义上的数字钟表起源于50年代或60年代。

伴随着在我国数字钟表电源电路销售市场的迅速发展趋势,尤其是十二五阶段经济发展方法这一领土主权主旋律早已明确,与之有关的关键生产制造技术运用和产品研发将变成领域公司关心的焦点。

基于FPGA的数字电子时钟设计与实现.

课程设计 (论文说明书题目:基于 FPGA 的数字电子时钟设计院 (系 :信息与通信学院专学生姓名:学号:0900240115指导教师:职2012 年 12 月 25 日一、所用设备与器材1.1仪器设备使用仪器设备有 FPGA DE2-70开发板、 PC 机、信号发生器。

图 1 FPGA DE2-70开发板图二.系统方案2.1 设计思想利用数字电子技术、 EDA 设计方法、 FPGA 等技术,设计、仿真并实现一个基于 FPGA 的数字电子时钟基本功能, 其基本组成框图如图 1所示,振荡器采用ALTERA 的 DE2-70实验板的 50MHz 输出,分频器将 50MHz 的方波进行分频进而得到 1Hz 的标准秒脉冲,时、分、秒计时模块分别由二十四进制时计数器、六十进制分计数器和六十进制秒计数器完成,校时模块完成时和分的校正。

扩展功能设计为倒计时功能,从 59分 55秒至 59分 59秒,每秒亮一盏灯报时。

2.1.1课题背景20世纪末,电子技术获得了飞速的发展,在其推动下,现代电子产品几乎渗透了社会的各个领域,有力的推动了社会生产力的发展和社会信息化程度的提高, 同时也使现代电子产品性能更进一步, 产品更新换代的节奏也越来越快。

20世纪 80年代末,出现了 FPGA(Field Progrommable Gate Array, CAE 和 CAD 技术的应用更为广泛,它们在 PCB 设计的原理图输入,自动布局布线及 PCB 分析, 以及逻辑设计,逻辑仿真布尔综合和化简等方面担任了重要的角色,为电子设计自动化必须解决的电路建模,标准文档及仿真测试奠定了基础。

硬件描述语言是 EDA 技术的重要组成部分, VHDL 是作为电子设计主流硬件的描述语言。

本论文就是应用 VHDL 语言来实现秒表的电路设计。

VHDL 语言是标准硬件描述语言,它的特点就是能形式化抽样表示电路结构及行为,支持逻辑设计中层次领域的描述,借用了高级语言的精巧结构简化电路描述,具有电路模拟与验证及保证设计的正确性,支持电路由高层向底层的综合变换,便于文档管理,易于理解和设计重用。

基于FPGA的数字电子钟的设计与实现

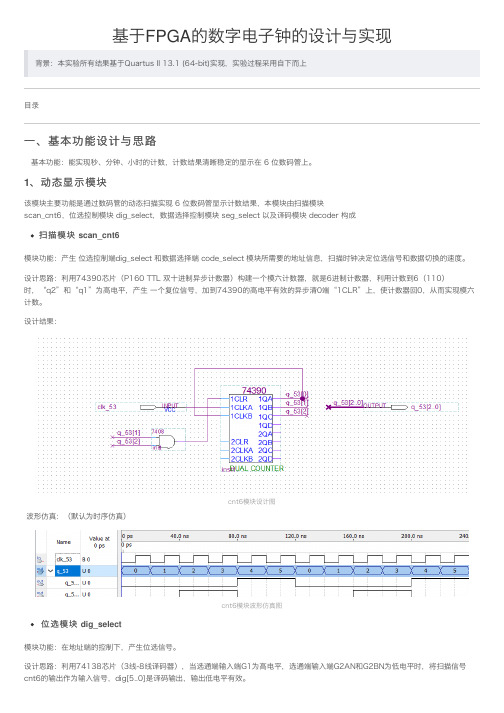

基于FPGA的数字电⼦钟的设计与实现背景:本实验所有结果基于Quartus II 13.1 (64-bit)实现,实验过程采⽤⾃下⽽上⽬录⼀、基本功能设计与思路基本功能:能实现秒、分钟、⼩时的计数,计数结果清晰稳定的显⽰在 6 位数码管上。

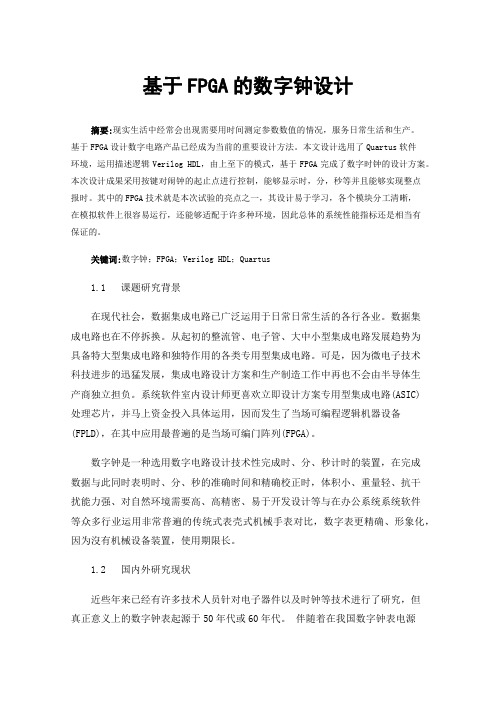

1、动态显⽰模块该模块主要功能是通过数码管的动态扫描实现 6 位数码管显⽰计数结果,本模块由扫描模块scan_cnt6,位选控制模块 dig_select,数据选择控制模块 seg_select 以及译码模块 decoder 构成扫描模块 scan_cnt6模块功能:产⽣ 位选控制端dig_select 和数据选择端 code_select 模块所需要的地址信息,扫描时钟决定位选信号和数据切换的速度。

设计思路:利⽤74390芯⽚(P160 TTL 双⼗进制异步计数器)构建⼀个模六计数器,就是6进制计数器,利⽤计数到6(110)时,“q2”和“q1”为⾼电平,产⽣ ⼀个复位信号,加到74390的⾼电平有效的异步清0端“1CLR”上,使计数器回0,从⽽实现模六计数。

设计结果:cnt6模块设计图波形仿真:(默认为时序仿真)cnt6模块波形仿真图位选模块 dig_select模块功能:在地址端的控制下,产⽣位选信号。

设计思路:利⽤74138芯⽚(3线-8线译码器),当选通端输⼊端G1为⾼电平,选通端输⼊端G2AN和G2BN为低电平时,将扫描信号cnt6的输出作为输⼊信号,dig[5..0]是译码输出,输出低电平有效。

设计结果:dig_select模块设计图波形仿真:dig_select模块波形仿真图数据选择模块 seg_select模块功能:输⼊ 6 组数据,每组数据 4bit,本模块完成在地址端的控制下从6 组数据当中选择 1 组输出。

设计思路:利⽤74151芯⽚(P91 8选1数据选择器),在控制输⼊端GN为低电平时,将扫描信号的选择下,分别选中D[5..0]对应的输⼊信号输出为Y。

多功能数字时钟fpga源代码

多功能数字时钟fpga源代码以下是一个基于FPGA的多功能数字时钟的简化源代码示例。

请注意,由于FPGA设计和编程的复杂性,这里提供的代码只是一个概念性的框架,并不能直接用于生产环境。

此外,代码的长度和详细程度可能会因具体的FPGA型号、设计工具和需求而有所不同。

verilogmodule DigitalClock(input wire clk, // 输入时钟信号input wire rst, // 复位信号output wire [5:0] sec, // 秒output wire [5:0] min, // 分output wire [4:0] hour // 时);reg [25:0] counter = 0; // 26位计数器reg [5:0] sec_reg = 0, min_reg = 0, hour_reg = 0; // 寄存器always @(posedge clk or posedge rst) beginif (rst) begincounter <= 0;sec_reg <= 0;min_reg <= 0;hour_reg <= 0;end else begincounter <= counter + 1;if (counter == 50000000) begin // 假设时钟频率为50MHz,则每1秒计数器加1counter <= 0;sec_reg <= sec_reg + 1;if (sec_reg == 60) beginsec_reg <= 0;min_reg <= min_reg + 1;if (min_reg == 60) beginmin_reg <= 0;hour_reg <= hour_reg + 1;if (hour_reg == 24)hour_reg <= 0;endendendendendassign sec = sec_reg;assign min = min_reg;assign hour = hour_reg;endmodule以上代码是用Verilog语言编写的,它是一种硬件描述语言,常用于FPGA和ASIC设计。

基于FPGA的数字时钟设计开题报告

开题报告毕业设计题目:基于FPGA的数字钟系统设计基于FPGA的数字钟系统设计开题报告1选题目的意义和可行性在这个时间就是金钱的年代里,数字电子钟已成为人们生活中的必需品。

目前应用的数字钟不仅可以实现对年、月、日、时、分、秒的数字显示,还能实现对电子钟所在地点的温度显示和智能闹钟功能,广泛应用于车站、医院、机场、码头、厕所等公共场所的时间显示。

随着现场可编程门阵列( field program-mable gate array ,FPGA) 的出现,电子系统向集成化、大规模和高速度等方向发展的趋势更加明显[1],作为可编程的集成度较高的ASIC,可在芯片级实现任意数字逻辑电路,从而可以简化硬件电路,提高系统工作速度,缩短产品研发周期。

故利用FPGA这一新的技术手段来研究电子钟有重要的现实意义。

设计采用FPGA现场可编程技术,运用自顶向下的设计思想设计电子钟。

避免了硬件电路的焊接与调试,而且由于FPGA的I /O端口丰富,内部逻辑可随意更改,使得数字电子钟的实现较为方便。

本课题使用Cyclone EP1C6Q240的FPGA器件,完成实现一个可以计时的数字时钟。

该系统具有显示时、分、秒,智能闹钟,按键实现校准时钟,整点报时等功能。

满足人们得到精确时间以及时间提醒的需求,方便人们生活[2-3]。

2 研究的基本内容与拟解决的主要问题2.1研究的基本内容数字时钟是采用电子电路实现对时间进行数字显示的计时装置,由于数字集成电路的发展和石英晶体振荡器的广泛应用,使得数字钟的精度不断提高。

数字时钟系统的实现有很多,可以利用VerilogDHL语言在Quartus II里实现时、分、秒计数的功能。

在芯片内部存储器设24个字节分别存放时钟的时、分、秒信息。

数字时钟首先是秒位(共8位)上按照系统时钟CLK进行计数,存储器内相应的秒值加1;若秒位的值达到60(110000),则将其清零,并将相应的分位(共8位)的值加1;若分值达到60(110000),则清零分位,并将时位(共8位)的值加1;若计数满24(100100)后整个系统从0开始重新进行计数。

基于FPGA的数字钟课程设计

集成电路设计课程设计报告专业班级学号姓名基于FPGA的数字钟课程设计1.任务和设计要求设计具有时、分、秒计数显示,以24小时循环计时的时钟电路,带有清零和校准功能;2.设计原理采用硬件描述语言Verilog 进行编程,实现20MHZ晶振到1HZ的分频;采用verilog 语言实现数字表功能实现的各个模块;通过各个模块的代码生成相应的模块原理图;再将各个模块生成的原理图进行叠加组成一个数字表系统;3.系统设计设计的数字表有6个输入,16个输出;6个输入中,有一个是时钟信号,开发板上的28号引脚输入的50MHZ的时钟信号;一个清零端,当数字表正常显示时,按下清零端可以实现数字钟整体电路图:4.各个模块设计基于EP1C6Q240C8的数字钟设计,有6个模块组成:Fdiv 分频模块Control 模式选择模块Tune 校正模块Zoushi 时间正常运行模块Saomiao 数码管动态扫描模块;Decoder BCD译码模块;Fdiv 模块:功能:实现20MHZ的时钟信号分成10KHZ的信号和1HZ的信号;输入:clk 为20MHZ的时钟信号;输出:f10000HZ 为10KH的时钟信号;F1HZ 为1HZ的时钟信号;Fdiv 模块代码:module fdiv(clk,f10000Hz,f1Hz);output f10000Hz,f1Hz;input clk;reg f10000Hz,f1Hz;integer CNT1=0,CNT2=0;always@(posedge clk)beginif(CNT1<1999)beginCNT1=CNT1+1;f10000Hz<=1'b0;endelsebeginCNT1=0;f10000Hz<=1'b1;endendalways@(posedge f10000Hz)beginif(CNT2<9999)beginCNT2=CNT2+1;f1Hz<=1'b0;endelsebeginCNT2=0;f1Hz<=1'b1;endendendmodulefdiv 模块波形仿真:由于实际的分频波形仿真中,由于要将20MHZ的分成1HZ的,需要将信号缩小20 000 000倍,因此,此处采用将20HZ的先分成10HZ,然后再将10HZ的分成1HZ的时钟信号;在仿真中这样整,在实际演示中再改下代码,实现真正的20MHZ到1HZ的分频;它们只是一个倍数关系而已;Control 模块:功能:实现电子表的正常显示及时间校正模式的转换;输入:key 模式修改键,每来一个高电平,mode加一次。

《可编程逻辑器件及应用》课程设计--基于FPGA的多功能数字时钟

摘要本课程设计给出了一种基于FPGA的多功能数字时钟方法,采用EDA作为开发工具,VHDL语言和图形输入为硬件描述语言,Quartus II 9.0作为运行程序的平台,编写的程序经过调试运行,波形仿真验证,下载到EDA实验箱的FPGA 芯片,实现了设计目该系统主要由分频模块、控制模块、计时模块、显示模块组成。

经编译和仿真所设计的程序,在可编程逻辑器件上下载验证,能够在数码管上完成年、月、日和时、分、秒的分别显示,由按键输入进行数字时钟的校时、清零、暂停功能。

关键词:EDA技术;FPGA;数码管AbstractThe course design gives a FPGA-based multifunctional digital clock using EDA as a development tool, VHDL language and graphical input hardware description language, the Quartus II 9.0 as a platform for running the program, written procedures debugging and running, the waveform simulation downloaded to the FPGA chip to achieve the design goals.The design for a multi-functional digital clock, with a year, month, day, hours, minutes and seconds count display to a 24-hour cycle count, with the pause time, clear function and the hours and minutes setting function.The main system is made up of frequency module, control module, time module, display module. After compiling the design and simulation procedures, the programmable logic device to download verification, the system can complete the year, month, day and the hours, minutes and seconds respectively, using keys to modify, clear , start and stop the digital clock.Key words:EDA technology;FPGA; digital clock; VHDL language; digital tube目录1 绪论................................................................................................................................... .. (1)1.1 课程背景 (1)1.2 设计目的 (1)2 总体设计流程说明 (2)2.1数字时钟的工作原理 (2)3 单元模块设计流程 (5)3.1 分频模块 (5)3.2 计数模块 (5)3.3 控制模块 (7)4 系统调试说明及分析 (10)5 总结 (11)6 附录 (12)1绪论1.1课程背景如今电子产品正向功能多元化,体积最小化,功耗最低化的方向发展。

(完整word版)基于FPGA的数字时钟设计开题报告

开题报告毕业设计题目:基于FPGA的数字钟系统设计基于FPGA的数字钟系统设计开题报告1选题目的意义和可行性在这个时间就是金钱的年代里,数字电子钟已成为人们生活中的必需品。

目前应用的数字钟不仅可以实现对年、月、日、时、分、秒的数字显示,还能实现对电子钟所在地点的温度显示和智能闹钟功能,广泛应用于车站、医院、机场、码头、厕所等公共场所的时间显示。

随着现场可编程门阵列( field program-mable gate array ,FPGA) 的出现,电子系统向集成化、大规模和高速度等方向发展的趋势更加明显[1],作为可编程的集成度较高的ASIC,可在芯片级实现任意数字逻辑电路,从而可以简化硬件电路,提高系统工作速度,缩短产品研发周期。

故利用FPGA这一新的技术手段来研究电子钟有重要的现实意义。

设计采用FPGA现场可编程技术,运用自顶向下的设计思想设计电子钟。

避免了硬件电路的焊接与调试,而且由于FPGA的I /O端口丰富,内部逻辑可随意更改,使得数字电子钟的实现较为方便。

本课题使用Cyclone EP1C6Q240的FPGA器件,完成实现一个可以计时的数字时钟。

该系统具有显示时、分、秒,智能闹钟,按键实现校准时钟,整点报时等功能。

满足人们得到精确时间以及时间提醒的需求,方便人们生活[2-3]。

2 研究的基本内容与拟解决的主要问题2.1研究的基本内容数字时钟是采用电子电路实现对时间进行数字显示的计时装置,由于数字集成电路的发展和石英晶体振荡器的广泛应用,使得数字钟的精度不断提高。

数字时钟系统的实现有很多,可以利用VerilogDHL语言在Quartus II里实现时、分、秒计数的功能。

在芯片内部存储器设24个字节分别存放时钟的时、分、秒信息。

数字时钟首先是秒位(共8位)上按照系统时钟CLK进行计数,存储器内相应的秒值加1;若秒位的值达到60(110000),则将其清零,并将相应的分位(共8位)的值加1;若分值达到60(110000),则清零分位,并将时位(共8位)的值加1;若计数满24(100100)后整个系统从0开始重新进行计数。

基于FPGA的数字时钟的设计1.(精选)

基于FPGA的数字时钟的设计课题:基于FPGA的数字时钟的设计学院:电气信息工程学院专业:测量控制与仪器班级: 08测控(2)班**:***学号: ********合作者姓名:颜志林2010 年12 月12 日综述近年来随着数字技术的迅速发展,各种中、大规模集成电路在数字系统、控制系统、信号处理等方面都得到了广泛的应用。

这就迫切要求理工科大学生熟悉和掌握常用中、大规模集成电路功能及其在实际中的应用方法,除通过实验教学培养数字电路的基本实验方法、分析问题和故障检查方法以及双踪示波器等常用仪器使用方法等基本电路的基本实验技能外,还必须培养大学生工程设计和组织实验能力。

本次课程设计的目的在于培养学生对基本电路的应用和掌握,使学生在实验原理的指导下,初步具备基本电路的分析和设计能力,并掌握其应用方法;自行拟定实验步骤,检查和排除故障、分析和处理实验结果及撰写实验报告的能力。

综合实验的设计目的是培养学生初步掌握小型数字系统的设计能力,包括选择设计方案,进行电路设计、安装、调试等环节,运用所学知识进行工程设计、提高实验技能的实践。

数字电子钟是一种计时装置,它具有时、分、秒计时功能和显示时间功能;具有整点报时功能。

本次设计我查阅了大量的文献资料,学到了很多关于数字电路方面的知识,并且更加巩固和掌握了课堂上所学的课本知识,使自己对数字电子技术有了更进一步的认识和了解。

1、课题要求1.1课程设计的性质与任务本课程是电子与信息类专业的专业的专业基础必修课——“数字电路”的配套实验课程。

目的在于培养学生的理论联系实际,分析和解决问题的能力。

通过本课程设计,使学生在理论设计、计算机仿真、指标调测、故障排除等方面得到进一步的训练,加强学生的实践能力。

学生通过设计、仿真、调试、撰写设计报告等过程,培养学生的动手能力和严谨的工作作风。

1.2课程设计的基本技术要求1)根据课题要求,复习巩固数字电路有关专业基础知识;2)掌握数字电路的设计方法,特别是熟悉模块化的设计思想;3) 掌握QUARTUS-2软件的使用方法;4) 熟练掌握EDA工具的使用,特别是原理图输入,波形仿真,能对仿真波形进行分析;5) 具备EDA技术基础,能够熟练使用VHDL语言进行编程,掌握层次化设计方法;6) 掌握多功能数字钟的工作原理,学会不同进制计数器及时钟控制电路的设计方法;7) 能根据设计要求对设计电路进行仿真和测试;8) 掌握将所设计软件下载到FPGA芯片的下载步骤等等。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

xxxx大学

电子设计自动化技术与应用

设计报告

设计题目:基于FPGA的数字时钟

学院:通信学院

姓名:

学号:

目录

一、设计任务 (3)

二、总体设计方案 (3)

1、设计思想 (3)

2、总体设计框图 (3)

三、单元电路设计 (4)

1、秒计数器模块设计与实现 (4)

2、分计数器模块设计与实现 (5)

3、时计数器模块设计与实现 (6)

4、2选1选择器模块设计与实现 (7)

5、译码器模块的设计与实现 (8)

6、3-8线译码器模块设计与实现 (9)

7、分频器的设计与实现 (9)

8、顶层原理设计图 (10)

四、硬件测试与结果分析 (11)

1、硬件测试: (11)

2、测试过程及结果分析 (12)

五、收获与体会 (12)

一、设计任务

1、能进行正常的时、分、秒计时功能,由LED数码管显示时间,最大计时

为23:59:59。

2、小时显示采用24进制,分显示和秒显示都采用60进制。

3、具有调时和调分功能。

二、总体设计方案

1、设计思想

本设计是基于Altera公司的Cyclone III 系列的EP3C16Q240C8芯片设计的,采用层次化设计方式,先设计数字时钟的底层器件:秒计数器、分计数器、时计数器、2选1选择器、译码器、分频器。

顶层采用原理图设计方式,将所设计的底层器件连接起来构成一个具有计时和调时功能的数字时钟。

2、总体设计框图

完整的数字时钟设计硬件框图如图所示。

三、单元电路设计

1、秒计数器模块设计与实现

1.1秒计数器流程图如下:

1.2秒计数器生成模块如图1所示:

图1

其中,clk 是时钟信号,daout 是60计数输出,enmin 是向分进位的高电平。

1.3 波形仿真图

波形分析:由波形图知秒计数器是由60进制计数器完成的00到59的循环计数功能,当计数到59时,再来一个计数脉冲则产生进位输出,即enmin=1,作为分计数器的计数脉冲。

2、分计数器模块设计与实现

2.1分计数器流程图如下:

2.2分计数器生成模块如图2所示:

其中,clk是时钟信号,daout是60计数输出,enhour是向时进位的高电平。

2.3波形仿真图

波形分析:由波形图可知,该模块实现了分计数的功能,计数循环从00到59,计数脉冲为秒计数器的进位输出,即enmin。

当计数到59时,再来一个计数脉冲则产生进位输出,即enhour=1,作为时计数器的计数脉冲。

3、时计数器模块设计与实现

3.1时计数器流程图如下:

3.2时计数器生成模块如图3所示:

其中,clk 是时钟信号,daout 是24计数输出。

3.3波形仿真图

波形分析:小时计数模块由24进制计数器完成的从00到23之间的循环计数,计数脉冲为分计数器的进位输出,即enhour 。

4、2选1选择器模块设计与实现

4.1 2选1选择器流程图如下:

4.2 2选1选择器生成模块如图4所示:

图4

其中,sel 是按键信号,b 是时钟信号,a 是来自秒向分进位(分向时进位)的信号,y 是所选信号。

5、译码器模块的设计与实现

5.1译码器流程如下:

5.2译码器生成模块如图5所示:

图5

其中,clk是时钟信号,second是秒计数数据,minute是分计数数据,hour是时计数数据,seg_dp 是显示“点”,sel是数码管的位选通信号,seg是数码管显示信号。

5.3波形仿真图

波形分析:译码器模块完成了将时、分、秒的二进制码转换为能在LED数码管上显示的7端BCD码,同时产生了数码管的位选通信号,即sel,位选通信号是将

时、分、秒的7端BCD码分别显示在对应的数码管上。

6、3-8线译码器模块设计与实现

6.1 3-8线译码器流程图如下:

6.2 3-8线译码器生成模块如图6所示:

图6

其中,sel是时、分、秒选择信号,y是8位译码信号。

6.3波形仿真图

波形分析:由波形图分析可知,3-8线译码器完成了3位信号的输入到8位译码的输出功能。

7、分频器的设计与实现

7.1 分频器流程图如下:

由于要为秒计数器提供1hz的脉冲和数码显示提供1000hz的脉冲,所

以要把50Mhz的时钟信号进行分频。

这是产生1hz脉冲这是产生1000hz脉冲

7.2分频器生成模块如图7所示。

图7

8、顶层原理设计图

将分频器、2选1选择器、秒计数器、分计数器、时计数器、译码器、3-8线译码器按照要求连接起来就组成了整个数字时钟的原理图,如图8所示。

图8

四、硬件测试与结果分析

1、硬件测试:

测试方式:clk选用clk1。

KS[0]控制调分,KS[1]控制调时。

数码管数码管

8、7用作小时显示,高位是小时的十位,低位是小时的个位。

数码管5、4用作

分钟显示,高位是分钟的十位,低位是分钟的个位。

数码管2、1用作秒钟显示,高位是秒钟的十位,低位是秒钟的个位。

管脚分配如图9所示。

图9

2、测试过程及结果分析

将文件下载到FPGA中,数码管上显示00-00-00,并开始计时,秒钟计到59向分钟进1,分钟计到59向小时进1。

闭合KS[0]键分钟以1HZ的频率加1,加到59向小时进1,分钟清0。

闭合KS[1]键小时以1HZ的频率加1,加到59小时清0。

本数字时钟能够满足正常计时和调分调时功能,达到预期的设计效果。

五、收获与体会

经过这次的数字时钟的综合设计,我对FPGA的知识从一窍不通开始有点了解了。

对QUTARTUS软件也是从零基础开始的,通过查阅各种资料,学习

其用法。

程序也是参考别人或者书上的,自己进行了调试,也修改了一些,

从中学到不少知识。

在进行波形仿真时不能仿真正确,请教过别人,学到了

很多有用的方法。

在此次设计中自己亲自参与了设计,这是很宝贵的。

对于我们搞理论研究的人来说,这次张毅老师的电子设计自动化实验课程弥补了我们动手能力

不强这方面的不足,这是难能可贵的,也正是达到了我学这门实验课的目地。

在设计中,我们还培养了自己独立分析问题和解决问题的能力。

总的来说,通过这门实验课,我们不仅对理论知识有了更深刻的理解,实际操作能力也得到了很好的锻炼,所以,我们不仅学到了知识,同时也得

到了很好的锻炼,衷心的感谢老师及这门课程。