基于FPGA的数字钟设计

基于FPGA的电子钟设计报告

基于FPGA的电子钟设计报告一、FPGA的基本知识1、可编程逻辑器件的概况可编程逻辑器件主要分为FPGA和CPLD 两种,两者的功能基本相同。

FPGA--现场可编程门阵列的简称CPLD--复杂可编程逻辑器件的简称2、FPGA芯片及其最小系统(1)FPGA芯片它的外形与普通嵌入式处理器芯片相同采用PGA(Organic pin grid Array,有机管脚阵列)的封装形式,但可以通过烧写特殊程序改变其内部结构,实现专门的电路功能。

基于FPGA的数字时钟2019-11-23 21:36·电力源动一、FPGA的基本知识1、可编程逻辑器件的概况可编程逻辑器件主要分为FPGA和CPLD 两种,两者的功能基本相同。

FPGA--现场可编程门阵列的简称CPLD--复杂可编程逻辑器件的简称它的外形与普通嵌入式处理器芯片相同采用PGA(Organic pin grid Array,有机管脚阵列)的封装形式,但可以通过烧写特殊程序改变其内部结构,实现专门的电路功能。

二、FPGA的设计方法1、编程语言FPGA的主流程序设计语言主要有VHDL语言与Verilog语言两种。

本课题采用VHDL语言进行编写。

VHDL--用简洁明确的源代码来描述复杂的逻辑控制。

它具有多层次的设计描述功能,层层细化,最后可直接生成电路级描述。

Verilog--一种基本语法与C语言相近,相比较于C语言更容易理解,2、图形化程序设计(设计效率低)三、软件开发环境QuartusII是Altera提供的FPGA开发集成环境,它提供了一种与结构无关的设计环境,使设计者能方便地进行设计输入、快速处理和器件编程。

它完全支持VHDL设计流程,其内部嵌有VHDL逻辑综合器。

四、数字钟功能模块认识数字时钟的设计采用了自顶向下分模块的设计。

底层是实现各功能的模块,各模块由VHDL语言编程实现顶层采用原理图形式调用。

具体的设计框图:各模块原理剖析:(1)在七段数码管上具有时--分--秒的依次显示;(2)时、分、秒的个位记满十向高位进一,分、秒的十位记满五向高位进一,小时按24进制计数,分、秒按60进制计数;(3)整点报时,当计数到整点时扬声器发出响声;(4)时间设置:可以通过按键手动调节秒和分的数值。

基于fpga的数字钟电路设计

基于fpga的数字钟电路设计

随着电子技术和航空电子技术的发展,高精度的电子时钟发挥着越来越重要的作用。

面对众多的时间选择方式,FPGA技术为企业提供了新的解决方案。

本文旨在设计一种基于FPGA技术的数字时钟电路,以满足工业系统时间测量和管理的需求。

数字时钟电路的设计主要分为三个方面:晶振、时钟频率调整以及I/O管脚分配。

首先,选用封装形式为HC49-S的晶振器,其主要特征包括频率精度低至±50ppm、温度范围

宽至−10℃至+70℃、工作温度可升至105℃以及动态特性良好等。

其次,进行时钟频率

调节用FPGA。

FPGA的时钟频率调节模块采用MMC和VCO技术实现时钟频率抢断,可对晶

振的稳定频率进行调节,从而获得高精度的时钟信号。

最后,通过FPGA的I/O管脚分配

完成时钟信号输出,从而将数字信号变换为时间信号,实现时间数据的采集和处理。

基于FPGA技术的数字时钟电路可以有效地满足工业系统实时时间测量和管理的需求,实现工业系统时间计量技术的发展。

该电路具有稳定高效、体积小、功耗低以及现场可实

现调整参数等优缺点,在工业领域具有很高的应用前景。

基于FPGA数字时钟

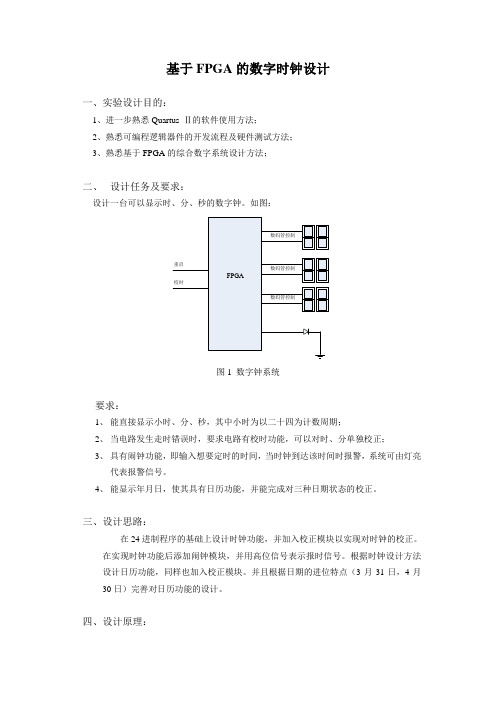

基于FPGA的数字时钟设计一、课程设计目的1、进一步熟悉QuartusⅡ的软件使用方法;2、熟悉可编程逻辑器件的开发流程及硬件测试方法;3、熟悉基于FPGA的综合数字系统设计方法;二、设计任务设计一台可以显示时、分、秒的数字钟。

如图1所示为基于FPGA的数字钟设计的系统框图。

图1 数字钟系统三、设计要求1、能直接显示小时、分、秒,其中小时为以二十四为计数周期;2、能够显示日期(即年、月、日),且要求在显示时钟的数码管上显示日期,即时钟数码管与日期数码管复用;3、年、月、日要严格按照实际日期,例如1月31天,4月30天,2月闰年29天等;4、当数字钟发生走时错误时,要求电路有校时功能,可以对时、分单独校正,且校正时间时系统时钟不工作;5、当日期发生错误时,要求有校正日期功能,可以对年、月、日单独校正,且矫正日期时时钟系统仍然工作;6、具有闹钟功能,即输入想要定时的时间,当时钟到达该时间时报警,系统可由灯亮代表报警信号。

四、设计内容1、时间计数模块本次是将秒分时各个模块分开进行设计,用秒的进位作为分模块的脉冲,用分的进位作为是模块的脉冲。

秒进位的仿真波形程序:秒的程序module miao(clk,gdata,ddata,en,cl,clr);input clk;input en;input clr;output [3:0] ddata;output [3:0] gdata;output cl;reg [7:0] q;reg cl;assign ddata=q%10;assign gdata=q/10;always @(negedge clk or posedge clr)beginif(clr==1)q=0;elsebeginif(en==1)beginif(q<59)beginq=q+1;cl=0;endelsebeginq=0;cl=1;endendendendendmodule分模块和时模块的程序一秒程序类似,只是进位计数不一样。

基于XilinxFPGA的数字钟设计

基于FPGA的多功能数字钟一、设计题目基于Xilinx FPGA的多功能数字钟设计二、设计目的1.掌握可编程逻辑器件的应用开发技术——设计输入、编译、仿真和器件编程;2.熟悉一种EDA软件使用;3.掌握Verilog设计方法;4.掌握分模块分层次的设计方法;5.用Verilog完成一个多功能数字钟设计;6.学会FPGA的仿真。

三、设计内容设计实验项目九多功能电子钟✧功能要求:利用实验板设计实现一个能显示时分秒的多功能电子钟,具体要求为:基本功能:1)准确计时,以数字形式显示时、分、秒,可通过按键选择指示当前显示时间范围模式;2)计时时间范围 00:00:00-23:59:593)可实现校正时间功能;4)可通过实现时钟复位功能:00:00:00扩展功能:1)定时报:时间自定(不要求改变),闹1分钟(1kHz)---利用实验板LED或外接电路实现。

2)仿广播电台正点报时:XX:59:[51,53,55,57(500Hz);59(1kHz)] ---利用实验板LED或外接电路实现。

3)报整点时数:XX:00:[00.5-XX.5](1kHz),自动、手动---利用实验板LED或外接电路实现。

4)手动输入校时;5)手动输入定时闹钟;6)万年历;7)其他扩展功能;✧设计步骤与要求:1)计算并说明采用Basys2实验板时钟50MHz实现系统功能的基本原理。

2)在Xilinx ISE13.1 软件中,利用层次化方法,设计实现模一百计数及显示的电路系统,设计模块间的连接调用关系,编写并输入所设计的源程序文件。

3)对源程序进行编译及仿真分析(注意合理设置,以便能够在验证逻辑的基础上尽快得出仿真结果)。

4)输入管脚约束文件,对设计项目进行编译与逻辑综合,生成下载所需.bit类型文件。

5)在Basys2实验板上下载所生成的.bit文件,观察验证所设计的电路功能。

四、总体设计思路主体分为分频模块,正常时间模块(包含两个模60计数器和一个模24计数器子模块),闹钟模块(分为一个模60计数器模块,一个模24计数器模块,四个比较器模块),电台报时模块,数码管显示模块(分为模式选择模块,片选信号及扫描程序模块,和译码模块)。

基于FPGA的数字钟课程设计

集成电路设计课程设计报告专业班级学号姓名基于FPGA的数字钟课程设计1.任务和设计要求设计具有时、分、秒计数显示,以24小时循环计时的时钟电路,带有清零和校准功能;2.设计原理采用硬件描述语言Verilog 进行编程,实现20MHZ晶振到1HZ的分频;采用verilog 语言实现数字表功能实现的各个模块;通过各个模块的代码生成相应的模块原理图;再将各个模块生成的原理图进行叠加组成一个数字表系统;3.系统设计设计的数字表有6个输入,16个输出;6个输入中,有一个是时钟信号,开发板上的28号引脚输入的50MHZ的时钟信号;一个清零端,当数字表正常显示时,按下清零端可以实现数字钟整体电路图:4.各个模块设计基于EP1C6Q240C8的数字钟设计,有6个模块组成:Fdiv 分频模块Control 模式选择模块Tune 校正模块Zoushi 时间正常运行模块Saomiao 数码管动态扫描模块;Decoder BCD译码模块;Fdiv 模块:功能:实现20MHZ的时钟信号分成10KHZ的信号和1HZ的信号;输入:clk 为20MHZ的时钟信号;输出:f10000HZ 为10KH的时钟信号;F1HZ 为1HZ的时钟信号;Fdiv 模块代码:module fdiv(clk,f10000Hz,f1Hz);output f10000Hz,f1Hz;input clk;reg f10000Hz,f1Hz;integer CNT1=0,CNT2=0;always@(posedge clk)beginif(CNT1<1999)beginCNT1=CNT1+1;f10000Hz<=1'b0;endelsebeginCNT1=0;f10000Hz<=1'b1;endendalways@(posedge f10000Hz)beginif(CNT2<9999)beginCNT2=CNT2+1;f1Hz<=1'b0;endelsebeginCNT2=0;f1Hz<=1'b1;endendendmodulefdiv 模块波形仿真:由于实际的分频波形仿真中,由于要将20MHZ的分成1HZ的,需要将信号缩小20 000 000倍,因此,此处采用将20HZ的先分成10HZ,然后再将10HZ的分成1HZ的时钟信号;在仿真中这样整,在实际演示中再改下代码,实现真正的20MHZ到1HZ的分频;它们只是一个倍数关系而已;Control 模块:功能:实现电子表的正常显示及时间校正模式的转换;输入:key 模式修改键,每来一个高电平,mode加一次。

基于FPGA的数字时钟设计

基于FPGA的数字时钟设计一、实验设计目的:1、进一步熟悉QuartusⅡ的软件使用方法;2、熟悉可编程逻辑器件的开发流程及硬件测试方法;3、熟悉基于FPGA的综合数字系统设计方法;二、设计任务及要求:设计一台可以显示时、分、秒的数字钟。

如图:图1 数字钟系统要求:1、能直接显示小时、分、秒,其中小时为以二十四为计数周期;2、当电路发生走时错误时,要求电路有校时功能,可以对时、分单独校正;3、具有闹钟功能,即输入想要定时的时间,当时钟到达该时间时报警,系统可由灯亮代表报警信号。

4、能显示年月日,使其具有日历功能,并能完成对三种日期状态的校正。

三、设计思路:在24进制程序的基础上设计时钟功能,并加入校正模块以实现对时钟的校正。

在实现时钟功能后添加闹钟模块,并用高位信号表示报时信号。

根据时钟设计方法设计日历功能,同样也加入校正模块。

并且根据日期的进位特点(3月31日,4月30日)完善对日历功能的设计。

四、设计原理:1、根据24进制与60进制的进位信号,完成分钟位,小时位的显示,使其构成基本时钟功能。

2、根据24小时的进位信号count,进行年月日功能的实现。

设置K2与K1为日历与时钟的切换键。

3、在时钟电平作用下,设计两个高低电位JZ1与JZ2电平与K2与K1信号同时控制小时位、分钟的校正。

4、用时钟电平clk2作为闹钟的进位信号,设置K2与K1为闹钟和时钟的切换键。

设置MZ1与MZ2控制闹钟的分钟位与小时位,进行闹钟的设定。

5、在K2、K1与使能信号控制下,设置JZ1与JZ2进行对日历的日与月的校正;JZ1与JZ2进行对年份的个位与十位的校正。

6、最终用K1、K2的四种模式控制显示闹钟、时钟与日历的切换显示模块。

五、设计过程:当时间为23:59:59则进位端count为1,此时判别月份与日期,进行相应的日进位与月进位。

模块2:校准与闹钟设置该程序段为分与时校正,当K1=K2=0时,JZ1为1时,进行分校准;JZ2为1时,进行时校准。

基于FPGA的数字时钟设计

第28卷 第5期核电子学与探测技术V ol .28 N o .5 2008年 9月Nuclear Electronics &Detection Technolo gySep . 2008 基于FPGA 的数字时钟设计宋克柱(中国科学技术大学近代物理系快电子学实验室,合肥 230026) 摘要:本文介绍一种基于F PG A 的数字时钟设计方法:DCM (数字时钟管理器)。

DCM 使用完全数字反馈系统确保多个时钟同步,使用完全数字延迟线技术可以精确控制时钟的频率和相位。

用户可以编程控制时钟任意倍频和分频及任意相位移动,使用非常方便可靠。

文章还给出应用设计原理图及逻辑仿真波形图。

关键词:时钟、锁相环、频率合成、相位移动、DCM中图分类号: T N786 文献标识码: A 文章编号: 0258-0934(2008)05-0982-05收稿日期:2006-12-27作者简介:宋克柱,男,1966年9月生,籍贯安徽和县,副教授,博士。

主要从事高速数据采集和信号处理、高速通讯等领域的研究工作。

已发表论文20多篇。

在较复杂应用电子系统中,经常会在一个系统或一块电路板中用到多种频率、不同相位或固定相位差的高速多相时钟,例如,高精度TDC (时间数字转换)系统。

传统的设计方法是采用锁相环分立器件来产生高速时钟,采用延迟线或分立器件产生时钟延时。

这些方法的缺点是精度不高、使用不方便,尤其高速时钟在PCB 板布线会产生较大的畸变。

随着大规模可编程逻辑器件FPGA 或CPLD 技术的发展,世界上几大可编程逻辑器件厂家都推出了新型的可编程逻辑器件,可以将锁相环或其它数字时钟逻辑核(logic core )集成在FPGA 里。

例如,Xilinx 公司的VirtexII 系列FPGA 的DCM (Digital Clo ck M anage r ),Altera 公司的A -pex20KE 系列的PLL (Phase Locked Loo p )。

基于FPGA的多功能数字时钟设计

7.利用适配器将综合后的网络表文件针对某一具体的目标器件进行逻辑映射操作,包括底层器件配置、逻辑分割、逻辑优化和布局布线。

8.在适配完成后,产生多项设计结果:(a)适配报告,包括芯片内部资源利用情况,设计的布尔方程描述情况等;(b)适配后的仿真模型;(c)器件编程文件。根据适配后的仿真模型,可以进行适配后时序仿真,因为已经得到器件的实际硬件特性(如时延特性),所以仿真结果能比较精确的预期未来芯片的实际性能。如果仿真结果达不到设计要求,就修改VHDL源代码或选择不同速度和品质的器件,直至满足设计要求。

1.CLB是FPGA的主要组成部分。图2-1是CLB基本结构框图,它主要由逻辑函数发生器、触发器、数据选择器等电路组成。CLB中3个逻辑函数发生器分别是G、F和H,相应的输出是G’、F’和H’。G有4个输入变量G1、G2、G3和G4;F也有4个输入变量F1、F2、F3和F4。这两个函数发生器是完全独立的,均可以实现4输入变量的任意组合逻辑函数。逻辑函数发生器H有3个输入信号;前两个是函数发生器的输出G’和F’,而另一个输入信号是来自信号变换电路的输出H1。这个函数发生器能实现3输入变量的各种组合函数。这3个函数发生器结合起来,可实现多达9变量的逻辑函数。

基于FPGA的数字电子钟的设计与实现

基于FPGA的数字电⼦钟的设计与实现背景:本实验所有结果基于Quartus II 13.1 (64-bit)实现,实验过程采⽤⾃下⽽上⽬录⼀、基本功能设计与思路基本功能:能实现秒、分钟、⼩时的计数,计数结果清晰稳定的显⽰在 6 位数码管上。

1、动态显⽰模块该模块主要功能是通过数码管的动态扫描实现 6 位数码管显⽰计数结果,本模块由扫描模块scan_cnt6,位选控制模块 dig_select,数据选择控制模块 seg_select 以及译码模块 decoder 构成扫描模块 scan_cnt6模块功能:产⽣ 位选控制端dig_select 和数据选择端 code_select 模块所需要的地址信息,扫描时钟决定位选信号和数据切换的速度。

设计思路:利⽤74390芯⽚(P160 TTL 双⼗进制异步计数器)构建⼀个模六计数器,就是6进制计数器,利⽤计数到6(110)时,“q2”和“q1”为⾼电平,产⽣ ⼀个复位信号,加到74390的⾼电平有效的异步清0端“1CLR”上,使计数器回0,从⽽实现模六计数。

设计结果:cnt6模块设计图波形仿真:(默认为时序仿真)cnt6模块波形仿真图位选模块 dig_select模块功能:在地址端的控制下,产⽣位选信号。

设计思路:利⽤74138芯⽚(3线-8线译码器),当选通端输⼊端G1为⾼电平,选通端输⼊端G2AN和G2BN为低电平时,将扫描信号cnt6的输出作为输⼊信号,dig[5..0]是译码输出,输出低电平有效。

设计结果:dig_select模块设计图波形仿真:dig_select模块波形仿真图数据选择模块 seg_select模块功能:输⼊ 6 组数据,每组数据 4bit,本模块完成在地址端的控制下从6 组数据当中选择 1 组输出。

设计思路:利⽤74151芯⽚(P91 8选1数据选择器),在控制输⼊端GN为低电平时,将扫描信号的选择下,分别选中D[5..0]对应的输⼊信号输出为Y。

基于FPGA多功能数字钟的设计

实验名称:基于FPGA的数字时钟设计一、实验目的:通过实验熟练运用Verilog HDL语言和 FPGA开发软件,使用BASYS2开发板设计一个可调式并且较复杂的数字时钟。

二、实验硬件要求:计算机、BASYS2开发板、蜂鸣器三、实验内容:1、电路功能:在ISE Design Suite 14.7软件开发环境下,使用Verilog描述语言、结合FPGA开发板编译和仿真数字时钟;要求时钟能进行基本的计时功能,按照:“时:分”来显示时间,秒的功能由流水灯表示;能引入秒脉冲进行校时、校分,并可用rst信号给清零;具有整点报时功能,当计时到整点的时候蜂鸣器开始鸣响,响声为乐曲“铃儿响叮当”。

2、电路图:3、Veilog 程序:1)分频模块div_clk:module divclk(sys_clk,rst,sec_clk);input sys_clk,rst;//系统时钟,复位output reg sec_clk;//秒时钟输出reg[27:0] cnt;//分频计数器,在人眼可识别范围之内always @(negedge sys_clk)beginif(rst)//对计数器进行复位begincnt <= 28'h0000000;sec_clk <= 1'b0;endelseif(cnt >= 28'h17d783f)begincnt <= 28'h0000000;sec_clk <= ~sec_clk;endelse cnt <= cnt+1'b1;endendmodule2)时钟计时模块clockmoduleclock(clk,rst,key,hor_h,hor_l,min_h,min_l,sec_h,sec_l,speak,sys_clk); input clk,rst,sys_clk;input [3:0]key;output [3:0]hor_h,hor_l,min_h,min_l,sec_h,sec_l;output speak;reg [3:0]hor_h,hor_l,min_h,min_l,sec_h,sec_l;reg speak;always@(posedge clk or posedge rst)beginif(rst)beginsec_h <=4'h0;sec_l <=4'h0;min_h <=4'h0;min_l <=4'h0;hor_h <=4'h0;hor_l <=4'h0;endelsecase(key)4'b1000:beginif(hor_h >= 4'h2)hor_h <= 4'h0;elsehor_h <= hor_h + 1'b1;end4'b0100:beginif(hor_l >= 4'h9||(hor_h >= 4'h2 && hor_l >= 4'h3)) hor_l <= 4'h0;elsehor_l <= hor_l + 1'b1;end4'b0010:beginif(min_h >= 4'h5)min_h <= 4'h0;elsemin_h <= min_h + 1'b1;end4'b0001:beginif(min_l >= 4'h9)min_l <= 4'h0;elsemin_l <= min_l + 1'b1;enddefault :beginif(sec_l >= 4'h9)beginsec_l <= 4'h0;if(sec_h >= 4'h5)beginsec_h <= 4'h0;if(min_l >= 4'h9)beginmin_l <= 4'h0;if(min_h >= 4'h5)beginmin_h <= 4'h0;if(hor_l >= 4'h9||(hor_h >= 4'h2 && hor_l >= 4'h3))beginhor_l <= 4'h0;if(hor_h >= 4'h2)hor_h <= 4'h0;elsehor_h <= hor_h + 1'b1;endelsehor_l <= hor_l + 1'b1;endelsemin_h <= min_h + 1'b1;endelsemin_l <= min_l + 1'b1;endelsesec_h <= sec_h + 1'b1;endelsesec_l <= sec_l + 1'b1;endendcaseendalways @(posedge clk)beginif(rst)speak <= 1'b0;else if(min_h == 4'h0 && min_l <=4'h0 && sec_h <= 4'h0)speak <= 1'b1;elsespeak <= 1'b0;endendmodule3)发声模块speaker:module speaker(clk,rst,en,f);input clk,rst,en;output reg f;reg [6:0] tonestep;reg [3:0] tonecode;reg [19:0] divcnt;reg [19:0] cntnum;reg sub_clk;reg[24:0] sub_cnt;always@(posedge clk)beginif(rst) beginsub_cnt <= 0;cntnum <= 0;divcnt <= 0;f <= 0;sub_clk <=0;endelse beginif(sub_cnt >=1500000)beginsub_clk <= ~sub_clk;sub_cnt <=0;endelse sub_cnt <= sub_cnt + 1'b1;if(en == 1'b1)begincase(tonecode)1:cntnum <= 95444;2:cntnum <= 85052;3:cntnum <= 75750;4:cntnum <= 71625;5:cntnum <= 63775;6:cntnum <= 56825;7:cntnum <= 50600;default : cntnum <= 0;endcaseif(cntnum == 0)f <= 1'b0;elseif(divcnt >= cntnum)begindivcnt <= 0;f <= ~f;endelse divcnt <= divcnt + 1'b1;endendendalways@(posedge sub_clk)beginif(rst)begintonestep <= 0;tonecode <= 0;endelseif(tonestep <=80)tonestep <= tonestep + 1'b1;else tonestep <= 0;case(tonestep)7'b0000000:tonecode <= 3;7'b0000001:tonecode <= 3;7'b0000010:tonecode <= 8;7'b0000011:tonecode <= 3;7'b0000100:tonecode <= 3;7'b0000101:tonecode <= 8;7'b0000110:tonecode <= 8;7'b0000111:tonecode <= 3;7'b0001000:tonecode <= 3;7'b0001001:tonecode <= 3;7'b0001010:tonecode <= 3;7'b0001011:tonecode <= 8;7'b0001100:tonecode <= 8;7'b0001101:tonecode <= 3;7'b0001110:tonecode <= 3;7'b0001111:tonecode <= 8;7'b0010000:tonecode <= 3;7'b0010001:tonecode <= 3;7'b0010010:tonecode <= 8;7'b0010011:tonecode <= 8;7'b0010101:tonecode <= 3; 7'b0010110:tonecode <= 3; 7'b0010111:tonecode <= 3; 7'b0011000:tonecode <= 8; 7'b0011001:tonecode <= 8; 7'b0011010:tonecode <= 3; 7'b0011011:tonecode <= 3; 7'b0011100:tonecode <= 8; 7'b0011101:tonecode <= 5; 7'b0011110:tonecode <= 5; 7'b0011111:tonecode <= 8; 7'b0100000:tonecode <= 8; 7'b0100001:tonecode <= 1; 7'b0100010:tonecode <= 1; 7'b0100011:tonecode <= 8; 7'b0100100:tonecode <= 2; 7'b0100101:tonecode <= 2; 7'b0100110:tonecode <= 8; 7'b0100111:tonecode <= 8; 7'b0101000:tonecode <= 3; 7'b0101001:tonecode <= 3; 7'b0101010:tonecode <= 3; 7'b0101011:tonecode <= 3; 7'b0101100:tonecode <= 8; 7'b0101101:tonecode <= 8; 7'b0101110:tonecode <= 4; 7'b0101111:tonecode <= 4; 7'b0110000:tonecode <= 8; 7'b0110001:tonecode <= 4; 7'b0110010:tonecode <= 4;7'b0110100:tonecode <= 8; 7'b0110101:tonecode <= 4; 7'b0110110:tonecode <= 4; 7'b0110111:tonecode <= 4; 7'b0111000:tonecode <= 8; 7'b0111001:tonecode <= 4; 7'b0111010:tonecode <= 8; 7'b0111011:tonecode <= 8; 7'b0111100:tonecode <= 4; 7'b0111101:tonecode <= 4; 7'b0111110:tonecode <= 8; 7'b0111111:tonecode <= 3; 7'b1000000:tonecode <= 3; 7'b1000001:tonecode <= 8; 7'b1000010:tonecode <= 8; 7'b1000011:tonecode <= 3; 7'b1000100:tonecode <= 3; 7'b1000101:tonecode <= 3; 7'b1000110:tonecode <= 8; 7'b1000111:tonecode <= 3; 7'b1001000:tonecode <= 8; 7'b1001001:tonecode <= 3; 7'b1001010:tonecode <= 8; 7'b1001011:tonecode <= 5; 7'b1001100:tonecode <= 5; 7'b1001101:tonecode <= 8; 7'b1001110:tonecode <= 5; 7'b1001111:tonecode <= 5; 7'b1010000:tonecode <= 8; 7'b1000001:tonecode <= 8;7'b1000010:tonecode <= 4;7'b1000011:tonecode <= 4;7'b1000100:tonecode <= 8;7'b1000101:tonecode <= 2;7'b1000110:tonecode <= 2;7'b1000111:tonecode <= 8;7'b1001000:tonecode <= 8;7'b1001001:tonecode <= 1;7'b1001010:tonecode <= 1;7'b1001011:tonecode <= 1;7'b1001100:tonecode <= 1;7'b1001101:tonecode <= 8;7'b1001110:tonecode <= 8;7'b1001111:tonecode <= 5;7'b1010000:tonecode <= 5;7'b1010001:tonecode <= 8;7'b1010010:tonecode <= 3;7'b1010011:tonecode <= 3;7'b1010100:tonecode <= 8;7'b1010101:tonecode <= 8;7'b1010110:tonecode <= 2;7'b1010111:tonecode <= 2;7'b1011000:tonecode <= 8;7'b1011001:tonecode <= 1;7'b1011010:tonecode <= 1;7'b1011011:tonecode <= 8;7'b1011100:tonecode <= 8;endcaseendendmodule4)数码管显示模块seg:module seg(q,ctr,h_h,h_l,m_h,m_l,clk,rst);output[6:0]q;output[3:0] ctr;input[3:0] h_h,h_l,m_h,m_l;input clk,rst;reg[6:0] q;reg[25:0] count;reg[3:0] temp;reg[3:0] scan;always @ (posedge clk)beginif (rst)begincount = 0;endelsebegincount = count +1;endendalways @ (posedge clk ) //Seg Scanbeginif(rst)beginscan<=4'b0000;endelsecase(count[11:10]) // 执行设计时将扫描频率改回 2'b00: scan<=4'b0111;2'b01: scan<=4'b1011;2'b10: scan<=4'b1101;2'b11: scan<=4'b1110;endcaseendassign ctr = scan;always @ (posedge clk) //Seg Scanbeginif(rst)begintemp<=4'b0000;endelsecase(count[11:10]) // 执行设计时将扫描频率改回 2'b00: temp<=h_h;2'b01: temp<=h_l;2'b10: temp<=m_h;2'b11: temp<=m_l;endcaseendalways @(posedge clk) //数码管译码beginif(rst)beginq<=7'b0000000;endelsecase(temp)4'd0:q<=7'b0000001; //04'd1:q<=7'b1001111; //14'd2:q<=7'b0010010; //24'd3:q<=7'b0000110; //34'd4:q<=7'b1001100; //44'd5:q<=7'b0100100; //54'd6:q<=7'b0100000; //64'd7:q<=7'b0001111; //74'd8:q<=7'b0000000; //84'd9:q<=7'b0000100; //9default:q<=7'b0000001;endcaseendendmodule5)秒计时流水灯模块sec_ledmodule sec_led(input sys_clk,input rst,output [7:0] led);reg[24:0] cnt;reg[7:0] led_reg;always@(posedge sys_clk)beginif(rst)cnt <= 0;else cnt <= cnt+1;endalways@(posedge sys_clk)beginif(rst)led_reg <= 8'b0000_0001;else if (cnt == 25'd4*******)beginled_reg <= led_reg << 1;if(led_reg==8'b1000_0000)led_reg<=8'b0000_0001;endassign led=led_reg;Endmodule6键盘修改模块:module keyboard(input sys_clk,// input rst_n,input ps2_clk,input ps2_data,output reg[3:0] key_val);wire [15:0]xkey;reg ps2cf,ps2df;reg clk25=0;reg [7:0]ps2c_filter,ps2d_filter;reg [10:0]shift1,shift2;assign xkey={shift2[8:1],shift1[8:1]};assign rst_n=1;always@(posedge sys_clk)clk25=~clk25;always@(posedge clk25 or negedge rst_n) beginif(!rst_n)beginps2c_filter<=0;ps2d_filter<=0;ps2cf<=1;ps2df<=1;endelsebeginps2c_filter[7]<=ps2_clk;ps2c_filter[6:0]<=ps2c_filter[7:1];ps2d_filter[7]<=ps2_data;ps2d_filter[6:0]<=ps2c_filter[7:1];if(ps2c_filter==8'b1111_1111)ps2cf<=1;elseif(ps2c_filter==8'b0000_0000)ps2cf<=0;if(ps2d_filter==8'b1111_1111)ps2df<=1;elseif(ps2d_filter==8'b0000_0000)ps2df<=0;endendalways@(negedge ps2cf or negedge rst_n)beginif(!rst_n)beginshift1<=0;shift2<=1;endelsebeginshift1<={ps2df,shift1[10:1]};shift2<={shift1[0],shift2[10:1]};endendparameterone = 16'b0001_0110_0001_0110,//{16,16},two = 16'b0001_1110_0001_1110,//{1e,1e},three = 16'b0010_0110_0010_0110,//{26,26},four = 16'b0010_0101_0010_0101,//{25,25},onen = 16'b1111_0000_0001_0110,//{F0,16},twon = 16'b1111_0000_0001_1110,//{F0,1E},threen = 16'b1111_0000_0010_0110,//{F0,26},fourn = 16'b1111_0000_0010_0101;//{F0,25};always@(xkey)case(xkey)one:key_val<=4'b1000;two:key_val<=4'b0100;three:key_val<=4'b0010;four:key_val<=4'b0001;onen:key_val<=4'b0000;twon:key_val<=4'b0000;threen:key_val<=4'b0000;fourn:key_val<=4'b0000;default:key_val<=4'b0000;endcaseendmodulemodule keyboard(input sys_clk,// input rst_n,input ps2_clk,input ps2_data,output reg[3:0] key_val);wire [15:0]xkey;reg ps2cf,ps2df;reg clk25=0;reg [7:0]ps2c_filter,ps2d_filter;reg [10:0]shift1,shift2;assign xkey={shift2[8:1],shift1[8:1]};assign rst_n=1;always@(posedge sys_clk)clk25=~clk25;always@(posedge clk25 or negedge rst_n)beginif(!rst_n)beginps2c_filter<=0;ps2d_filter<=0;ps2cf<=1;ps2df<=1;endelsebeginps2c_filter[7]<=ps2_clk;ps2c_filter[6:0]<=ps2c_filter[7:1];ps2d_filter[7]<=ps2_data;ps2d_filter[6:0]<=ps2c_filter[7:1];if(ps2c_filter==8'b1111_1111)ps2cf<=1;elseif(ps2c_filter==8'b0000_0000)ps2cf<=0;if(ps2d_filter==8'b1111_1111)ps2df<=1;elseif(ps2d_filter==8'b0000_0000)ps2df<=0;endendalways@(negedge ps2cf or negedge rst_n)beginif(!rst_n)beginshift1<=0;shift2<=1;endelsebeginshift1<={ps2df,shift1[10:1]};shift2<={shift1[0],shift2[10:1]};endendparameterone = 16'b0001_0110_0001_0110,//{16,16},two = 16'b0001_1110_0001_1110,//{1e,1e},three = 16'b0010_0110_0010_0110,//{26,26},four = 16'b0010_0101_0010_0101,//{25,25},onen = 16'b1111_0000_0001_0110,//{F0,16},twon = 16'b1111_0000_0001_1110,//{F0,1E},threen = 16'b1111_0000_0010_0110,//{F0,26},fourn = 16'b1111_0000_0010_0101;//{F0,25};always@(xkey)case(xkey)one:key_val<=4'b1000;two:key_val<=4'b0100;three:key_val<=4'b0010;four:key_val<=4'b0001;onen:key_val<=4'b0000;twon:key_val<=4'b0000;threen:key_val<=4'b0000;fourn:key_val<=4'b0000;default:key_val<=4'b0000;endcaseendmodule4、仿真波形图和波形解释:(1)、仿真波形图:(2)、波形解释:将系统的50Mhz的时钟频率进行分频为1hz的频率。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

摘要伴随着集成电路技术的发展, 电子设计自动化(EDA)技术逐渐成为数字电路设计的重要手段。

基于FPGA的EDA技术的发展和应用领域的扩大与深入,使得EDA技术在电子信息,通信,自动控制,计算机等领域的重要性日益突出。

本设计给出了一种基于FPGA的多功能数字钟方法,采用EDA作为开发工具,VHDL语言和图形输入为硬件描述语言,QuartusII作为运行程序的平台,编写的程序经过调试运行,波形仿真验证,下载到EDA实验箱的FPGA芯片,实现了设计目标。

系统主芯片采用CycloneII系列EP2C35F672C8。

采用自顶向下的设计思想,将系统分为五个模块:分频模块、计时模块、报时模块、显示模块、顶层模块。

用VHDL语言实现各个功能模块, 图形输入法生成顶层模块. 最后用QuartusII 软件进行功能仿真, 验证数字钟设计的正确性。

测试结果表明本设计实现了一个多功能的数字钟功能,具有时、分、秒计时显示功能,以24小时循环计时;具有校正小时和分钟的功能;以及清零,整点报时功能。

关键词:EDA技术;FPGA;数字钟;VHDL语言;自顶向下AbstractAccompanied by the development of integrated circuit technology, electro nic design automation (EDA) technology is becoming an important means of digital circuit design. FPGA EDA technology development and expansion of a pplication fields and in-depth, the importance of EDA technology in the field of electronic information, communication, automatic control, computer, etc. hav e become increasingly prominent.This design gives a FPGA-based multifunctional digital clock using ED A as a development tool, VHDL language and graphical input hardware descri ption language, the QuartusII as a platform for running the program, written procedures debugging and running, the waveform simulation downloaded to th e FPGA chip to achieve the design goals.The main system chip CycloneII series EP2C35F672C8. Adopted a topdw n design ideas, the system is divided into five modules: frequency module, ti ming module, timer module, display module, the top-level module. With VHD L various functional modules, graphical input method to generate the top-level module. Last QuartusII under simulation, to verify the correctness of the digi tal clock design.The test results show that the design of a multifunctional digital clock, with seconds time display, 24-hour cycle timing; has a school, cleared, and th e whole point timekeeping functions.Key words: EDA technology; FPGA; VHDL language; top-down; digital cloc k目录1 绪论 (4)1.1 研究背景 (4)1.2 研究目的 (5)1.3 研究方法和内容 (5)2 本软件开发环境 (5)2.1 FPGA简介 (5)2.1 .1 FPGA概述 (6)2.1.2 FPGA基本结构 (6)图2-1 CLB基本结构 (8)2.1.3 FPGA系统设计流程 (8)2.1.4 FPGA开发编程原理 (10)2.2 QuartusII设计平台 (10)2.2.1 软件开发环境及基本流程 (10)2.2.2 软件的具体设计流程 (11)3总体设计方案 (12)3.1 数字钟的硬件构成原理 (12)3.2 软件设计的功能框图和流程框图 (13)4 软件设计与功能实现 (15)4.1 分频模块功能的软件设计与实现 (15)4.2 计时校时模块功能的软件设计与实现 (16)4.3 整点报时模块功能的软件设计与实现 (17)4.4 扫描译码显示模块功能的软件设计与实现 (17)4.5 顶层模块功能的软件设计与实现 (18)5 系统功能调试及分析 (18)6 结论及展望 (19)6.1 结论 (19)6.2 展望 (20)参考文献 (22)附录 (23)基于FPGA的数字钟设计1 绪论现代社会的标志之一就是信息产品的广泛使用,而且是产品的性能越来越强,复杂程度越来越高,更新步伐越来越快。

支撑信息电子产品高速发展的基础就是微电子制造工艺水平的提高和电子产品设计开发技术的发展。

前者以微细加工技术为代表,而后者的代表就是电子设计自动化(electronic design automatic,EDA)技术。

ASIC是专用的系统集成电路,是一种带有逻辑处理的加速处理器。

而FPGA是特殊的ASIC芯片,与其他的ASIC芯片相比,它具有设计开发周期短、设计制造成本低、开发工具先进、标准产品无需测试、质量稳定以及可实时在线检测等优点。

本设计采用的VHDL语言是一种全方位的硬件描述语言,具有极强的描述能力,能支持系统行为级、寄存器传输级和逻辑门级三个不同层次的设计;支持结构、数据流、行为三种描述形式的混合描述、覆盖面广、抽象能力强,因此在实际应用中越来越广泛。

数字化的钟表给人们带来了极大的方便。

近些年,随着科技的发展和社会的进步,人们对数字钟的要求也越来越高,传统的时钟已不能满足人们的需求。

多功能数字钟不管在性能还是在样式上都发生了质的变化,有电子闹钟、数字闹钟等等。

而基于FPGA的数字钟设计能极大的扩展其功能。

1.1 研究背景当今电子产品正向功能多元化,体积最小化,功耗最低化的方向发展。

它与传统的电子产品在设计上的显著区别是大量使用大规模可编程逻辑器件,使产品的性能提高,体积缩小,功耗降低。

同时广泛运用现代计算机技术,提高产品的自动化程度和竞争力,缩短研发周期。

EDA技术正是为了适应现代电子技术的要求,吸收众多学科最新科技成果而形成的一门新技术。

EDA是电子设计自动化(Elcctronic Design Automation)的缩写,是90年代初从CAD(计算机辅助设备),CAM(计算机辅助制造),CAT(计算机辅助测试)和CAE(计算机辅助工程)的概念发展而来的。

EDA技术是以计算机为工具,根据硬件描述语言VHDL完成设计文件,自动的完成逻辑编译,化简,分割,综合及优化,布局布线,仿真以及对特定目标芯片的适配编译和编程下载等工作。

典型的EDA工具中必须包含两个特殊的软件包,即综合器和适配器,综合器的功能就是将设计者在EDA平台上完成的针对某个系统项目的VHDL 原理图或状态图形描述,针对给定的硬件系统组件,进行编译,优化,转换和综合,最终获得我们将实现的功能的描述文件。

综合器在工作前,必须给定要实现的硬件结构参数,它的功能就是将软件描述与给定的硬件结构用一定的方式联系起来,也就是说综合器是软件描述与硬件实现的一座桥梁。

综合过程就是将电路的高级语言描述转换成低级的,可与目标器件CPLD相映射的网表文件。

适配器的功能是将由综合器产生的网表文件配置与指定的目标器件中,产生最终的下载文件。

适配器所选的目标器件(CPLD芯片)必须包含于在综合器中已指定的目标器件系列。

本次数字钟设计利用VHDL硬件描述语言和图形输入相结合的编程方式,并通过可编程逻辑器件FPGA进行硬件设计,用LED数码管动态显示计时结果。

数字钟可以由各种技术实现,如单片机等。

利用可编程逻辑器件具有其他方式没有的特点,它具有成功率高,理论与实践结合紧密,体积小,容量大,I/O口丰富,易编程和加密等特点,并且它还具有开放的界面,丰富的设计库,模块化的工具等优良性能,应用非常方便。

因此,本设计采用可编程逻辑器件FPGA 来实现。

1.2 研究目的现在是一个知识爆炸的新时代。

新产品、新技术层出不穷,电子技术的发展更是日新月异。

可以说,电子技术的应用无处不在,电子技术正在不断地改变我们的生活,改变着我们的世界。

钟表的数字化给人们生产生活带来了极大的方便,而且大大地扩展了钟表原先的报时功能。

诸如定时自动报警、定时启闭电路、定时开关烘箱、通断动力设备,甚至各种定时电气的自动启用等,所有这些,都是以钟表数字化为基础的。

因此,研究数字钟及扩大其应用,有着非常现实的意义。

1.3 研究方法和内容本设计主要研究基于FPGA的数字钟,采用EDA作为开发工具,VHDL语言和图形输入为硬件描述语言,采用自顶向下的设计思想,QuartusII软件作为运行程序的平台。

设计的数字钟时间以24小时为一个周期,用LED数码管动态显示时、分、秒。

具有清零和整点报时功能,可以对小时,分钟进行单独校对,使其校正到标准时间。

校对时间由按键进行控制,为了保证计时的稳定及准确,须由晶体振荡器提供时间基准信号并经分频得到。

2 本软件开发环境2.1 FPGA简介2.1 .1 FPGA概述FPGA是现场可编程门阵列(Field Programmable Gate Array)的简称,与之相应的CPLD是复杂可编程逻辑器件(Complex Programmable Logic Device)的简称,两者的功能基本相同,只是实现原理略有不同,有时可以忽略这两者的区别,统称为可编程逻辑器件CPLD/FPGA。