EDA实验指导简述基于FPGA的动态扫描电路设计

基于FPGA的EDA开放性实验项目

文档从互联网中收集,已重新修正排版,word格式支持编辑,如有帮助欢迎下载支持。

毕业设计 [论文]题目:基于FPGA的EDA开放性实验项目设计与研究学院:电气与信息工程学院专业:电子信息工程姓名:党俊博学号:0指导老师:梁成武完成时间:2013年5月24日摘要培养大批应用型、技术型人才是我国本科教育的目标。

实验教学是理论联系实际的重要环节,对培养学生的技术应用能力、创新能力具有不可替代的作用。

而先进的实验教学不仅需要基础实验,更需要一本好的开放性实验指导书。

EDA 是电子类专业重要的一门专业基础课,具有较强的实践性。

本论文针对我校学生学习特点,设计了九个具有代表性的实用开放性实践项目,以满足学生对开放性实验的需求。

本论文介绍了常用数字电路的设计原理和方法,内容涉及到控制类、仪器仪表类、小游戏类、嵌入式处理器等实验项目,重点讲述电路的设计原理、FPGA内部功能模块电路划分及VHDL代码描述。

该实验指导书基本满足我校电子信息工程专业对开放性实验的需求,通过实践项目的学习,可以达到锻炼学生的动手操作、扩展电路、软硬件结合以及实验仿真等教学目的。

关键词:EDA,开放性实验, Quartus II,NIOS II, FPGAABSTRACTA large number of application-oriented training, technical talent is the goal of undergraduate education. Experimental teaching is an important link theory with practice, to cultivate the students' ability to apply technology, innovation has an irreplaceable role. And advanced experimental teaching requires not only basic experiments, but also need a good guide book open experiment. EDA is an electronic specialty important a basic course, with a strong practical. In this thesis, I am learning characteristics of students, the design of nine representative practical open practice programs to meet students' needs for open experiment.This paper describes the commonly used digital circuit design principles and methods, which relates to the control, instrumentation class, small game category, embedded processors and other experimental projects focuses on circuit design principles, FPGA internal function modules and VHDL circuit partitioning code Description. The experimental guide book basically meet my school electronic information engineering requirements for open experiment, learning through practical projects, you can reach the students hands-on training, expansion of the circuit, hardware and software as well as experimental simulation teaching purposes.Keywords:EDA, open experiment, Quartus II, NIOS II, FPGA目录摘要..................................................................................................................错误!未定义书签。

EDA实验指导 基于FPGA的动态扫描电路设计new

FPGA实验指导及记录实验三基于FPGA的数码管动态扫描电路设计1.实验目的:(1)掌握FPGA工作的基本原理、FPGA硬件平台的使用;(2)熟悉7段数码管显示译码电路的设计。

(3)掌握数码管动态扫描显示原理及动态扫描电路的设计。

2.实验任务:利用FPGA硬件平台上的6位数码管动态显示计数器输出数据。

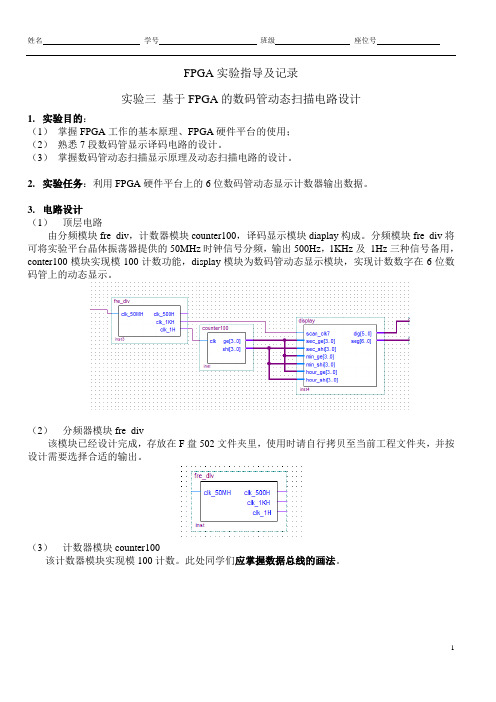

3.电路设计(1)顶层电路由分频模块fre_div,计数器模块counter100,译码显示模块diaplay构成。

分频模块fre_div将可将实验平台晶体振荡器提供的50MHz时钟信号分频,输出500Hz,1KHz及1Hz三种信号备用,conter100模块实现模100计数功能,display模块为数码管动态显示模块,实现计数数字在6位数码管上的动态显示。

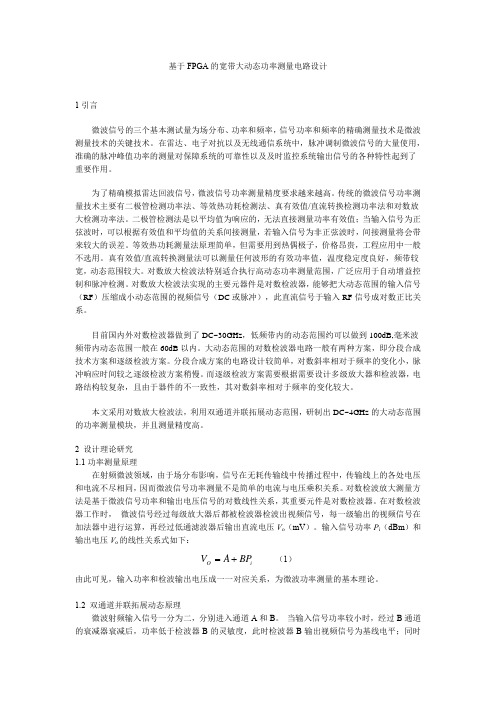

(2)分频器模块fre_div该模块已经设计完成,存放在F盘502文件夹里,使用时请自行拷贝至当前工程文件夹,并按设计需要选择合适的输出。

(3)计数器模块counter100该计数器模块实现模100计数。

此处同学们应掌握数据总线的画法。

(4)译码显示模块display该模块由counter6模块,dig_select模块,seg_select模块以及decoder模块构成,请同学们自行完成该模块总体设计,当display模块的输入信号scanclk频率为1KHz时,数码管扫描周期为36ms,每次扫描每位数码管显示时长6ms。

各子模块设计思路如下。

a)counter6模块该模块需使用74390设计一个模6的计数器。

请在空白处做预设计,画出电路图。

b)dig_select模块该模块用于选择6位数码管中的某一位显示相应字形。

74138为3-8译码器,功能表见附录。

c)decoder模块可将4位8421BCD码译为七段码,驱动数码管以十进制数形式显示数字。

7448为共阴极数码管译码器,功能表见附录。

d)seg_select模块该模块功能是从6组4bit信号中选择一组作输出。

基于EDA技术的FPGA设计

基于EDA技术的FPGA设计对传统电子系统设计方法与现代电子系统设计方法进行了比拟,引出了基于EDA技术的现场可编程门阵列(FPGA)电路,提出现场可编程门阵列(FPGA)是近年来迅速开展的大规模可编程专用集成电路(ASIC),在数字系统设计和控制电路中越来越受到重视。

介绍了这种电路的根本结构、性能特点、应用领域及使用中的考前须知。

对基于EDA技术的FPGA进行了展望。

指出EDA技术将是未来电子产品设计技术开展的主要方向。

集成电路技术和计算机技术的蓬勃开展,让电子产品设计有了更好的应用市场,实现方法也有了更多的选择。

传统电子产品设计方案是一种基于电路板的设计方法,该方法需要选用大量的固定功能器件,然后通过这些器件的配合设计从而模拟电子产品的功能,其工作集中在器件的选用及电路板的设计上。

随着计算机性价比的提高及可编程逻辑器件的出现,对传统的数字电子系统设计方法进行了解放性的革命,现代电子系统设计方法是设计师自己设计芯片来实现电子系统的功能,将传统的固件选用及电路板设计工作放在芯片设计中进行。

从20世纪90年代初开始,电子产品设计系统日趋数字化、复杂化和大规模集成化,各种电子系统的设计软件应运而生。

在这些专业化软件中,EDA(ElectronicDesignAutomation)具有一定的代表性,EDA技术是一种基于芯片的现代电子系统设计方法。

它的优势主要集中在能用HDL语言进行输入、进行PLD(可编程器件)的设计与仿真等系统设计自动化上;20世纪90年末,可编程器件又出现了模拟可编程器件,由于受技术、可操作性及性价比的影响,今后EDA技术会向模拟可编程器件的设计与仿真方向开展,并占据市场的一定份额。

EDA技术主要包括大规模可编程逻辑器件、硬件描述语言、开发软件工具及实验开发系统4个方面。

其中,大规模可编程逻辑器件是利用EDA技术进行电子系统设计的载体硬件,描述语言是利用EDA技术进行电子系统设计的主要表达手段,开发软件工具是利用EDA技术进行电子系统设计的智能化与自动化设计工具,实验开发系统那么是提供芯片下载电路及EDA实验、开发的外围资源。

基于FPGA的宽带大动态功率测量电路设计v1

基于FPGA 的宽带大动态功率测量电路设计1引言微波信号的三个基本测试量为场分布、功率和频率,信号功率和频率的精确测量技术是微波测量技术的关键技术。

在雷达、电子对抗以及无线通信系统中,脉冲调制微波信号的大量使用,准确的脉冲峰值功率的测量对保障系统的可靠性以及及时监控系统输出信号的各种特性起到了重要作用。

为了精确模拟雷达回波信号,微波信号功率测量精度要求越来越高。

传统的微波信号功率测量技术主要有二极管检测功率法、等效热功耗检测法、真有效值/直流转换检测功率法和对数放大检测功率法。

二极管检测法是以平均值为响应的,无法直接测量功率有效值;当输入信号为正弦波时,可以根据有效值和平均值的关系间接测量,若输入信号为非正弦波时,间接测量将会带来较大的误差。

等效热功耗测量法原理简单,但需要用到热偶极子,价格昂贵,工程应用中一般不选用。

真有效值/直流转换测量法可以测量任何波形的有效功率值,温度稳定度良好,频带较宽,动态范围较大。

对数放大检波法特别适合执行高动态功率测量范围,广泛应用于自动增益控制和脉冲检测。

对数放大检波法实现的主要元器件是对数检波器,能够把大动态范围的输入信号(RF )压缩成小动态范围的视频信号(DC 或脉冲),此直流信号于输入RF 信号成对数正比关系。

目前国内外对数检波器做到了DC~30GHz ,低频带内的动态范围约可以做到100dB,毫米波频带内动态范围一般在60dB 以内。

大动态范围的对数检波器电路一般有两种方案,即分段合成技术方案和逐级检波方案。

分段合成方案的电路设计较简单,对数斜率相对于频率的变化小,脉冲响应时间较之逐级检波方案稍慢。

而逐级检波方案需要根据需要设计多级放大器和检波器,电路结构较复杂,且由于器件的不一致性,其对数斜率相对于频率的变化较大。

本文采用对数放大检波法,利用双通道并联拓展动态范围,研制出DC~4GHz 的大动态范围的功率测量模块,并且测量精度高。

2 设计理论研究1.1功率测量原理在射频微波领域,由于场分布影响,信号在无耗传输线中传播过程中,传输线上的各处电压和电流不尽相同,因而微波信号功率测量不是简单的电流与电压乘积关系。

eda技术fpga课程设计

eda技术fpga课程设计一、教学目标本课程旨在通过FPGA设计原理与实践,让学生掌握FPGA的基本知识和应用技能,培养EDA技术应用型人才。

知识目标:使学生了解FPGA的硬件结构和基本工作原理,掌握FPGA的配置和编程方法,理解并应用常见的EDA工具。

技能目标:培养学生使用EDA工具进行FPGA设计的能力,包括逻辑设计、综合、布局布线等,以及能够进行简单的FPGA系统开发。

情感态度价值观目标:培养学生对EDA技术和FPGA应用的兴趣,激发学生的创新意识和实践能力,培养学生团队协作和解决问题的能力。

二、教学内容本课程的教学内容主要包括FPGA基本原理、EDA工具使用、FPGA设计与应用等。

第一部分:FPGA基本原理,包括FPGA的硬件结构、工作原理和配置方法。

第二部分:EDA工具使用,包括FPGA逻辑设计、综合、布局布线等基本操作。

第三部分:FPGA设计与应用,包括数字信号处理、数字逻辑设计、嵌入式系统设计等。

三、教学方法为了提高学生的学习兴趣和主动性,本课程将采用讲授法、案例分析法、实验法等多种教学方法。

讲授法:用于向学生传授FPGA基本原理和EDA工具使用方法。

案例分析法:通过分析实际案例,让学生了解FPGA在实际应用中的重要作用。

实验法:让学生亲自动手进行FPGA设计,培养其实际操作能力。

四、教学资源为了支持教学内容和教学方法的实施,我们将准备以下教学资源:教材:选用经典的FPGA教材,为学生提供系统性的理论知识。

参考书:提供相关的FPGA设计和应用方面的参考书籍,丰富学生的知识面。

多媒体资料:制作PPT、视频等教学资料,提高学生的学习兴趣。

实验设备:准备FPGA开发板和相关的实验设备,让学生能够进行实际操作。

五、教学评估本课程的评估方式包括平时表现、作业、考试等,以全面客观地评价学生的学习成果。

平时表现:通过观察学生在课堂上的参与程度、提问回答等情况,评估其学习态度和理解能力。

作业:布置相关的FPGA设计和应用作业,评估学生对课程内容的理解和应用能力。

《基于fpga按键动态显示设计 》实践报告

《基于fpga按键动态显示设计》实践报告本实践报告旨在介绍基于FPGA按键动态显示的设计。

FPGA是现代数字电路设计中常用的可编程逻辑器件,具有高度的灵活性和可重构性。

本设计主要利用FPGA实现按键输入的检测和动态显示的功能,使用户可以通过按键来控制显示内容的变化。

首先,我们需要了解FPGA的基本原理和使用方法。

FPGA由可编程逻辑单元、存储单元、时钟单元等组成,可以根据用户需求进行编程,实现不同的功能。

在本设计中,我们采用Xilinx公司的FPGA芯片作为开发板,通过Vivado软件进行设计和编程。

接着,我们详细介绍了按键动态显示的实现方法。

首先,通过FPGA芯片进行按键输入的检测,判断用户是否按下了某个按键。

然后,根据按键的状态来改变显示内容,实现动态显示的效果。

具体实现过程中,我们采用了状态机的设计方法,将按键输入和显示输出分别作为状态机的输入和输出。

最后,我们进行了实验验证,测试了按键动态显示的功能和效果。

实验结果表明,本设计可以实现按键输入的检测和动态显示的功能,具有较好的实用性和稳定性。

综上所述,本实践报告介绍了基于FPGA按键动态显示的设计方法和实现过程,为数字电路设计爱好者提供了一种实用的设计方案。

- 1 -。

基于eda软件fpga设计流程

基于eda软件fpga设计流程下载温馨提示:该文档是我店铺精心编制而成,希望大家下载以后,能够帮助大家解决实际的问题。

文档下载后可定制随意修改,请根据实际需要进行相应的调整和使用,谢谢!并且,本店铺为大家提供各种各样类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,如想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by theeditor. I hope that after you download them,they can help yousolve practical problems. The document can be customized andmodified after downloading,please adjust and use it according toactual needs, thank you!In addition, our shop provides you with various types ofpractical materials,such as educational essays, diaryappreciation,sentence excerpts,ancient poems,classic articles,topic composition,work summary,word parsing,copy excerpts,other materials and so on,want to know different data formats andwriting methods,please pay attention!基于 EDA 软件的 FPGA 设计流程一般包括以下步骤:1. 设计规划确定设计目标和功能需求。

基于FPGA的动态轨道衡硬件电路设计

基于FPGA的动态轨道衡硬件电路设计1 引言动态轨道衡是一种对运行中的列车(标准四轴货车)进行自动称重的计量设备,是集传感器技术、微电子技术、计算机控制及测试技术、机械制造自动化技术、物料输送和管理技术等为一体的综合技术,是现代称重计量和控制系统工程的重要技术基础。

应用电子称重技术开发的电子称重系统,具有广阔的应用领域和较强的渗透性,同其它高技术产业一样,电子衡器产业也是国家经济和科学竞争的重要组成部分之一[1]。

电子定量包装秤是电子称重技术在定量系统中的具体应用,是将机械、电气、电子、计算机、自动控制与衡器等融为一体的智能机电结合计量设备。

它是一种按照事先设计的方法和程序,将大宗颗粒物料分成预定质量的小份载荷形式的自动称量设备。

其技术原理是称重台面将列车重量传递至传感器,传感器将重量转换为电压信号,模/数转换系统将电压信号转换为数字信号,再由计算机处理,得出每节车重量、速度,从而实现对货物列车的自动称重[2]。

2 动态轨道衡的设计方案2.1 动态轨道衡硬件组成原理图表的标注:图片标注在下方,现在的动态轨道衡基本上以电子式为主,电子式动态轨道衡由承重台、称重传感器、称重显示控制器等组成。

承重台是支承货物列车的平台;称重传感器将重量信号转变成便于测试的电信号;称重显示控制器的核是微处理器,并包括信号放大、滤波、A/D 转换、显示、串行通讯等模块,可将称重值存储并显示。

有的动态轨道衡配在上位机,可将称重显示控制器的称重信号传递到上位机上,便于远程监控和管理[3]。

动态轨道衡硬件组成原理如所示。

2.2 数据采集模块电路设计动态轨道衡的称重流程如下:首先,载有货物的火车经过轨道衡,由传感器采集压力信号,再经过硬件电路处理,即数据采集模块;其次,将数据采集模块出来的信号经过传输到达数据处理分析模块,对采集的信号进行分析与处理,再次,将该信号保存,换算成重量信息进行显示、保存或打印;最后,结束称重。

称重流程见所示。

eda课程设计基于fpga秒表电路设计

一、概述EDA(Electronics Design Automation)是电子设计自动化的缩写,是一种利用计算机技术对电子系统进行设计的方法。

FPGA(Field Programmable Gate Array)是一种可编程逻辑器件,可以根据设计要求对硬件电路进行重新编程。

秒表电路是一种常见的数字电路,可以用于测量时间间隔。

本篇文章将基于EDA课程设计,利用FPGA进行秒表电路设计的研究和探讨。

二、背景知识在进行本课程设计之前,需要了解以下一些基本的背景知识:1. EDA技术:EDA技术是一种利用计算机辅助进行电子设计的方法,包括了电路仿真、综合、布局布线等一系列的设计流程。

在本课程设计中,将会使用EDA技术来进行秒表电路的设计和验证。

2. FPGA技术:FPGA是一种可编程的逻辑器件,可以根据设计的需要进行重编程,灵活性很高。

在本课程设计中,将会使用FPGA来实现秒表电路的硬件设计。

3. 秒表电路:秒表电路是一种数字电路,可以用来实现时间的计时和显示功能。

在本课程设计中,将会对秒表电路的设计进行详细讨论。

三、课程设计目标本课程设计的主要目标是使用EDA技术和FPGA技术,设计并验证一个基于FPGA的秒表电路。

具体目标包括:1. 学习和掌握EDA软件的使用方法,包括电路设计、仿真验证等功能。

2. 熟悉FPGA的工作原理和编程方法,能够进行FPGA的硬件设计。

3. 设计并验证一个完整的秒表电路,包括计时功能、显示功能等。

四、课程设计步骤本课程设计将分为以下几个步骤进行:1. 学习EDA软件的基本操作:首先需要学习和掌握EDA软件的基本操作方法,包括电路设计、综合、布局布线、仿真验证等功能。

这一步是为了为后续的秒表电路设计和验证做好准备。

2. 学习FPGA的编程方法:其次需要了解FPGA的工作原理和编程方法,包括FPGA的硬件描述语言、开发工具的使用等。

这一步是为了进行秒表电路的硬件设计做好准备。

EDA 技术:EDA实验3 扫描显示电路设计

下载步骤 2、选择start按钮,如果有错,检查电缆是否 连接正确。

注意: 由于本实验箱没有配置器件,每次重 新上电后必须要重新下载!!!

4、根据连接的引脚进行管脚分配(Assign\pin)

5、重新编译

6、打开实验箱电源,选择tools\programmer 开始 下载程序

下载步骤

1、选择下载文件(后缀为sof的文件,文件名与实体名一致)

开始下载 按钮

选择下载 文件

选择下载 电缆

选择下载 模式

下载文件电缆的选择

选择下载电缆,在Hardware Settings一栏内 选择Add Hardware…后,再选择ByteBlaster MV

选择

计数器

4

十

显示 4 译码显示 7

(BCD输

4值

出) 百

... 其它5路

全0显示

SelTmp[2..0]

Clk

数码管

Sel[2..0]

扫描

实验步骤

1、用VHDL完成上述功能

2、进行时序仿真

3、打开实验箱,用导线连接相关引脚(连接时关 掉电源)

3、选择器件(EPF10K10LC84-4) (Assign\device)

实验三 扫描显示电路设计

实验要求

1、了解实验系统箱中数码管显示模块 的工作原理,学习使用实验箱。

2、设计显示信号选择及扫描控制电路。 将实验二中的计数值用数码管显示出来。

3、当计数器计数到自己的学号+100后, 计数器停止计数。按复位键后重新计数。

原理框图

Reset En Clk3

4

模1000 个

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

(1)数码管原理。

LED数码管也称为半导体数码管,是目前数字电路中最常用的显示器件之一,它以发光二极管作为笔段,分为共阴和共阳两种,其差别在于共阴数码管的八段发光二极管的阴极都连在一起,而阳极对应各段分别控制;共阳数码管则是八段发光二极管的阳极连在一起,阴极各段可分别控制,具体见下图。

8位数码动态扫描显示电路

(2)7448译码器

7448功能表

序号

输入

输出

LT

RBI

D

C

B

A

BI/RBO

Qa

Qb

Qc

Qd

Qe

Qf

Qg

字形

0

1

1

0

0

0

0

1

1

1

1

1

1

1

0

□

1

1

X

0

0

0

1

1

0

1

1

0

0

0

0

1

2

1

X

0

0

1

0

1

1

1

0

1

1

0

1

2

3

1

X

0

0

1

1

1

1

1

1

1

0

0

1

3

4

1

X

0

1

0

0

1

0

1

1

0

0

1

1

4

5

1

X

0

a)counter6模块

该模块需使用74390设计一个模6的计数器。请在空白处做预设计,画出电路图。

b)dig_select模块

该模块用于选择6位数码管中的某一位显示相应字形。74138为3-8译码器,功能表见附录。

c)decoder模块

可将4位8421BCD码译为七段码,驱动数码管以十进制数形式显示数字。7448为共阴极数码管译码器,功能表见附录。

(2)分频器模块fre_div

该模块已经设计完成,存放在F盘502文件夹里,使用时请自行拷贝至当前工程文件夹,并按设计需要选择合适的输出。

(3)计数器模块counter100

该计数器模块实现模100计数。此处同学们应掌握数据总线的画法。

(4)译码显示模块display

该模块由counter6模块,dig_select模块,seg_select模块以及decoder模块构成,请同学们自行完成该模块总体设计,当display模块的输入信号scanclk频率为1KHz时,数码管扫描周期为36ms,每次扫描每位数码管显示时长6ms。各子模块设计思路如下。

(a)引脚图(b)共阴极(c)共阳极

段数码管引脚图

引脚图中的3脚和8脚是公共端com,连在一起,7段数码管加上一个小数点共计8段,因此对数码管进行编码正好是一个字节(8位二进制)。以共阴数码管为例,公共端接GND,其余各段高电平点亮,则数码编码见表。

显示

dp

g

f

e

d

c

b

a

0

0

0

1

1

1

1

1

1

1

0

0

0

0

0

0

1

1

1

1

匕

15

1

X

1

1

1

1

1

0

0

0

0

0

0

0

灭

X

X

X

X

X

X

X

0

0

0

0

0

0

0

0

灭

脉冲X

1

0

0

0

0

1

0

0

0

0

0

0

0

灭

灯测试

0

X

X

X

X

X

1

1

1

1

1

1

1

1

日

(3)3-8译码器

74138功能表

3.电路设计

(1)顶层电路

由分频模块fre_div,计数器模块counter100,译码显示模块diaplay构成。分频模块fre_div将可将实验平台晶体振荡器提供的50MHz时钟信号分频,输出500Hz,1KHz及1Hz三种信号备用,conter100模块实现模100计数功能,display模块为数码管动态显示模块,实现计数数字在6位数码管上的动态显示。

动态显示

将所有数码管的8个显示笔划的同名端连在一起,另外为每个数码管的公共极COM增加位选通控制电路,位选通由各自独立的I/O线控制。如有8个数码管,则一共需要16个I/O口(8个段选、8个位选),见图2-5-2,其中k1~k8是位选信号。当输出字形码时,所有数码管都接收到相同的字形码,但究竟是哪个数码管会显示出字形,取决于对位选通COM端电路的控制,所以我们只要将需要显示的数码管的选通控制打开(以共阴数目管为例,低电平选中相应数码管),该位就显示出字形,没有选通的数码管就不会亮。通过分时轮流控制各个数码管的的COM端,就使各个数码管轮流受控显示,这就是动态驱动。所谓动态扫描显示即轮流向各位数码管送出字型码,尽管实际上各位数码管并非同时点亮,但只要扫描的速度足够快,利用发光二极管的余辉和人眼视觉暂留作用,使人感觉各位数码管同时在显示。动态显示的亮度比静态显示要差一些,但是能够节省大量的I/O端口,而且功耗更低。

1

0

1

1

1

0

1

1

0

1

1

5

6

1

X

0

1

1

0

1

0

0

1

1

1

1

1

6

7

1

X

0

1

1

1

1

1

1

1

0

0

0

0

7

8

1

X

1

0

0

0

1

1

1

1

1

1

1

1

8

9

1

X

1

0

0

1

1

1

1

1

0

0

1

1

9

10

1

X

1

0

1

0

1

0

0

0

1

1

0

1

11

1

X

1

0

1

1

1

0

0

1

1

0

0

1

12

1

X

1

1

0

0

1

0

1

0

0

0

1

1

13

1

X

1

1

0

1

1

1

0

0

1

0

1

1

14

1

X

1

1

1

0

1

0

d)seg_select模块

该模块功能是从6组4bit信号中选择一组作输出。(注意自行添加输入输出端)

上图中seclect1bit模块可使用74151设计,其功能为从6位输入数据中选择1位输出。请大家在下面空白处完成预设计。

4.引脚配置(列出输入输出引脚号)

引脚名

引脚号

引脚名

引脚号

输入节点

输出节点

5.实验结果(实验结果,如:波形结果、硬件平台结果;实验过程中的重点、难点、遇到的问题及解决方法等)

0

1

1

0

2

0

1

0

1

1

0

1

1

3

0

1

0

0

1

1

1

1

4

0

1

0

1

0

1

0

1

5

0

1

0

1

1

1

0

1

6

0

1

1

1

1

1

0

1

7

0

0

0

0

0

1

1

1

8

0

1

1

1

1

1

1

1

9

0

1

0

1

1

1

1

1

A

0

1

1

1

0

1

1

1

B

0

1

1

1

1

1

0

0

C

0

0

1

1

1

0

0

1

D

0

1

0

1

1

1

1

0

E

0

1

1

1

1

0

0

1

F

0

1

1

1

0

0

0

1

数码管有两种显示方式:

静态显示

每个数码管的8个段选信号(a~g、dp)都必须接一个8位数据线来保持显示的字形。当送入一次字型码后,显示可一直保持,直到送入新的字形码为止。优点是占用CPU时间少,便于控制显示。缺点是占用I/O口资源太多,如有8个数码管,就需要8×8=64个I/O口。

FPGA实验指导及记录

实验三基于FPGA的数码管动态扫描电路设计

1.实验目的:

(1)掌握FPGA工作的基本原理、FPGA硬件平台的使用;

(2)熟悉7段数码管显示译码电路的设计。