哈工大Verilog课程设计-状态机

verilog 状态机 最佳写法

verilog 状态机最佳写法Verilog编程语言广泛应用于数字电路设计中,特别是在嵌入式系统和硬件描述语言中。

状态机是一种常用的设计模式,可以帮助我们描述复杂的行为和控制逻辑。

本文将介绍如何使用Verilog编写状态机,并提供一些最佳实践。

第一部分:Verilog简介Verilog是一种硬件描述语言,最初由美国自动化控制协会(ACM)开发。

它是一种用于描述、仿真和生成数字电路的高级编程语言。

Verilog提供了描述硬件的能力,使我们能够在逻辑级别上描述电路的行为。

第二部分:状态机简介状态机是一种抽象的数学模型,用于描述系统或程序的行为。

它由一组状态、输入和输出组成,并在不同状态之间进行转换。

状态机可以用于描述任何连续或离散的系统,包括硬件和软件。

第三部分:状态机的设计方法在Verilog中,我们可以使用参数化模块和状态寄存器来描述状态机。

参数化模块可以接受输入和输出,根据当前状态和输入转换到下一个状态,并产生相应的输出。

下面是一个简单的例子:```module fsm #(parameter N=3) (input logic clk, reset, input logic [N-1:0] input, output [N-1:0] output);typedef enum logic [1:0] {S0, S1, S2} state_t;state_t state, next_state;always_ff @(posedge clk or posedge reset) begin if (reset) beginstate <= S0;end else beginstate <= next_state;endendalways_comb begincase (state)S0: begin// State S0 behavioroutput = input;next_state = S1;endS1: begin// State S1 behavioroutput = ~input;next_state = S2;endS2: begin// State S2 behavioroutput = 2'b11;next_state = S0;enddefault: begin// Default behavioroutput = 2'b00;next_state = S0;endendcaseendendmodule```在这个例子中,我们定义了一个状态机模块,它有一个时钟信号、一个复位信号、一个输入信号和一个输出信号。

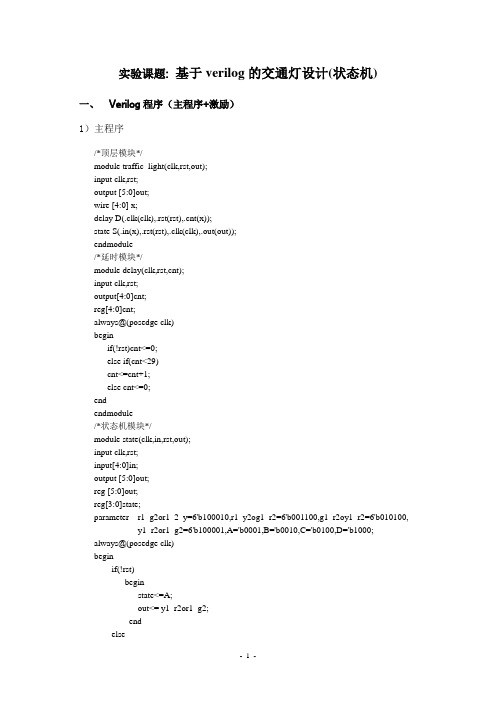

基于verilog的交通灯设计(状态机)

实验课题:基于verilog的交通灯设计(状态机)一、Verilog程序(主程序+激励)1)主程序/*顶层模块*/module traffic_light(clk,rst,out);input clk,rst;output [5:0]out;wire [4:0] x;delay D(.clk(clk),.rst(rst),.cnt(x));state S(.in(x),.rst(rst),.clk(clk),.out(out));endmodule/*延时模块*/module delay(clk,rst,cnt);input clk,rst;output[4:0]cnt;reg[4:0]cnt;always@(posedge clk)beginif(!rst)cnt<=0;else if(cnt<29)cnt<=cnt+1;else cnt<=0;endendmodule/*状态机模块*/module state(clk,in,rst,out);input clk,rst;input[4:0]in;output [5:0]out;reg [5:0]out;reg[3:0]state;parameter r1_g2or1_2_y=6'b100010,r1_y2og1_r2=6'b001100,g1_r2oy1_r2=6'b010100, y1_r2or1_g2=6'b100001,A='b0001,B='b0010,C='b0100,D='b1000;always@(posedge clk)beginif(!rst)beginstate<=A;out<= y1_r2or1_g2;endelsebegincase(state)A: beginif(in<25)state<=A;elsebeginstate<=B;out<=r1_g2or1_2_y;endendB: beginif(in>24)state<=B;elsebeginstate<=C;out<=r1_y2og1_r2;endendC: beginif(in<25)state<=C;elsebeginstate<=D;out<=g1_r2oy1_r2;endendD: beginif(in>24)state<=D;elsebeginstate<=A;out<=y1_r2or1_g2;endendendcaseendendendmodule2)激励module test;reg clk,rst;wire [5:0]out;traffic_light test(clk,rst,out);initialbeginclk='b1;forever #5 clk=~clk;endinitialbeginrst='b0;#10 rst='b1;#500 rst='b0;#10 rst='b1;endendmodule二、实验波形图截图三、波形分析输出out[5:0]分别对应:out[5]:主干道红灯out[4]:主干道黄灯out[3]:主干道绿灯out[2]:支干道红灯out[1]:支干道黄灯out[0]:支干道绿灯初始状态为:主干道红灯亮,支干道绿灯亮。

Verilog 有限状态机设计(课堂PPT)

begin

case( state )

state0:

out = 3'b001;

state1:

out = 3'b010;

state2:

out = 3'b100;

state3:

out = 3'b111;

default:

out = 3'b001;

endcase

end

endmodule

11

8.2 有限状态机的Verilog描述

begin if(clr) qout<=0;

//异步复位

else case(qout)

3'b000: qout<=3'b001;

3'b001: qout<=3'b010;

3'b010: qout<=3'b011;

3'b011: qout<=3'b100;

3'b100: qout<=3'b000;

default: qout<=3'b000; /*default语句*/

state2 = 2’b11, state3 = 2’b10; // 格雷码

always @( posedge clk or posedge clr ) begin

if( clr ) state <= state0; // 定义初态 state <= next_state; end

8

always @( state or start or step2 or step3 ) // 状态转换

EDA技术与应用

第八章 有限状态机设计

1

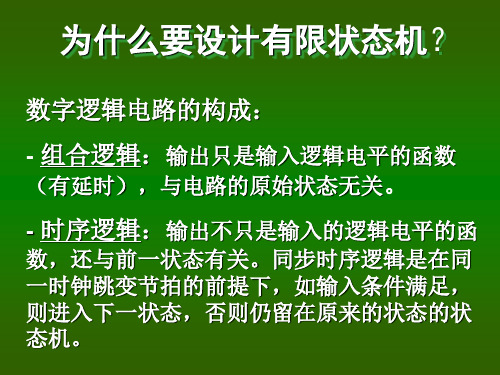

verilog---为什么要设计有限状态机

为什么要设计有限状态机? 为什么要设计有限状态机?

10ns

clock t S1 S2 S3 t S4 t Sn t 开 关 t t

为什么要设计有限状态机? 为什么要设计有限状态机?

如果我们能设计这样一个电路: 如果我们能设计这样一个电路: 1)能记住自己目前所处的状态 ; 2)状态的变化只可能在同一个时钟的跳变沿 时刻发生,而不可能发生在任意时刻; 时刻发生,而不可能发生在任意时刻; 3)在时钟跳变沿时刻,如输入条件满足,则 在时钟跳变沿时刻,如输入条件满足, 进入下一状态,并记住自己目前所处的状态, 进入下一状态,并记住自己目前所处的状态, 否则仍保留原来的状态; 否则仍保留原来的状态; 4)在进入不同的状态时刻,对系统的开关阵 在进入不同的状态时刻, 列做开启或关闭的操作。 列做开启或关闭的操作。

如果能严格以时钟跳变沿为前提,按排 如果能严格以时钟跳变沿为前提, 好时序, 好时序,来操作逻辑系统中每一个开关 Si,则系统中数据的流动和处理会按同 Si,则系统中数据的流动和处理会按同 一时钟节拍有序地进行 节拍有序地进行, 一时钟节拍有序地进行,避免了冒险和 竞争现象, 竞争现象,时延问题就能有效地加以解 决。 利用有限状态机就能产生复杂的以时钟 跳变沿为前提的同步时序逻辑, 跳变沿为前提的同步时序逻辑,并提供 操作逻辑系统的开关阵列所需要的复杂 具有信号无锁和先后次序等要求的)。 控制时序(具有信号无锁和先后次序等要求的)。

成的网络。常用的有:计数器、复杂的数据流动控制 成的网络。常用的有:计数器、 逻辑、运算控制逻辑、指令分析和操作控制逻辑。 逻辑、运算控制逻辑、指令分析和操作控制逻辑。同 步时序逻辑的设计是设计复杂的数字逻辑系统的核心。 步时序逻辑的设计是设计复杂的数字逻辑系统的核心。

Verilog HDL入门基础之时序状态机的设计

时序状态机的设计入门与提高计算机及具有存储器或按照所存储信息执行一系列操作的其他数字系统统称为“时序状态机”,其电路可以通过时序逻辑进行建模。

时序状态机的性能与组合逻辑不同,因为时序状态机的输出不仅仅取决于当前的输入值,而且取决于历史的输入值。

时序状态机被广泛应用于需要指定顺序操作的应用中。

所有的时序状态机都具有如图的通用反馈结构,在这种结构中时序状态机的下一状态是由当前状态和当前输入一起形成的:时序状态机可以按是否受一个公共的时钟控制(钟控)分为同步状态机和异步状态机;根据状态数目是否有限分为有限状态机和无限状态机。

此处只讨论有限状态机。

有限状态机的(FSM)分类有限状态机有米利(Mealy)机和摩尔(Moore)机:米利(Mealy)机:米利(Mealy)机的下一状态和输出都取决于当前状态和当前输入。

摩尔(Moore)机:摩尔(Moore)机的下一状态取决于当前状态和当前输入,而输出仅仅取决于当前状态。

有限状态机常用的描述、开发方法有限状态机可以借助时序图、状态表、状态图以及ASM图进行系统的描述与设计。

•时序图可以用于说明系统中及系统与周围环境的接口中信号的有效输入与状态转移之间的关系。

•状态表与状态转移表以表格的形式表示在当前状态和输入的各种组合下状态机的下一状态和输出•状态转移图(STG)是一种有向图,图中带有标记的节点或顶点与时序状态机的状态一一对应。

当系统处于弧线起点的状态时,用有向边或弧线表示在输入信号的作用下可能发生的状态转移。

米利机STG的顶点用状态进行标记,状态转移图的有向边有下面两种标记方法:(1)用能够导致状态向指定的下一状态转移的输入信号来标记(2)在当前状态下,用输入信号的输出来进行标记摩尔机的状态转移图与米利机相类似,但它的输出是由各状态的顶点来表示的,而不是在弧线上表示•算法状态机(ASM)图是时序状态机功能的一种抽象,是模拟其行为特性的关键工具。

它类似于软件流程图,但显示的是计算流程图(如寄存器操作)的时间顺序,以及在状态机输入影响下发生的时序步骤。

verilog 三段式状态机

Verilog状态机设计‐‐‐‐‐‐‐‐‐三段式状态机练习:设计一个串行数据检测器。

要求是:连续4个或4个以上的1时输出为1,其他输入情况下为0。

编写测试模块并给出仿真波形。

目的:学会状态机设计方法模块源码`timescale 1ps/1psmodule FSM (input iCLK,input iRST_N,input iA,output oMATCH);parameter S0 = 3'b000,S1 = 3'b001,S2 = 3'b010,S3 = 3'b011,S4 = 3'b100;reg [2:0] state, next_state;reg match, next_match;wire is_match_out;assign oMATCH = match;// sequential circuitalways@(posedge iCLK, negedge iRST_N) beginif (!iRST_N) beginstate <= S0;match <= 1'b0;endelse beginstate <= next_state;match <= next_match;endend// combinational circuit for state logicalways@(*) begin //*号不能改为posedge iCLK, negedge iRST_N next_state = S0;case (state)S0 : next_state = (iA==1) ? S1 : S0;S1 : next_state = (iA==1) ? S2 : S0;S2 : next_state = (iA==1) ? S3 : S0;S3 : next_state = (iA==1) ? S4 : S0;S4 : next_state = (iA==1) ? S4 : S0;endcaseend// combinational circuit for output logicassign is_match_out = (next_state == S4) ? 1 : 0;//注意点:如何next_state用state则输出会比现在延时1个周期。

哈工大电大数字电子技术基础大作业

哈工大电大数字电子技术基础大作业

H a r b i n I n s t i t u t e o f T e c h n o l o g y

数字电子技术基础大作业

课程名称:数字电子技术基础

设计题目:血型与状态机

院系:

班级:

设计者:

学号:

哈尔滨工业大学

血型逻辑电路设计

一实验目的

1.掌握采用可编程逻辑器件实现数字电路与系统

的方法。

2.掌握采用Xilinx_ISE软件开发可编程逻辑器件

的过程。

3.学会设计血型能否输血的数字电路。

4.掌握Verilog HDL描述数字逻辑电路与系统的方

法。

二设计要求

1.采用BASYS2开发板开关,LED,数码管等制作验

证能否输血的电路。

2.采用Xilinx_ISE软件进行编程、仿真与下载设

计到BASYS2开发板。

三电路图

1.电路模块图(简化)

应用:

2.内部电路组成(简化)。

第8章 Verilog有限状态机设计

endcase

end

endmodule

module fsm52(clk,clr,z);

input clk,clr; output reg z; output reg[4:0] state;

Parameter s0=5'b00001,s1=5'b00010,s2=5'b00100,

s3=5'b01000,s4=5'b10000;

3'b011: qout<=3'b100;

3'b100: qout<=3'b000;

default: qout<=3'b000;

/*default语句*/

endcase

end

always @(qout)

/*此过程产生输出逻辑*/

begin case(qout)

3'b100: z=1'b1;

default:z=1'b0;

摩尔型(Moore)状态机 米里型(Mealy)状态机

摩尔型状态机与米里型状态机

1、状态机的概念 摩尔型moore状态机:输出只与当前状态有关,需

等待时钟的到来; 米里型mealy状态机:输出与当前状态和输入有关,

不依赖时钟信号的同步; 2、moore状态机的实现:用case(检查当前状态)

【例8.1】两个always过程 【例8.2】单过程P196,输出信号z比

【例8.1】 的延后了一个时钟周期的时间

用状态机设计计数器

【例8.1】两个always过程

【例8.2】单过程

用状态机设计模5计数器?

module fsm(clk,clr,z,qout);

Verilog三段式状态机

Verilog三段式状态机(FSM)网上收集整理……时序电路的状态是一个状态变量集合,这些状态变量在任意时刻的值都包含了为确定电路的未来行为而必需考虑的所有历史信息。

状态机采用VerilogHDL语言编码,建议分为三个always段完成。

这是为什么呢?设计FSM的方法和技巧多种多样,但是总结起来有两大类:第一种,将状态转移和状态的操作和判断等写到一个模块(process、block)中。

另一种是将状态转移单独写成一个模块,将状态的操作和判断等写到另一个模块中(在Verilog代码中,相当于使用两个“always”block)。

其中较好的方式是后者。

其原因如下。

首先FSM和其他设计一样,最好使用同步时序方式设计,好处不再累述。

而状态机实现后,状态转移是用寄存器实现的,是同步时序部分。

辑判断实现的,之所以第二种比第一种编码方式合理,就在于第二种编码将同步时序和组合逻辑分别放到不同的程序块(process,block)中实现。

这样做的好处不仅仅是便于阅读、理解、维护,更重要的是利于综合器优化代码,利于用户添加合适的时序约束条件,利于布局布线器实现设计。

三段式建模描述FSM的状态机输出时,只需指定case敏感表为次态寄存器,然后直接在每个次态的case分支中描述该状态的输出即可,不用考虑状态转移条件。

三段式描述方法虽然代码结构复杂了一些,但是换来的优势是使FSM做到了同步寄存器输出,消除了组合逻辑输出的不稳定与毛刺的隐患,而且更利于时序路径分组,一般来说在FPGA/CPLD等可编程逻辑器件上的综合与布局布线效果更佳。

示例如下://第一个进程,同步时序always模块,格式化描述次态寄存器迁移到现态寄存器always @ (posedge clk or negedge rst_n) //异步复位if(!rst_n)current_state <= IDLE;elsecurrent_state <= next_state;//注意,使用的是非阻塞赋值//第二个进程,组合逻辑always模块,描述状态转移条件判断always @ (current_state) //电平触发beginnext_state = x; //要初始化,使得系统复位后能进入正确的状态S1: if(...)next_state = S2; //阻塞赋值...endcaseend//第三个进程,同步时序always模块,格式化描述次态寄存器输出always @ (posedge clk or negedge rst_n)...//初始化case(next_state)S1:out1 <= 1'b1; //注意是非阻塞逻辑S2:out2 <= 1'b1;default:... //default的作用是免除综合工具综合出锁存器。

第8章 Verilog有限状态机设计

always @(posedge clk or posedge clr)

//此过程定义状态转换

beginif(clr) qout<=0;

//异步复位

else case(qout)

3'b000: qout<=3'b001;

3'b001: qout<=3'b010;

3'b010: qout<=3'b011;

第8章 Verilog有限状态机设计

8.1 有限状态机(FSM)

有限状态机(Finite State Machine,FSM) 1、适于设计数字系统的控制模块,适于用

FPGA实现; 2、认为是组合逻辑和寄存器逻辑的特殊组 合,寄存器用于存储状态,组合逻辑用于状态 译码和产生输出信号;

8.1 有限状态机

位热码方式*/

/*状态编码,采用一

always @(posedge clk or posedge clr)

//此过程定义状态转换

begin

if(clr) state<=s0;

//异步复位

else case(state)

s0: state<=s1;

s1: state<=s2;

s2: state<=s3;

s3: state<=s4;

s4: state<=s0;

default: state<=s0; /*default语句*/

endcase

end

always @(state)

/*此过程产生输出逻辑*/

begin case(state)s4:z=1'b1;

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

可编程逻辑器件大作业(二)

2012年12月

一、题目

利用Verilog HDL设计一个电路,对输入的一串二进制数,用于检测序列中连续3个或者3个以上的1,状态转换图如图所示。

要求:

1、编写源程序;

2、给出仿真电路图、状态转换图和仿真波形图

二、程序代码

module moore(clk,din,op,reset);

input clk,din,reset;

output op;

reg[1:0] current_state,next_state;

reg op;

parameter S0=2'b00,S1=2'b01,S2=2'b10,S3=2'b11;

always @ (posedge clk)

begin

if(!reset) current_state = S0;

else current_state <= next_state;

end

always @ (din or current_state)

begin

case( current_state )

S0: begin

op = 0;

if(din == 0)

next_state = S0;

else

next_state = S1;

end

S1: begin

op = 0;

if(din == 0)

next_state = S0;

else

next_state = S2;

end

S2: begin

op = 0;

if(din == 0)

next_state = S0;

else

next_state = S3;

end

S3: begin

op = 1;

if(din == 0)

next_state = S0;

else

next_state = S3;

end

default:begin

next_state = S0;

op = 0;

end

endcase

end

endmodule

三、仿真波形图

可知仿真波形图与状态转换图的相符四、仿真电路图

五、状态转换图

六、心得体会

通过设计过程对状态机的概念有了更深的理解,认识到了其在现实生活中的重要应用。

更熟练地掌握了Verilog HDL硬件描述语言,提高了编程能力;对利用quartus软件设计过程有了大致的了解。