CD74HC74中文资料

74HC74DB中文资料

2003 Jul 10

3

元器件交易网

Philips Semiconductors

Product specification

Dual D-type flip-flop with set and reset; positive-edge trigger

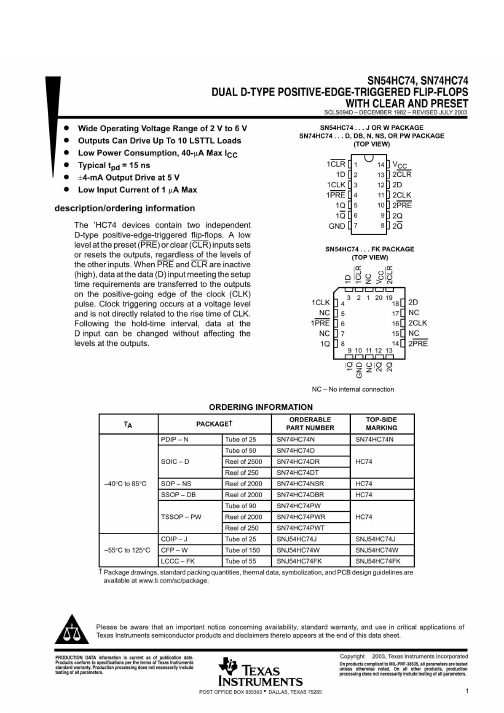

PINNING PIN 1 2 3 4 5 6 7 8 9 10 11 12 13 14 SYMBOL 1RD 1D 1CP 1SD 1Q 1Q GND 2Q 2Q 2SD 2CP 2D 2RD VCC data input clock input (LOW-to-HIGH, edge-triggered) asynchronous set-direct input (active LOW) true flip-flop output complement flip-flop output ground (0 V) complement flip-flop output true flip-flop output asynchronous set-direct input (active LOW) clock input (LOW-to-HIGH, edge-triggered) data input asynchronous reset-direct input (active LOW) positive supply voltage DESCRIPTION asynchronous reset-direct input (active LOW)

74HC74; 74HCT74

GENERAL DESCRIPTION The 74HC/HCT74 is a high-speed Si-gate CMOS device and is pin compatible with low power Schottky TTL (LSTTL). They are specified in compliance with JEDEC standard no. 7A. The 74HC/HCT74 are dual positive-edge triggered, D-type flip-flops with individual data (D) inputs, clock (CP) inputs, set (SD) and reset (RD) inputs; also complementary Q and Q outputs. The set and reset are asynchronous active LOW inputs and operate independently of the clock input. Information on the data input is transferred to the Q output on the LOW-to-HIGH transition of the clock pulse. The D inputs must be stable one set-up time prior to the LOW-to-HIGH clock transition for predictable operation. Schmitt-trigger action in the clock input makes the circuit highly tolerant to slower clock rise and fall times.

ls系列74hc系列cd系列芯片功能

74LS系列芯片功能反相器驱动器LS04 LS05 LS06 LS07 LS125 LS240 LS244 LS245 与门与非门LS00 LS08 LS10 LS11 LS20 LS21 LS27 LS30 LS38 或门或非门与或非门LS02 LS32 LS51 LS64 LS65异或门比较器LS86译码器LS138 LS139寄存器LS74 LS175 LS37374系列::74LS00 TTL 2输入端四与非门74LS01 TTL 集电极开路2输入端四与非门74LS02 TTL 2输入端四或非门74LS03 TTL 集电极开路2输入端四与非门74LS04 TTL 六反相器74LS05 TTL 集电极开路六反相器74LS06 TTL 集电极开路六反相高压驱动器74LS07 TTL 集电极开路六正相高压驱动器74LS08 TTL 2输入端四与门74LS09 TTL 集电极开路2输入端四与门74LS10 TTL 3输入端3与非门74LS107 TTL 带清除主从双J-K触发器74LS109 TTL 带预置清除正触发双J-K触发器74LS11 TTL 3输入端3与门74LS112 TTL 带预置清除负触发双J-K触发器74LS12 TTL 开路输出3输入端三与非门74LS121 TTL 单稳态多谐振荡器74LS122 TTL 可再触发单稳态多谐振荡器74LS123 TTL 双可再触发单稳态多谐振荡器74LS125 TTL 三态输出高有效四总线缓冲门74LS126 TTL 三态输出低有效四总线缓冲门74LS13 TTL 4输入端双与非施密特触发器74LS132 TTL 2输入端四与非施密特触发器74LS133 TTL 13输入端与非门74LS136 TTL 四异或门74LS138 TTL 3-8线译码器/复工器74LS139 TTL 双2-4线译码器/复工器74LS14 TTL 六反相施密特触发器74LS145 TTL BCD—十进制译码/驱动器74LS15 TTL 开路输出3输入端三与门74LS150 TTL 16选1数据选择/多路开关74LS151 TTL 8选1数据选择器74LS153 TTL 双4选1数据选择器74LS154 TTL 4线—16线译码器74LS155 TTL 图腾柱输出译码器/分配器74LS156 TTL 开路输出译码器/分配器74LS157 TTL 同相输出四2选1数据选择器74LS158 TTL 反相输出四2选1数据选择器74LS16 TTL 开路输出六反相缓冲/驱动器74LS160 TTL 可预置BCD异步清除计数器74LS161 TTL 可予制四位二进制异步清除计数器74LS162 TTL 可预置BCD同步清除计数器74LS163 TTL 可予制四位二进制同步清除计数器74LS164 TTL 八位串行入/并行输出移位寄存器74LS165 TTL 八位并行入/串行输出移位寄存器74LS166 TTL 八位并入/串出移位寄存器74LS169 TTL 二进制四位加/减同步计数器74LS17 TTL 开路输出六同相缓冲/驱动器74LS170 TTL 开路输出4×4寄存器堆74LS173 TTL 三态输出四位D型寄存器74LS174 TTL 带公共时钟和复位六D触发器74LS175 TTL 带公共时钟和复位四D触发器74LS180 TTL 9位奇数/偶数发生器/校验器74LS181 TTL 算术逻辑单元/函数发生器74LS185 TTL 二进制—BCD代码转换器74LS190 TTL BCD同步加/减计数器74LS191 TTL 二进制同步可逆计数器74LS192 TTL 可预置BCD双时钟可逆计数器74LS193 TTL 可预置四位二进制双时钟可逆计数器74LS194 TTL 四位双向通用移位寄存器74LS195 TTL 四位并行通道移位寄存器74LS196 TTL 十进制/二-十进制可预置计数锁存器74LS197 TTL 二进制可预置锁存器/计数器74LS20 TTL 4输入端双与非门74LS21 TTL 4输入端双与门74LS22 TTL 开路输出4输入端双与非门74LS221 TTL 双/单稳态多谐振荡器74LS240 TTL 八反相三态缓冲器/线驱动器74LS241 TTL 八同相三态缓冲器/线驱动器74LS243 TTL 四同相三态总线收发器74LS244 TTL 八同相三态缓冲器/线驱动器74LS245 TTL 八同相三态总线收发器74LS247 TTL BCD—7段15V输出译码/驱动器74LS248 TTL BCD—7段译码/升压输出驱动器74LS249 TTL BCD—7段译码/开路输出驱动器74LS251 TTL 三态输出8选1数据选择器/复工器74LS253 TTL 三态输出双4选1数据选择器/复工器74LS256 TTL 双四位可寻址锁存器74LS257 TTL 三态原码四2选1数据选择器/复工器74LS258 TTL 三态反码四2选1数据选择器/复工器74LS259 TTL 八位可寻址锁存器/3-8线译码器74LS26 TTL 2输入端高压接口四与非门74LS260 TTL 5输入端双或非门74LS266 TTL 2输入端四异或非门74LS27 TTL 3输入端三或非门74LS273 TTL 带公共时钟复位八D触发器74LS279 TTL 四图腾柱输出S-R锁存器74LS28 TTL 2输入端四或非门缓冲器74LS283 TTL 4位二进制全加器74LS290 TTL 二/五分频十进制计数器74LS293 TTL 二/八分频四位二进制计数器74LS295 TTL 四位双向通用移位寄存器74LS298 TTL 四2输入多路带存贮开关74LS299 TTL 三态输出八位通用移位寄存器74LS30 TTL 8输入端与非门74LS32 TTL 2输入端四或门74LS322 TTL 带符号扩展端八位移位寄存器74LS323 TTL 三态输出八位双向移位/存贮寄存器74LS33 TTL 开路输出2输入端四或非缓冲器74LS347 TTL BCD—7段译码器/驱动器74LS352 TTL 双4选1数据选择器/复工器74LS353 TTL 三态输出双4选1数据选择器/复工器74LS365 TTL 门使能输入三态输出六同相线驱动器74LS365 TTL 门使能输入三态输出六同相线驱动器74LS366 TTL 门使能输入三态输出六反相线驱动器74LS367 TTL 4/2线使能输入三态六同相线驱动器74LS368 TTL 4/2线使能输入三态六反相线驱动器74LS37 TTL 开路输出2输入端四与非缓冲器74LS373 TTL 三态同相八D锁存器74LS374 TTL 三态反相八D锁存器74LS375 TTL 4位双稳态锁存器74LS377 TTL 单边输出公共使能八D锁存器74LS378 TTL 单边输出公共使能六D锁存器74LS379 TTL 双边输出公共使能四D锁存器74LS38 TTL 开路输出2输入端四与非缓冲器74LS380 TTL 多功能八进制寄存器74LS39 TTL 开路输出2输入端四与非缓冲器74LS390 TTL 双十进制计数器74LS393 TTL 双四位二进制计数器74LS40 TTL 4输入端双与非缓冲器74LS42 TTL BCD—十进制代码转换器74LS352 TTL 双4选1数据选择器/复工器74LS353 TTL 三态输出双4选1数据选择器/复工器74LS365 TTL 门使能输入三态输出六同相线驱动器74LS366 TTL 门使能输入三态输出六反相线驱动器74LS367 TTL 4/2线使能输入三态六同相线驱动器74LS368 TTL 4/2线使能输入三态六反相线驱动器74LS37 TTL 开路输出2输入端四与非缓冲器74LS373 TTL 三态同相八D锁存器74LS374 TTL 三态反相八D锁存器74LS375 TTL 4位双稳态锁存器74LS377 TTL 单边输出公共使能八D锁存器74LS378 TTL 单边输出公共使能六D锁存器74LS379 TTL 双边输出公共使能四D锁存器74LS38 TTL 开路输出2输入端四与非缓冲器74LS380 TTL 多功能八进制寄存器74LS39 TTL 开路输出2输入端四与非缓冲器74LS390 TTL 双十进制计数器74LS393 TTL 双四位二进制计数器74LS40 TTL 4输入端双与非缓冲器74LS42 TTL BCD—十进制代码转换器74LS447 TTL BCD—7段译码器/驱动器74LS45 TTL BCD—十进制代码转换/驱动器74LS450 TTL 16:1多路转接复用器多工器74LS451 TTL 双8:1多路转接复用器多工器74LS453 TTL 四4:1多路转接复用器多工器74LS46 TTL BCD—7段低有效译码/驱动器74LS460 TTL 十位比较器74LS461 TTL 八进制计数器74LS465 TTL 三态同相2与使能端八总线缓冲器74LS466 TTL 三态反相2与使能八总线缓冲器74LS467 TTL 三态同相2使能端八总线缓冲器74LS468 TTL 三态反相2使能端八总线缓冲器74LS469 TTL 八位双向计数器74LS47 TTL BCD—7段高有效译码/驱动器74LS48 TTL BCD—7段译码器/内部上拉输出驱动74LS490 TTL 双十进制计数器74LS491 TTL 十位计数器74LS498 TTL 八进制移位寄存器74LS50 TTL 2-3/2-2输入端双与或非门74LS502 TTL 八位逐次逼近寄存器74LS503 TTL 八位逐次逼近寄存器74LS51 TTL 2-3/2-2输入端双与或非门74LS533 TTL 三态反相八D锁存器74LS534 TTL 三态反相八D锁存器74LS54 TTL 四路输入与或非门74LS540 TTL 八位三态反相输出总线缓冲器74LS55 TTL 4输入端二路输入与或非门74LS563 TTL 八位三态反相输出触发器74LS564 TTL 八位三态反相输出D触发器74LS573 TTL 八位三态输出触发器74LS574 TTL 八位三态输出D触发器74LS645 TTL 三态输出八同相总线传送接收器74LS670 TTL 三态输出4×4寄存器堆74LS73 TTL 带清除负触发双J-K触发器74LS74 TTL 带置位复位正触发双D触发器74LS76 TTL 带预置清除双J-K触发器74LS83 TTL 四位二进制快速进位全加器74LS85 TTL 四位数字比较器74LS86 TTL 2输入端四异或门74LS90 TTL 可二/五分频十进制计数器74LS93 TTL 可二/八分频二进制计数器74LS95 TTL 四位并行输入\输出移位寄存器74LS97 TTL 6位同步二进制乘法器反相器:Vcc 6A 6Y 5A 5Y 4A 4Y 六非门74LS04┌┴—┴—┴—┴—┴—┴—┴┐ 六非门(OC门) 74LS05 _ │14 13 12 11 10 9 8│ 六非门(OC高压输出) 74LS06 Y = A )││ 1 2 3 4 5 6 7│└┬—┬—┬—┬—┬—┬—┬┘1A 1Y 2A 2Y 3A 3Y GND驱动器:Vcc 6A 6Y 5A 5Y 4A 4Y┌┴—┴—┴—┴—┴—┴—┴┐│14 13 12 11 10 9 8│Y = A )│ 六驱动器(OC高压输出) 74LS07│ 1 2 3 4 5 6 7│└┬—┬—┬—┬—┬—┬—┬┘1A 1Y 2A 2Y 3A 3Y GNDVcc -4C 4A 4Y -3C 3A 3Y┌┴—┴—┴—┴—┴—┴—┴┐_ │14 13 12 11 10 9 8│Y =A+C )│ 四总线三态门74LS125│ 1 2 3 4 5 6 7│└┬—┬—┬—┬—┬—┬—┬┘-1C 1A 1Y -2C 2A 2Y GNDVcc -G B1 B2 B3 B4 B8 B6 B7 B8┌┴—┴—┴—┴—┴—┴—┴—┴—┴—┴┐ 8位总线驱动器74LS245│20 19 18 17 16 15 14 13 12 11│)│ DIR=1 A=>B│ 1 2 3 4 5 6 7 8 9 10│ DIR=0 B=>A└┬—┬—┬—┬—┬—┬—┬—┬—┬—┬┘DIR A1 A2 A3 A4 A5 A6 A7 A8 GND页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器正逻辑与门,与非门:Vcc 4B 4A 4Y 3B 3A 3Y┌┴—┴—┴—┴—┴—┴—┴┐│14 13 12 11 10 9 8│Y = AB )│ 2输入四正与门74LS08│ 1 2 3 4 5 6 7│└┬—┬—┬—┬—┬—┬—┬┘1A 1B 1Y 2A 2B 2Y GNDVcc 4B 4A 4Y 3B 3A 3Y┌┴—┴—┴—┴—┴—┴—┴┐__ │14 13 12 11 10 9 8│Y = AB )│ 2输入四正与非门74LS00│ 1 2 3 4 5 6 7│└┬—┬—┬—┬—┬—┬—┬┘1A 1B 1Y 2A 2B 2Y GNDVcc 1C 1Y 3C 3B 3A 3Y┌┴—┴—┴—┴—┴—┴—┴┐___ │14 13 12 11 10 9 8│Y = ABC )│ 3输入三正与非门74LS10│ 1 2 3 4 5 6 7│└┬—┬—┬—┬—┬—┬—┬┘1A 1B 2A 2B 2C 2Y GNDVcc H G Y┌┴—┴—┴—┴—┴—┴—┴┐│14 13 12 11 10 9 8│)│ 8输入与非门74LS30│ 1 2 3 4 5 6 7│ ________└┬—┬—┬—┬—┬—┬—┬┘ Y = ABCDEFGHA B C D E F GND页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器正逻辑或门,或非门:Vcc 4B 4A 4Y 3B 3A 3Y┌┴—┴—┴—┴—┴—┴—┴┐ 2输入四或门74LS32│14 13 12 11 10 9 8│)│ Y = A+B│ 1 2 3 4 5 6 7│└┬—┬—┬—┬—┬—┬—┬┘1A 1B 1Y 2A 2B 2Y GNDVcc 4Y 4B 4A 3Y 3B 3A┌┴—┴—┴—┴—┴—┴—┴┐ 2输入四或非门74LS02│14 13 12 11 10 9 8│ ___)│ Y = A+B│ 1 2 3 4 5 6 7│└┬—┬—┬—┬—┬—┬—┬┘1Y 1A 1B 2Y 2A 2B GNDVcc 2Y 2B 2A 2D 2E 1F┌┴—┴—┴—┴—┴—┴—┴┐ 双与或非门74S51│14 13 12 11 10 9 8│ _____)│ 2Y = AB+DE│ 1 2 3 4 5 6 7│ _______└┬—┬—┬—┬—┬—┬—┬┘ 1Y = ABC+DEF1Y 1A 1B 1C 1D 1E GNDVcc D C B K J Y┌┴—┴—┴—┴—┴—┴—┴┐ 4-2-3-2与或非门74S64 74S65(OC门)│14 13 12 11 10 9 8│ ______________)│ Y = ABCD+EF+GHI+JK│ 1 2 3 4 5 6 7│└┬—┬—┬—┬—┬—┬—┬┘A E F G H I GND页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器2输入四异或门74LS86Vcc 4B 4A 4Y 3Y 3B 3A┌┴—┴—┴—┴—┴—┴—┴┐│14 13 12 11 10 9 8│)│ _ _│ 1 2 3 4 5 6 7│ Y=AB+AB└┬—┬—┬—┬—┬—┬—┬┘1A 1B 1Y 2Y 2A 2B GND8*2输入比较器74LS688_Vcc Y B8 A8 B7 A7 B6 A6 B5 A5┌┴—┴—┴—┴—┴—┴—┴—┴—┴—┴┐ 8*2输入比较器74LS688│20 19 18 17 16 15 14 13 12 11│)││ 1 2 3 4 5 6 7 8 9 10│└┬—┬—┬—┬—┬—┬—┬—┬—┬—┬┘CE A1 B1 A2 B2 A3 B3 A4 B4 GND_Y=A1⊙B1+A2⊙B2+A3⊙B3+A4⊙B4+A5⊙B5+A6⊙B6+A7⊙B7+A8⊙B8 页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器3-8译码器74LS138Vcc -Y0 -Y1 -Y2 -Y3 -Y4 -Y5 -Y6 __ _ _ _ __ _ _ __ _ _ __ _┌┴—┴—┴—┴—┴—┴—┴—┴┐ Y0=A B C Y1=A B B Y2=A B C Y3=A B C │16 15 14 13 12 11 10 9 │)│ __ _ _ __ _ __ _ __│ 1 2 3 4 5 6 7 8│ Y4=A B C Y5=A B C Y6=A B C Y7=A B C└┬—┬—┬—┬—┬—┬—┬—┬┘A B C -CS0 -CS1 CS2 -Y7 GND双2-4译码器74LS139Vcc -2G 2A 2B -Y0 -Y1 -Y2 -Y3 __ __ __ __ __ __ __ __┌┴—┴—┴—┴—┴—┴—┴—┴┐ Y0=2A 2B Y1=2A 2B Y2=2A 2B Y3=2A 2B │16 15 14 13 12 11 10 9 │)│ __ __ __ __ __ __ __ __│ 12 3 4 5 6 7 8│ Y0=1A 1B Y1=1A 1B Y2=1A 1B Y3=1A 1B└┬—┬—┬—┬—┬—┬—┬—┬┘-1G 1A 1B -Y0 -Y1 -Y2 -Y3 GND8*2输入比较器74LS688_Vcc Y B8 A8 B7 A7 B6 A6 B5 A5┌┴—┴—┴—┴—┴—┴—┴—┴—┴—┴┐ 8*2输入比较器74LS688│20 19 18 17 16 15 14 13 12 11│)││ 1 2 3 4 5 6 7 8 9 10│└┬—┬—┬—┬—┬—┬—┬—┬—┬—┬┘CE A1 B1 A2 B2 A3 B3 A4 B4 GND_Y=A1⊙B1+A2⊙B2+A3⊙B3+A4⊙B4+A5⊙B5+A6⊙B6+A7⊙B7+A8⊙B8寄存器:Vcc 2CR 2D 2Ck 2St 2Q -2Q┌┴—┴—┴—┴—┴—┴—┴┐ 双D触发器74LS74│14 13 12 11 10 9 8 │)││ 1 2 3 4 5 6 7│└┬—┬—┬—┬—┬—┬—┬┘1Cr 1D 1Ck 1St 1Q -1Q GNDVcc 8Q 8D 7D 7Q 6Q 6D 5D 5Q ALE┌┴—┴—┴—┴—┴—┴—┴—┴—┴—┴┐ 8位锁存器74LS373│20 19 18 17 16 15 14 13 12 11│)││ 1 2 3 4 5 6 7 8 9 10│└┬—┬—┬—┬—┬—┬—┬—┬—┬—┬┘-OE 1Q 1D 2D 2Q 3Q 3D 4D 4Q GND74HC系列功能表集成电路-74HC系列型号器件名称厂牌[数据表] 74HC00 四2输入端与非门 TI74HC01 四2输入端与非门(OC)74HC02 四2输入端或非门 TI74HC03 四2输入端与非门(OC) TI74HC04 六反相器 TI74HC05 HEX INVERTERS74HC08 四2输入端与门 TI74HC09 QUADRUPLE 2-INPUT POSITIVE-AND74HC10 三3输入端与非门 TI74HC11 三3输入端与门 TI74HC14 双4输入端与非门 TI74HC20 双4输入端与非门 TI74HC21 双4输入端与门 TI74HC27 三3输入端或非门 TI74HC30 8输入端与非门 TI74HC32 四2输入端或门 TI74HC42 4线-10线译码器(BCD输入) TI74HC73 DUAL J-K FLIP-FLOP TI74HC74 双上升沿D型触发器 TI74HC75 4-BIT BISTABLE LATCH TI74HC85A 四位数值比较器 TI74HC86 四2输入端异或门 TI74HC93 双4输入端与非门 TI74HC107 双主-从J-K触发器 TI74HC109 双J-K触发器 TI74HC112 双下降沿J-K触发器 TI型号器件名称厂牌[数据表]74HC123 可重触发双稳态触发器 TI74HC125 四总线缓冲器 TI74HC126 四总线缓冲器74HC132 四2输入端与非门74HC133 13-INPUT POSITIVE-NAND74HC137 地址锁存3线-8线译码器74HC138 3线-8线译码器74HC139 双2线-4线译码器74HC147 10线-4线优先编码器74HC148 8-LINE TO 3-LINE PRIORITY ENCODERS 74HC151 8-INPUT MULTIPLEXER74HC153 DUAL 4-INPUT MULTIPLEXER74HC154 4线-16线译码器74HC157 四2选1数据选择器74HC158 四2选1数据选择器74HC160 DECADE COUNTER74HC161 4位二进制同步计数器74HC162 DECADE COUNTER74HC163 4-BIT BINARY PRESETTABLE COUNTER74HC164 8位移位寄存器74HC165 8位并行输入/串行输出寄存器74HC166 8位并行输入/串行输出移位寄存器 TI,PHI 74HC173 4位D型寄存器 TI74HC174 HEX D-TYPE FLIP-FLOP WITH RESET TI74HC175 四上升沿D型触发器 TI74HC190 十进制同步加/减计数器 TI74HC191 4位二进制同步加/减计数器 TI74HC192 BCD二进制同步加/减计数器 TI型号器件名称厂牌[数据表]74HC193 可预置4位二进制加/减计数器 TI74HC194 4位并入/串入-并出/串出移位寄存 TI74HC195 4位移位寄存器 TI74HC221 双单稳态触器 TI74HC237 3-8线译码器(带地址锁存) TI74HC238 3-8线译码器 TI74HC239 双2-4线译码器74HC240 八反相缓冲/线驱动/线接收器 TI74HC241 八缓冲/线驱动/线接收器 TI74HC243 四总线收发器 TI74HC244 八缓冲/线驱动/线接收器 TI,FSC74HC245 八双向总线发送/接发器 TI,FSC74HC251 8选1数据选择器74HC253 双4选1数据选择器74HC257 四2选1数据选择器74HC258 四2选1数据选择器74HC259 8位可寻址锁存器74HC266 QUADRUPLE 2-INPUT EXCLUSIVE-NOR 74HC273 八D触发器74HC280 9位奇偶产生器/校验器 TI74HC283 4位二进制超位全加器74HC297 DIGITAL PHASE-LOCKED-LOOP74HC299 8位双向通用移位/存储寄存器型号器件名称厂牌[数据表]74HC354 带锁存三态8-1多路转换开关74HC365 六总线驱动器74HC366 六反相总线驱动器74HC367 六总线驱动器74HC368 六反相总线驱动器74HC373 六D型锁存器74HC374 六上升沿D型触发器74HC375 4-BIT BISTABLE LATCH74HC377 六上升沿D型触发器74HC378 6-BIT D-TYPE FLIP-FLOP74HC379 QUADRUPLE D-TYPE FLIP-FLOP74HC390 双十进制计数器74HC393 双4位二进制计数器74HC4002 高速CMOS双4输入端或非门74HC4015 高速CMOS双4位串入/并出移位寄存器74HC4016 高速CMOS四传输门74HC4017 高速CMOS十进制计数/分配器74HC4020 高速CMOS14级串行二进制计数/分频器74HC4024 高速CMOS7级二进制串行计数/分频器74HC4040 高速CMOS12级二进制串行计数/分频器74HC4046A 高速CMOS锁相环74HC4049 高速CMOS六反相缓冲/变换器74HC4050 高速CMOS六同相缓冲/变换器CD系列芯片功能CD4000 双3输入端或非门+单非门TICD4001 四2输入端或非门HIT/NSC/TI/GOLCD4002 双4输入端或非门NSCCD4006 18位串入/串出移位寄存器NSCCD4007 双互补对加反相器NSCCD4008 4位超前进位全加器NSCCD4009 六反相缓冲/变换器NSCCD4010 六同相缓冲/变换器NSCCD4011 四2输入端与非门HIT/TICD4012 双4输入端与非门NSCCD4013 双主-从D型触发器FSC/NSC/TOSCD4014 8位串入/并入-串出移位寄存器NSCCD4015 双4位串入/并出移位寄存器TICD4016 四传输门FSC/TICD4017 十进制计数/分配器FSC/TI/MOTCD4018 可预制1/N计数器NSC/MOTCD4019 四与或选择器PHICD4020 14级串行二进制计数/分频器FSCCD4021 08位串入/并入-串出移位寄存器PHI/NSCCD4022 八进制计数/分配器NSC/MOTCD4023 三3输入端与非门NSC/MOT/TICD4024 7级二进制串行计数/分频器NSC/MOT/TICD4025 三3输入端或非门NSC/MOT/TICD4026 十进制计数/7段译码器NSC/MOT/TICD4027 双J-K触发器NSC/MOT/TICD4028 BCD码十进制译码器NSC/MOT/TICD4029 可预置可逆计数器NSC/MOT/TICD4030 四异或门NSC/MOT/TI/GOLCD4031 64位串入/串出移位存储器NSC/MOT/TICD4032 三串行加法器NSC/TICD4033 十进制计数/7段译码器NSC/TICD4034 8位通用总线寄存器NSC/MOT/TICD4035 4位并入/串入-并出/串出移位寄存NSC/MOT/TI CD4038 三串行加法器NSC/TICD4040 12级二进制串行计数/分频器NSC/MOT/TICD4041 四同相/反相缓冲器NSC/MOT/TICD4042 四锁存D型触发器NSC/MOT/TICD4043 4三态R-S锁存触发器("1"触发) NSC/MOT/TI CD4044 四三态R-S锁存触发器("0"触发) NSC/MOT/TI CD4046 锁相环NSC/MOT/TI/PHICD4047 无稳态/单稳态多谐振荡器NSC/MOT/TICD4048 4输入端可扩展多功能门NSC/HIT/TICD4049 六反相缓冲/变换器NSC/HIT/TICD4050 六同相缓冲/变换器NSC/MOT/TICD4051 八选一模拟开关NSC/MOT/TICD4052 双4选1模拟开关NSC/MOT/TICD4053 三组二路模拟开关NSC/MOT/TICD4054 液晶显示驱动器NSC/HIT/TICD4055 BCD-7段译码/液晶驱动器NSC/HIT/TI CD4056 液晶显示驱动器NSC/HIT/TICD4059 “N”分频计数器NSC/TICD4060 14级二进制串行计数/分频器NSC/TI/MOT CD4063 四位数字比较器NSC/HIT/TICD4066 四传输门NSC/TI/MOTCD4067 16选1模拟开关NSC/TICD4068 八输入端与非门/与门NSC/HIT/TICD4069 六反相器NSC/HIT/TICD4070 四异或门NSC/HIT/TICD4071 四2输入端或门NSC/TICD4072 双4输入端或门NSC/TICD4073 三3输入端与门NSC/TICD4075 三3输入端或门NSC/TICD4076 四D寄存器CD4077 四2输入端异或非门HITCD4078 8输入端或非门/或门CD4081 四2输入端与门NSC/HIT/TICD4082 双4输入端与门NSC/HIT/TICD4085 双2路2输入端与或非门CD4086 四2输入端可扩展与或非门CD4089 二进制比例乘法器CD4093 四2输入端施密特触发器NSC/MOT/ST CD4094 8位移位存储总线寄存器NSC/TI/PHICD4095 3输入端J-K触发器CD4096 3输入端J-K触发器CD4097 双路八选一模拟开关CD4098 双单稳态触发器NSC/MOT/TICD4099 8位可寻址锁存器NSC/MOT/STCD40100 32位左/右移位寄存器CD40101 9位奇偶较验器CD40102 8位可预置同步BCD减法计数器CD40103 8位可预置同步二进制减法计数器CD40104 4位双向移位寄存器CD40105 先入先出FI-FD寄存器CD40106 六施密特触发器NSC\TICD40107 双2输入端与非缓冲/驱动器HAR\TICD40108 4字×4位多通道寄存器CD40109 四低-高电平位移器CD40110 十进制加/减,计数,锁存,译码驱动STCD40147 10-4线编码器NSC\MOTCD40160 可预置BCD加计数器NSC\MOTCD40161 可预置4位二进制加计数器NSC\MOTCD40162 BCD加法计数器NSC\MOTCD40163 4位二进制同步计数器NSC\MOTCD40174 六锁存D型触发器NSC\TI\MOTCD40175 四D型触发器NSC\TI\MOTCD40181 4位算术逻辑单元/函数发生器CD40182 超前位发生器CD40192 可预置BCD加/减计数器(双时钟) NSC\TI CD40193 可预置4位二进制加/减计数器NSC\TICD40194 4位并入/串入-并出/串出移位寄存NSC\MOT CD40195 4位并入/串入-并出/串出移位寄存NSC\MOT CD40208 4×4多端口寄存器型号器件名称厂牌备注CD4501 4输入端双与门及2输入端或非门CD4502 可选通三态输出六反相/缓冲器CD4503 六同相三态缓冲器CD4504 六电压转换器CD4506 双二组2输入可扩展或非门CD4508 双4位锁存D型触发器CD4510 可预置BCD码加/减计数器CD4511 BCD锁存,7段译码,驱动器CD4512 八路数据选择器CD4513 BCD锁存,7段译码,驱动器(消隐)CD4514 4位锁存,4线-16线译码器CD4515 4位锁存,4线-16线译码器CD4516 可预置4位二进制加/减计数器CD4517 双64位静态移位寄存器CD4518 双BCD同步加计数器CD4519 四位与或选择器CD4520 双4位二进制同步加计数器CD4521 24级分频器CD4522 可预置BCD同步1/N计数器CD4526 可预置4位二进制同步1/N计数器CD4527 BCD比例乘法器CD4528 双单稳态触发器CD4529 双四路/单八路模拟开关CD4530 双5输入端优势逻辑门CD4531 12位奇偶校验器CD4532 8位优先编码器CD4536 可编程定时器CD4538 精密双单稳CD4539 双四路数据选择器CD4541 可编程序振荡/计时器CD4543 BCD七段锁存译码,驱动器CD4544 BCD七段锁存译码,驱动器CD4547 BCD七段译码/大电流驱动器CD4549 函数近似寄存器CD4551 四2通道模拟开关CD4553 三位BCD计数器CD4555 双二进制四选一译码器/分离器CD4556 双二进制四选一译码器/分离器CD4558 BCD八段译码器CD4560 "N"BCD加法器CD4561 "9"求补器CD4573 四可编程运算放大器CD4574 四可编程电压比较器CD4575 双可编程运放/比较器CD4583 双施密特触发器CD4584 六施密特触发器CD4585 4位数值比较器CD4599 8位可寻址锁存器。

74HC74

一、简介 74HC74 是双通道可再触发、 再复位单触发多频振荡器, 是一个高速的 CMOS 集成电路, 适合于低功率的 TTL 电信号,符合 JEDEC 标准的第 7A 条款。 二、特点 宽电压输入范围:2.0~6.0V; 对称输出阻抗; 抗噪声性能强; 低功耗; 平稳的发送延迟; ESD 保护。 三、内部框图

四、引脚功能

引 脚 1 2 3 4 号 名

1R D

称

功

能

异步复位指令输入(低电平有效) 数据输入 时钟输入 异步设置指令输入(低电平有效) 触发输出主通道 触发输出补偿 地 触发输出补偿

6

7 8

9 10 11 12 13 14

2Q

触发输出主通道 异步设置指令输入(低电平有效) 时钟输入 数据输入 异步复位指令输入(低电平有效) 正电源电压

2SD

2CP 2D

2SD

VCC

74HC74DTR2G中文资料

74HC74Dual D Flip−Flop with Set and ResetHigh −Performance Silicon −Gate CMOSThe 74HC74 is identical in pinout to the LS74. The device inputs are compatible with standard CMOS outputs; with pullup resistors, they are compatible with LSTTL outputs.This device consists of two D flip −flops with individual Set, Reset,and Clock inputs. Information at a D −input is transferred to the corresponding Q output on the next positive going edge of the clock input. Both Q and Q outputs are available from each flip −flop. The Set and Reset inputs are asynchronous.Features•Output Drive Capability: 10 LSTTL Loads•Outputs Directly Interface to CMOS, NMOS, and TTL •Operating V oltage Range: 2.0 to 6.0 V •Low Input Current: 1.0 m A•High Noise Immunity Characteristic of CMOS Devices•In Compliance with the JEDEC Standard No. 7A Requirements •ESD Performance: HBM > 2000 V; Machine Model > 200 V •Chip Complexity: 128 FETs or 32 Equivalent Gates•Pb −Free Packages are AvailableMARKING DIAGRAMSHC74= Device Code A = Assembly Location L, WL = Wafer Lot Y = YearW, WW = Work Week G or G = Pb −Free PackageTSSOP −14DT SUFFIX CASE 948GSOIC −14D SUFFIX CASE 751AHC 74ALYW GG114See detailed ordering and shipping information in the package dimensions section on page 4 of this data sheet.ORDERING INFORMATION(Note: Microdot may be in either location)RESET 1DATA 1CLOCK 1SET 1RESET 2DATA 2CLOCK 2SET 2Q1Q1Q2Q2PIN 14 = V CC PIN 7 = GNDFUNCTION TABLEstates are unpredictable if Set and Reset go high simultaneously.LOGIC DIAGRAMPIN ASSIGNMENTSET 1CLOCK 1DATA 1RESET 1SET 2CLOCK 2DATA 2RESET 2V CC Q2Q2GNDQ1Q1MAXIMUM RATINGSSymbol ParameterValue Unit V CC DC Supply Voltage (Referenced to GND)– 0.5 to + 7.0V V in DC Input Voltage (Referenced to GND)– 0.5 to V CC + 0.5V V out DC Output Voltage (Referenced to GND)– 0.5 to V CC + 0.5V I in DC Input Current, per Pin ±20mA I out DC Output Current, per Pin±25mA I CC DC Supply Current, V CC and GND Pins ±50mA P D Power Dissipation in Still Air,SOIC Package†TSSOP Package†500450mW T stg Storage Temperature– 65 to + 150_C T LLead Temperature, 1 mm from Case for 10 Seconds(SOIC or TSSOP Package)260300_CStresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied.Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.†Derating —SOIC Package: – 7 mW/_C from 65_ to 125_CTSSOP Package: − 6.1 mW/_C from 65_ to 125_CFor high frequency or heavy load considerations, see Chapter 2 of the ON Semiconductor High −Speed CMOS Data Book (DL129/D).RECOMMENDED OPERATING CONDITIONSSymbol ParameterMin Max Unit V CC DC Supply Voltage (Referenced to GND)2.0 6.0V V in , V outDC Input Voltage, Output Voltage (Referenced to GND)0V CC V T A Operating Temperature, All Package Types – 55+ 125_C t r , t fInput Rise and Fall Time V CC = 2.0 V (Figures 1, 2, 3)V CC = 3.0 V V CC = 4.5 V V CC = 6.0 V00001000600500400nsThis device contains protection circuitry to guard against damage due to high static voltages or electric fields. However, precautions must be taken to avoid applications of any voltage higher than maximum rated voltages to this high −impedance cir-cuit. For proper operation, V in and V out should be constrained to the range GND v (V in or V out ) v V CC .Unused inputs must always be tied to an appropriate logic voltage level (e.g., either GND or V CC ).Unused outputs must be left open.DC ELECTRICAL CHARACTERISTICS (Voltages Referenced to GND)Symbol Parameter Test Conditions V CC(V)Guaranteed LimitUnit – 55 to25_C v85_C v 125_CV IH Minimum High−Level Input Voltage V out = 0.1 V or V CC – 0.1 V|I out| v 20 m A2.03.04.56.01.52.13.154.21.52.13.154.21.52.13.154.2VV IL Maximum Low−Level Input Voltage V out = 0.1 V or V CC – 0.1 V|I out| v 20 m A2.03.04.56.00.50.91.351.80.50.91.351.80.50.91.351.8VV OH Minimum High−Level Output Voltage V in = V IH or V IL|I out| v 20 m A2.04.56.01.94.45.91.94.45.91.94.45.9VV in = V IH or V IL|I out| v 2.4 mA|I out| v 4.0 mA|I out| v 5.2 mA3.04.56.02.483.985.482.343.845.342.23.75.2V OL Maximum Low−Level Output Voltage V in = V IH or V IL|I out| v 20 m A2.04.56.00.10.10.10.10.10.10.10.10.1VV in = V IH or V IL|I out| v 2.4 mA|I out| v 4.0 mA|I out| v 5.2 mA3.04.56.00.260.260.260.330.330.330.40.40.4I in Maximum Input Leakage Current V in = V CC or GND 6.0±0.1±1.0±1.0m AI CC Maximum Quiescent SupplyCurrent (per Package)V in = V CC or GNDI out = 0 m A6.0 2.02080m ANOTE:Information on typical parametric values can be found in Chapter 2 of the ON Semiconductor High−Speed CMOS Data Book (DL129/D).AC ELECTRICAL CHARACTERISTICS (C L = 50 pF, Input t r = t f= 6.0 ns)Symbol Parameter V CC(V)Guaranteed LimitUnit – 55 to25_C v85_C v 125_Cf max Maximum Clock Frequency (50% Duty Cycle)(Figures 1 and 4)2.03.04.56.06.01530354.81024284.08.02024MHzt PLH, t PHL Maximum Propagation Delay, Clock to Q or Q(Figures 1 and 4)2.03.04.56.01007520171259025211501203026nst PLH, t PHL Maximum Propagation Delay, Set or Reset to Q or Q(Figures 2 and 4)2.03.04.56.01058021181309526221601303227nst TLH, t THL Maximum Output Transition Time, Any Output(Figures 1 and 4)2.03.04.56.07530151395401916110552219nsC in Maximum Input Capacitance—101010pF NOTE:For propagation delays with loads other than 50 pF, and information on typical parametric values, see Chapter 2 of the ON Semiconductor High−Speed CMOS Data Book (DL129/D).C PD Power Dissipation Capacitance (Per Flip−Flop)*Typical @ 25°C, V CC = 5.0 VpF32*Used to determine the no−load dynamic power consumption: P D = C PD V CC2f + I CC V CC. For load considerations, see Chapter 2 of the ON Semiconductor High−Speed CMOS Data Book (DL129/D).TIMING REQUIREMENTS (Input t r = t f = 6.0 ns)Symbol ParameterV CC (V)Guaranteed LimitUnit – 55 to 25_C v 85_C v 125_C t suMinimum Setup Time, Data to Clock (Figure 3)2.03.04.56.080351614100452017120552420nst hMinimum Hold Time, Clock to Data (Figure 3)2.03.04.56.0 3.03.03.03.0 3.03.03.03.0 3.03.03.03.0nst recMinimum Recovery Time, Set or Reset Inactive to Clock (Figure 2)2.03.04.56.08.08.08.08.08.08.08.08.08.08.08.08.0nst wMinimum Pulse Width, Clock (Figure 1)2.03.04.56.0602512107530151390401815nst wMinimum Pulse Width, Set or Reset (Figure 2)2.03.04.56.0602512107530151390401815nst r , t fMaximum Input Rise and Fall Times (Figures 1, 2, 3)2.03.04.56.0100080050040010008005004001000800500400nsORDERING INFORMATIONDevicePackage Shipping †74HC74D SOIC −1455 Units / Rail 74HC74DG SOIC −14(Pb −Free)74HC74DR2SOIC −142500 / Tape & Reel 74HC74DR2G SOIC −14(Pb −Free)74HC74DTR2TSSOP −14*74HC74DTR2GTSSOP −14*†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.*This package is inherently Pb −Free.SWITCHING WAVEFORMSSETDATARESETFigure 5. EXPANDED LOGIC DIAGRAMSOIC −14CASE 751A −03ISSUE HNOTES:1.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.2.CONTROLLING DIMENSION: MILLIMETER.3.DIMENSIONS A AND B DO NOT INCLUDE MOLD PROTRUSION.4.MAXIMUM MOLD PROTRUSION 0.15 (0.006)PER SIDE.5.DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127(0.005) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION.DIM MIN MAX MIN MAX INCHESMILLIMETERS A 8.558.750.3370.344B 3.80 4.000.1500.157C 1.35 1.750.0540.068D 0.350.490.0140.019F 0.40 1.250.0160.049G 1.27 BSC 0.050 BSC J 0.190.250.0080.009K 0.100.250.0040.009M 0 7 0 7 P 5.80 6.200.2280.244R0.250.500.0100.019____DIMENSIONS: MILLIMETERS*For additional information on our Pb −Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.TSSOP −14CASE 948G −01ISSUE BDIM MIN MAX MIN MAX INCHESMILLIMETERS A 4.90 5.100.1930.200B 4.30 4.500.1690.177C −−− 1.20−−−0.047D 0.050.150.0020.006F 0.500.750.0200.030G 0.65 BSC 0.026 BSC H 0.500.600.0200.024J 0.090.200.0040.008J10.090.160.0040.006K 0.190.300.0070.012K10.190.250.0070.010L 6.40 BSC 0.252 BSC M0 8 0 8 NOTES:1.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.2.CONTROLLING DIMENSION: MILLIMETER.3.DIMENSION A DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS.MOLD FLASH OR GATE BURRS SHALL NOT EXCEED 0.15 (0.006) PER SIDE.4.DIMENSION B DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION.INTERLEAD FLASH OR PROTRUSION SHALL NOT EXCEED 0.25 (0.010) PER SIDE.5.DIMENSION K DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.08(0.003) TOTAL IN EXCESS OF THE K DIMENSION AT MAXIMUM MATERIAL CONDITION.6.TERMINAL NUMBERS ARE SHOWN FOR REFERENCE ONLY .7.DIMENSION A AND B ARE TO BE DETERMINED AT DATUM PLANE −W −.____14X REF K14X0.360.65PITCHSOLDERING FOOTPRINT**For additional information on our Pb −Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.“Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.PUBLICATION ORDERING INFORMATION。

74HC74中文资料_数据手册_参数

74HC74宽工作电压范围2 V 6 VD输出可以开车10 LSTTL LoadsD低功耗,40-µA马克斯ICCD典型信息= 15 nsD±4-mA输出驱动VD低输入电 流的5点1µA Maxdescription /订购informationThe HC74设备包含两个independentD-type positive-edge-triggered拖鞋。74HC74在预置(PRE)或 清除(CLR)输入设置或重置输出的低电平,而不考虑其他输入的电平。当PRE和CLR处于非活动状态(高)时,满足setuptime要求的数据 (D)输入处的数据被传输到时钟(CLK)脉冲正向边缘的输出端。时钟触发发生在电压水平,与CLK的上升时间没有直接关系。在保持时间 间隔之后,可以在不影响输出电平的情况下更改输入端的数据。订购包图纸,标准包装数量,74HC74热数据,符号,和PCB设计指南超 过“绝对最大额定值”下列出的应力可能对设备造成永久性损坏。这些只是应力等级,设备在这些或任何其他条件下的功能运行,超 出“推荐操作条件”的指示,是不受限制的。长时间暴露在绝对最大额定条件下可能会影响设备的可靠性。如果观察输入和输出电流额 定值,可能会超过输入和输出电压额定值。封装热阻抗按JESD 5计算环保(RoHS &没有某人/ Br): TI定义“绿色”意味着“Pb-Free”,此 外,使用包装材料,不含卤素,包括溴(Br)或锑(某人)总数的0.1%以上产品的重量。(3)实验室,峰值温度。湿度敏感性级别评级根据 JEDECindustry标准分类和soldertemperature峰值。重要信息和免责声明:本页所提供的信息代表德州仪器自提供之日起的知识和信念。TI 的知识和信念基于第三方提供的信息,对于这些信息的准确性不作任何陈述或保证。74HC74目前正在努力更好地整合来自第三方的信 息。TI已采取并将继续采取合理措施,提供具有代表性和准确的信息,但可能未对来料和化学品进行破坏性测试或化学分析。TI和TI供 应商认为某些信息是专有的,因此CAS号码和其他有限的信息可能无法发布。在任何情况下,TI因该等信息而产生的责任都不应超过 TIto客户在本文件中每年销售的TI部件的采购总价

74ls74中文资料

74ls74中文资料74LS74内含两个独立的D上升沿双d触发器,每个触发器有数据输入(D)、置位输入()复位输入()、时钟输入(CP)和数据输出(Q、)。

、的低电平使输出预置或清除,而与其它输入端的电平无关。

当、均无效(高电平式)时,符合建立时间要求的D数据在CP上升沿作用下传送到输出端。

74ls74功能表:输入输出S D R D CP D Qn+1 Qn+10 1 ×× 1 01 0 ××0 10 0 ××φ φ1 1 ↑ 1 1 01 1 ↑0 0 11 1 ↓×Qn Qn图1 74ls74引脚图实验:用74LS74构成4位寄存器一个D触发器可实现一位二进数的存储,因此应采用4个D触发器实现4位寄存器。

由于要实现移位寄存,4个D触发器之间应相互联接。

(1)首先在图2中完成相应的联线,构成可实现并入并出、串入串出、并入串出、串入并出的多功能移位寄存。

按图接好电路。

(2) D3 D2 D1 D0分别接逻辑开关,Q3 Q2 Q1 Q0接发光二极管;(3) 先清零;(4) 按下列要求,实现相应功能,观察结果,并描述工作过程。

并入并出:使数据输入端D3D2D1D0=1011,给CP端输入一个正单脉冲,观察Q3Q2Q1Q0发光二极管的状态,、将结果填入表中。

并入串出:使数据输入端D3D2D1D0=1011,给CP端输入4个正单脉冲,观察Q3端发光二极管的状态,将结果填入表6中。

串入并出:使数据输入端D0分别为1011,同时通过给CP端输入正单脉冲将D0端的4 个数据送入寄存器。

观察Q3Q2Q1Q0端发光二极管的状态,将结果填入表中。

串入串出:使数据输入端D0分别为1011,同时通过给CP端输入正单脉冲,将D0端的4 个数据送入寄存器。

在CP端输完8个脉冲后,观察Q3端发光二极管的状态,将结果填入表2中。

并入并出:D3D2D1D0=10111个CP脉冲Q3Q2Q1Q0=结论:并入串出D3D2D1D0=10114个CP脉冲Q3=结论串入并出D3=10114个CP脉冲Q3Q2Q1Q0=结论串入串出D3=10118个CP脉冲Q3=结论图274ls153芯片管脚图引脚逻辑功能以及封装2007年12月17日 23:53 本站原创作者:本站用户评论()关键字:74ls153管脚图逻辑功能图封装:74LS163引脚功能表及管脚定义图(带时序波形图)发布:2011-08-30 | 作者: | 来源: huangjiapeng| 查看:2620次 | 用户关注:定时器由与系统秒脉冲(由时钟脉冲产生器提供)同步的计数器构成,要求计数器在状态信号ST作用下,首先清零,然后在时钟脉冲上升沿作用下,计数器从零开始进行增1计数,向控制器提供模5的定时信号TY和模25的定时信号TL。

74hc74中文资料

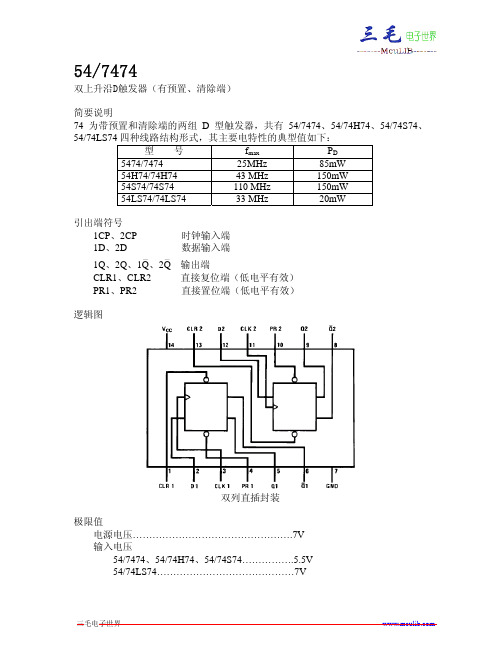

双上升沿D触发器(有预置、清除端)

简要说明

74 为带预置和清除端的两组 D 型触发器,共有 54/7474、54/74H74、54/74S74、

54/74LS74 四种线路结构形式,其主要电特性的典型

5474/7474

25MHz

85mW

54H74/74H74

43 MHz

VI=5.5V(‘LS74 为 PR,CLR

1

1

1

0.2

7V)

IIH 输 入 高 电 平 电 流

Vcc=最大

VIH=2.4V(‘S74 和’LS74 为 2.7V)

D CLR PR CP

40

50

50

120

150

150

80

100

100

80

100

100

20

40 40

uA

20

IIL输入低电平电 流

Vcc=最大 VIL=0.4V(‘S74 为

三毛电子世界

13.5

40

tPLH CP-Q

tPHL

_

CP-Q

25

15

9

25 ns

40

20

9

40

[2]:fmax-最大时钟频率,tPLH输出由低到高传输延迟时间,tPHL输出由高到低传输延迟时间

[3]:测tPHL(PR-Q_ ,CLR-Q),CP(H)时tPHL最大值为 13.5ns,CP(L)时tPHL最大值为 8ns

三毛电子世界

工作环境温度 54XXX …………………………………. -55~125℃ 74XXX …………………………………. 0~70℃

存储温度 ………………………………………….-65~150℃

74和cd系列详细资料

常用74系列标准数字电路的中文名称资料器件代号器件名称74 74LS 74HC00 四2输入端与非门√ √ √01 四2输入端与非门(OC) √ √02 四2输入端或非门√ √ √03 四2输入端与非门(OC) √ √04 六反相器√ √ √05 六反相器(OC) √ √06 六高压输出反相器(OC,30V) √ √07 六高压输出缓冲,驱动器(OC,30V) √ √ √08 四2输入端与门√ √ √09 四2输入端与门(OC) √ √ √10 三3输入端与非门√ √ √11 三3输入端与门√ √12 三3输入端与非门(OC) √ √ √13 双4输入端与非门√ √ √14 六反相器√ √ √15 三3输入端与门(OC) √ √16 六高压输出反相器(OC,15V) √17 六高压输出缓冲,驱动器(OC,15V) √20 双4输入端与非门√ √ √21 双4输入端与门√ √ √22 双4输入端与非门(OC) √ √25 双4输入端或非门(有选通端) √ √ √26 四2输入端高压输出与非缓冲器√ √ √27 三3输入端或非门√ √ √28 四2输入端或非缓冲器√ √ √30 8输入端与非门√ √ √32 四2输入端或门√ √ √33 四2输入端或非缓冲器(OC) √ √37 四2输入端与非缓冲器√ √38 四2输入端与非缓冲器(OC) √ √40 双4输入端与非缓冲器√ √ √42 4线-10线译码器(BCD输入) √ √43 4线-10线译码器(余3码输入) √44 4线-10线译码器(余3葛莱码输入) √48 4线-7段译码器√49 4线-7段译码器√50 双2路2-2输入与或非门√ √ √51 2路3-3输入,2路2-2输入与或非门√ √ √52 4路2-3-2-2输入与或门√53 4路2-2-2-2输入与或非门√54 4路2-3-3-2输入与或非门√ √55 2路4-4输入与或非门√60 双4输入与扩展器√ √61 三3输入与扩展器√62 4路2-3-3-2输入与或扩展器√64 4路4-2-3-2输入与或非门√65 4路4-2-3-2输入与或非门(OC) √70 与门输入J-K触发器√71 与或门输入J-K触发器√72 与门输入J-K触发器√74 双上升沿D型触发器√ √78 双D型触发器√ √85 四位数值比较器√86 四2输入端异或门√ √ √87 4位二进制原码/反码√95 4位移位寄存器√101 与或门输入J-K触发器√102 与门输入J-K触发器√107 双主-从J-K触发器√108 双主-从J-K触发器√109 双主-从J-K触发器√110 与门输入J-K触发器√111 双主-从J-K触发器√ √112 双下降沿J-K触发器√113 双下降沿J-K触发器√114 双下降沿J-K触发器√116 双4位锁存器√120 双脉冲同步驱动器√121 单稳态触发器√ √ √122 可重触发单稳态触发器√ √ √123 可重触发双稳态触发器√ √ √125 四总线缓冲器√ √ √126 四总线缓冲器√ √ √128 四2输入端或非线驱动器√ √ √132 四2输入端与非门√ √ √常用4000系列标准数字电路的中文名称资料型号器件名称厂牌备注CD4000 双3输入端或非门+单非门TICD4001 四2输入端或非门HIT/NSC/TI/GOLCD4002 双4输入端或非门NSCCD4006 18位串入/串出移位寄存器NSCCD4007 双互补对加反相器NSCCD4008 4位超前进位全加器NSCCD4009 六反相缓冲/变换器NSCCD4010 六同相缓冲/变换器NSCCD4011 四2输入端与非门HIT/TICD4012 双4输入端与非门NSCCD4013 双主-从D型触发器FSC/NSC/TOSCD4014 8位串入/并入-串出移位寄存器NSCCD4015 双4位串入/并出移位寄存器TICD4016 四传输门FSC/TICD4017 十进制计数/分配器FSC/TI/MOTCD4018 可预制1/N计数器NSC/MOTCD4019 四与或选择器PHICD4020 14级串行二进制计数/分频器FSCCD4021 08位串入/并入-串出移位寄存器PHI/NSCCD4022 八进制计数/分配器NSC/MOTCD4023 三3输入端与非门NSC/MOT/TICD4024 7级二进制串行计数/分频器NSC/MOT/TICD4025 三3输入端或非门NSC/MOT/TICD4026 十进制计数/7段译码器NSC/MOT/TICD4027 双J-K触发器NSC/MOT/TICD4028 BCD码十进制译码器NSC/MOT/TICD4029 可预置可逆计数器NSC/MOT/TICD4030 四异或门NSC/MOT/TI/GOLCD4031 64位串入/串出移位存储器NSC/MOT/TICD4032 三串行加法器NSC/TICD4033 十进制计数/7段译码器NSC/TICD4034 8位通用总线寄存器NSC/MOT/TICD4035 4位并入/串入-并出/串出移位寄存NSC/MOT/TI CD4038 三串行加法器NSC/TICD4040 12级二进制串行计数/分频器NSC/MOT/TICD4041 四同相/反相缓冲器NSC/MOT/TICD4042 四锁存D型触发器NSC/MOT/TICD4043 4三态R-S锁存触发器("1"触发) NSC/MOT/TI CD4044 四三态R-S锁存触发器("0"触发) NSC/MOT/TI CD4046 锁相环NSC/MOT/TI/PHICD4047 无稳态/单稳态多谐振荡器NSC/MOT/TICD4048 4输入端可扩展多功能门NSC/HIT/TICD4049 六反相缓冲/变换器NSC/HIT/TICD4050 六同相缓冲/变换器NSC/MOT/TICD4051 八选一模拟开关NSC/MOT/TICD4052 双4选1模拟开关NSC/MOT/TICD4053 三组二路模拟开关NSC/MOT/TICD4054 液晶显示驱动器NSC/HIT/TICD4055 BCD-7段译码/液晶驱动器NSC/HIT/TI CD4056 液晶显示驱动器NSC/HIT/TICD4059 “N”分频计数器NSC/TICD4060 14级二进制串行计数/分频器NSC/TI/MOT CD4063 四位数字比较器NSC/HIT/TICD4066 四传输门NSC/TI/MOTCD4067 16选1模拟开关NSC/TICD4068 八输入端与非门/与门NSC/HIT/TICD4069 六反相器NSC/HIT/TICD4070 四异或门NSC/HIT/TICD4071 四2输入端或门NSC/TICD4072 双4输入端或门NSC/TICD4073 三3输入端与门NSC/TICD4075 三3输入端或门NSC/TICD4076 四D寄存器CD4077 四2输入端异或非门HITCD4078 8输入端或非门/或门CD4081 四2输入端与门NSC/HIT/TICD4082 双4输入端与门NSC/HIT/TICD4085 双2路2输入端与或非门CD4086 四2输入端可扩展与或非门CD4089 二进制比例乘法器CD4093 四2输入端施密特触发器NSC/MOT/ST CD4094 8位移位存储总线寄存器NSC/TI/PHICD4095 3输入端J-K触发器CD4096 3输入端J-K触发器CD4097 双路八选一模拟开关CD4098 双单稳态触发器NSC/MOT/TICD4099 8位可寻址锁存器NSC/MOT/STCD40100 32位左/右移位寄存器CD40101 9位奇偶较验器CD40102 8位可预置同步BCD减法计数器CD40103 8位可预置同步二进制减法计数器CD40104 4位双向移位寄存器CD40105 先入先出FI-FD寄存器CD40106 六施密特触发器NSC\TICD40107 双2输入端与非缓冲/驱动器HAR\TICD40108 4字×4位多通道寄存器CD40109 四低-高电平位移器CD40110 十进制加/减,计数,锁存,译码驱动STCD40147 10-4线编码器NSC\MOTCD40160 可预置BCD加计数器NSC\MOTCD40161 可预置4位二进制加计数器NSC\MOTCD40162 BCD加法计数器NSC\MOTCD40163 4位二进制同步计数器NSC\MOTCD40174 六锁存D型触发器NSC\TI\MOTCD40175 四D型触发器NSC\TI\MOTCD40181 4位算术逻辑单元/函数发生器CD40182 超前位发生器CD40192 可预置BCD加/减计数器(双时钟) NSC\TI CD40193 可预置4位二进制加/减计数器NSC\TICD40194 4位并入/串入-并出/串出移位寄存NSC\MOT CD40195 4位并入/串入-并出/串出移位寄存NSC\MOT CD40208 4×4多端口寄存器CD4501 4输入端双与门及2输入端或非门CD4502 可选通三态输出六反相/缓冲器CD4503 六同相三态缓冲器CD4504 六电压转换器CD4506 双二组2输入可扩展或非门CD4508 双4位锁存D型触发器CD4510 可预置BCD码加/减计数器CD4511 BCD锁存,7段译码,驱动器CD4512 八路数据选择器CD4513 BCD锁存,7段译码,驱动器(消隐)CD4514 4位锁存,4线-16线译码器CD4515 4位锁存,4线-16线译码器CD4516 可预置4位二进制加/减计数器CD4517 双64位静态移位寄存器CD4518 双BCD同步加计数器CD4519 四位与或选择器CD4520 双4位二进制同步加计数器CD4521 24级分频器CD4522 可预置BCD同步1/N计数器CD4526 可预置4位二进制同步1/N计数器CD4527 BCD比例乘法器CD4528 双单稳态触发器CD4529 双四路/单八路模拟开关CD4530 双5输入端优势逻辑门CD4531 12位奇偶校验器CD4532 8位优先编码器CD4536 可编程定时器CD4538 精密双单稳CD4539 双四路数据选择器CD4541 可编程序振荡/计时器CD4543 BCD七段锁存译码,驱动器CD4544 BCD七段锁存译码,驱动器CD4547 BCD七段译码/大电流驱动器CD4549 函数近似寄存器CD4551 四2通道模拟开关CD4553 三位BCD计数器CD4555 双二进制四选一译码器/分离器CD4556 双二进制四选一译码器/分离器CD4558 BCD八段译码器CD4560 "N"BCD加法器CD4561 "9"求补器CD4573 四可编程运算放大器CD4574 四可编程电压比较器CD4575 双可编程运放/比较器CD4583 双施密特触发器CD4584 六施密特触发器CD4585 4位数值比较器CD4599 8位可寻址锁存器CD22100 4×4×1交叉点开关。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

CD54HC74, CD74HC74, CD74HCT74

Absolute Maximum Ratings

DC Supply Voltage, VCC . . . . . . . . . . . . . . . . . . . . . . . . -0.5V to 7V DC Input Diode Current, IIK

Maximum Storage Temperature Range . . . . . . . . . .-65oC to 150oC

Maximum Lead Temperature (Soldering 10s) . . . . . . . . . . . . . 300oC

(SOIC - Lead Tips Only)

CD74HC74M

-55 to 125 14 Ld SOIC

M14.15

CD74HCT74M

-55 to 125 14 Ld SOIC

M14.15

NOTES:

1. When ordering, use the entire part number. Add the suffix 96 to obtain the variant in the tape and reel.

For VI < -0.5V or VI > VCC + 0.5V . . . . . . . . . . . . . . . . . . . . . .±20mA DC Drain Current, per Output, IO

For -0.5V < VO < VCC + 0.5V. . . . . . . . . . . . . . . . . . . . . . . . . .±25mA DC Output Diode Current, IOK

H

H

↑

H

H

L

H

H

↑

L

L

H

H

H

L

X

Q0

Q0

NOTE: H = High Level (Steady State) L = Low Level (Steady State) X = Don’t Care ↑ = Low-to-High Transition Q0 = the level of Q before the indicated input conditions were established.

12 DATA

11 CLOCK

10 SET

R D

F/F 1 CP

S

R D

F/F 2 CP

S

5 Q

6 Q

9 Q

8 Q

GND = PIN 7 VCC = PIN 14

TRUTH TABLE

INPUTS

OUTPUTS

SET

RESET

CP

D

Q

Q

L

H

X

X

H

L

H

L

X

X

L

H

L

L

X

X

H (Note 3)

H (Note 3)

• Asynchronous Set and Reset

• Complementary Outputs

• Buffered Inputs

• TTAyp=ic2a5lofCMAX = 50MHz at VCC = 5V, CL = 15pF, • Fanout (Over Temperature Range)

[ /Title (CD54H C74, CD74H C74, CD74H CT74) /Subject (Dual D FlipFlop with Set

Features

Description

• Hysteresis on Clock Inputs for Improved Noise Immunity and Increased Input Rise and Fall Times

- Standard Outputs . . . . . . . . . . . . . . . 10 LSTTL Loads - Bus Driver Outputs . . . . . . . . . . . . . 15 LSTTL Loads • Wide Operating Temperature Range . . . -55oC to 125oC

Thermal Information

Thermal Resistance (Typical, Note 4)

θJA (oC/W) θJC (oC/W)

PDIP Package . . . . . . . . . . . . . . . . . . .

90

-

SOIC Package . . . . . . . . . . . . . . . . . . . 120

TEMP. RANGE

PART NUMBER

(oC)

PACKAGE

PKG. NO.

CD54HC74F

-55 to 125 14 Ld CERDIP F14.3

CD74HC74E

-55 to 125 14 Ld PDIP

E14.3

CD74HCT74E

-55 to 125 14 Ld PDIP

E14.3

Pinout

CD54HC74, CD74HC74, CD74HCT74 (PDIP, SOIC, CERDIP) TOP VIEW

1R 1 1D 2 1CP 3 1S 4 1Q 5 1Q 6 GND 7

14 VCC 13 2R 12 2D 11 2CP 10 2S 9 2Q 8 2Q

CAUTION: These devices are sensitive to electrostatic discharge. Users should follow proper IC Handling Procedures.

3. This configuration is nonstable, that is, it will not persist when set and reset inputs return to their inactive (high) level.

2

元器件交易网

The 74HCT logic family is functionally as well as pin compatible with the standard 74LS logic family.

Ordering Information

• Significant Power Reduction Compared to LSTTL Logic ICs

Operating Conditions

Temperature Range (TA) . . . . . . . . . . . . . . . . . . . . . -55oC to 125oC Supply Voltage Range, VCC

HC Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2V to 6V HCT Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4.5V to 5.5V DC Input or Output Voltage, VI, VO . . . . . . . . . . . . . . . . . 0V to VCC Input Rise and Fall Time 2V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1000ns (Max) 4.5V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 500ns (Max) 6V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 400ns (Max)

• Balanced Propagation Delay and Transition Times

The Harris CD54HC74, CD74HC74 and CD74HCT74 utilize silicon gate CMOS technology to achieve operating speeds equivalent to LSTTL parts. They exhibit the low power consumption of standard CMOS integrated circuits, together with the ability to drive 10 LSTTL loads.

元器件交易网www.cecbLeabharlann

Data sheet acquired from Harris Semiconductor SCHS124 January 1998

CD54HC74, CD74HC74, CD74HCT74

Dual D Flip-Flop with Set and Reset Positive-Edge Trigger

This flip-flop has independent DATA, SET, RESET and CLOCK inputs and Q and Q outputs. The logic level present at the data input is transferred to the output during the positive-going transition of the clock pulse. SET and RESET are independent of the clock and are accomplished by a low level at the appropriate input.