Verilog入门

第3章 Verilog设计入门

(3)赋值符号“<=” 说明:只能用于顺序语句中

• 改错:

module mux41a (a,b,c,d,s1,s0,y) input a,b,c,d,s1,s0; output y; reg a,b,c,d; always @ * begin : mux41 case({s1,s0}) 2'b1: y=a; 2'b2: y=b; 2'b3: y=c; 2'b4: y=d; endcase endmodule

Verilog中的四种基本数值:

0:即二进制数0、低电平、逻辑0、事件为伪 的判断结果; 1:即二进制数1、高电平、逻辑1、事件为真 的判断结果; z或Z:高阻态,或高阻值,还可用“?”表示。 x或X:不确定,或未知的逻辑状态。

3.assign连续赋值语句

由assign引导的赋值语句方式也称为数据流描述方式,即当等号右侧 的驱动表达式中的任一信号发生变化时,表达式被计算一遍,赋给左 侧的目标变量;

当一个模块中有多个assign语句时,不允许有多个不同赋值表 达式,即在同一个模块中,wire型变量不允许有多个驱动源。 如果驱动表达式为高阻态,是可以允许的。

2.等式操作符

(1)当关系为真时,等式操作的结果为1,当关系为假时,结果为0; (2) ==等于操作符,两个二进制数比较必须每一位都相等,结果才为1, 否则为0,且如果其中有的位是未知值X或高阻值z都判断为假,输出0; (3)全等比较操作符===,将两个比较值当成确定的值进行比较,当表述 相同为1.

3.1.3 4选1多路选择器及其数据流描述方式

数据流描述方式:即直接用布尔逻辑表达式来描述模块的功能。

第 3 章 Verilog HDL 基础知识

第三章

Verilog 基础知识

module D_ff(q,data,enable,reset,clock); output q; input data,enable,reset,clock; reg q; always @(posedge clock) //时钟上升沿有效 if (reset == 0) q = 1’b0; else if (enable==1) q = data; //隐含: else q = q: endmodule

第三章

Verilog 基础知识

3) 指定位宽的基数格式 这种格式的表示形式为: <size>’<base_format><number> 参数<size>用来指定所表示数的位宽。当位宽小于数 值的实际位数时,相应的高位部分被忽略;当位宽大于数 值的实际位数,且数值的最高位是 0 或 1 时,相应的高位 部分补0;而当位宽大于数值的实际位数,但数值的最高 位是 x 或 z 时,相应的高位部分补 x 或z。二进制的一个 x 或 z 表示 1 位处于 x 或 z,八进制的一个 x 或 z 表示 3 位 二进制位都处于 x 或 z,十六进制的一个 x 或 z 表示 4 位 二进制位都处于 x 或 z。另外,数值中的 z 可以用“ ?” 来代替。

第三章

Verilog 基础知识

第3章

Verilog HDL 基础知识

希望通过本章的介绍,能够对 Verilog HDL 有初步 的了解。 (1)词法:包括间隔符与注释符、数值、字符串与关键字。 (2)数据类型:包括物理数据类型与抽象数据类型。 (3)运算符:包括算术运算符、逻辑运算符、关系运算 符、相等关系运算符、按位运算符、归约运算符、移 位运算符、条件运算符、连接与复制操作及其优先级。 (4)系统任务与系统函数:包括标准输出任务、文件管理 任务、仿真控制任务、时间函数及其他常用函数。 (5)编译指令:宏编译指令、文件包含指令、条件编译指 令、时间定标指令与工作库定义指令。

verilog教程

verilog教程Verilog是一种硬件描述语言(HDL),用于描述数字系统的行为和结构。

它是一种流行的HDL,广泛用于硬件设计和验证领域。

本教程将介绍Verilog的基本概念和语法,以帮助初学者入门。

一、Verilog的基本概念1.1 什么是VerilogVerilog是一种描述数字系统的语言,它可以用来描述硬件电路、验证设计的正确性以及进行电路仿真。

1.2 Verilog的应用领域Verilog广泛应用于硬件设计和验证领域,包括用于开发ASIC(应用特定集成电路)、FPGA(现场可编程门阵列)以及其他数字系统的设计。

1.3 Verilog的版本Verilog有多个版本,包括Verilog-1995、Verilog-2001以及最新的Verilog-2005、这些版本之间有一些语法和功能上的差异。

二、Verilog的语法结构2.1模块和端口在Verilog中,所有的电路描述都是由模块(module)组成的。

模块是电路的基本组成单元,可以看作是一个黑盒子,它接受一些输入,产生一些输出。

2.2信号声明在Verilog中,我们需要声明所有的输入和输出信号。

可以使用`input`和`output`关键字来声明这些信号。

2.3电路实现Verilog允许使用多种语句和结构来描述电路的行为和结构。

这些语句包括顺序语句、条件语句、循环语句以及层次结构。

2.4实例化模块在一个模块中,我们可以实例化其他的模块。

这样可以将一个大的电路拆分成多个小的模块,方便编写和测试。

三、Verilog的仿真和验证3.1静态验证Verilog语言本身提供了很多语法和语义层面的验证功能,对于语法和类型错误会有相应的提示。

3.2激励设计在进行电路验证时,我们需要为输入信号提供激励。

Verilog提供了一种称为`testbench`的特殊模块,用于生成输入信号并将其应用到待验证的电路中。

3.3波形仿真在Verilog中,我们可以使用仿真器来模拟电路的行为,并生成波形图来验证电路是否按预期工作。

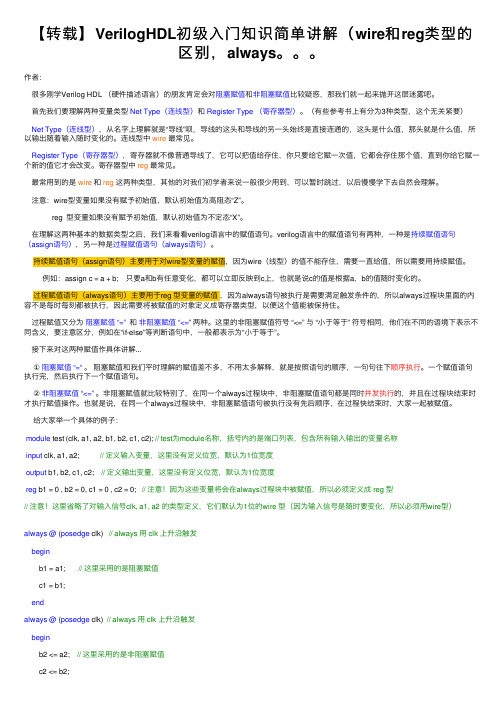

【转载】VerilogHDL初级入门知识简单讲解(wire和reg类型的区别,always。。。

【转载】VerilogHDL初级⼊门知识简单讲解(wire和reg类型的区别,always。

作者:很多刚学Verilog HDL (硬件描述语⾔)的朋友肯定会对阻塞赋值和⾮阻塞赋值⽐较疑惑,那我们就⼀起来抛开这层迷雾吧。

⾸先我们要理解两种变量类型 Net Type(连线型)和 Register Type (寄存器型)。

(有些参考书上有分为3种类型,这个⽆关紧要)Net Type(连线型),从名字上理解就是“导线”呗,导线的这头和导线的另⼀头始终是直接连通的,这头是什么值,那头就是什么值,所以输出随着输⼊随时变化的。

连线型中wire最常见。

Register Type(寄存器型),寄存器就不像普通导线了,它可以把值给存住,你只要给它赋⼀次值,它都会存住那个值,直到你给它赋⼀个新的值它才会改变。

寄存器型中reg最常见。

最常⽤到的是 wire和reg这两种类型,其他的对我们初学者来说⼀般很少⽤到,可以暂时跳过,以后慢慢学下去⾃然会理解。

注意:wire型变量如果没有赋予初始值,默认初始值为⾼阻态“Z”。

reg 型变量如果没有赋予初始值,默认初始值为不定态“X”。

在理解这两种基本的数据类型之后,我们来看看verilog语⾔中的赋值语句。

verilog语⾔中的赋值语句有两种,⼀种是持续赋值语句(assign语句),另⼀种是过程赋值语句(always语句)。

持续赋值语句(assign语句)主要⽤于对wire型变量的赋值,因为wire(线型)的值不能存住,需要⼀直给值,所以需要⽤持续赋值。

例如:assign c = a + b; 只要a和b有任意变化,都可以⽴即反映到c上,也就是说c的值是根据a,b的值随时变化的。

过程赋值语句(always语句)主要⽤于reg 型变量的赋值,因为always语句被执⾏是需要满⾜触发条件的,所以always过程块⾥⾯的内容不是每时每刻都被执⾏,因此需要将被赋值的对象定义成寄存器类型,以便这个值能被保持住。

2024版华为Verilog入门教程

目录•Verilog概述•Verilog基础语法•组合逻辑电路设计•时序逻辑电路设计•数字系统设计方法学•华为Verilog编程规范与技巧Verilog概述1 2 3Verilog语言诞生,最初用于模拟电子系统的行为。

1980年代初期Verilog逐渐发展成为硬件描述语言(HDL),用于描述数字电路和系统的结构和行为。

1980年代中期Verilog不断完善和发展,成为电子设计自动化(EDA)领域的重要标准之一,广泛应用于集成电路设计、FPGA开发等领域。

1990年代至今Verilog历史与发展集成电路设计Verilog可用于描述数字集成电路的逻辑功能、时序关系和电路结构,是IC设计领域的重要工具。

FPGA开发Verilog可用于FPGA的逻辑设计和编程,实现复杂的数字系统和算法。

ASIC设计Verilog可用于ASIC设计的各个阶段,包括逻辑设计、综合、布局布线等。

系统级建模与仿真Verilog可用于构建系统级模型,进行系统仿真和性能分析。

Verilog应用领域01Verilog 是一种硬件描述语言(HDL ),用于描述数字电路和系统的结构和行为。

02与其他硬件描述语言(如VHDL )相比,Verilog具有更接近C 语言的语法风格,易于学习和使用。

Verilog 支持多种抽象层次的描述,包括行为级、寄存器传输级(RTL )、门级和开关级,方便设计师在不同设计阶段使用。

Verilog 与硬件描述语言关系02Verilog基础语法标识符与关键字标识符用于标识变量、模块、函数等程序实体的名称,由字母、数字和下划线组成,首字符必须是字母或下划线。

关键字Verilog语言中的保留字,用于定义语言结构和控制语句,如`module`、`input`、`output`、`if`、`else`等。

数据类型与运算符数据类型包括整型(`integer`)、实型(`real`)、时间型(`time`)以及用户自定义类型等。

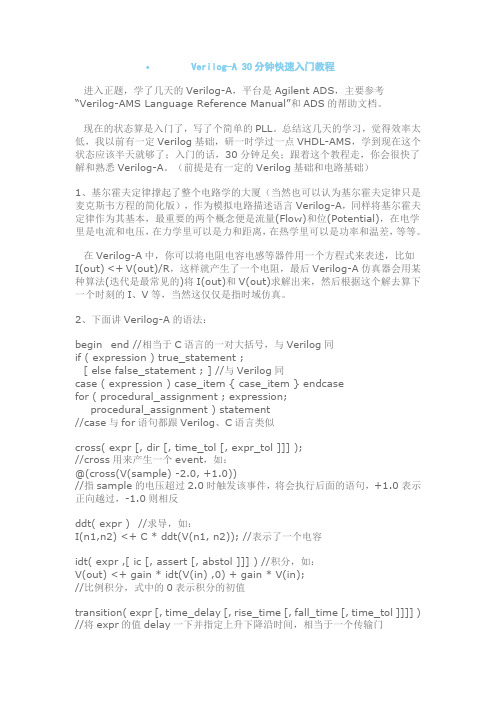

(完整word版)Verilog-A30分钟快速入门教程

•Verilog-A 30分钟快速入门教程进入正题,学了几天的Verilog-A,平台是Agilent ADS,主要参考“Verilog-AMS Language Reference Manual”和ADS的帮助文档。

现在的状态算是入门了,写了个简单的PLL。

总结这几天的学习,觉得效率太低,我以前有一定Verilog基础,研一时学过一点VHDL-AMS,学到现在这个状态应该半天就够了;入门的话,30分钟足矣;跟着这个教程走,你会很快了解和熟悉Verilog-A。

(前提是有一定的Verilog基础和电路基础)1、基尔霍夫定律撑起了整个电路学的大厦(当然也可以认为基尔霍夫定律只是麦克斯韦方程的简化版),作为模拟电路描述语言Verilog-A,同样将基尔霍夫定律作为其基本,最重要的两个概念便是流量(Flow)和位(Potential),在电学里是电流和电压,在力学里可以是力和距离,在热学里可以是功率和温差,等等。

在Verilog-A中,你可以将电阻电容电感等器件用一个方程式来表述,比如I(out) <+ V(out)/R,这样就产生了一个电阻,最后Verilog-A仿真器会用某种算法(迭代是最常见的)将I(out)和V(out)求解出来,然后根据这个解去算下一个时刻的I、V等,当然这仅仅是指时域仿真。

2、下面讲Verilog-A的语法:begin end //相当于C语言的一对大括号,与Verilog同if ( expression ) true_statement ;[ else false_statement ; ] //与Verilog同case ( expression ) case_item { case_item } endcasefor ( procedural_assignment ; expression;procedural_assignment ) statement//case与for语句都跟Verilog、C语言类似cross( expr [, dir [, time_tol [, expr_tol ]]] );//cross用来产生一个event,如:@(cross(V(sample) -2.0, +1.0))//指sample的电压超过2.0时触发该事件,将会执行后面的语句,+1.0表示正向越过,-1.0则相反ddt( expr ) //求导,如:I(n1,n2) <+ C * ddt(V(n1, n2)); //表示了一个电容idt( expr ,[ ic [, assert [, abstol ]]] ) //积分,如:V(out) <+ gain * idt(V(in) ,0) + gain * V(in);//比例积分,式中的0表示积分的初值transition( expr [, time_delay [, rise_time [, fall_time [, time_tol ]]]] ) //将expr的值delay一下并指定上升下降沿时间,相当于一个传输门laplace_zp( expr ,ζ,ρ)将expr进行拉普拉斯变换,具体表达式参看相关文献,还有laplace_zd()等数据类型:integer、real,另外就是discipline,不知道怎么翻译比较好,比如说它将电压电流这两个nature类型作为一个discipline,这些都在disciplines.vams 这个头文件里建好了,编程时要`include "disciplines.vams"。

Verilog入门

– 数据流型描述

• 通过assign连续赋值实现组合逻辑功能的描 述

第五章 Verilog 语言

Verilog HDL结构

• Verilog HDL是由module模块组成,模块定义关键词 module 开始,到关键词 endmodule结束,每条Verilog语句以分号 “;”作为结束(块语句、编译向导、endmodule等除外)

第五章 Verilog 语言

Verilog概述

• 与C语言的联系与区别

项目 C Verilog

执行顺序

时序概念 语法限制

顺序执行

无延迟 灵活完善

并行执行

存在延迟 限制严格,需 要有数字电路 的知识

第五章 Verilog 语言

Verilog概述

• 抽象层次

– 系统级:C等高级语言描述 – 行为级:模块的功能描述 – RTL级:寄存器与组合电路的合成 – 逻辑门级:基本逻辑门的组合(and, or, nand) – 开关级:晶体管开关的组合(nmos, pmos)

第五章 Verilog 语言

Verilog 语法与实例

• 基本词法定义

– 空白符 : 空格(space bar),TAB 键,return键。 – 注释 (Comment) : “//”或“/*, */”。

第五章 Verilog 语言

Verilog 语法与实例

/* 2-to-1 multiplexer; out = a when sel = 0;out = b when sel = 1; */ module MUX_2(out, a, b, sel); output out; input a, b, sel; //netlist not(sel_, sel); and(a1, a, sel_),(b1, b, sel); or(out, a1, a2); endmodule

3第3章Veri讲义log设计入门

3.1 组合电路的Verilog描述

3.1.2 4选1多路选择器及其case语句表述方式 6.赋值操作符 “<=”,只能用于顺序语句,不能用于assign引 导的并行语句 两种过程赋值操作: (1)阻塞式赋值“=”:语句执行结束,右侧表达式的值立刻赋给左侧 目标变量。 对于always引导的块语句中含有多条阻塞式赋值语句时,当执行 某一条语句时,其它语句不允许执行,被阻塞了,具有顺序执行的特点。

精品

3第3章Verilog设计入门

3.1 组合电路的Verilog描述

3.1.1 2选1多路选择器及其Verilog描述

3.1 组合电路的Verilog描述

3.1.1 2选1多路选择器及其Verilog描述

1)关键字module endmodule引导的完整的电路模块描述。 2)标识符MUX21a是用户自定义电路名,有其命名规则。 3)端口表的表述。 4)关键字input output描述电路外部端口的信号类型和流动方向。 5)关键字assign引导的赋值语句,条件语句的表述。

3.1 组合电路的Verilog描述

3.1.2 4选1多路选择器及其case语句表述方式 assign连续赋值语句的特点: ✓只能引导一条语句,多条语句要用多个assign引导; ✓并行性,当驱动表达式中的变量发生变化时,语句才被执行,否则不执行; ✓assign引导的语句中的所有信号为wire型; ✓同一目标变量名不允许有多个驱动源,例如以下表达方式不允许:

3.1 组合电路的Verilog描述

3.1.2 4选1多路选择器及其case语句表述方式

3.1 组合电路的Verilog描述

3.1.2 4选1多路选择器及其case语句表述方式 5.并位操作和数字表达

第1章 Verilog HDL入门简介

Verilog HDL数字系统设计及仿真

数字电路的回忆—七进制计数器

Verilog HDL数字系统设计及仿真

➢状态转换图

➢卡诺图

2

Verilog HDL数字系统设计及仿真

➢ Q3* 的卡诺图

➢状态方程:

Q3* Q3Q2 ' Q3 'Q2Q1

3

Verilog HDL数字系统设计及仿真

8

采用Verilog HDL代码

Verilog HDL数字系统设计及仿真

➢计数器模块

➢JK触发器模块

module

module JK_FF(J,K,CLK,Q,Qn);

Counter(Q3,Q2,Q1,C,CLK); input J,K;

output Q3,Q2,Q1,C;

input CLK;

input CLK;

output Q,Qn;

wire J1,K2,J3;

wire G3_n,G4_n,G5_n,G6_n,G7_n,G8_n;

nand G7(G7_n,Qn,J,CLK);

JK_FF JK1(Q1,Q1n,J1,1,CLK);nand G8(G8_n,CLK,K,Q);

JK_FF JK2(Q2, ,Q1,K2,CLK); nand G5(G5_n,G8_n,G6_n);

nand G1(Q,G3_n,Qn);

or or1(K2,Q1,Q3);

nand G2(Qn,Q,G4_n);

endmodule

not G9(CLK_n,CLK);

endmodule

9

Verilog HDL数字系统设计及仿真

➢更简洁的代码

module Counter(Q,CLK,RESET);

verilog语法入门

模块的测试

测试模块常见的形式:

module t; reg …; //被测模块输入/输出变量类型定义 wire…; //被测模块输入/输出变量类型定义 initial begin …; …; …; end … …//产生测试信号 always #delay begin …; end … …//产生测试信号

语法详细讲解

编译引导语句

使用`define 编译引导能提供简单的文本替代功能 `define <宏名> <宏文本> 在编译时会用宏文本来替代源代码中的宏名。 合理地使用`define可以提高程序的可读性

举例说明:

`define on 1’b1 `define off 1’b0 `define and_delay #3 在程序中可以用有含义的文字来表示没有意思的数码提高了程序 的可读性,在程序中可以用 `on, `off, `and_delay 分别表 示 1,0,和 #3 。

语法详细讲解

编译引导语句

编译引导语句用主键盘左上角小写键 “ ` ” 起头 用于指导仿真编译器在编译时采取一些特殊处理 编译引导语句一直保持有效,直到被取消或重写 `resetall 编译引导语句把所有设置的编译引导恢复到 缺省状态 常用的编译引导有: a) `define b) `include c) `timescale d) `uselib e) `resetall ……..

语法详细讲解

特殊符号 “#”

特殊符号 “#” 常用来表示延迟:

在过程赋值语句时表示延迟。 例:initial begin #10 rst=1; #50 rst=0; end 在门级实例引用时表示延迟。 例:not #1 not1(nsel, sel); and #2 and2(a1, a, nsel); 在模块实例引用时表示参数传递 介绍参数类型变量时再讲。。。。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第五章 Verilog 语言

例: module MUX_2(out, a, b, sel); output out; input a, b, sel; not U0(sel_, sel); and U1(a1, a, sel_), and U2(b1, b, sel); or U3(out, a1, a2); endmodule

例: wire net1; wand net2; tri [15:0] bus_in; wand [0:31] bus_a, bus_b; 当沒指定 net 是何种 type 时,Verilog 会以 default 值

来设定,default 为一位的 wire型

第五章 Verilog 语言

Verilog 语法与实例

第五章 Verilog 语言

• `define

`define <name> <macro_text> 例: `define ADD 3’h0 `define SUB 3’h1 .... case(opcode) `ADD:.... `SUB:..... end case • 例: `include “user_define_task.v” • `timescale 例: `timescale <time unit>/<time precision> `include

wand,triand 多重驱动时,具有线与特性的连线 trireg 具有电荷保持特性的连线 tri1 tri0 supply1 supply0 具有弱上拉电阻的连线 具有弱下拉电阻的连线 电源线,逻辑 1 地线,逻辑 0

第五章 Verilog 语言

Verilog 语法与实例

• 连线型变量声明:

<net type> <[msb:lsb]> <delay> <net name> <, <net name>>*;

第五章 Verilog 语言

Verilog概述

• Verilog 语言的描述风格

– 行为描述

描 述 复 杂 度 • 只对系统行为与功能进行描述,不涉及时序 电路实现,是一种高级语言描述的方法,有 很强的通用性

– 结构型描述

• 描述实体连接的结构形式,通过实例描述, 将verilog已定义的基本实例嵌入到语言中

第五章 Verilog 语言

例: `timescale 10ns / 1ps module MUX2(out, a, b, sel); output out; input a, b, sel; not #3 not1(sel_, sel); // delay 3个10ns ... endmodule

第五章 Verilog 语言

Verilog概述

• Verilog是在C语言的基础上发展起来的一种 硬件描述语言 • 由Gateway Automation 于1983年首创,并于 1995年成为IEEE标准,即IEEE standard 1364

第五章 Verilog 语言

Verilog概述

• 支持不同抽象层次的精确描述以及混合模拟,如 行为级、 RTL级、开关级等 • 设计、测试、模拟所用的语法都相同 • 较高层次的描述与具体工艺无关 • 提供了类似C语言的高级程序语句,如if-else, for, while, break, case,loop以及int等数据类型 • 提供了算术、逻辑、位操作等运算符 • 包含完整的组合逻辑元件,如and、or、xor等, 无需自行定义 • 支持元件门级延时和元件门级驱动强度(nmos, pmos)

module var_mux (out, a, b, sel); parameter width = 8, delay = 3; output [width-1:0] out; input [width-1:0] a, b; input sel; assign #delay out = sel ? a : b;

第五章 Verilog 语言

Verilog 语法与实例

• 数字表示:整数,实数 整数:+/- <位宽> ‘<基数符号> <数值>

<位宽>:指定整数的大小,以bit为单位。

<基数符号>:指定整数的基数,可以是b(binary)二进

制;o(octal)八进制;d(decimal)十进制;h(hex-

adecimal)十六进制。

第五章 Verilog 语言

可编程逻辑器件应用实践

孙涛 ise_sunt@

第五章 Verilog 语言

主要内容

• 目的:

– 通过具体实例讲解Verilog 的语法,快速掌握 Verilog的语法与结构

• 内容:

1. Verilog概述 2. Verilog HDL结构 3. Verilo :通过过程赋值语句赋值 • 电荷保持作用:在下一次赋值之前保持不变 • 对应硬件:触发器、锁存器

第五章 Verilog 语言

Verilog 语法与实例

连线类

Net Types wire, tri wor, trior Function 标准连线(default) 多重驱动时,具有线或特性的连线

第五章 Verilog 语言

Verilog概述

• 与C语言的联系与区别

项目 C Verilog

执行顺序

时序概念 语法限制

顺序执行

无延迟 灵活完善

并行执行

存在延迟 限制严格,需 要有数字电路 的知识

第五章 Verilog 语言

Verilog概述

• 抽象层次

– 系统级:C等高级语言描述 – 行为级:模块的功能描述 – RTL级:寄存器与组合电路的合成 – 逻辑门级:基本逻辑门的组合(and, or, nand) – 开关级:晶体管开关的组合(nmos, pmos)

endmodule

第五章 Verilog 语言

Verilog 语法与实例

• 模拟时间定标`timescale `timescale <计时单位>/<计时精度> 例:`timescale 1ns/100ps

– 合法的整数:1、10、100 – 合法时间单位:s、ms、µs、ns、ps、fs

not, and, or, xor, nor begin, end

第五章 Verilog 语言

Verilog 语法与实例

• 特殊字符: $,#,`

– $:以$开头的标识符代表系统命令 $time:返回目前的仿真时间 $display:显示出信号的值 $stop:停止仿真 –# not #3 not1(sel_, sel);// instance delay – ` `define,`include,`timescale

<数值>:指定整数的值。

第五章 Verilog 语言 整数:

17 //位宽, 基数符号不写会采用default值 (32bit十进制) 8’d32 //8-bit十进制值为32 8’h12 8’h1A 8’b0001_1100 /* ”_”无特別意义,只是为了方便二进制数易读*/ 8’o37 32’bx // ”x”表unknown 4’b0??? // ”?”表High impedance

– 数据流型描述

• 通过assign连续赋值实现组合逻辑功能的描 述

第五章 Verilog 语言

Verilog HDL结构

• Verilog HDL是由module模块组成,模块定义关键词 module 开始,到关键词 endmodule结束,每条Verilog语句以分号 “;”作为结束(块语句、编译向导、endmodule等除外)

module module_name(Port_list) 端口声明; 数据类型声明; 电路描述; endmodule

例:上升沿D触发器

module dff_pos(data,clk,q); input data,clk; //端口声明 output q; //端口声明 reg q; //数据类型声明 always @(posedge clk) q=data;//电路描述 endmodule

第五章 Verilog 语言

Verilog 语法与实例

• 基本词法定义

– 空白符 : 空格(space bar),TAB 键,return键。 – 注释 (Comment) : “//”或“/*, */”。

第五章 Verilog 语言

Verilog 语法与实例

/* 2-to-1 multiplexer; out = a when sel = 0;out = b when sel = 1; */ module MUX_2(out, a, b, sel); output out; input a, b, sel; //netlist not(sel_, sel); and(a1, a, sel_),(b1, b, sel); or(out, a1, a2); endmodule

– 连线类(Net):反映硬件电路的物理连接特 性的变量 – 寄存器类(Register):具有数据存储特性的 变量

第五章 Verilog 语言

Verilog 语法与实例

• 连线型与寄存器型区别:

– 连线型:

• • • • • 驱动方式(赋值方式): 连接到一个门或模块的输出端; 用assign赋值 电荷保持作用:没有电荷保持作用,未被驱动时将处于高阻态 对应硬件:物理信号连接

第五章 Verilog 语言

Verilog 语法与实例

• Verilog的四种逻辑状态: 0:逻辑零、逻辑非、低电平 1:逻辑1、逻辑真、高电平 x或X:不定态 z或Z:高阻态

第五章 Verilog 语言

Verilog 语法与实例