MCU 晶体振荡电路的设计

单片机晶振电路原理及作用_单片机晶振电路设计方案

单片机晶振电路原理及作用_单片机晶振电路设计在电子学上,通常将含有晶体管元件的电路称作“有源电路”(如有源音箱、有源滤波器等),而仅由阻容元件组成的电路称作“无源电路”。

电脑中的晶体振荡器也分为无源晶振和有源晶振两种类型。

无源晶振与有源晶振的英文名称不同,无源晶振为crystal(晶体),而有源晶振则叫做oscillator(振荡器)。

无源晶振是有2个引脚的无极性元件,需要借助于时钟电路才能产生振荡信号,自身无法振荡起来,所以“无源晶振”这个说法并不准确;有源晶振有4只引脚,是一个完整的振荡器,其中除了石英晶体外,还有晶体管和阻容元件,因此体积较大。

有源晶振有源晶振通常的用法:一脚悬空,二脚接地,三脚接输出,四脚接电压。

有源晶振不需要DSP的内部振荡器,信号质量好,比较稳定,而且连接方式相对简单(主要是做好电源滤波,通常使用一个电容和电感构成的PI型滤波网络,输出端用一个小阻值的电阻过滤信号即可),不需要复杂的配置电路。

相对于无源晶体,有源晶振的缺陷是其信号电平是固定的,需要选择好合适输出电平,灵活性较差,而且价格高。

有源晶振是右石英晶体组成的,石英晶片之所以能当为振荡器使用,是基于它的压电效应:在晶片的两个极上加一电场,会使晶体产生机械变形;在石英晶片上加上交变电压,晶体就会产生机械振动,同时机械变形振动又会产生交变电场,虽然这种交变电场的电压极其微弱,但其振动频率是十分稳定的。

当外加交变电压的频率与晶片的固有频率(由晶片的尺寸和形状决定)相等时,机械振动的幅度将急剧增加,这种现象称为“压电谐振”。

压电谐振状态的建立和维持都必须借助于振荡器电路才能实现。

图3是一个串联型振荡器,晶体管T1和T2构成的两级放大器,石英晶体XT与电容C2构成LC 电路。

在这个电路中,石英晶体相当于一个电感,C2为可变电容器,调节其容量即可使电路进入谐振状态。

该振荡器供电电压为5V,输出波形为方波。

单片机的内部时钟与外部时钟单片机有内部时钟方式和外部时钟方式两种:(1)单片机的XTAL1和XTAL2内部有一片内振荡器结构,但仍需要在XTAL1和XTAL2两端连接一个晶振和两个电容才能组成时钟电路,这种使用晶振配合产生信号的方法是内部时钟方式;(2)单片机还可以工作在外部时钟方式下,外部时钟方式较为简单,可直接向单片机XTAL1引脚输入时钟信号方波,而XTAL2管脚悬空。

单片机晶振电路详解

单片机晶振电路详解

晶振电路晶振是晶体振荡器的简称在电气上它可以等效成一个电容和一个电阻并联再串联一个电容的二端网络电工学上这个网络有两个谐振点以频率的高低分其中较低的频率是串联谐振较高的频率是并联谐振由于晶体自身的特性致使这两个频率的距离相当的接近在这个极窄的频率范围内晶振等效为一个电感所以只要晶振的两端并联上合适的电容它就会组成并联谐振电路这个并联谐振电路加到一个负反馈电路中就可以构成正弦波振荡电路由于晶振等效为电感的频率范围很窄所以即使其他元件的参数变化很大这个振荡器的频率也不会有很大的变化晶振有一个重要的参数那就是负载电容值选择与负载电容值相等的并联电容就可以得到晶振标称的谐振频率

一般的晶振振荡电路都是在一个反相放大器(注意是放大器不是反相器)的两

端接入晶振再有两个电容分别接到晶振的两端每个电容的另一端再接到地这两个电容串联的容量值就应该等于负载电容请注意一般IC 的引脚都有等效输入电容这个不能忽略

一般的晶振的负载电容为15pF 或12.5pF 如果再考虑元件引脚的等效输入电容则两个22pF 的电容构成晶振的振荡电路就是比较好的选择

如上图:晶振是给单片机提供工作信号脉冲的这个脉冲就是单片机的工作速度比如12M 晶振单片机工作速度就是每秒12M 当然单片机的工作频率是有范围的不能太大一般24M 就不上去了不然不稳定

晶振与单片机的脚XTAL0 和脚XTAL1 构成的振荡电路中会产生偕波(也就

是不希望存在的其他频率的波) 这个波对电路的影响不大但会降低电路的时钟振荡器的稳定性为了电路的稳定性起见ATMEL 公司只是建议在晶振的两引脚处接入两个10pf-50pf 的瓷片电容接地来削减偕波对电路的稳定性的影响所。

单片机晶振电路原理图

单片机晶振电路原理图

单片机晶振电路的原理图如下:

[晶振电路原理图]

在原理图中,我们可以看到一个晶振元件被连接到一个单片机上。

晶振元件包括四个引脚:两个供电引脚(VCC和GND),一个输出引脚(OUT),以及一个输入引脚(IN)。

VCC和GND引脚分别连接到单片机的供电电源,用于为晶振

元件提供电源。

OUT引脚连接到单片机的晶振输入引脚,用

于向单片机提供晶振信号。

IN引脚则连接到单片机的晶振输

出引脚,用于接收单片机的反馈信号。

晶振元件起到了一个产生稳定的振荡频率的作用。

当VCC和GND引脚被连接到电源后,晶振元件开始振荡,将振荡信号

通过OUT引脚输出。

单片机接收到这个振荡信号后,会根据

反馈信号通过IN引脚调整晶振元件的振荡频率,从而保持稳

定的振荡。

通过晶振电路,单片机能够根据振荡信号来确定时间的基准,进而实现各种功能。

这是单片机工作的基础。

晶体振荡器电路+PCB布线设计指南

AN2867应用笔记ST微控制器振荡器电路设计指南前言大多数设计者都熟悉基于Pierce(皮尔斯)栅拓扑结构的振荡器,但很少有人真正了解它是如何工作的,更遑论如何正确的设计。

我们经常看到,在振荡器工作不正常之前,多数人是不愿付出太多精力来关注振荡器的设计的,而此时产品通常已经量产;许多系统或项目因为它们的晶振无法正常工作而被推迟部署或运行。

情况不应该是如此。

在设计阶段,以及产品量产前的阶段,振荡器应该得到适当的关注。

设计者应当避免一场恶梦般的情景:发往外地的产品被大批量地送回来。

本应用指南介绍了Pierce振荡器的基本知识,并提供一些指导作法来帮助用户如何规划一个好的振荡器设计,如何确定不同的外部器件的具体参数以及如何为振荡器设计一个良好的印刷电路板。

在本应用指南的结尾处,有一个简易的晶振及外围器件选型指南,其中为STM32推荐了一些晶振型号(针对HSE及LSE),可以帮助用户快速上手。

目录ST微控制器振荡器电路设计指南目录1石英晶振的特性及模型32振荡器原理53Pierce振荡器64Pierce振荡器设计74.1反馈电阻R F74.2负载电容C L74.3振荡器的增益裕量84.4驱动级别DL外部电阻R Ext计算84.4.1驱动级别DL计算84.4.2另一个驱动级别测量方法94.4.3外部电阻R Ext计算 104.5启动时间104.6晶振的牵引度(Pullability) 10 5挑选晶振及外部器件的简易指南 11 6针对STM32™微控制器的一些推荐晶振 126.1HSE部分126.1.1推荐的8MHz晶振型号 126.1.2推荐的8MHz陶瓷振荡器型号 126.2LSE部分12 7关于PCB的提示 13 8结论141 石英晶振的特性及模型石英晶体是一种可将电能和机械能相互转化的压电器件,能量转变发生在共振频率点上。

它可用如下模型表示:图1石英晶体模型C0:等效电路中与串联臂并接的电容(译注:也叫并电容,静电电容,其值一般仅与晶振的尺寸有关)。

如何设计一个基本的振荡电路

如何设计一个基本的振荡电路振荡电路是电子领域中常见的电路之一,用于产生稳定的交流信号。

本文将介绍如何设计一个基本的振荡电路,并给出详细的步骤和注意事项。

1. 确定振荡器类型首先,我们需要确定要设计的振荡电路的类型。

常见的振荡器类型包括晶体振荡器、RC振荡器和LC振荡器等。

不同的振荡器类型适用于不同的应用,因此在设计之前要明确振荡器的使用目的。

2. 选择频率和波形确定振荡电路所需要产生的频率和波形。

频率决定了振荡器的工作范围,而波形则影响信号的稳定性和适用性。

常见的波形包括正弦波、方波和三角波等。

3. 选择元件和数值根据所选择的振荡器类型确定所需的元件和数值。

例如,对于RC振荡器,需要选择合适的电容器和电阻器;对于LC振荡器,需要选择合适的电感和电容器。

元件的数值将直接影响振荡器的频率和稳定性,因此要根据设计要求进行合理选择。

4. 绘制电路图根据所选的元件和数值绘制振荡电路的电路图。

在绘制电路图时,应尽量使电路清晰易读,可以使用电路设计软件或手工绘制。

5. 进行仿真和调试使用电路仿真软件对所设计的振荡电路进行仿真,并进行调试和优化。

通过仿真可以评估电路的性能和稳定性,发现可能存在的问题并加以解决。

6. 制作实物电路在经过仿真调试之后,可以使用所选的元件和电路板等材料制作实物电路。

制作实物电路时要注意元件的连接方式和排布,确保电路的可靠性和稳定性。

7. 进行测试和验证制作完成后,进行测试和验证。

通过测试可以判断电路是否正常工作,是否符合设计要求。

如果测试结果不理想,需要进行进一步的调试和优化。

总结:设计一个基本的振荡电路需要经过以上的步骤,包括确定振荡器类型、选择频率和波形、选择元件和数值、绘制电路图、进行仿真和调试、制作实物电路以及进行测试和验证。

每个步骤都需要仔细考虑和详细规划,以确保设计出稳定可靠的振荡电路。

当然,在实际设计过程中还需注意电路间的互应,元器件的选型和性能的调整等一系列细节问题。

晶体震荡电路的设计与量测

在半導體製程技術的不斷提升下,產品體積大幅縮小,對功能與運算時脈卻更為要求,因此,本文以晶體震盪電路的設計與量測為題,探討相關特性與技術。

由於科技的日新月異,IC內部的複雜度與精確度較從前大幅提升,所需的時脈速度也越來越高,相對的要求時脈的穩定度與精確度也大幅提昇,如何利用晶體(Crystal)來設計與量測所需的振盪電路,已經成為一個重要的課題,以下我們分成幾個部分加以討論。

電氣特性有鑑於其晶體電氣特性的複雜,我們針對晶體的電氣特性或是振盪電路有影響的部分,做一詳細討論,由於陶瓷/晶體的電器特性相似,所以也一併討論。

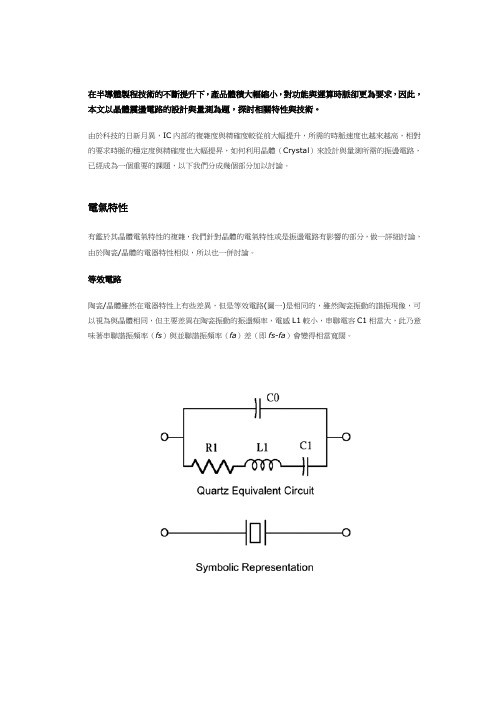

等效電路陶瓷/晶體雖然在電器特性上有些差異,但是等效電路(圖一)是相同的,雖然陶瓷振動的諧振現像,可以視為與晶體相同,但主要差異在陶瓷振動的振盪頻率,電感L1較小,串聯電容C1相當大,此乃意味著串聯諧振頻率(fs)與並聯諧振頻率(fa)差(即fs-fa)會變得相當寬闊。

圖一Crystal / Ceramic model圖二串聯共振並聯共振當晶體工作在串聯共振時,等效電路(圖二)阻抗在時是趨近於0,好的串聯共振線路設計,與負載電容無關,所以就不需要指定。

當晶體工作在並聯共振時,就像一電感在電路上,因此負載電容就非常重要,因為它可以決定振盪點的位置,如(圖三)所示。

而且電抗改變,頻率也跟隨著改變,所以在不同頻率與間,由、L1決定,在並聯線路的設計上,負載電容是需要指定的,如(圖四)所示。

圖三並聯共振頻率區域圖四並聯共振AT-CUT與BT-CUT典型的AT-CUT曲線是S形,BT-CUT曲線是拋物線形,如(圖五)所示;兩種Cut都對稱於室溫(25℃±3℃)。

在相同的頻率下,BT-CUT的Quartz blank相對的比A-CUT厚,因此提供較好的Yield 與低單價,在選擇適當的切割前,要注意的是他們所擁有的不同移動參數和頻率VS溫度特性。

圖五溫度曲線圖改變負載電容和PullabilityPullability是定義頻率與負載電容的關係,而負載電容是指與晶體串聯或是並聯的電容。

MCU晶体旁边电容的作用及振荡电路的分析

MCU晶体旁边电容的作用及振荡电路的分析Y1是晶体,相当于三点式里面的,C1和C2就是电容,5404和R1实现一个NPN的,大家可以对比高频书里的三点式电容振荡电路。

接下来分析一下这个电路。

5404必须要一个,不然它处于饱和截止区,而不是放大区,R1相当于三极管的偏置作用,让5404处于放大区域,那么5404就是一个反相器,这个就实现了NPN三极管的作用,NPN三极管在共放射极接法时也是一个反相器。

接下来用通俗的办法讲解一下这个三点式振荡电路的工作原理,大家也可以挺直看书。

大家知道一个正弦振荡电路要振荡的条件是,系统放大倍数大于1,这个简单实现,相位满足360°,接下来主要讲解这个相位问题:5404由于是反相器,也就是说实现了180°移相,那么就需要C1,C2和Y1实现180°移相就可以,恰好,当C1,C2,Y1形成谐振时,能够实现180移相,这个大家最容易的可以以地作为参考,谐振的时候,C1、C2上通过的一样,地在C1、C2中间,所以恰好相反,实现180移相。

当C1增大时,C2端的振幅增加,当C2降低时,振幅也增加。

有些时候C1,C2不焊也能起振,这个不是说没有C1,C2,而是由于芯片引脚的分布电容引起的,由于原来这个C1,C2就不需要很大,所以这一点很重要。

接下来分析这两个电容对振荡稳定性的影响。

由于7404的电压反馈是靠C2的,假设C2过大,反馈电压过低,这个也是不稳定,假设C2过小,反馈电压过高,储存能量过少,简单受外界干扰,也会辐射影响外界。

C1的作用对C2恰好相反。

由于我们布板的时候,假设双面板,比较厚的,那么分布电容的影响不是很大,假设在高密度多层板时,就需要考虑分布电容,尤其是VCO之类的振荡电路,更应当考虑分布电容。

有些用于工控的项目,建议不要用晶体的办法振荡,二是挺直接一个有源的晶振无数时候大家会用到32.768K的时钟晶体来做时钟,而不是用的晶体分频后来做时钟,这个缘由无数人想不明了,其实这个跟晶体的稳定度有关,频率越高的晶体,Q值普通难以做高,频率稳定度不高,32.768K 的晶体稳定度等各方面都不错,形成了一个工业标准,比较简单做高。

MCU晶体振荡电路的设计

应该稍微偏大(例如考虑15pF,而不是7pF)

设计安全因子SF

振荡负阻测算法:

振荡回路中插入电阻RADD 增加RADD阻值,使振荡电路显现无法起振 MHz频率级别,确保 SF >5 32KHz~500KHz ,确保 SF >3

MCU晶体振荡电路的设计

2015年9月15日 张明峰

内容简述

• 晶体原理

• 振荡电路原理

• 测量方式 • 系统设计

晶体原理

C0: 制造晶体时电极引入的并联电容 Lm: 晶体振动时表现出的感抗 Cm: 晶体振动时表现出的容抗

Rm: 晶体振动时表现出的阻抗(损耗) 考虑到Rm的值可以忽略不计,晶体的交流等效阻抗表达式为:

晶体振荡区域

FS:晶体固有串联谐振频率,Z=0 FA:晶体串联失谐频率,Z趋于无穷大

FS和FA之间阴影区为晶体并联振荡工作区 • 晶体呈现感抗 • 需要外接并联负载电容,使并联谐振

频率为晶体手册标称频率

对于给定晶体,不同的CL决定了不同的振荡频率

晶体参数实例

CL ESR C0

ESR CL

C0

典型的MCU振荡电路构成

附录

Colpitts 振荡器

标准电容三点式振荡

3361典型电路部分

晶体并联谐振电路 高频特性较好,频率干净稳定 常用于射频应用

• 陶瓷谐振器起振速度比晶体快

启动时间也受C1、C2和RX取值的影响

• 增大Rx、减小激励、增加启动时间 • C1/C2串联等效值偏离CL太多,增加启动时间

Hale Waihona Puke 晶体频率拉拽度(灵敏度)考虑

射频接收系统晶体振荡电路的设计与分析

射频接收系统晶体振荡电路的设计与分析简介采用了理论分析、工程估算、SPICE模拟以及与实际调试相结合的方法确定了射频接收系统中晶体振荡电路的结构、直流工作点及电路的元器件参数。

关键词射频晶体振荡器 SPICE模拟工程估算随着通信技术的快速发展,振荡器的研究、设计和技术得到了很大的发展。

为了适应无线寻呼接收机、FM-SCA股票机、PDA等通信产品的小型化,在射频接收电路中一本振采用了晶体振荡电路。

一、射频接收中晶体振荡电路的设计及工程估算1. 振荡电路的确定对振荡电路的选择取决于对工作频率、频率稳定度的要求,同时还要考虑射频接收小型化、低功耗及其他要求。

晶体振荡电路应设计成结构简单、功耗小、调试方便并且频率可以微调的电路。

经过分析,确定采用如图1所示的结构。

该电路为电容三点式振荡,是串联式晶体振荡电路。

图1 一本振石英晶体振荡电路原理图(1) 振荡电路原理分析图2为图1的交流等效电路,其中C16、C17、L05组成的支路相对于三次泛音晶体的基频开路,在晶体的标称频率振荡时可以不考虑。

由于振荡器的输出负载和振荡器之间是弱耦合,故也可以忽略不计。

晶振工作在串联谐振频率上,且晶振发生串联谐振时,该振荡器电路的正反馈最强,只有这时才能满足振幅条件而使电路起振。

一旦晶振工作点偏离串联谐振点,由于晶体的动态电感很大,而R09较小,则等效并联在电感和晶振两端的电阻较小,大大影响了谐振网络的Q值,使电路无法工作。

图2 交流等效电路在此电路中,电路进入集电结的饱和区而发生饱和限幅失真,集电极电流因此包含丰富的谐波分量,输出负载网络调谐在振荡回路的二次谐波上(L06和晶振支路相对于二次谐波开路),而有效抑制基波及其余各次谐波。

此种类型的振荡器可以用如图3所示的模型描述,即一个线性时不变网络(LTIN)将振荡器电路分成三部分:一个非线性有源器件、一个基波谐振网络和一个二次谐波网络。

图3 一本振石英晶体振荡器等效电路模型其中,有源器件的电流-电压转移关系可描述为:由于除了基波和二次谐波外,其他各次谐波没有可以流通的谐振回路,故为简化起见,分析时仅列出这两项(如上式所示)。

晶体振荡器外围电路设计噪声降低电路设计指南

晶体振荡器外围电路设计噪声降低电路设计指南在电子设备和通信系统的设计和布局中,必须仔细考虑晶体振荡器和外围电路,以优化性能。

作为信号源的核心,晶体振荡器必须产生很高的精度输出,因此对高频率噪声从其他的板上来说是非常敏感的。

这种电路在设计时需要明确的注意。

这些技术说明是在一些外围电路中减少噪音的设计指南,在这些电路中高频噪声对晶体振荡器的输出尤其有利。

晶体振荡器和周边电路的噪声来源首先,在图1中,我们指出了典型的由晶体振荡器和外围电路产生的噪声。

有三个主要的噪声源:1.电源线路噪声2.输出线路噪声3.晶体振荡器的噪声通常被称为“噪声”的是这三个因素的累积结果。

下面我们将对地址类型的噪声进行解释。

1。

电源线路噪声电压波纹和开关噪声通常是由电源线发出的。

这种噪声会影响晶体振荡器的输出。

此外,有必要确保晶体振荡器产生的波纹噪声不会流到电源线上。

实施这些措施还可以改善隔离,防止其他设备产生的外部噪声流入晶体振荡器,从而保证晶体振荡器的稳定性。

2。

输出线路噪声输出线噪声是指输出线作为天线的晶体振荡器输出的信号。

对于输出信号和物理跟踪,应该实现降低噪声的技术。

3。

晶体振荡器噪声晶体振荡器的噪音是指晶体振荡器内部集成电路和电路发出的噪声。

要解决这一噪声,需要确保晶体振荡器稳定的电源供应,并确保所需波形的形成,以实现晶体振荡器的稳定运行。

这些噪声源依赖于上述的原因,并可通过本文稍后所提到的功率线和输出线技术间接地减轻。

上述电源发出的噪声水平与电流和电流环路径成正比。

因此,电流或电流回路阻抗的降低会导致发射噪音的降低。

一般来说,电流和电流环路径长度与晶体振荡器及其外围电路有关。

电流量:电源线=晶体振荡器>输出线电流环大小:输出线>电源线>晶体振荡器输出线噪声对晶体振荡电路有最大的影响,其次是功率线的噪声贡献。

实际晶体振荡器所发出的噪声比其他两种来源的噪声要低得多。

[噪音对策]在这些技术说明中,我们已经研究了晶体振荡器及其外围电路中的噪声来源。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

附录

Colpitts 振荡器

3361典型电路部分

标准电容三点式振荡

晶体并联谐振电路 高频特性较好,频率干净稳定 常用于射频应用

RF反馈偏置电阻的作用

RF使片内反相器工作于图中斜线所示的线性放大区

• OSC1和OCS2偏置于VDD/2

需参考具体MCU的数据手册选择合理的阻值

例如:

负载电容CL的计算

C1/C2串联等效值

电路寄生电容

一般电路设计,CS 约为5-7pF C1和C2必须为高频特性良好低ESR的陶瓷电容(C0G材 质),取值可以不同 所得的CL必须符合晶体厂家提供的器件参数规范

启动时间也受C1、C2和RX取值的影响

• 增大Rx、减小激励、增加启动时间 • C1/C2串联等效值偏离CL太多,增加启动时间

晶体频率拉拽度(灵敏度)考虑

外接负载电容的变化所造成振荡频率变化率

设计验证后,大规模生产时电路的实际负载电容值CL会有波动

பைடு நூலகம்• C1、C2器件批量供货时参数的离散性 • 电路板分布电容的不确定性 • 芯片引脚寄生电容的不确定性

晶体振荡区域

FS:晶体固有串联谐振频率,Z=0

FS和FA之间阴影区为晶体并联振荡工作区 • • 晶体呈现感抗 需要外接并联负载电容,使并联谐振 频率为晶体手册标称频率

FA:晶体串联失谐频率,Z趋于无穷大

对于给定晶体,不同的CL决定了不同的振荡频率

晶体参数实例

ESR CL

CL ESR C0 C0

典型的MCU振荡电路构成

MCU片内置反相器,提供振荡环路增益,并产生180度相移(有些MCU可以配置反相器的 增益)

RF电阻为片内反相器提供一个线性工作区(有些MCU把RF集成在片内)

C1和C2为移相电容,每个分别产生90度移相,结合反相器的180度移相,环路总计正好是 360度移相 若不考虑实际电路存在的分布寄生电容,C1和C2的串联等效值,就是晶体并联谐振的CL 值!!! Rx为驱动衰减电阻,避免晶体过激励

等效CL的变化,会造成振荡频率的变化 (ppm/pF) 通常,为降低上述参数对振荡电路特性的影响,晶体参数的CL选取 应该稍微偏大(例如考虑15pF,而不是7pF)

设计安全因子SF

振荡负阻测算法:

振荡回路中插入电阻RADD 增加RADD阻值,使振荡电路显现无法起振 MHz频率级别,确保 SF >5 32KHz~500KHz ,确保 SF >3

MCU晶体振荡电路的设计

2015年9月15日 张明峰

内容简述 • • • • 晶体原理 振荡电路原理 测量方式 系统设计

晶体原理

C0: Lm: Cm: Rm:

制造晶体时电极引入的并联电容 晶体振动时表现出的感抗 晶体振动时表现出的容抗 晶体振动时表现出的阻抗(损耗)

考虑到Rm的值可以忽略不计,晶体的交流等效阻抗表达式为:

反相放大器输入端电容 电路寄生电容 示波器探棒接入电容(< 1pF)

Vpp为示波器所测得反相放大器输入端波形峰峰值

振荡启动时间

一般而言,晶体标称频率越高,启动时间越短:

• ~MHz频段,起振过程为几ms • 32KHz,可能需要1-5s

Q值越高,起振时间越长

• 陶瓷谐振器起振速度比晶体快

晶体激励功率DL和RX

晶体获得的激励功率:

实测振荡电路电流RMS值 参考晶体参数手册得到最大允许激励功率

• 典型值50uW-100uW • 最大值500uW~1mW

调整RX值,确保DL不超过最大值

示波器有源电流探头测IQ

晶体激励功率测算(方法2)

Ctot

• CL1 • CS • Cprobe