CPCI数据总线接口的设计与实现[图]

基于CPCI总线技术的新型雷达显控台接口设计

1硬 件 组 成

交换 的过 程 中,数据传 输速 率低 、误码 率 高等 问题

一

由于 设计 实 现 了雷 达 系 统 控 制 信 息 和 状 态 信 息 的

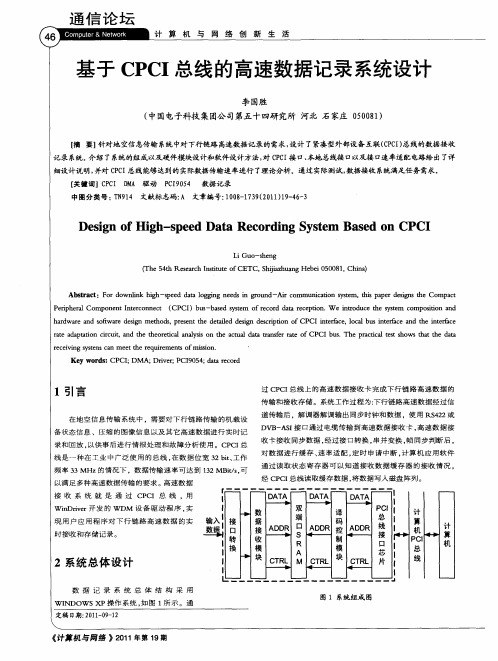

综 合传 输 ,因此称 其为 多功 能接 口板 。该板 的硬件 原理如 图 1 所示 。 其 中,P I9 5 C 0 4是美 国 P X 公 司生产 的先 进 L 的P I C 总线接 口芯片 ,它满 足 P I 22协议 ,支 持 C . v 3 bt3 2 i MHz时钟 P I 线 ,特 别适 合于 P I 线 3 C 总 C 总 外 设产 品开 发 。

9 5 B A I O4 L

/

M E A IA RM S O R

二 _ J L S RAM ADDR EN A DDR

— _

/# R

RAY ED#

地 计 器 址 数

I

收 稿 日期 :2 1.32 。 020 —9

图 1 多功 能接 口板 硬 件 原 理

・0 2 2・

21 0 2年 6月第 3期

现代导航

・0 2 l・

基于 C C 总线 技术的新型中国电子科技集团公司第 二十研 究所,西安 70 6 ) 10 8

摘 要:针对 当前雷达系统中显控 台和各分机之间信息传送的情况,采用 L D 三线同步 串 V S 口和 C C P I总线技 术开发 了一种 多功 能接 口板 。重点 叙述 了板 卡设 计开发 中的难 点和 细节 ,并且

详 细研 究 了 P I 04的状 态机 ,具有 一定 的 实用性 和推 广价 值 。 C 5 9

关键词 :三线同步 串口;P I 04 P I总线 C 5 ;C C 9 中图 分类号 : N9 5 T 5 文献标 识码 : A

基于CPCI总线的高速数据记录系统设计

Ke r s y wo d :CPCI DM A; i e ; ; Dr r pC1 0 4 d t e o d v 9 5 ; a rc r a

P 邱 hr mp n n t cn et ( P ) u— ae s m f eoddt rcp o . ei ̄ d c h s m o oio n e ea Co o et ne o nc C CI b s bs s t o cr a eet n W o u etes t cmp s nad l I r d ye r a i n ye i t

4 7

3硬 件 设 计

31C C 接 口 . P I

CP I 术 是 在 周边 元件 扩 展接 口( CI技 术 基 础 上 , C技 P ) 对 板 卡 的机 械 结 构 和 连接 方 式 改 进 而成 ,电气 特 性 与 P I 全 C完

相 同 。 C 总 线 模 块 由 P 10 4来 实现 。 C 9 5 P I C 95 P I0 4是一 个 3 2位 3 3 MHz 总线 主 控 I0 加 速 器 , 实 现 P I . 规 范 的要 求 。 1 能 C 22版 P 95 CI0 4作 为桥 接芯 片 ,在 P I 线 和 L cl 线 之 间 有 P C 总 oa总 CI

定 稿 日期 : 01 0— 2 2 1- 9 1

模 A 块 儿 I C R M C R 丁 L T L C R 片 I T L

l

总 线

机

I

I

图 1 系统组 成 图

《 计算机与网络 》2 1 年第 1 期 01 9

CPCI总线接口设计论文

CPCI总线接口设计论文1地面测试台整体结构地面测试台的测试对象采编存储器。

测试台的主要功能包括向采编存储器提供模拟信号供其采集,向采编存储器下发控制命令,接收采编存储器下发的高速LVDS实时数据并进行后续处理。

测试台的整体结构如图1所示。

CPCI总线上挂有3个CPCI板卡,分别为CPU卡、接口卡、信源卡。

其中,CPU卡为处理系统,接口卡和信源卡为功能卡。

本文将以接口卡为主要依据来介绍如何以FPGA逻辑控制来实现CPCI局部总线接口和高速LVDS接口。

2LVDS高速数据接口实现2.1LVDS接口硬件电路设计由于趋肤效应和介质损耗,高速信号在传输过程中会衰减。

因此,当传输距离较长时,往往要使用电缆驱动器和均衡器来保证高速数据传输的准确性。

电缆驱动器将信号以最大功率耦合到电缆上[4],延长信号的传输距离,电缆均衡器可以对传输的信号进行高频补偿,以至达到标准逻辑电位。

本设计中,LVDS串行器、解串器分别选用TI公司的SN65LV1203和SN65LV1224,信号驱动器、电缆均衡器分别选用NS公司的CLC001和CLC014。

LVDS接口电路结构如图2所示,采编存储器的FPGA控制LVDS串行器将10bit并行数据转换成差分串行数据,再通过电缆驱动器将信号耦合到电缆上。

地面测试台的电缆均衡器对接收到的信号进行高频补偿之后传送给解串器,解串器根据参考时钟将差分串行数据转换成10bit的并行数据,由FP-GA进行后续的处理。

2.2FPGA逻辑控制LVDS数据接收由于CPCI接口传输的时钟和LVDS数据接收电路的时钟不匹配,为了保证数据传输的可靠性,在编写VHDL语言程序时FPGA内部调用一个异步时钟控制的缓存FIFO[8]IP核来对接收到的LVDS高速数据进行缓存,如图2所示。

上位机通过配置PCI9054的传输计数寄存器,将一次DMA传输的数据量设置为2kbyte。

写FIFO的时钟为18.432MHz,读FIFO的时钟为36.864MHz,当FIFO内数据量达到2kbyte时,FPGA立即通知上位机启动一次DMA传输。

CPCI数据总线接口的设计与实现

LU Qn ,MA Ta y I i g i i n

( o m nct n i s n h 0hIs t eo C iaEet nc T cnl yGop in70 6 ,C ia C m u i i s v i ,T e t niu f hn l r i eh o g ru ,X ’ 10 8 hn ) a o D io 2 st co s o a

目前 大多 数 嵌பைடு நூலகம்入 式 计 算 机 系 统 的接 口最 终 都 要 经 过 C C 总 线 与计算 机 内存 进 行 交 互 。C C PI P I的总 线 规 范

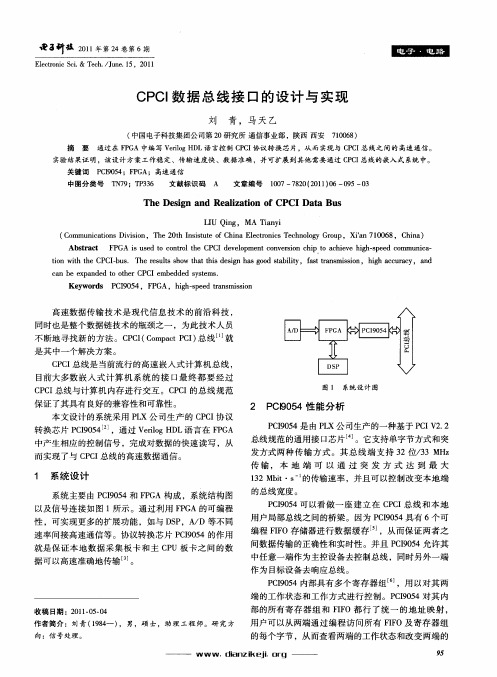

图 1 系统设 计 图

保证了其具有 良好的兼容性和可靠性 。

本 文设 计 的 系统采 用 P X公 司生 产 的 C C 协 议 L PI 转 换 芯片 P I0 42,通 过 V ro D C9 5 _ J eigH L语 言 在 F G l PA 中产生 相应 的控 制信 号 ,完 成对 数据 的快 速 读 写 ,从 而 实现 了与 C C 总线 的高速 数 据通 信 。 PI

以及信 号连 接 如 图 1所示 。通 过 利用 F G P A的可 编 程 性 ,可 实现 更 多 的扩 展 功能 ,如 与 D P / 等不 同 S ,A D 速 率 间接高 速通 信等 。协议转 换 芯 片 P I04的作 用 C95

就 是保 证 本 地 数 据 采 集 板 卡 和 主 C U板 卡 之 间 的数 P

的总线 宽度 。 P I0 4可 以看 做 一 座 建 立 在 C C 总 线 和 本 地 C9 5 PI 用 户局 部总 线之 间 的桥梁 。因为 P I0 4具 有 6个 可 C9 5

1 系统 设 计

系统 主要 由 P I0 4和 F G C9 5 P A构 成 ,系统结 构 图

CPCI数据总线接口的设计与实现

CPCI数据总线接口的设计与实现

刘青;马天乙

【期刊名称】《电子科技》

【年(卷),期】2011(024)006

【摘要】通过在FPGA中编写Verilog HDL语言控制CPCI协议转换芯片,从而实现与CPCI总线之间的高速通信.实验结果证明,该设计方案工作稳定、传输速度快、数据准确,并可扩展到其他需要通过CPCI总线的嵌入式系统中.

【总页数】3页(P95-96,100)

【作者】刘青;马天乙

【作者单位】中国电子科技集团公司第20研究所通信事业部,陕西西安,710068;中国电子科技集团公司第20研究所通信事业部,陕西西安,710068

【正文语种】中文

【中图分类】TN79;TP336

【相关文献】

1.基于CPCI和光纤接口的数据采集卡设计与实现 [J], 李波;张兴敢;魏耀

2.基于CPCI总线的具有热切换能力的数据处理模块的设计与实现 [J], 韩振国;梁

小虎

3.双通道数据传输PXI总线接口控制程序设计与实现 [J], 樊昊;龚志红

4.一种可配置数据交互流程的嵌入式总线接口测试系统设计与实现 [J], 李智

5.基于CPCI接口的海量数据采集系统设计与实现 [J], 徐小杰;黄可生;林峰;许庆芬

因版权原因,仅展示原文概要,查看原文内容请购买。

基于CPCI总线冗余控制计算机的设计与实现

基于CPCI总线冗余控制计算机的设计与实现随着人们对于计算机系统控制的可靠性要求逐渐提高,在本文中,介绍了一种基于CPCI总线控制计算机的冗余设计方式,并对其实现原理以及应用方式进行一定的分析与探讨。

标签:CPCI总线冗余控制实现1 概述作为系统的核心部件,控制计算机有着进行控制、数据处理等作用。

而对于其重要性而言,高度的可靠性是其在正常运作中必不可少的一部分。

冗余技术其功能就是在系统中设计多套相同给定任务的技术,当主系统出现故障时,其冗余部分的设备就会在第一时间介入,并将工作进行承担,从而对系统发生故障的时间尽到最大程度的降低,并将系统的故障率进行降低。

从这里我们就可以了解到对一个稳定性要求极高的控制计算机来说,对其采用冗余方式的设计是非常重要的。

2 系统原理对于冗余控制系统来说,其是由两套相对独立的计算机组合而成。

在两个计算机中,分别有一套独立的I/O信号,其在控制电路对信号进行切换选择之后对外提供的一套I/O接口,同时处于工作中的I/O信号对外界进行接通并连接。

在这两套计算机设备中,其无论是硬件还是软件的配置都是完全一样的,并在普通计算机的基础上多了扩展板设备。

扩展板工作在Compact PCI总线中,并可以依据系统所需要的功能来配置相应的接口。

在系统中,设置了4个扩展板槽位,如果工作需要的槽位很多,就可以使用CPCI总线进行扩展。

工作系统示意图如图1 所示:在冗余控制系统中的计算机加电开关也是相对独立的,这就使我们可以通过对开关的控制来对需要工作的计算机进行选择,同时,切换电路也可以对相应计算机的接口进行自动的识别。

而当其中的一套计算机处于工作状态中时,另一台计算机就处于冷备份的状态。

3 双电源互锁设计在系统中,分别设置了两种额度的DC电源输出。

以+5V电源为例,在其每块电源中都有着使能端、输出端与互锁控制信号输出端。

其中,使能端能够对电源的DC-DC转换的工作信号进行控制,其中的一块电源互锁信号也同另一块电源的使能端进行连接。

CPCI总线背景下嵌入式计算机通用接口设计分析

射 的方 式进行传播 ,因此 ,在对外围控制和匹 配 电路进行设计 时,要按照相应的规范进行 , 以保证总 线信号的完整性。

对 于通 用接 口而言 ,其软件 主要 是基 于 多任务 操作 系统 Vx Wo r k s 进 行设计 ,从而 实 现通信、存储器优化管理 、中断管理服务等系

统功能。

接 口主要包 括硬 件和 软件两 个部 分 ,软 件部分的设计重点在于信 息格 式的定义 、功能

2 . 2 . 1 主板程序 的功能和函数

背 景

中遇 口 的 用现 计 相 术, 嵌入 并 成

是现场编程 技术与软件 、硬件设计相结合的方

法,结 合通用总线接 口设计技术 、数据库共享

实时访问技术、数据 交换技术等 ,利用相关的 电路设计和 函数设 计 ,对 C P CI 总 线背景下的

嵌 入 式 计 算机 通用 接 口进 行 设 计 。

( 2 ) 可 编 程 逻 辑 芯 片 :主 要 用 于 实 现地

社会效益 ,具有重大的技术价值 。

参考文献

[ 1 】汪 强 .基 于 C P C I总 线 的 嵌 入 式计 算 机 通 用接 口设 计 [ J ] .计 算 机 工 程 与 设

以实现主板对于扩展板的控制,以及相互之 间 数实现 ,主要是对扩展板的生产 厂商、设备版

的数据和信息交换。 本号 、相关参数 、配置文件的路径 等信息进行 读取 ,并将相应的扩展板初始化参数写入双 口 A M 的扩展板初始 化参数 区,为 扩展板 的初 R 通用 接 口的硬件 设计 ,主要 是针对 扩展 始化提供数据支持 。 2 . 2 . 2扩展板程序 的功能和 函数

基于CPCI系统的高速数字通信接口电路设计与应用.doc

基于CPCI系统的高速数字通信接口电路设计与应用在CPCI系统环境下高速数字通信AFDX协议端系统接口的电路设计与功能实现。

采用Verilog编程实现基于FPGA的硬件设计部分,采用C编程实现基于MicroBlaze的嵌入式软件设计。

0 引言随着通信技术的高速发展,嵌入式系统对数据传输速率的要求更高。

在航空等军用电子设备中,实现信号处理算法的数字信号处理机,起着至关重要的作用。

CPCI总线技术有效解决了高速互联问题。

20世纪90年代,PCI总线技术被广泛应用,但是它可靠性较低,无法满足对正常运行时间要求较高的高可用性系统。

加之其主板连接器可靠性低,更换时易被损坏。

CPCI的高带宽特点,决定了其适用于高速数据通信场合。

随着国外著名计算机系统公司基于CPCI产品和方案的推广及PICMG/PRC对CPCI技术的宣传,我国工业控制领域越来越多地把CPCI应用于高性能嵌入式系统之中。

本文研究了在CPCI系统环境下高速数字通信AFDX协议端系统接口的电路设计与功能实现。

采用Verilog编程实现基于FPGA的硬件设计部分,采用C编程实现基于MicroBlaze的嵌入式软件设计。

1 基于FPGA的硬件设计1.1 MAC模块、FIFO模块和MII模块FIFO模块分为接收FIFO和发送FIFO,通过调用IP核来实现。

本文所设计的MAC模块和FIFO模块的基本结构如图1所示。

MAC核通过MII接口和PHY芯片进行外部通信,通过发送FIFO和接收FIFO进行FPGA内部数据的通信。

1.2 CRC模块CRC模块通过检验数据的CRC值,判决接收的数据的正确性和有效性。

在数据包被发送后,紧接着该数据包的4 B CRC 也会被发送。

接收者通过数据包和CRC数据就可以得出新的CRC值。

若新CRC值为0,表明接收和发送的数据不一致,crc_error将会置1。

其管脚定义如表2所示。

1.3 规整模块和冗余管理模块规整模块根据每条VL的BAG,Lmax值,对其数据流进行规整。

CPCI总线在数字化电台中的设计用

随着现代军事通信技术的进步,数字化短波电台逐步往嵌入式、模块化的方向发展。

CPCI 总线作为一种新兴的总线技术,在短波电台的模块化设计上具有重要的应用价值,可以较大程度地提高数字化短波电台的可靠性和保障性。

CPCI总线架构CPCI规范是由PICMG(PCI Industrial Computer Manufacturer’s Group,PCI工业计算机制造商联盟)制定的一种新的开放工业计算机标准,用于工业和嵌入式应用。

它定义了更加坚固耐用的PCI版本,在电气、逻辑和软件功能等方面,与PCI标准完全兼容。

CPCI全称Compact PCI,简单的说就是PCI specification(PCI电气规范)加上rugged Eurocard packaging(欧式卡)结构。

CPCI模块以插卡的方式安装在机箱内的支架上,并采用垂直方向通风散热,具有更好的散热性和抗震动性。

这样,在CPCI系统中就可采用在台式机中广泛使用的高性能PCI技术,降低了新技术的使用成本,系统的整体性能得以提升。

而且,基于PCI技术的丰富软件工具,也使得用户在使用中更加便捷。

同时,欧式卡结构使得系统的可靠性进一步提高。

另外采用IEEE 1101.11后端输出方式,使得对系统的维护更加方便快捷,大大缩短了系统的平均维护时间。

CPCI系统背板和CPCI板卡采用的是标准2mm高密度气密性针孔连接器,板卡的尺寸分3U(100mm×160mm)和6U(160mm×233mm)两种,3U的系统只提供32位/64位的PCI 系统总线,6U的系统除了提供32位/64位的PCI系统总线外,还有多达315线的用户定义输入/输出线,非常适用于数字化短波电台的模块化设计应用。

CPCI总线具有极高的性能,其主要特点是:1.具有地址数据多路复用的高性能32位或64位的同步总线。

总线引脚数目和部件数量少(对于总线目标设备只有47根信号线,对于主设备最多只有49根信号线),降低了成本及布线复杂度。

CPCI总线接口设计方法

CPCI总线接口设计方法摘要:随着科学技术不断发展,新一代嵌入式前端处理中总线速率和CPU处理器技术在多种装备设计制造中不断得到广泛应用。

本文立足于在对CPCI总线标准进行深入研究的基础上,对基于FPGA的CPCI总线接口设计方法进行了进一步的学习探讨,并对其接口设计功能进行了简单分析,希望可以在以后的工作中提供一些借鉴作用。

关键词:FPGA;CPCI;总线接口PCI工业计算机厂商联盟制定的CPCI规范,在嵌入式应用和工业中得到了广泛的应用。

在软件功能、逻辑以及电气方面其能够很好的兼容于PCI标准。

在本次设计探讨中选择了FPGA芯片和CPCI协议转换芯片PCI9030,将简化的PCI接口逻辑设计完成,并且保证了具有32bit数据宽度、33MHz总线周期的PCI从设备模块的接口功能的实现,将大量的逻辑资源节省了下来。

1基于FPGA的CPCI总线接口设计的系统分析现在设计CPCI总线接口与设计PCI接口采用了相同的方法,一般都会选择两种方案,也就是专用总线接口和可编程逻辑器件。

其中可编程逻辑器件主要是以PCI协议为根据使PCI总线接口控制器得以实现,然而由于PCI协议具有非常高的复杂性,因此其具有较长的周期和较大的开发难度,并且无法在较短的时间内保证系统稳定的实现。

目前很多开发者都是选择现成的PCI接口器件,其具有很高的通用性和较低的成本,并且可以对数据传输进行优化,将相应的配置空间提供出来,因此其属于一种不仅省时而且省力的方案。

选择FPGA+PCI接口芯片构建本系统,其主要由Altera的FPGA芯片和PCI9030共同组成。

选择EP2C35F672I8器件作为FPGA芯片,其能够利用硬件描述语言将控制时序信号形成,完成读写地址总线和数据总线,从而实现与CPCI数据总线的通信工作。

PCI9030一共提供了3种物理总线接口,也就是PCI总线接口、串行EEPROM接口以及LOCAL总线接口,其同时还包括若干个中断发生器、可编程片选信号、可编程GPIO接口以及LOCAL总线地址到PCI总线空间。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

CPCI数据总线接口的设计与实现[图]

高速数据传输技术是现代信息技术的前沿科技,同时也是整个数据链技术的瓶颈之一,为此技术人员不断地寻找新的方法。

CPCI(Compact PCI)总线就是其中一个解决方案。

CPCI总线是当前流行的高速嵌入式计算机总线,目前大多数嵌入式计算机系统的接口最终都要经过CPCI总线与计算机内存进行交互。

CPCI的总线规范保证了其具有良好的兼容性和可靠性。

本文设计的系统采用PLX公司生产的CPCI协议转换芯片PCI9054,通过Verilog HDL语言在FPGA中产生相应的控制信号,完成对数据的快速读写,从而实现了与CPCI总线的高速数据通信。

1 系统设计

系统主要由PCI9054和FPGA构成,系统结构图以及信号连接。

通过利用FPGA的可编程性,可实现更多的扩展功能,如与DSP,A/D等不同速率间接高速通信等。

协议转换芯片PCI9054的作用就是保证本地数据采集板卡和主CPU板卡之间的数据可以高速准确地传输。

2 PCI9054性能分析

PCI9054是由PLX公司生产的一种基于PCI V2.2总线规范的通用接口芯片。

它支持单字节方式和突发方式两种传输方式。

其总线端支持32位/33MHz传输,本地端可以通过突发方式达到最大132Mbit·s-1的传输速率,并且可以控制改变本地端的总线宽度。

PCI9054可以看做一座建立在CPCI总线和本地用户局部总线之间的桥梁。

因为PCI9054具有6个可编程FIFO存储器进行数据缓存,从而保证两者之间数据传输的正确性和实时性。

并且PCI9054允许其中任意一端作为主控设备去控制总线,同时另外一端作为目标设备去响应总线。

PCI9054内部具有多个寄存器组,用以对其两端的工作状态和工作方式进行控制。

PCI9054对其内部的所有寄存器组和FIFO都行了统一的地址映射,用户可以从两端通过编程访问所有FIFO及寄存器组的每个字节,从而查看两端的工作状态和改变两端的工作方式。

3 PCI9054局部总线的接口设计

整个CPCI接口的设计思路为:FPGA通过桥接芯片PCI9054与CPCI总线连接,其内部使用异步双口RAM来进行高速数据的缓冲,通过使用VerilogHDL语言编程来控制FPGA中的异步双口RAM,以实现系统数据在嵌入式CUP板卡内存与CPCI板卡之间的高速传输。

PCI9054提供了3种物理总线接口:CPCI总线接口、LOCAL总线接口和串行EPROM接口。

其中CPCI总线接口协议在嵌入式操作系统中的驱动包已经带有,而串行EEPROM的初始化是由PLX公司的PLXMON软件在嵌入式操作系统中进行在线烧写的,所以本系统设计的重点就是关于LOCAL总线接口的控制和传输,其接口电路示意图。

PCI9054与本地总线之间的接口称之为LOCAL BUS,是CPCI总线系统设计中十分重要的一环。

PCI9054 LOCAL BUS在系统设计中,其总线直接与Alter公司的EP2S90F78014芯片的数据总线相连,同时通过运用Verilog HDL语言编程来实现对双口RAM控制器的功能。

PCI9054 LOCAL BUS有3种工作模式,分别为M、J和C模式。

M模式是专为Motorola公司开发和设计的,而另外两种工作模式就应用的比较广泛。

其中J模式因为没有LocaL Master,所以它的地址总线和数据线没有分开,从而增加了开发难度。

而在C模式下,PCI9054芯片通过片内的逻辑控制可以将CPCI的局部地址和数据总线分开,从而有效地降低了开发难度,并且能灵活地为本地工作时序提供各种工作方式,所以本系统设计方案选择了LOCAL总线的C工作模式,工作频率为40MHz。

4 局部总线的实现

PCI9054支持主模式、从模式和DMA传输方式,根据本系统设计的需求,采用从模式传输方式,即允许CPCI总线上的主设备访问局部总线上的配置寄存器或内存,支持多种模式传输。

FPGA内部逻辑要设计本地端总线控制模块,实现局部总线的状态控制,同时产生片内的读写时序及地址信号以支持突发传输和单周期传输,因此使用Verilog HDL语言中的状态机来完成上述功能。

其状态转换,。

5 测试结果

利用SingnalTap采集到的单周期时序传输图,。

6 结束语

以PCI9054为核心介绍了CPCI板卡与嵌入式CPU板卡之间高速数据通信系统接口的软硬件设计。

PCI9054因其灵活和方便的接口功能,使操作者只需关心LOCAL BUS接口电路的时序设计,并且利用其传输速率高的特性,可以帮助一些对实时性要求较高的系统解决其传输数据的问题。