ADI的高速PCB设计

高速PCB设计指南

高速PCB设计指南高速PCB设计是电子设计领域中的一个重要分支。

高速PCB设计涉及到比较高的频率信号的传输,如高速数据总线、时钟、控制信号等。

随着电子技术的快速发展,高速PCB设计已经成为一个必要的技能。

本文将为您提供高速PCB设计的基本指南。

一、PCB板布局在进行高速PCB设计时,PCB板布局是非常关键的。

以下是几个需要注意的方面:1. RF电路和敏感板路应该远离高功率板路。

2. 高速数字信号应当互相分离开来,避免信号干扰。

3. 模拟信号路径应该和数字信号路径分离开来。

4. 时钟和数据线需要独立布局,减少相互干扰的影响。

5. 保持合理的板厚度并且保持一致。

6. 尽量减少信号层的数量,这能减少移动信号的时间延迟。

7. 适当加入障碍物物避免辐射的干扰,同时进行地垫。

二、信号完整性高速PCB设计需要考虑信号完整性的问题,保证信号的质量和稳定性。

1. 确定信号的路径。

2. 在尽可能短时间内连接信号。

3. 接口处必须要匹配阻抗。

4. 优化功率地方的供电电路。

5. 在设计时需要考虑信号畸变。

三、布线PCB布线是高速PCB设计中的一个重要环节。

以下是您需要关注的点:1. 在电源附近使用CAP滤波器,同时优化供电地焊盘。

2. 在时钟和数据线路线长领域内布置并优化相应的差分路线。

3. 适当的铺铜层能有效减少层间传输的互联参数。

并在特殊情况下,使用壳体充当屏蔽。

4. 在IO端口上使用自适应阻抗技术。

5. 使用捆绑电线和费正负电平特性电缆。

四、仿真分析在高速PCB设计时,仿真分析是一种非常有效的工具,可以帮助您预测PCB设计的结果并优化开发流程。

1. 使用仿真工具来分析布局的合理性。

2. 使用仿真工具跑完整电路板的分析。

3. 使用时间领域和频域仿真工具,以检测信号时间延迟和频率响应的问题。

4. 使用SPICE仿真工具进行供电电路仿真。

五、技术细节通过这里的技术细节,可以帮助您更好地进行高速PCB设计:1. 在PCB设计时,要留有足够的边距和缓冲区域。

优化PCB布局实现高速ADC设计

优化PCB布局实现高速ADC设计就能降低PDS的阻抗。

比如我们要设计10mΩ的参考平面,如果在系统电路板上使用多个电容值,便可降低在500 MHz频率范围内的阻抗,如图4中的红色曲线所示。

图4:标准的去耦电容可以帮助降低高达500MHz的PDS阻抗,而频率超过500MHz时则由平面电容解决。

了解所用电容可以降低设计中所用电容的数量和类型。

然而,让我们再看一下绿色曲线,其在同样的设计上仅使用了0.1μF和10μF两种电容。

这证明了如果使用恰当的电容,则不需要采用如此多的电容值。

这也有助于节省布局和物料清单(BO M)成本。

然而,并非所有的电容“生来平等”,即使来源于同一供应商,其工艺、尺寸和样式也有差别。

如果未使用正确的电容,则不论是采用多个电容还是采用几种不同类型的电容,其结果都会给PDS带来反作用。

放置电容或者使用不同的电容工艺和型号都有可能形成电感环路,它们将对系统内的频率做出不同响应以及彼此之间发生谐振(图5)。

了解系统所用电容类型的频率响应非常重要。

随便选用电容会让设计低阻抗PDS系统的努力付诸东流。

要设计出合格的PDS,需要使用各种电容(再见图4)。

PCB上使用的典型电容值只能将直流或者接近直流的约500MHz频率范围内的阻抗降低。

在500MHz以上时,电容将由PCB形成的内部电容决定。

电源平面和接地平面是否叠置得足够紧密?为此,请设计一个支持较大平面电容的PCB层叠结构。

例如,六层堆叠结构可能包含顶部信号层、第一接地层、第一电源层、第二电源层、第二接地层和底部信号层。

规定第一接地层和第一电源层在层叠结构中彼此靠近。

将这两层的间距设定为2~4mil,将形成一个固有的高频平面电容。

此电容的最大优点在于它免费,您只需要在PCB制造笔记中进行说明即可。

如果必须分割电源平面,并在同一平面上具有多个VDD电源轨,则应使用尽可能大的电源平面。

不要留下空洞,同时还应注意敏感电路。

这将使该VDD平面的电容达到最大。

ADI技术专家问答:关于高速PCB设计的200个问答

ADI技术专家问答:关于高速PCB设计的200个问答——针对高速PCB设计头痛的问题,比如布局布线,EMI/EMC/SI/PI/ESD等问题现场问答内容总结。

1.讲座中讲到为了减少寄生电容的影响,要去除运放焊盘下面的地层,这个底层是指地平面吗?如果是的话,如何去除那个焊盘下面的地呢?是的。

焊盘下面的地也要去掉。

2.对于高速AD采样电路,有模拟和数字电路混合在一起,如何避免地反弹噪声对采样的影响?一般要分割AGND,DGND,然后选择在合适的地方一点接地。

3.在很多的书上看到模拟和数字地和电源的问题,在实际的设计中,我们怎样处理,比如模拟和数字的供电是否需要两个稳压的芯片单独输出,模拟地和数字地最后怎样连接在一起等?一般来说不需要两个单独的稳压芯片,中间加一磁珠就可以了,要尽量避免数字部分的噪声耦合到模拟部分。

对于低速精密系统来说,一般采用模拟地与数字地单点接地的方法,具体可以参考评估板;对于高速而言,为了最小的电流回路,一般不具体分模拟地与数字地,也就是只采用一个地平面。

4.1、如何减少数字信号对模拟信号的干扰?尤其是模拟小信号,如:微安电流脉冲。

2、在多通道模拟输出中,如何减少通道与通道之间的串扰?以及实现通道的高阻状态,即未接通通道不被干扰的问题?1.一般情况,通过分开模拟地和数字地,还有分开模拟电源以及数字电源,可以减少数字对模拟信号的干扰。

2。

一般情况下,未接通道是否高阻由片子本身决定,多通道系统中,尽量减少通道间平行走线的长度并用地将其隔开都能减少通道间的串扰。

5.对电源分割,能不能提供一些指导性建议你好,对于电源分割,你可以参考中的High SpeedDesign Techniques里面的章节。

谢谢6.What problem in digital GND and analogGND connecting together ?如果一点共地做的不是很好,会影响信噪比和系统的性能。

7.ADI是否提供适合PROTEL制做PCB板的元器件封装库?我们很快会提供这些封装库。

高速ADC PCB布局布线技巧

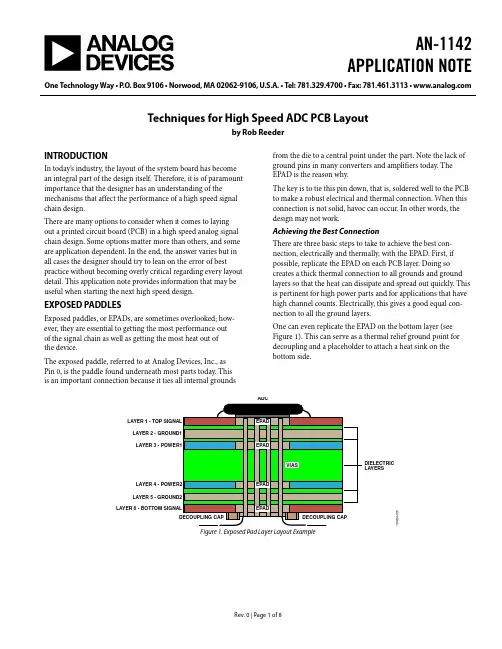

INTRODUCTION

In today’s industry, the layout of the system board has become an integral part of the design itself. Therefore, it is of paramount importance that the designer has an understanding of the mechanisms that affect the performance of a high speed signal chain design.

REVISION HISTORY

1/12—Revision 0: Initial Version

Application Note

Plane Coupling...................................................................................4 Splitting Grounds ..............................................................................5 Conclusion..........................................................................................6 References ...........................................................................................6

DECOUPLING CAP

高速pcb设计规则

高速pcb设计规则

高速PCB设计规则是指在设计PCB时需要遵循的一系列规则和原则,以确保信号传输的质量和稳定性。

高速 PCB 的设计需要考虑多

种因素,如信号传输速度、信号波形、传输距离、干扰等等。

以下是一些常见的高速 PCB 设计规则:

1. 避免信号线的走线路径过长,尽可能缩短信号线的长度,以

减小信号传输延迟和损耗。

2. 保证信号线之间的距离足够大,以避免互相干扰,同时也能

降低信号串扰的风险。

3. 使用合适的层次结构设计,尽可能将信号线和电源线分离,

以减少干扰和噪声。

4. 在 PCB 的布线中,保证地线和供电线的宽度足够宽,以确保稳定的供电和地面连接。

5. 在 PCB 的布线中,避免过多的弯曲或拐角,以减小信号传输中的损失和延迟。

6. 选用合适的 PCB 材料和厚度,以满足高速信号传输的需求。

7. 注意 PCB 的电磁兼容性,通过合理的布线和屏蔽来减少干扰。

以上是高速 PCB 设计中的一些基本规则,但实际上,高速 PCB 的设计涉及的方面非常广泛,需要根据具体的应用场景来进行设计。

为了保证高速 PCB 的质量和可靠性,需要有专业的技术人员进行设

计和测试。

- 1 -。

Altium Designer实战攻略与高速PCB设计 4

内容提要

• • • • • • • • 新建和编辑原理图 添加元件 添加电气线及电气属性 总线操作 Port端口操作 添加二维线和文字 放置NO ERC检查测试点 原理图设计上机实例

添加元件及属性更改

1、添加元件

单击 图标,或执行菜单命令【Place】【Part】

添加元件及属性更改

2、元件属性更改 在放置元件时,元件附着在光标上按TAB键或放置元件后,双击元件即可弹出 元件属性对话框,可根据需要更改元件位号等

添加电气线及电气属性

1、绘制电气线(Wire)

添加电气线及电气属性

添加二维线和文字

1、添加二维线

执行菜单命令【Place】【Drawing Tools】 【Line】,即可进入添加二维 线状态。

单击鼠标左键即可定位二维线的一端,移动鼠标并再次单击鼠标左键即可完成 一条二维线的绘制,右击鼠标可以退出放置二维线设计状态。

这里需要注意的是:二维线是没有任何电气属性的,通常用于标识用。

添加二维线和文字

2、添加文字 执行菜单命令【Place】【Text String】,此时光标变成十字形,并带有一个 文本字Text。移动光标到合适位置后,单击左键即可添加文字。 在放置状态下按下键盘的【TAB】键或者放置完成后,双击需要设置属性的文 本字,将弹出“Annotation”对话框。在这个对话框中,可以设置文字的颜色, 位置,定位,以及具体的文字说明和字体。

新建和编辑原理图

5、绘制原理图前的准备-指定Integrated Library 在调用元件之前,要进行元件库的指定。 执行菜单命令【Design】 【Add/Remove Library】。在弹出的对话框中, 点击【Add Library】,添加已准备好的Integrated Library,点击【OK】即可。

高速ADC_PCB布局布线技巧

高速ADC-PCB布局布线技巧在高速模拟信号链设计中,印刷电路板(PCB)布局布线需要考虑许多选项,有些选项比其它选项更重要,有些选项则取决于应用。

最终的答案各不相同,但在所有情况下,设计工程师都应尽量消除最佳做法的误差,而不要过分计较布局布线的每一个细节。

这里分享一篇ADI资深系统应用工程师Rob Reeder写的一篇文章《高速ADC PCB布局布线技巧》。

Rob Reeder写的文章深入浅出,相信这篇文章对大家的高速设计项目会有所帮助。

裸露焊盘裸露焊盘(EPAD)有时会被忽视,但它对充分发挥信号链的性能以及器件充分散热非常重要。

裸露焊盘,ADI公司称之为引脚0,是目前大多数器件下方的焊盘。

它是一个重要的连接,芯片的所有内部接地都是通过它连接到器件下方的中心点。

不知您是否注意到,目前许多转换器和放大器中缺少接地引脚,原因就在于裸露焊盘。

关键是将此引脚妥善固定(即焊接)至PCB,实现牢靠的电气和热连接。

如果此连接不牢固,就会发生混乱,换言之,设计可能无效。

实现最佳连接利用裸露焊盘实现最佳电气和热连接有三个步骤。

首先,在可能的情况下,应在各PCB层上复制裸露焊盘,这样做的目的是为了与所有接地和接地层形成密集的热连接,从而快速散热。

此步骤与高功耗器件及具有高通道数的应用相关。

在电气方面,这将为所有接地层提供良好的等电位连接。

甚至可以在底层复制裸露焊盘(见图1),它可以用作去耦散热接地点和安装底侧散热器的地方。

(注:即在PCB底层阻焊开窗露铜,让散热铜皮直接与空气接触,能够更好地散热)其次,将裸露焊盘分割成多个相同的部分,如同棋盘。

在打开的裸露焊盘上使用丝网交叉格栅,或使用阻焊层。

此步骤可以确保器件与PCB之间的稳固连接。

在回流焊组装过程中,无法决定焊膏如何流动并最终连接器件与PCB。

连接可能存在,但分布不均。

可能只得到一个连接,并且连接很小,或者更糟糕,位于拐角处。

将裸露焊盘分割为较小的部分可以确保各个区域都有一个连接点,实现更牢靠、均匀连接的裸露焊盘(见图2和图3)。

高速电路板的设计方法

高速电路板的设计方法高速电路板的设计是电子产品开发过程中至关重要的一步。

它涉及到信号传输的快速性、稳定性和可靠性等方面。

在本文中,我们将介绍高速电路板设计的基本方法,以帮助工程师们更好地应对挑战。

一、高速电路板设计概述高速电路板设计是一门复杂而重要的技术。

它主要关注数据信号的快速传输和尽可能降低信号失真。

高速电路板设计需要考虑信号的传输速度、信号完整性、噪声抑制、阻抗匹配以及电磁干扰等多个因素。

二、布局设计1. 信号与电源分离:将高速信号和电源信号分离布局,以减少信号干扰。

2. 分层布局:将电路板分为不同的层次,每层分别布置不同的信号层或电源层。

这样可以最大程度地减少信号干扰和电源电流的返流。

3. 地线设计:将地线作为信号层的一部分,提供可靠的回流路径,以降低信号失真。

4. 路由优化:根据信号传输的需求,采用最短线路和合适的拓扑结构来布置信号路由。

三、信号完整性设计1. 控制传输线长度:为了减少信号传输时的延迟和时延不一致,尽量控制传输线的长度和阻抗一致性。

2. 选择合适的信号引线:采用合适的信号引线来降低信号传输过程中的反射和耦合。

3. 选择合适的电磁屏蔽材料:采用电磁屏蔽材料来减少外部电磁干扰对信号的影响。

四、阻抗匹配设计1. 控制传输线的宽度和间距:通过控制传输线的宽度和间距来达到所需的阻抗值。

2. 添加阻抗匹配器:根据需求,可以添加阻抗匹配器以确保信号传输的稳定性和可靠性。

五、电磁兼容性设计1. 电源滤波设计:采用合适的电源滤波器来抑制高频噪声,减少对周围电路的影响。

2. 地线布局:合理布置地线以减少电磁辐射和接收。

3. 接地设计:良好地接地可以减少电磁噪声。

六、其他设计考虑因素1. 热管理:高速电路板在工作过程中会产生一定的热量,因此需要合理布局散热器和散热孔。

2. 维护性设计:设计应该考虑到电路板的维护和检修,易于更换故障部件。

3. ESD保护:添加静电放电保护措施来保护电路板免受静电干扰。

高速ADCDAC电路及PCB设计要点梳理

高速ADCDAC电路及PCB设计要点梳理概要在高速模拟信号链设计中,印刷电路板(PCB)布局布线需要考虑许多选项,有些选项比其它选项更重要,有些选项则取决于应用。

最终的答案各不相同,但在所有情况下,设计工程师都应兼顾全局,而不要过分计较布局布线的每一个细节。

很多情况下做不到面面俱到,只能根据电路板及产品的面积进行取舍。

下面就给大家分享一下ADC/DAC电路及PCB设计中几个比较重要的问题:1数字地模拟地是否分割的问题硬件工程师最常提出的问题是:使用ADC时是否应将接地层分为AGND和DGND接地层?简单回答是:视情况而定。

详细回答则是:通常不分离。

为什么不呢?因为在大多数情况下,盲目分离接地层只会增加返回路径的电感,它所带来的坏处大于好处。

从公式V = L(di/dt)可以看出,破坏了GND的完整性,随着电感增加,电压噪声会提高。

随着电感增加,设计人员一直努力压低的PDN阻抗也会增加。

随着提高ADC采样速率的需求继续增长,降低开关电流(di/dt)的方式却很有限。

因此,除非需要分离接地层,否则请保持这些接地连接。

所以我们的结论是大部分情况下推荐不做DGND AGND分割,这个和大家早期经验做法相左。

我们大部分的产品是有尺寸要求的,可能没有足够和理想的空间。

受尺寸限制的影响,电路板无法实现良好的布局分割时,就需要分离接地层。

这可能是为了符合传统设计要求或尺寸,必须将脏乱的总线电源或高噪声数字电路放在某些区域。

这种情况下,分离接地层是实现良好性能的关键。

然而,为使整体设计有效,必须在电路板的某个地方通过一个磁珠或局部连接点将这些接地层连在一起。

最终,PCB上往往会有一个连接点成为返回电流通过而不会导致性能降低或强行将返回电流耦合至敏感电路的最佳位置。

如果此连接点位于转换器、其附近或下方,则不需要分离接地。

2巴伦的选择问题,规格及类型ADI的参考设计里面一般推荐是mini circuit的巴伦,但也有有高端的marki的巴伦变压器,动则上千元一个。

高速电路设计指南2020071516540002

简介通常来说,高速电路是指电路处理的信号频率足够高使得传输线对该频率表现的阻抗足以对信号产生影响,工作在这种频率上的电路。

《高速电路设计指南》以ADI官方网站的技术文章和模拟对话为基础资料来源整理成册。

从设计实践角度出发,介绍在高速电路设计中需要掌握的各项技术及技能。

ADI智库是ADI公司面向中国工程师打造的一站式资源分享平台,除了汇聚ADI官网的海量技术资料、视频外,还有大量首发的、免费的培训课程、视频直播等。

九大领域、十项技术,加入ADI智库,您可以尽情的浏览收藏、下载相关资源。

此外,您还可一键报名线上线下会议活动,更有参会提醒等贴心服务。

目录终结高速转换器带宽术语 (3)高速转换器:内涵、原因和原理概述 (8)高速差分ADC驱动器设计指南 (16)高速放大器测试需要足够多的数学知识以使巴伦运转! (44)高速DAC宽带输出网络知识与设计 (52)高速ADC的电源设计 (57)低频和高频电路接地 (66)了解JESD204B规范的各层——从高速ADC的角度出发 (74)高速模数转换器精度透视 (83)第一部分 (83)第二部分 (89)高速ADC PCB布局布线规则 (103)第一部分 (103)第二部分 (103)第三部分 (104)第四部分 (105)高速ADC PCB布局布线技巧 (106)终结高速转换器带宽术语有很多令人困惑的规格都与转换器带宽有关。

为了在新的设计中选用适当的转换器,我应当使用什么带宽术语呢?开始一个新设计时,需要决定的首要参数就是带宽。

带宽为设计指明方向,引导设计人员开辟通往成功之路。

本质上有三类前端可供选择:基带型、带通或超奈奎斯特型(有时也称为窄带或子采样型——基本上不会用到第1奈奎斯特区)以及宽带型,如图1所示。

前端的选用取决于具体应用。

图1. 基带、带通与宽带,F SAMPLE =200MSPS。

基带设计要求的带宽是从直流(或低kHz/MHz区)到转换器的奈奎斯特频率。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

The World Leader in High Performance Signal Processing SolutionsA Practical Guide toHigh-Speed Printed CircuitBoard LayoutAgendaOverviewSchematicLocation location locationLocation, location, locationPower supply bypassingParasiticsGround and power planesPackagingRF Signal routing and shielding SummaryOverviewPCB layout is one of the last steps in the design process and often one of the most criticalHigh-speed circuit performance is heavily dependant onHigh speed circuit performance is heavily dependant on layoutA high-performance design can be rendered useless due to a poor or sloppy layoutpoor or sloppy layoutToday’s presentation will help:p y pz Improve the layout processz Ensure expected circuit performance is achievedz Reduce design timeL tz Lower costz Lower stress for you and the PCB designerThe World Leader in High Performance Signal Processing SolutionsSchematicSchematicA good layout starts with a good Schematic! Schematic flow and contentInclude as much information as you canInclude as much information as you canWhat should you include?Items to Include on a Schematic N tNotesComponent tolerances and case sizesPart numbers (internal/external/alternative)Board stack upTests or alignment procedurespPower dissipationControlled impedance and line matchingComponent de-ratingThermal requirementsThermal requirementsKeep outsMechanical considerationsCritical component placementCritical component placementWarning flagsWhat ever else you can think of!SchematicThe World Leader in High Performance Signal Processing SolutionsLocation, location, location! Location location location!Location, Location, LocationLocation Location LocationJust as in real estate location is everything!Input/output and power connections are typically defined…Everything else is undefinedd fi d E thi l i d fi dz Critical component placementSignal routingz Signal routingz Circuit and component proximityThe World Leader in High Performance Signal Processing SolutionsPower Supply BypassingPower Supply BypassingBypassing is essential tohigh speed circuitpperformanceCapacitors right at powersupply pinsCapacitors provide low ACz Capacitors provide low ACimpedance to groundz Provide local charge storagefor fast rising/falling edgesf f t i i/f lli dPower Supply BypassingBypassing is essential tohigh speed circuitperformance +V S L1pCapacitors right at powersupply pinsCapacitors provide low ACIC C10.1µF 1µH z Capacitors provide low AC impedance to groundz Provide local charge storagef f t i i /f lli dµfor fast rising/falling edges Keep trace lengths shortEQUIVALENT DECOUPLED POWER LINE CIRCUIT RESONATES AT:f =1f =2πLC √f = 500kHzPower Supply BypassingBypassing is essential tohigh speed circuitpperformanceCapacitors right at powersupply pinsCapacitors provide low ACz Capacitors provide low ACimpedance to groundz Provide local charge storagefor fast rising/falling edgesf f t i i/f lli dKeep trace lengths shortPower Supply BypassingBypassing is essential tohigh speed circuitpperformanceCapacitors right at powersupply pinsCapacitors provide low ACz Capacitors provide low ACimpedance to groundz Provide local charge storagefor fast rising/falling edgesf f t i i/f lli dKeep trace lengths shortClose to load returnClose to load returnz Helps minimize transientcurrents in the ground planePower Supply BypassingB i i ti l tBypassing is essential to high speed circuit performanceC i i hCapacitors right at power supply pins z Capacitors provide low AC i d t dimpedance to groundz Provide local charge storage for fast rising/falling edgesK t l th h tKeep trace lengths short Close to load returnz Helps minimize transient pcurrents in the ground planeValuesz Individual circuit performance d dua c cu t pe o a cePower Supply Bypassing B i i ti l tBypassing is essential tohigh speed circuitperformanceC i i hCapacitors right at powersupply pinsz Capacitors provide low ACimpedance to groundimpedance to groundz Provide local charge storage forfast rising/falling edgesKeep trace lengths shortKeep trace lengths shortClose to load returnz Helps minimize transient currentsin the ground planein the ground planeValuesz Individual circuit performanceMaintains low AC impedancez Maintains low AC impedancePower Supply Bypassing B i i ti l tBypassing is essential tohigh speed circuitperformanceCapacitors right at powerCapacitors right at powersupply pinsz Capacitors provide low ACimpedance to groundP id l l h t fz Provide local charge storage forfast rising/falling edgesKeep trace lengths shortClose to load returnClose to load returnz Helps minimize transient currentsin the ground planeValuesz Individual circuit performancez Maintains low AC impedancez Multiple resonancesPower Supply Bypassing B i i ti l t hi hBypassing is essential to high speed circuit performanceCapacitors right at powersupply pinssupply pinsz Capacitors provide lowimpedance AC returnProvide local charge storage forz Provide local charge storage forfast rising/falling edgesKeep trace lengths shortClose to load returnz Helps minimize transient currentsin the ground planeValuesz Individual circuit performancez Maintains low AC impedancez Multiple resonancesFerrite beadsThe World Leader in High Performance Signal Processing SolutionsParasiticsParasiticsPCB parasites take the form of undesired capacitors PCB parasites take the form of undesired capacitors, inductors and resistors embedded within the PCBParasitics are extremely difficult to remove from a PCB Prevention is the best method to minimize parasiticsTrace/Pad CapacitancedAdkA C 3.11=K = relative dielectric constantA iA = area in cm 2Trace/Pad CapacitanceTrace/Pad CapacitanceApproximate Trace InductanceAll dimensions are in mmAll dimensions are in mmApproximate Trace InductanceAll dimensions are in mmExampleL= 25.4mmW = .25mm()H = .035mm (1oz copper)Strip Inductance = 28.8nHAt 10MHz Z L 1.86 Ωa 3.6% errorAt10MHz Z=1.86a3.6%errorin a 50ΩsystemApproximate Trace InductanceAll dimensions are in mmExampleL= 2.54cm =25.4mm Minimize Inductance 1)Use Ground planeW = .25mmH = .035mm (1oz copper)1) Use Ground plane2) Keep length short (halvingthe length reducesi d b44%)() Strip Inductance = 28.8nHAt10MHz Z=1.86a3.6%errorinductance by 44%) 3) Doubling width only reduces inductance byAt 10MHz Z L 1.86 Ωa 3.6% errorin a 50Ωsystem11%Via ParasiticsVia Cross SectionD 2T&HDD 1Capacitor Parasitic ModelResistor Parasitic ModelLow Frequency Op Amp SchematicHigh Speed Op Amp Schematic/en/design-tools/dt-multisim-spice-program-download/design-center/index.htmlHigh Speed Op Amp SchematicParasitic CapacitanceStray Capacitance Simulation SchematicFrequency Response with 2pF Stray Capacitance1.8dB peaking1.8dB peakingStray InductanceParasitic InductanceParasitic Inductance Simulation SchematicAD805525.4mm x .25mm” =29nHPulse Response With and Without Ground Plane0.6dB overshootTransient Response AD80091GHz Current Feedback AmplifierR F 402Ω+5V R G 5V 10uF 402Ω0.1uF 0.1uF 150Ω10uF -5VSmall Changes Can Make a Big Difference!Circuit ACi it A Circuit BCi it BImproper Use of Scope Probe Ground ClipEffect of Clip Lead InductanceProper Grounding for Scope Probe in High-Speed MeasurmentsSmall Changes Make Big Differences Circuit ACircuit B21ns17ns25% reduction in ringing duration and amplitudeThe World Leader in High Performance Signal Processing SolutionsGround and Power PlanesGround and Power Planes Provide A common reference pointShieldingLower noiseLower noiseLower resistancepLower impedanceReduces parasiticsHeat sinkPower distributionGround PlaneIIGround Plane and Trace RoutingGround Plane and Trace Routing。