针对BGA封装的四层和六层高速PCB设计指南

4-12多层PCB层叠方案

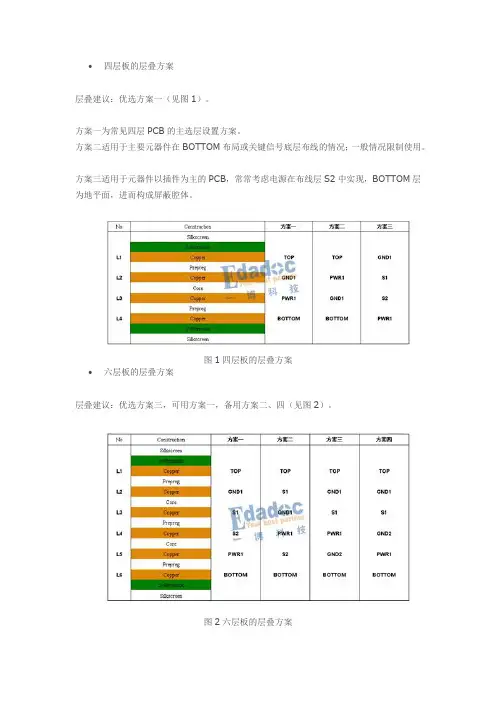

∙四层板的层叠方案层叠建议:优选方案一(见图1)。

方案一为常见四层PCB的主选层设置方案。

方案二适用于主要元器件在BOTTOM布局或关键信号底层布线的情况;一般情况限制使用。

方案三适用于元器件以插件为主的PCB,常常考虑电源在布线层S2中实现,BOTTOM层为地平面,进而构成屏蔽腔体。

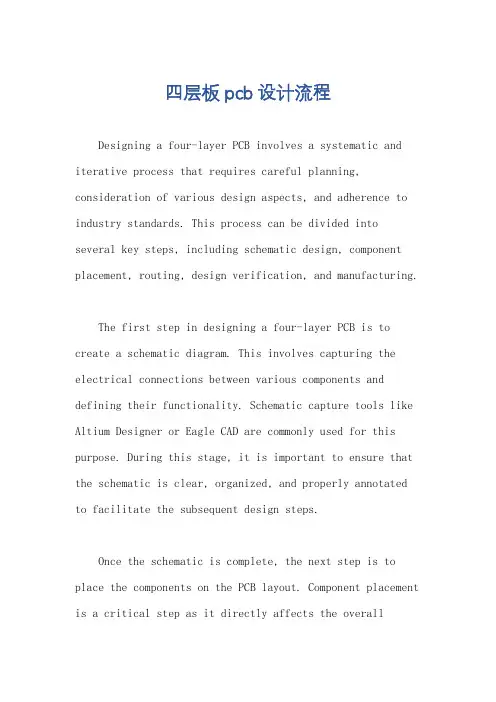

图1四层板的层叠方案∙六层板的层叠方案层叠建议:优选方案三,可用方案一,备用方案二、四(见图2)。

图2六层板的层叠方案对于六层板,优先考虑方案三,优先布线S1层。

增大S1和PWR1之间的间距,缩小PWR1和GND2之间的间距,以减小电源平面的阻抗。

在数码消费等对成本要求较高的时候,常采用方案一,优先布线S1层。

与方案一相比,方案二保证了电源、地平面相邻,减少电源阻抗,但所有走线全部裸露在外,只有S1才有较好的参考平面;不推荐使用。

但在埋盲孔设计时,优先采用此方案。

对于局部、少量信号要求较高的场合,方案四比方案三更适合,它能提供极佳的布线层S1。

十层板的层叠方案层叠建议:推荐方案一、方案二(见图3)。

图3十层板的层叠方案对于单一电源层的情况,首先考虑方案一。

层叠设置时,加大S1~S2、S3~S4的间距控制串扰。

对于需要两电源层的情况,首先考虑方案二。

层叠设置时,加大S1~S2、S3~S4的间距控制串扰。

方案五EMC效果较佳,但与方案四比,牺牲一个布线层;在成本要求不高、EMC指标要求较高且必须双电源层的核心单板,建议采用此种方案;优先布线层S1、S2。

十二层板的层叠方案层叠建议:推荐方案一、方案三(见图4)。

图4十二层板的层叠方案。

四层板pcb设计流程

四层板pcb设计流程Designing a four-layer PCB involves a systematic and iterative process that requires careful planning, consideration of various design aspects, and adherence to industry standards. This process can be divided into several key steps, including schematic design, component placement, routing, design verification, and manufacturing.The first step in designing a four-layer PCB is to create a schematic diagram. This involves capturing the electrical connections between various components and defining their functionality. Schematic capture tools like Altium Designer or Eagle CAD are commonly used for this purpose. During this stage, it is important to ensure that the schematic is clear, organized, and properly annotated to facilitate the subsequent design steps.Once the schematic is complete, the next step is to place the components on the PCB layout. Component placement is a critical step as it directly affects the overallperformance and manufacturability of the PCB. Careful consideration must be given to factors such as signal integrity, power distribution, and thermal management. It is important to place components in a logical and efficient manner, taking into account any design constraints or requirements.After component placement, the routing phase begins. This involves connecting the components using copper traces on the PCB. Proper routing techniques are crucial to ensure signal integrity, minimize noise, and optimize the overall performance of the PCB. The routing process can be done manually or with the help of automated routing tools, depending on the complexity of the design. It is important to adhere to design rules and guidelines provided by the PCB manufacturer during this stage.Once the routing is complete, the next step is to perform design verification. This involves checking the PCB design for any errors, such as electrical connectivity issues, design rule violations, or potential manufacturing problems. Design verification can be done using varioustools, such as Design Rule Checkers (DRC) and SignalIntegrity (SI) analysis tools. It is important tothoroughly review and validate the design to ensure its functionality and manufacturability.Finally, the completed PCB design is ready for manufacturing. It is important to generate the necessary manufacturing files, such as Gerber files, drill files, and assembly drawings, which provide the necessary information for the fabrication and assembly processes. It is recommended to work closely with the chosen PCBmanufacturer to ensure that the design meets their specific requirements and to address any potential manufacturing issues.In conclusion, designing a four-layer PCB involves a systematic and iterative process that encompasses various stages, including schematic design, component placement, routing, design verification, and manufacturing. Each step requires careful consideration, adherence to design rules and guidelines, and collaboration with the PCB manufacturer. By following these steps and considering various designaspects, one can ensure a successful and efficient four-layer PCB design.。

PCB叠层设计层的排布原则和常用层叠结构

PCB叠层设计层的排布原则和常用层叠结构

一、PCB叠层设计层的排布原则

1、符合设计要求

PCB的叠层设计层要符合系统的结构要求,如信号传输、控制线路、

电源线路等。

这些要求具体取决于系统的功能和特点,要根据系统的需求

做出具体的叠层设计。

2、选择合适的铜厚度

叠层的设计要根据系统的参数,如电源电压和负载,确定线路的电阻

和电容,并估算线路的截面积。

根据截面积和PCB板材的铜厚度,确定叠

层设计中适当的铜厚度。

3、信号传输需求

叠层的设计需要考虑信号传输的需求,包括信号传输的速度、范围和

灵敏度。

线路的长度、铜厚度和布线方式,均会影响信号的传输特性。

因此,在叠层设计中要充分考虑信号传输的需求,进行合理的设计。

4、传输功耗过大

在进行叠层设计时,要注意线路的连接方式,避免节点功耗过大,以

免引起线路内部温度升高,影响系统的稳定性和可靠性。

5、保证叠层间的绝缘性

在PCB的叠层设计中,要注意保证叠层间的绝缘性,避免接触和短路。

这不仅有利于线路的正常工作,也有助于降低功耗,提高系统性能。

1、4层PCB

4层 PCB(4 Layer PCB)是一种常见的PCB叠层结构。

在PCB设计中高效地使用BGA信号布线技术

在PCB设计中高效地使用BGA信号布线技术在PCB设计中,BGA(Ball Grid Array)是一种常用的封装技术,它在相同面积下可以提供更高的引脚密度,因此适用于处理高速和高密度的布线需求。

在使用BGA封装技术进行信号布线时,有几个重要的因素需要考虑,以确保设计的高效可靠。

1.规划布线通道:在BGA布线中,通常有两种常用策略:单层布线和多层布线。

单层布线通常在引脚数量较少,较低的布线密度情况下使用;而多层布线则适用于引脚数量较多,布线密度较高的情况下。

在规划布线通道时,需要考虑尽量短的信号路径,减少信号传输延迟和串扰的可能性。

2.信号分组:将BGA封装中的引脚按照信号类型进行分组是有效的信号布线策略。

可将相似功能的引脚放置在相互靠近的位置,并通过同一信号层进行布线,以减少信号之间的干扰。

同时,高频和低频信号应尽量分离布线,减少串扰。

3.增加布线层:BGA封装通常包含了大量引脚,为了布线需要足够的PCB层。

增加布线层可以提供更多的信号层,以便高效地进行多层布线。

通常建议使用4层以上的PCB来布线BGA,以便分配足够的信号和地平面。

4.使用阵列布线:BGA封装的引脚通常呈阵列状排列,因此可以使用阵列布线技术来提高布线效率。

阵列布线指的是使用平行布线或90度布线方式将相邻引脚连接起来。

这种布线方式可以减少信号路径长度,降低串扰的可能性。

5.路由约束:在进行BGA信号布线之前,需要制定一些路由约束,以确保布线的高效和可靠。

例如,可以对布线层的走线宽度和间距进行约束,保证足够的空间进行布线,并避免信号交叉或短路。

6.使用信号地和电源地:BGA信号布线时,需要保持良好的信号完整性和减少噪声。

为了实现这一点,可以采用分离的信号地和电源地,确保它们之间保持足够的距离,以减少可能的干扰。

7.使用垂直引脚:BGA封装通常具有多行多列引脚,其中垂直引脚的布线更容易实现。

因此,在布线时,应优先考虑使用垂直引脚进行布线,以便在布线通道中留下更多的空间,便于其他引脚的布线。

PCB四层板教程

PCB四层板教程PCB(Printed Circuit Board)是电子设备中最常用的一种基板,它用来连接和支持电子组件,同时提供电气和机械支持。

四层板是其中一种类型,相比双层板,四层板可以提供更高的布线密度,更好的电磁兼容性和抗干扰能力。

在本篇教程中,我将为您介绍如何设计和制作一个四层板。

第一步:设计规划在设计之前,您需要明确您的设计需求和目标。

首先,确定所需要布局的组件数量和类型,以及它们之间的连接关系。

其次,选定适当的PCB尺寸和形状,以确保它可以适应您的设备中。

最后,考虑信号和电源分布,分配适当的射频、高速信号和地平面,以减少串扰和信号死角。

第二步:原理图设计在原理图设计中,您将创建一个电路连接图。

选择适当的EDA (Electronic Design Automation)工具,如Eagle、Altium Designer 等,并创建一个新的工程文件。

在原理图中添加符号来代表您所使用的电子元件,并根据规划好的布局连接它们。

确保正确命名每个引脚,以便在布局和布线阶段更容易进行。

第三步:布局在布局阶段,您将决定各个组件的物理位置,并分配相应的电源和地平面。

根据您设定的约束条件,选择适当的布局方法,如集中式布局、分层布局等。

关注高功率和高频率组件的散热和电源分布,以避免热点和噪声问题。

使用自动布局工具辅助调整和优化布局。

第四步:分层在四层板中,将信号层和电源层分开是非常重要的,以减少信号串扰和电源噪声。

将高速信号放在内层或上层,而将地和电源放在内、外层。

在布局软件中,创建内层和外层规划,然后分配信号和地层。

第五步:布线在布线阶段,您将连接每一个元件和电路之间的信号线路。

选择适当的线宽和间距,以确保足够的电流和阻抗控制。

将高速信号和时钟线路保持短而直接,并避免穿越敏感区域。

使用信号完整性工具,如走线检查和信号完整性仿真,来验证和优化布线结果。

第六步:设计规则检查在设计完成后,进行设计规则检查是必不可少的。

高速PCB设计指南2

高速PCB设计指南2高速pcbo指南高速pcbo指南II第一篇高密度(hd)路的o本文介绍了B和s中的许多人认为晶圆模具的BGA密封B受到Y型sub-B产品所需的空g的限制一可行的解q方案,它同rm足@些b品更高功能c性能的要求。

y型b品的高密度路ob配工著想。

今天的R值正在推动霓虹草鱼子产品B、产品R、性能C、可靠性是第一个测试]。

在@City_L中进行凿毛的用户必须注意B配置的效率,因为@喘振控制成本高。

sub-b产品的技术GM步骤和}s性别的正b增长ω对高密度道路u施工方法的需求。

O需要表面Nb、密集g距离和矢量密封B的EW路径ICR可能需要具有^和^密集g间距的高密度路面板。

然而,展望未来,一些已经提供微旁路孔和序列MB板的公司正在投入大量的容量@高密度子b品的_l者越碓绞艿因素的挑穑何锢恚}s元件上更密的引_g隔、力nb必很精密、和h境s多塑z封b吸潮,造成b配理期g的破裂。

物理因素也包括安b工的}s性c最kb品的可靠性。

m一步的政q定必考]b品⑷绾窝u造和b配o湫率。

^脆弱的引_元件,如0〃50c0〃40mm0〃020″c0〃016″引_g距的sqfpshrinkquadflatpack,可能在so一持m的b配工合格率方面向b配<姨岢鲆挑稹w畛晒φ拈_l是那些已行工jc的路板o指引和工jc的焊p缀涡睢在H环境中,焊接P基于所用sub-b零件的焊接类型。

在可能的情况下,将P形与nκ焊接,使用Mei Mo为B感到羞耻,并以透明的方式工作。

无论零件是安装在板的一侧,还是进行波峰、回流焊或其他焊接,PC零件的焊接尺寸应确保焊接CCZ为CM。

然而,焊接局部放电外壳的尺寸为x,K受B的生存能力水平以及C、G、B或其他l零件的公差限制。

就生物学特性而言,G在CWD病例中的R位置为P。

1、焊p的要求H技术小组委员会tiecinternational ELETROTECH mission的61188收到Jr关于在新H腐蚀下焊接拐角或P凸l零件的不同术语。

PCB高速板4层以上的设计经验(综合)

PCB高速板4层以上的设计经验PCB高速板4层以上的布线经验:1、3点以上连线,尽量让线依次通过各点,便于测试,线长尽量短。

2、引脚之间尽量不要放线,特别是集成电路引脚之间和周围。

3、不同层之间的线尽量不要平行,以免形成实际上的电容。

4、布线尽量是直线,或45度折线,避免产生电磁辐射。

5、地线、电源线至少10-15mil以上(对逻辑电路)。

6、尽量让铺地多义线连在一起,增大接地面积。

线与线之间尽量整齐。

7、注意元件排放均匀,以便安装、插件、焊接操作。

文字排放在当前字符层,位置合理,注意朝向,避免被遮挡,便于生产。

8、元件排放多考虑结构,贴片元件有正负极应在封装和最后标明,避免空间冲突。

9、目前印制板可作4—5mil的布线,但通常作6mil线宽,8mil线距,12/20mil焊盘。

布线应考虑灌入电流等的影响。

10、功能块元件尽量放在一起,斑马条等LCD附近元件不能靠之太近。

11、过孔要涂绿油(置为负一倍值)。

12、电池座下最好不要放置焊盘、过空等,PAD和VIL尺寸合理。

13、布线完成后要仔细检查每一个联线(包括NETLABLE)是否真的连接上(可用点亮法)。

14、振荡电路元件尽量*近IC,振荡电路尽量远离天线等易受干扰区。

晶振下要放接地焊盘。

15、多考虑加固、挖空放元件等多种方式,避免辐射源过多。

高速PCB过孔设计技巧在高速PCB板设计中,过孔设计是一个重要因素,它由孔、孔周围的焊盘区和POWER层隔离区组成,通常分为盲孔、埋孔和通孔三类。

在PCB板设计过程中通过对过孔的寄生电容和寄生电感分析,总结出高速PCB板过孔设计中的一些注意事项。

目前高速PCB板的设计在通信、计算机、图形图像处理等领域应用广泛,所有高科技附加值的电子产品设计都在追求低功耗、低电磁辐射、高可靠性、小型化、轻型化等特点,为了达到以上目标,在高速PCB板设计中,过孔设计是一个重要因素。

1、过孔过孔是多层PCB板设计中的一个重要因素,一个过孔主要由三部分组成,一是孔;二是孔周围的焊盘区;三是POWER层隔离区。

四层pcb板制作工艺流程

四层pcb板制作工艺流程英文回答:The manufacturing process of a four-layer PCB board involves several key steps to ensure the quality and functionality of the final product.Step 1: Substrate Preparation.The first step in the process is to prepare the substrate, which is typically made of fiberglass-reinforced epoxy laminate. The substrate is cleaned and then coated with a layer of copper on both sides.Step 2: Inner Layer Core Preparation.Next, the inner layer cores are prepared by laminating together layers of fiberglass-reinforced epoxy with copper foil. The layers are then etched to create the circuitry pattern.Step 3: Layer Alignment and Bonding.The inner layer cores are aligned and bonded together with the substrate to create a multi-layered panel. This is done using heat and pressure to ensure a strong bond between the layers.Step 4: Drilling.Small holes are drilled through the panel at specific locations to create electrical connections between the different layers. These holes are then plated with copper to create vias.Step 5: Outer Layer Core Preparation.Similar to the inner layer cores, the outer layer cores are prepared by laminating together layers of fiberglass-reinforced epoxy with copper foil. The layers are then etched to create the outer layer circuitry pattern.Step 6: Outer Layer Lamination.The outer layer cores are aligned and bonded to the panel, creating a four-layer PCB. This is done using heat and pressure, similar to the inner layer bonding process.Step 7: Plating and Etching.The outer layer circuitry is plated with a thin layer of solder mask and then etched to remove any excess copper, leaving only the desired circuitry pattern.Step 8: Surface Finishing.The final step in the process is to apply a surface finish to the PCB, which can include options such as hotair solder leveling (HASL), immersion gold, or immersion tin.中文回答:四层PCB板的制作工艺流程包括以下关键步骤,以确保最终产品的质量和功能性。

bgapcb设计方法

bgapcb设计方法

BGA(球栅阵列)PCB设计方法涉及多个关键步骤,包括确定信号层数、控制扇出等。

以下是一个简化的BGA PCB设计流程:

1. 确定信号层数:根据电路板需求确定所需的信号层数,这将影响平面层数以及布线到设计中所需的最终走线宽度。

2. 扇出:扇出是从器件焊盘到相邻过孔的走线。

这个过程需要考虑如何进入和退出BGA,以及是否需要控制阻抗。

3. 使用BGA开始PCB布局:由于BGA通常是设备中的主处理器,并且可能需要与电路板上的许多其他组件连接,因此通常的做法是先放置最大的BGA组件并使用它开始布局PCB。

4. 接地和电源:确保正确处理接地和电源问题,这对于确保电路板的功能和可靠性至关重要。

5. 定义合适的退出路径:在布局过程中,定义合适的退出路径以优化布线效率。

在设计过程中,需要考虑到BGA焊盘和封装的布局,包括使用过孔进行各层之间的电气连接,以及如何处理焊盘和扇出的布局。

此外,还需要根据产品特定可靠性标准进行高可靠性设计。

请注意,以上信息仅供参考,建议咨询专业人士获取具体信息。

PCB四层电路板教程

PCB四层电路板教程PCB(Printed Circuit Board)即印刷电路板,是一种用于连接和支持电子元件的基板。

它通常由一层或多层的导电材料(如铜箔)和绝缘材料(如树脂胶)组成。

这个四层PCB电路板教程将介绍四层PCB电路板的制作步骤和注意事项。

一、设定原理图和PCB布局首先,你需要设计电路的原理图和布局。

选择合适的设计工具,例如EAGLE或Altium Designer,创建原理图和布局。

确保按照电子元器件的规格和尺寸进行布局设计,并留出适当的空间用于连线。

二、导入原理图到PCB设计工具将设计好的原理图导入到PCB设计工具中,根据设计规范和要求设置PCB布局。

这包括将元件放置在合适的位置,确定线路的走向和长度,以及确保元件之间的间距足够大以避免短路或干扰。

三、划分地电平和供电电平四层PCB电路板通常将地电平和供电电平划分到内层(层2和层3)中。

地电平是为了提供电路中所有地连接之间的最低电阻路径。

供电电平则提供稳定的电源给整个电路。

四、划分信号层和分布电容层剩余的两层(外层)则可以用于信号层和分布电容层。

信号层用于布线,连接电子元件和器件之间的信号线。

分布电容层用于安置电容器,以提供局部的电源补偿和降低噪音。

五、布置层间连接和通孔在布局和分层电路时,需要考虑到将各层之间的连接和通孔。

连接和通孔在四层PCB电路板中非常重要,因为它们构成了四层电路板的关键部分。

六、布线和连线开始进行布线和连线。

跟随原理图和布局设计,将电子元件之间用导线连接起来。

确保走线路径合适,避免交叉、干扰和短路。

同时,注意信号线和电源线的区分和布局,以降低噪音和干扰。

七、规范检查和修订完成布线后,进行规范检查。

确保每个连线都符合设计规范和要求。

检查通孔和连接是否准确并符合设计要求。

如果有需要,进行修订和调整。

八、生成PCB制作文件完成规范检查后,生成PCB制作文件。

将PCB设计导出到Gerber文件格式,这是一种广泛应用于PCB制造的文件格式。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

表 2: 有助于尽量降低成本的制造规则

特征尺寸

英制 (mils)

公制 (mm)

BGA 球焊盘直径

15

0.381

迹线宽度

5

0.127

间隔

5

0.127

过孔外径

23

0.584

过孔外径

12

0.305

球栅间距、引出 路径和扇出端

FT256 BGA 封装遵循表 2 中迹线宽度和间隔的制造规则,其 BGA 球栅间距为 1 mm/40 mils。 如图 1 所示,FT256 封装的所有信号都集中在两层上 (例如顶层和底层)。

简介

尽量降低成本的 PCB 设计规则

左右 PCB 成本的主要因素有两个:制造能力和产量。设计低成本 PCB 的规则取决于 PCB 生产 设备能按最低价格制造出什么。这一现实情况还决定着在既保持低成本又适于大批量制造的电 路中可实现的 PCB 层数。遗憾的是,市场对增加可编程逻辑的封装引脚数的需求意味着更小 的形状因数,因此加大了对 PCB 布局成本的压力。尽管如此,如果使用 FT256 1 mm 球栅阵列 (BGA) 封装的 Spartan-3E FPGA,仍然能以尽量低的成本设计出四层电路板。

如果用外来设计规则 (如 1 mils 迹线与间隔)设计电路板,则可选的制造方案有限,且成本高 昂。一密耳即千分之一英寸,亦称一英毫,等于 0.0254 毫米。某些北美厂家或许能够用这些 规则制造电路板,但将此种 PCB 制造工艺搬到亚洲的主流生产设备上却不大可能大幅度降低 成本。随着产量的提高,有更多厂家乐于制造电路板以降低成本,但是,达到可接受的成本所 需的时间可能比产品的寿命还要长。本应用指南即针对这一情况提出能改进制造方案和降低成 本的一些解决办法。

XAPP489 (v1.0) 2006 年 10 月 31 日

/cn

1

球栅间距、引出路径和扇出端

R

表 2 所列为业界广泛接受、能尽量降低制造成本的制造规则。例如,小迹线的公差难以控制; 而设计迹线宽度不小于 5 mils 的 PCB (如表 2 所示)可尽量降低制造成本。

XAPP489 (v1.0) 2006 年 10 月 31 日

/cn

5

电源平面

电源平面

R

Spartan-3E 的高速设计成功地使用了一种单层三分面。图 7 所示为该设计的四分之一。这种 设计具有 200-300 ps 的边沿速率,同时切换 LVCMOS 3.3V I/O 时的切换噪声为 80。

X489_01_050106

FT256 封装的阵列大小为 16 x 16 个焊球。忽略分布在周围的电源焊球,从一层上引出三个外 围焊球环,这种能力仅从顶层就可以最多引出 156 路信号。图 2 所示为 XC3S500E 演示板顶信 号层上由三个外围行组成的完整信号扇出的一个四分之一扇面。

XAPP489 (v1.0) 2006 年 10 月 31 日

© 2006 Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and further disclaimers are as listed at /legal.htm. All other trademarks and registered trademarks are the property of their respective owners. All specifications are subject to change without notice. NOTICE OF DISCLAIMER: Xilinx is providing this design, code, or information "as is." By providing the design, code, or information as one possible implementation of this feature, application, or standard, Xilinx makes no representation that this implementation is free from any claims of infringement. You are responsible for obtaining any rights you may require for your implementation. Xilinx expressly disclaims any warranty whatsoever with respect to the adequacy of the implementation, including but not limited to any warranties or representations that this implementation is free from claims of infringement and any implied warranties of merchantability or fitness for a particular purpose.

X489_03_032306

图 3: 底层上的迹线引出路径

XAPP489 (v1.0) 2006 年 10 月 31 日

/cn

3

过孔位置

过孔位置

R

应尽可能将信号过孔限制在球栅中部,使过孔朝向焊盘外侧。如果不控制过孔的位置和尺寸以 有效布置引出路径,则过孔有可能阻塞引出路径。Spartan-3E FPGA 的大多数电源引脚都位于 阵列中部,所以这些引脚所需的过孔阻塞引出路径的可能性极小。 图 4 所示为 XC3S500E FT256 封装的完整扇出。因为对称的过孔形式允许将 2 至 3 行焊球引出 到顶层,所以只用两个信号层即可引出所有信号。I/O 信号的过孔显示为黄褐色。所有其他过 孔均为电源过孔,如表 3 所定义。

表 1 所示为不同制造地点大量生产不同层数 PCB 的制造成本。层越多,制造成本越高;具体 成本因产量和市场条件而异。

表 1: PCB 制造成本

制造地点 美国国内

亚洲

成本 (美元 / 平方英尺)(1)

2层

4层

6层

0.18

0.22

0.24

0.13

0.16

0.17

注: 1. 这是 2004 年中期估算的成本,假定板材利用率为 100%,未包括不可用面积 (如划线截去的面积)。

/cn

7

电源平面

R

在本特例中,电路板的高速 LVDS 信号在 VCCO = 2.5V 下传输,要求有一个 100 Ω 的差动控制 阻抗。可以用与顶层 LVDS 信号耦合的接地平面和与第四层 LVDS 信号耦合的第三层 2.5V VCCO 面区满足这一阻抗要求。

六层电路板堆栈示例

/cn

2

球栅间距、引出路径和扇出端

R

X489_02_033006

图 2: 顶层的一个四分之一扇面

这个扇出图案是对称的,适用于全部四个四分之一扇面。所有迹线和过孔格局都是呈扇形从阵 列中心向外展开。

对底层其余内部焊球行用过孔重复这一做法,便可最多引出 84 个信号引脚。图 3 所示为演示 板底层上所用的引出路径。因为 Spartan-3E FT256 封装中心下方的电路板上有许多接地引 脚,所以 FT256 封装的所有引出路径都可通过邻近的过孔直接接地。在紧靠 BGA 封装区域的 外沿,引出迹线至少可以散开成 6 mils 宽外加 6 mils 间隔。

应用指南:Spartan-3E 系列

R

XAPP489 (v1.0) 2006 年 10 月 31 日

针对 Spartan-3E FT256 BGA 封装的四层和六层 高速 PCB 设计

提要

本应用指南针对 FT256 1 mm BGA 封装的 Spartan™-3E FPGA,讨论了低成本、四至六层、 大批量印刷电路板 (PCB) 的布局问题,同时探讨高速信号和信号完整性 (SI) 因素对低层数 PCB 布局的影响。本应用指南的读者为设计工程师、管理人员和 PCB 布局人员,他们对与 SI 相关 的设计问题应当已经有所了解。本应用指南主要讲述 FT256 封装的 Spartan-3E 器件,但这些 信息也适用于同等的 FG256 封装,其中包含的通用指南可用于优化其他器件和封装的电路板 布局。

图 4: 过孔位置和扇出

X489_04_081206

表 3: 过孔类型图例

颜色 绿 粉 深蓝 浅绿 黄褐

电压 (V) 0 2.5 1.2

多种 多种

信号

地 VCCAUX VCCINT VCCO

I/O

图 5 仅显示 FT256 封装中过孔的四分之一,以便放大显示过孔的形式和对称性。

XAPP489 (v1.0) 2006 年 10 月 31 日

XAPP489 (v1.0) 2006 年 10 月 31 日

图 8: 分面示例

/cn

X489_08_032606

6

电源平面

R

各面区应尽可能连续而无间断。在图 8 中,浅蓝色和红色面区显然是连续的。图 9 所示为电路 板的放大图,其中的黄色面区也可以看成是连续的。

图 9: 连续的黄色面区 图 10 所示为此电路板上所用的实心接地平面。

在六层电路板中,可以对电源平面使用多种堆栈组合。表 5 所示为针对去耦合优化的六层堆 栈。在此堆栈中,四个面层提供了三个去耦电容器。把第三层和第四层的两个接地平面放在一 起是一种不良的堆栈方法,因为这样会大大降低有效的面去耦作用。在第一层和第二层的未用 板区和辅助板区上覆满铜 (这些板区与面电压相连),也可以加强电源平面的去耦作用。可以 在第五层和第六层上使用同样的技术。

Z = 2πFL