实验四_基本时序逻辑电路的VHDL模型

VHDL语言的时序电路设计

VHDL语言的时序电路设计-----设计一个可逆计数译码显示电路一、实验目的掌握VHDL设计的基本方法,进一步熟悉MAX+PLUSII的使用。

二、实验内容1、具有清除端、使能端,计数范围为0—9的可逆计数器设计。

输出为8421BCD码。

2、8421BCD码—七段LED译码显示电路设计。

三、实验条件(1)电脑。

(2)开发软件:MAX+PLUSII。

(3)实验设备:EL—EDA—V型、EDA实验开发系统。

(4)拟用芯片:ACEX1K:EP1K100QC208-3。

四、实验要求1、用VHDL设计上述两个电路,用元件例化的方式实现顶层设计。

2、完成功能仿真和时序仿真。

3、对设计结果进行下载和硬件测试。

提示:设计可以采用自顶向下的设计方法或自底向上的设计方法。

一般采用自顶向下的设计方法,即先对顶层进行系统结构描述,再组建底层设计。

五、实验步骤1、用元件例化的方式实现顶层设计;2、设计具有异步清除端、同步使能端,计数范围为0—9的十进制可逆计数器;3、设计8421BCD码/七段LED的显示译码器。

六、实验设计(1)可逆计数、译码及显示电路的VHDL语言程序LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;------entity count10_top isport(CLR,EN,UP,CLK: in STD_LOGIC;LED7S: OUT STD_LOGIC_VECTOR(6 DOWNTO 0);CO,BO: OUT STD_LOGIC);end count10_top;-------architecture a of count10_top iscomponent count10port( CLR,EN,UP,CLK: in STD_LOGIC;Q: OUT STD_LOGIC_VECTOR(3 DOWNTO 0);CO,BO: OUT STD_LOGIC );end component;component DEC7Sport(A: in STD_LOGIC_VECTOR(3 DOWNTO 0);LED7S: OUT STD_LOGIC_VECTOR(6 DOWNTO 0));end component;SIGNAL D: STD_LOGIC_VECTOR(3 DOWNTO 0);beginU1:count10 PORT MAP (CLR,EN,UP,CLK,D,CO,BO);U2:DEC7S PORT MAP (D,LED7S);end a;----LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;entity count10 isport(CLR,EN,UP,CLK: in STD_LOGIC;Q: BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0);CO,BO: OUT STD_LOGIC);end count10;-----architecture b of count10 isbeginProcess(CLR,EN,UP,CLK)beginIF CLR='0' THENQ<="0000";ELSIF CLK'EVENT AND CLK='1' THENIF EN='1' THENIF UP='1' THENIF Q=9 THENQ<="0000";ELSEQ<=Q+1;END IF;ELSEIF Q=0 THENQ<="1001";ELSEQ<=Q-1;END IF;END IF;END IF;END IF;END Process;CO<='1' when Q=9 ELSE'0';BO<='1' when Q=0 ELSE'0';end b;-----LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;entity DEC7S isPORT(A:IN BIT_VECTOR(3 DOWNTO 0);LED7S:OUT BIT_VECTOR(6 DOWNTO 0)); END DEC7S;ARCHITECTURE one OF DEC7S ISBEGINPROCESS(A)BEGINCASE A(3 DOWNTO 0) ISWHEN "0000"=>LED7S<="0111111";WHEN "0001"=>LED7S<="0000110";WHEN "0010"=>LED7S<="1011011";WHEN "0011"=>LED7S<="1001111";WHEN "0100"=>LED7S<="1100110";WHEN "0101"=>LED7S<="1101101";WHEN "0110"=>LED7S<="1111101";WHEN "0111"=>LED7S<="0000111";WHEN "1000"=>LED7S<="1111111";WHEN "1001"=>LED7S<="1101111";WHEN OTHERS=>NULL;END CASE;END PROCESS;END one;(2)仿真波形(1)系统仿真情况系统功能仿真结果与时序仿真结果分别如图1、图2所示:图1、系统功能仿真结果图2、系统时序仿真结果从系统仿真结果可以看出,本系统完全符合设计要求。

vhdl实验报告

vhdl实验报告VHDL实验报告引言:VHDL(Very High Speed Integrated Circuit Hardware Description Language)是一种硬件描述语言,广泛应用于数字电路设计和仿真。

本篇实验报告将介绍我在VHDL实验中的学习和实践经验,包括实验目的、实验过程、实验结果以及对VHDL的理解和展望。

一、实验目的VHDL实验的主要目的是让我们掌握VHDL语言的基本语法和使用方法,能够利用VHDL描述数字电路,并通过仿真和综合工具进行验证和实现。

通过这些实验,我们可以深入了解数字电路的原理和设计方法,提高我们的逻辑设计能力和工程实践能力。

二、实验过程在实验过程中,我们首先学习了VHDL的基本语法,包括实体声明、端口声明、信号声明等。

然后,我们通过实例学习了VHDL的建模方法,包括组合逻辑电路的建模和时序逻辑电路的建模。

在组合逻辑电路的建模中,我们学习了使用逻辑运算符和条件语句描述电路的功能;在时序逻辑电路的建模中,我们学习了使用过程语句和时钟信号描述电路的状态转换。

在学习了VHDL的基础知识后,我们开始进行实验设计。

我们选择了一个简单的数字电路,如4位加法器,来进行实验验证。

首先,我们通过VHDL语言描述了加法器的功能和结构,包括输入端口、输出端口和中间信号。

然后,我们使用仿真工具进行了功能仿真,验证了加法器的正确性。

接着,我们使用综合工具将VHDL代码综合成门级电路,并进行了时序仿真和时序优化,验证了加法器的时序正确性和性能。

三、实验结果通过实验,我们成功地实现了4位加法器的功能,并验证了其正确性和性能。

在功能仿真中,我们输入了不同的测试数据,观察了输出结果,发现加法器能够正确地进行加法运算,并得到了正确的结果。

在时序仿真中,我们观察了电路的时序行为,包括输入信号的变化、输出信号的响应和中间信号的传播延迟等,发现加法器能够在时序上满足要求,并且具有较好的性能。

VHDL实验(完整版)

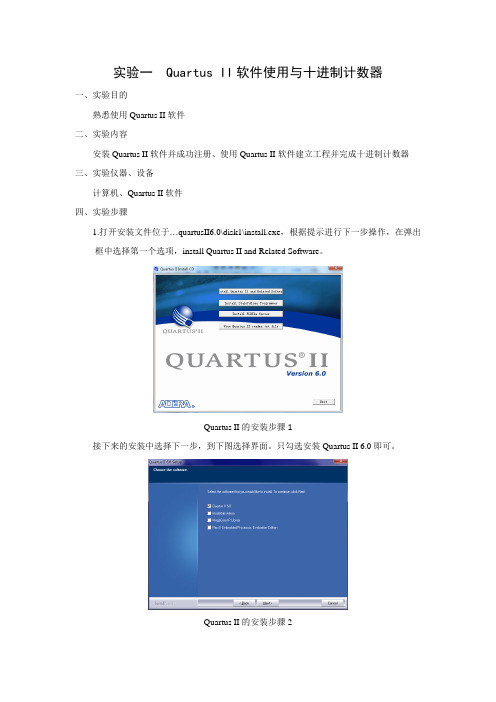

实验一 Quartus II软件使用与十进制计数器一、实验目的熟悉使用Quartus II软件二、实验内容安装Quartus II软件并成功注册、使用Quartus II软件建立工程并完成十进制计数器三、实验仪器、设备计算机、Quartus II软件四、实验步骤1.打开安装文件位于…quartusII6.0\disk1\install.exe,根据提示进行下一步操作,在弹出框中选择第一个选项,install Quartus II and Related Software。

Quartus II的安装步骤1接下来的安装中选择下一步,到下图选择界面。

只勾选安装Quartus II 6.0即可。

Quartus II的安装步骤22.完成安装步骤2后选择下一步至下图所示,选择完全安装complete,再继续点击下一步至安装开始。

完全安装Quartus II软件软件安装途中出现如下图所示情况时,选择安装文件中的…disk2\disk2\quartus,然后选择确定——OK继续安装直到结束。

安装过程中换disk2路径Quartus II软件的安装至此结束,此安装步骤WINXP/WIN 7均有效,WIN8若有问题,请修改兼容权限。

3.软件注册。

软件安装结束后打开Quartus II软件将出现下图所示情况,这是没有注册的提醒,我们必须先进行注册才能建立工程文件,若大家忽略了这个提示窗口,直接进行工程建立等工作,任何仿真图和编译功能都无法正常使用,等于白费功夫浪费时间,还要重新(由于软件注册是绑定MAC物理地址,所以每台机器的license 做,非常影响学习兴趣和情绪。

是完全不一样的,实验室的电脑已经安装好了Quartus II软件,但是没有注册,所以做实验的时候一点要先注册,不然就白做了)Quartus II软件提示未注册弹窗注册方法,打开quiic7.1 lisence 生成器文件夹中的keymaker.exe,在弹出的窗口中点击Make License,在文件夹中就会出现和本台机器相匹配的license.dat。

实验四 实验4 VHDL语言进行简单时序电路——一 JK触发器的设计

实验4 VHDL语言进行简单时序电路——一JK触发器的设计一、实验目的学习在QuartusⅡ下用VHDL语言设计简单时序电路与功能仿真的方法。

二、验仪器设备1、PC机一台2、QuartusⅡ。

三、实验要求1、预习教材中的相关内容,编写出JK触发器的VHDL源程序。

2、用VHDL语言输入方式完成电路设计,编译、仿真。

四、实验内容及参考实验步骤一、设计输入1、开机,进入QuartusⅡ。

2、为本工程设计建立一个文件夹。

3、建立设计文件。

选择File菜单之New项,选择文件类型,本设计选择VHDLFile。

建立一个文本编辑文件4、输入源程序, 保存文件。

注意,必须保存为vhd类型,且文件名与源程序的实体名相同。

二、创建工程并编译1、创建一个新的工程,将多路选择器文件加入工程。

2、编译。

点击Start Compilation按钮进行编译。

如果发现错误,改正后再次编译。

三、仿真1、建立波形文件。

选择File菜单之New项,选择Other Fles中的Vector WaveformFile文件类型,建立一个波形文件2、设定仿真时间。

选择菜单Edit的End Time ….项设定仿真时间域。

例如1us.3、输入端口信号。

选择菜单View的Utility Windows项的Node Finder选项,在弹出得出的对话框中单击List按钮,将需要的端口信号拖倒波形编辑器中。

4、编辑输入波形。

在输入端口加上适当的信号,以便在输出端进行观察。

5、保存文件。

6、进行仿真。

点击Start Simulation按钮进行仿真。

7、观察分析波形。

观察仿真结果,并进行波形分析,看是否与设计相符。

五、实验报告1、根据实验过程写出试验报告2、总结用VHDL语言的设计流程3、总结时序电路的设计方法。

附录JK触发器VHDL源程序library ieee;use ieee.std_logic_1164.all;entity jkff1 isport(j,k:in std_logic;clk:in std_logic;q,qn:out std_logic);end entity jkff1;architecture bhv of jkff1 issignal q1:std_logic;beginprocess(clk)beginif clk'event and clk='1' thenif j='1'and k='0' then q1<='0';elsif j='0'and k='1' then q1<='1';elsif j='1'and k='1' then q1<=not q1;else q1<=q1;end if;end if;end process;q<=q1;qn<=not q1;end architecture bhv;。

EDA-VHDL时序逻辑电路实验

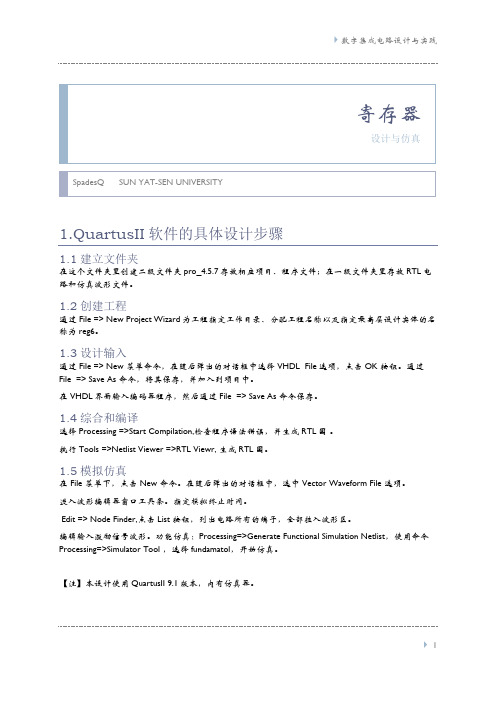

1.QuartusII软件的具体设计步骤1.1建立文件夹在这个文件夹里创建二级文件夹pro_4.5.7存放相应项目、程序文件;在一级文件夹里存放RTL电路和仿真波形文件。

1.2创建工程通过 File => New Project Wizard为工程指定工作目录、分配工程名称以及指定最高层设计实体的名称为reg6。

1.3设计输入通过 File => New 菜单命令,在随后弹出的对话框中选择 VHDL File选项,点击 OK 按钮。

通过File => Save As 命令,将其保存,并加入到项目中。

在VHDL界面输入编码器程序,然后通过 File => Save As 命令保存。

1.4综合和编译选择Processing =>Start Compilation,检查程序语法错误,并生成RTL图。

执行Tools =>Netlist Viewer =>RTL Viewr, 生成RTL图。

1.5模拟仿真在 File 菜单下,点击 New 命令。

在随后弹出的对话框中,选中 Vector Waveform File 选项。

进入波形编辑器窗口工具条。

指定模拟终止时间。

Edit => Node Finder,点击 List 按钮,列出电路所有的端子,全部拉入波形区。

编辑输入激励信号波形。

功能仿真:Processing=>Generate Functional Simulation Netlist,使用命令Processing=>Simulator Tool ,选择fundamatol,开始仿真。

【注】本设计使用QuartusII 9.1版本,内有仿真器。

2.程序设计library ieee;use ieee.std_logic_1164.all;entity reg6 isport(clk:in std_logic;r :in std_logic;d :in std_logic_vector(5downto0);q :out std_logic_vector(5downto0)); end reg6;architecture behavioral of reg6 issignal q_temp:std_logic_vector(5downto0); beginprocess(clk,r)beginif(r='1')thenq_temp<="000000";elsif(clk'event and clk='1')thenq_temp<=d;end if;end process;q<=q_temp;end behavioral;3.RTL电路寄存器RTL电路4.功能仿真波形图:reg6寄存器仿真结果波形分析:仿真图显示,reset为高电平时,输出为000000,其他输出根据clk上升沿来临时跳变为输入,符合逻辑。

基本时序电路设计(使用VHDL语言)

实验报告一、实验目的熟悉利用QuartusⅡ的VHDL文本设计流程,学习基本时序电路的设计、多层次电路设计、编译及仿真全过程。

二、实验内容1.设计含异步清零和同步时钟使能的加法计数器。

(1)代码:(2)仿真波形仿真结果分析:clr为清零端,当clr=‘0’时,计数清零;enb为使能端,当enb=‘1’时,允许计数,enb=‘0’时,禁止计数;cout为输出端,计数范围为0~15。

实验内容(6)(1)原理图:(2)仿真波形2.设计7段数码显示译码器。

(1)代码:(2)仿真波形仿真结果分析:七段显示管中的七段分别对应的是O[6]~O[0],当输入为0时,显示0(01111111),十六进制为3F;当输入为1时,显示1(0000110),十六进制为06,一次类推.实验内容3:(1)代码:(2)计数器和译码器连接电路的顶层文件原理图(2)仿真波形仿真结果分析:该原理图的工作原理跟七段显示管的工作原理是一样的(上一题),只是它又引入了一个4位二进制计数器(包括使能端),让所设计的原理图能自动计数并且显示出来。

3.设计数控分频器。

(1)代码:(2)仿真波形实验仿真分析:当在输入端LOAD给定不同输入数据时,将对输入的时钟信号有不同的分频比.三、实验环境计算机、QuartusII软件四、实验结果与讨论1、从实验的仿真波形分析可知,每个程序都可以满足相对的功能条件,与理论结果一致.2、在设置数控分频器时,我只设置4位的,但如果想得到八位的或更高的只要稍微修改里面的参数即可。

六、总结(1)在设计计数器和译码器的连接电路时,一开始忘记cout=‘0’,导致输出cout都没变化,后面根据仿真波形才发现自己的错误。

(2)设计数控分频器,由于对数控分频器原理理解不够透彻,导致了花的时间比较多,不然前面的实验都能在比较快的时间内完成。

VHDL与数字电路设计实验报告

VHDL与数字电路设计实验报告引言本实验旨在通过使用VHDL编程语言和数字电路设计技术,实现特定功能的电路设计。

本文档将对实验的步骤、设计原理和结果进行详细描述。

实验步骤1. 步骤一:熟悉VHDL编程语言在实验开始之前,团队成员对VHDL编程语言进行了研究和熟悉。

我们了解了VHDL的基本语法、数据类型和结构,并获得了对VHDL设计原理的初步理解。

2. 步骤二:设计功能电路在本实验中,我们选择了一个特定的功能电路进行设计。

我们首先进行了功能需求分析,并根据需求确定了电路的输入输出信号以及主要的逻辑运算。

然后,我们使用VHDL编程语言将电路的逻辑运算实现为代码,并进行了仿真和测试。

3. 步骤三:电路仿真和验证为了验证我们设计的电路功能的正确性,我们使用了VHDL仿真工具进行了电路的仿真和验证。

我们根据输入信号的不同组合,观察输出信号的变化,并与我们预期的结果进行比较。

通过这一步骤,我们确认了我们设计的电路能够按照预期工作。

4. 步骤四:电路实现和测试在确认电路的设计和仿真结果无误之后,我们进一步将电路实现到实际的数字电路平台上,并进行了硬件测试。

我们使用实际的输入信号来测试电路的性能和稳定性,并对输出信号进行观察和分析。

通过这一步骤,我们验证了电路在实际环境中的可行性。

设计原理我们设计的电路基于特定的功能需求,采用了经典的数字电路设计原理。

通过使用VHDL编程语言,我们将电路的逻辑运算实现为逻辑门和触发器的组合。

通过将输入信号连接到适当的逻辑门和触发器,我们实现了所需的功能。

结果与分析经过实验步骤的完成,我们成功地设计和实现了一个具有特定功能的数字电路。

在仿真测试和实际测试中,电路都表现出了良好的性能和稳定性。

根据结果的分析,我们验证了电路的设计原理和逻辑的正确性。

结论本实验通过使用VHDL编程语言和数字电路设计技术,成功地实现了一个具有特定功能的电路设计。

我们的实验结果表明,VHDL和数字电路设计技术在电路设计领域具有重要的应用价值。

数电实验报告

一、实验名称1. 实验一QuartusⅡ原理图输入法设计与实现2. 实验二用VHDL设计与实现组合逻辑电路(一)3. 实验三用VHDL设计与实现时序逻辑电路(二)4.实验四用VHDL设计与实现时序逻辑电路(三)(数码管动态扫描控制器)二、实验任务要求1.实验一:○1用逻辑门设计实现一个半加器,仿真验证其功能,并生成新的半加器图形模块单元;○2用上面生成的半加器模块和逻辑门设计实现一个全加器,仿真验证其功能,并下载到实验板测试,要求用拨码开关设定输入信号,发光二极管显示输出信号;○3用3线-8线译码器(74LS138)和逻辑门设计实现函数F=CBA+CBA+CBA+CBA,仿真验证其功能,并下载到实验班测试。

要求用拨码开关设定输入信号,发光二极管显示输出信号;2.实验二:○1用VHDL语言设计实现一个4位二进制奇校验器,输入奇数个…1‟时,输出为…1‟,否则输出为…0‟,仿真验证其功能,并下载到实验板测试。

要求用拨码开关设定输入信号,发光二极管显示输出信号;○2用VHDL语言设计实现一个8421码转换为余3码的代码转换器,仿真验证其功能,并下载到实验板测试。

要求用拨码开关设定输入信号,发光二极管显示输出信号;○3用VHDL语言设计实现一个共阴极7段数码管译码器,仿真验证其功能,并下载到实验班测试。

要求用拨码开关设定输入信号,发光二极管显示输出信号;3.实验三:○1用VHDL语言设计实现一个分频系数为12,分频输出信号占空比为50%的分频器。

要求在Quartus Ⅱ平台上设计程序并仿真验证设计;○2用VHDL语言设计实现一个带异步复位的8421码十进制计数器,仿真验证其功能,并下载到实验板测试。

要求用拨码开关设定输入信号,发光二极管显示输出信号;○3将分频器、8421十进制计数器、数码管译码器3个电路进行连接并下载测试。

4.实验四:○1用VHDL语言设计并实现六个数码管串行扫描电路,要求同时显示0、1、2、3、4、5这6个不同的数字图形到6个数码管上,仿真验证其功能,并下载到实验板测试;(必做)○2用VHDL语言设计并实现六个数码管循环左滚动,时钟点亮6个数码管,坐出右进,状态为:012345→123450→234501→345012→450123→501234→012345;(选做)○3用VHDL语言设计并实现六个数码管向左滚动,用全灭的数码管填充右边,直至全部变灭,然后再一次从右边一个一个地点亮。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验四基本时序逻辑电路的VHDL模型

一、实验目的

1掌握简单的VHDL程序设计。

2 掌握VHDL语言对基本时序逻辑电路的建模。

二、实验内容

分别设计并实现锁存器、触发器的VHDL模型。

(一)寄存(锁存)器

1 实验原理

寄存器用于寄存一组二值代码,广泛用于各类数字系统。

因为一个触发器能储存1位二值代码,所以用N个触发器组成的寄存器能储存一组N位的二值代码。

2 实验内容:

实现同步锁存器(同步锁存器指复位和加载功能全部与时钟同步,复位端的优先级最高。

在数字系统设计时,采用完全同步的锁存器,可以避免时序错误。

)

附:一个8位寄存器的VHDL描述。

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY REG IS

PORT(D:IN STD_LOGIC_VECTOR(0 TO 7); CLK:IN STD_LOGIC;

Q:OUT STD_LOGIC_VECTOR(0 TO 7));

END REG;

ARCHITECTURE ART OF REG IS

BEGIN

PROCESS(CLK)

BEGIN

IF(CLK'EVENT AND CLK=‘1’)THEN

Q<=D;

END IF;

END PROCESS;

END ART;

(二)触发器

实验内容:

1、D触发器

1)、带异步置位的D触发器(当时钟信号或置位信号有跳变时激活进程。

如果置位信号有效(高电平),D触发器被置位,输出信号高电平,如果置位

信号无效,此时时钟信号出现上升沿,D触发器输出信号变为输入信号);

2)、带异步复位和置位的D触发器(当时钟信号、复位信号或置位信号有跳变时激活进程。

如果复位信号有效(高电平),D触发器被复位,输出信号低电平;如果复位信号无效置,而置位信号有效(高电平),D触发器被置位,输出信号高电平,如果复位信号和置位信号都无效,此时时钟信号出现上升沿,D触发器输出信号变为输入信号)。

附:最简单的D触发器,没有复位和职位信号。

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY DCFQ IS

PORT(D,CLK:IN STD_LOGIC;

Q:OUT STD_LOGIC);

END DCFQ;

ARCHITECTURE ART OF DCFQ IS

BEGIN

PROCESS(CLK)

BEGIN

IF (CLK'EVENT AND CLK=‘1’)THEN -- 时钟上升沿触发

Q<=D;

END IF;

END PROCESS;

END ART;

上述触发器为最简单的D触发器,没有复位和职位信号。

根据上例写一个

2、JK触发器

从真值表可以看出,PRN=0 时,触发器置数,Q=’1’;CLRN=0 时,触发器清零,Q=’0’;当

PRN=CLRN=J=K=’1’时,在CLK 上升沿的时候,触发器翻转。

3)RS触发器

四、实验报告

1、简要说明实验步骤。

2、写出实验用的VHDL源程序。

3、记录仿真结果(波形),说明输出延时情况。

4、记录实验结果,并分析其结果的正确性。

5、说明实验中遇到的问题及解决方法,写出实验心得体会。

实验心得体会

做完EDA实验,我感到受益匪浅。

这不仅使我了解了EDA的实验系统,学习了MAX+PLUSⅡ软件的使用,掌握了基本的电路设计流程、方法以及技巧,更增强了我对EDA设计的兴趣。

在实验的过程中,老师又结合实际详细的教了我们VHDL语言的基本指令及编程方法,教我们熟悉了在PC机上运用MAX+PLUSⅡ软件和EPLD进行电路设计的设计和仿真过程。