实例—使用make及Makefile文件

make makefile 的参数

make makefile 的参数make是一个常用的构建工具,用于自动化编译和构建软件项目。

makefile是make工具的配置文件,用于描述项目的构建规则和依赖关系。

本文将介绍makefile的参数,包括常用的参数及其用法。

一、常用参数及其用法1. -f 文件名:指定makefile的文件名,默认为"makefile"或"Makefile"。

通过该参数,可以使用其他名称的makefile文件。

2. -C 目录:指定make命令的工作目录。

在执行make命令时,会切换到指定的目录,并在该目录下查找makefile文件进行构建。

3. -n:显示执行make命令时的操作,但不实际执行。

通过该参数,可以预览make命令的执行过程,检查构建规则是否正确。

4. -p:显示make命令的内置变量和规则。

通过该参数,可以查看make命令的内部工作机制,了解makefile文件的编写规则和使用方法。

5. -B:强制重新构建目标文件。

通过该参数,可以忽略文件的时间戳,强制重新执行构建规则,生成新的目标文件。

6. -j 并发数:指定make命令的并发执行数。

通过该参数,可以提高构建速度,同时执行多个任务。

7. -s:静默模式,不显示执行的命令。

通过该参数,可以减少输出信息,使构建过程更加清晰。

二、makefile的构建规则makefile由一系列构建规则组成,每个规则定义了目标文件、依赖文件和构建命令。

make命令根据构建规则,自动判断需要更新的文件,并执行相应的构建命令。

构建规则的基本格式如下:目标文件: 依赖文件构建命令其中,目标文件是要生成的文件,依赖文件是目标文件依赖的文件,构建命令是生成目标文件的命令。

构建规则中的目标文件和依赖文件可以是文件名,也可以是变量。

通过使用变量,可以提高makefile的可维护性和灵活性。

构建命令可以是任意的Shell命令,包括编译、链接、拷贝等操作。

c语言makefile编写实例

c语言makefile编写实例Makefile是用来管理程序编译的工具,可以方便地管理程序的编译过程。

使用Makefile可以大大简化程序的编译过程,提高程序的可维护性。

Makefile的语法比较简单,主要由目标、依赖和命令三部分组成。

下面我们以一个简单的C程序为例,来介绍如何使用Makefile进行编译。

假设我们有一个名为hello.c的程序,代码如下:```c#include <stdio.h>int main(){printf("Hello, world!\n");return 0;}```我们需要使用gcc编译器将其编译成可执行文件。

下面是一个简单的Makefile:```makefilehello: hello.cgcc -o hello hello.c```这个Makefile很简单,它定义了一个名为hello的目标,该目标依赖于hello.c文件,并使用gcc命令将其编译成可执行文件。

如果我们在终端中输入make命令,Makefile会自动执行编译过程:```$ makegcc -o hello hello.c```Makefile还可以定义多个目标,每个目标可以有多个依赖和多个命令。

下面是一个稍微复杂一些的Makefile:```makefileCC=gccCFLAGS=-Wall -gall: hello goodbyehello: hello.o$(CC) $(CFLAGS) -o hello hello.ogoodbye: goodbye.o$(CC) $(CFLAGS) -o goodbye goodbye.ohello.o: hello.c$(CC) $(CFLAGS) -c hello.cgoodbye.o: goodbye.c$(CC) $(CFLAGS) -c goodbye.cclean:rm -f *.o hello goodbye```这个Makefile定义了两个目标:all和clean。

makefile中make指令传入的参数

makefile中make指令传入的参数Makefile中make指令传入的参数是指在执行make命令时,可以通过命令行传入的参数。

这些参数可以用于控制程序的编译、运行等行为,使得程序更加灵活和可配置。

在Makefile中,我们可以通过在命令行中输入make和参数来执行相应的操作。

参数可以是任意的字符串,可以用于指定编译选项、目标文件、源文件等等。

下面我将结合一些实际的例子,来详细讲解一下如何使用make指令传入的参数。

我们需要在Makefile中定义一些变量,用于存储传入的参数。

可以通过在命令行中使用“变量名=参数值”的方式来传入参数。

例如,我们可以定义一个变量CC,用于存储编译器的路径:```CC = gcc```在命令行中执行make命令时,可以通过“make CC=/usr/local/bin/gcc”来传入参数,将编译器的路径设置为“/usr/local/bin/gcc”。

接下来,我们可以在Makefile中使用这些参数。

例如,我们可以使用$(CC)来表示编译器的路径:```$(CC) -o target source.c```在执行make命令时,make会将$(CC)替换为实际的参数值,然后执行相应的命令。

这样,我们就可以通过命令行传入不同的编译器路径,来编译源文件。

除了编译器的路径,还可以通过命令行传入其他的参数。

例如,我们可以定义一个变量CFLAGS,用于存储编译选项:```CFLAGS = -Wall -O2```在命令行中执行make命令时,可以通过“make CFLAGS=-g”来传入参数,将编译选项设置为“-g”。

然后,我们可以在Makefile中使用这些参数。

例如,我们可以在编译命令中加入$(CFLAGS):```$(CC) $(CFLAGS) -o target source.c```在执行make命令时,make会将$(CFLAGS)替换为实际的参数值,然后执行相应的命令。

makefile make install 用法举例 -回复

makefile make install 用法举例-回复Makefile是一个用于管理代码编译和构建的工具,其中make install是Makefile中的一个常见目标。

在此文章中,我将一步一步介绍make install的用法,并提供相应的示例。

一、Makefile概述:Makefile是一个文本文件,用于指定代码编译和构建的规则。

通过Makefile,我们可以定义各种目标(target),每个目标包含一组依赖项(dependencies)和相应的命令(commands),用于生成目标文件。

其中,make install是一个常见的目标,用于将编译好的文件安装到指定的位置。

二、make install用法:make install的主要作用是将编译完成的文件复制到指定的目录中。

这个目录可以是系统级的目录,也可以是用户级的目录。

对于系统级的目录,一般需要管理员权限进行安装。

以下是make install的用法示例:1. 默认安装到系统级目录:在Makefile中定义一个目标install,并在该目标中使用相应的命令将文件复制到系统级目录(如/usr/local/bin)中。

示例代码如下:makefileinstall:cp myapp /usr/local/bin在命令行中执行make install命令即可将编译好的myapp文件复制到/usr/local/bin目录中。

2. 指定安装目录:如果我们想将文件安装到其他目录,可以通过make install命令的参数来指定目标目录。

示例代码如下:makefileinstall:mkdir -p /opt/myappcp myapp /opt/myapp在命令行中执行make install PREFIX=/opt/myapp命令即可将编译好的myapp文件复制到/opt/myapp目录中。

3. 用户级安装:对于一些软件,用户可以选择在自己的文件夹中进行安装,而无需管理员权限。

Make命令完全详解教程

Make命令完全详解教程无论是在Linux还是在Unix环境中,make都是一个非常重要的编译命令。

不管是自己进行项目开发还是安装应用软件,我们都经常要用到make或make install。

利用make工具,我们可以将大型的开发项目分解成为多个更易于管理的模块,对于一个包括几百个源文件的应用程序,使用make和makefile工具就可以简洁明快地理顺各个源文件之间纷繁复杂的相互关系。

而且如此多的源文件,如果每次都要键入gcc命令进行编译的话,那对程序员来说简直就是一场灾难。

而make工具则可自动完成编译工作,并且可以只对程序员在上次编译后修改过的部分进行编译。

因此,有效的利用make和makefile工具可以大大提高项目开发的效率。

同时掌握make和makefile之后,您也不会再面对着Linux下的应用软件手足无措了。

一、Make程序的命令行选项和参数Make命令参数的典型序列如下所示:make [-f makefile文件名][选项][宏定义][目标]这里用[]括起来的表示是可选的。

命令行选项由破折号“–”指明,后面跟选项,如也可以每个选项使用一个破折号,如甚至混合使用也行,如Make命令本身的命令行选项较多,这里只介绍在开发程序时最为常用的三个,它们是:–k:如果使用该选项,即使make程序遇到错误也会继续向下运行;如果没有该选项,在遇到第一个错误时make程序马上就会停止,那么后面的错误情况就不得而知了。

我们可以利用这个选项来查出所有有编译问题的源文件。

–n:该选项使make程序进入非执行模式,也就是说将原来应该执行的命令输出,而不是执行。

–f :指定作为makefile的文件的名称。

如果不用该选项,那么make程序首先在当前目录查找名为makefile的文件,如果没有找到,它就会转而查找名为Makefile的文件。

如果您在Linux下使用GNU Make的话,它会首先查找GNUmakefile,之后再搜索makefile和Makefile。

makefile make install 用法举例

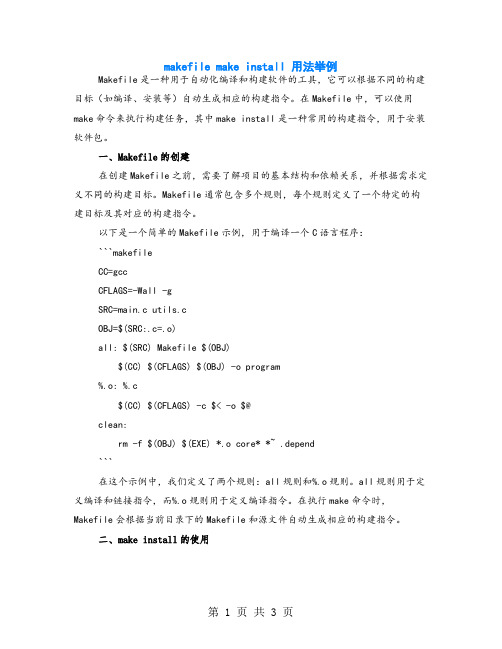

makefile make install 用法举例Makefile是一种用于自动化编译和构建软件的工具,它可以根据不同的构建目标(如编译、安装等)自动生成相应的构建指令。

在Makefile中,可以使用make命令来执行构建任务,其中make install是一种常用的构建指令,用于安装软件包。

一、Makefile的创建在创建Makefile之前,需要了解项目的基本结构和依赖关系,并根据需求定义不同的构建目标。

Makefile通常包含多个规则,每个规则定义了一个特定的构建目标及其对应的构建指令。

以下是一个简单的Makefile示例,用于编译一个C语言程序:```makefileCC=gccCFLAGS=-Wall -gSRC=main.c utils.cOBJ=$(SRC:.c=.o)all: $(SRC) Makefile $(OBJ)$(CC) $(CFLAGS) $(OBJ) -o program%.o: %.c$(CC) $(CFLAGS) -c $< -o $@clean:rm -f $(OBJ) $(EXE) *.o core* *~ .depend```在这个示例中,我们定义了两个规则:all规则和%.o规则。

all规则用于定义编译和链接指令,而%.o规则用于定义编译指令。

在执行make命令时,Makefile会根据当前目录下的Makefile和源文件自动生成相应的构建指令。

二、make install的使用make install是Makefile中常用的一种构建指令,用于将软件包安装到目标系统中。

使用make install命令时,需要指定安装的目标目录和安装选项。

下面是一个简单的示例:假设我们有一个名为myapp的软件包,将其安装到/usr/local/目录下:```bashmake install prefix=/usr/local/```在这个示例中,我们使用make install命令将myapp软件包安装到/usr/local/目录下。

c++的makefile实例

1. 将上述代码保存到一个名为 "Makefile"(注意大小写)的文件中。 2. 将 "your_program" 替换为你的目标程序的名称。 3. 将 "main.cpp"、"file1.cpp" 和 "file2.cpp" 替换为你的源代码文件的名称(如果有更 多文件,可以继续添加)。 4. 运行命令 `make` 来编译和构建你的程序。

c++的makefile实例

- `%.o: %.cpp`:这个规则用于编译每个源代码文件。它将每个 .cpp 文件编译为对应的 .o 文件。

- `clean`:这个规则用于清理生成的目标文件和目标程序。

你可以根据你的实际需要修改和调整这个 Makefile,例如添加其他编译选项、链接库等 。运行命令 `make clean` 可以删除生成的目标文件和目标程序。

all: $(TARGET)

$(TARGET): $(OBJS) $(CC) $(CFLAGS) -o $@ $^

%.o: %.cpp $(CC) $(CFLAGS) -c $< -o $@

clean:

rm -f $(OBJS) $(TARGET)

c++的makefile实例

在这个示例中,你需要做以下几个步骤:

c++的makefile实例

这个 Makefile 的规则解释如下:

- `CC`:定义了编译器的名称(在这里使用了 g++)。 - `CFLAGS`:定义了编译器的选项(在这里使用了 -std=c++11 和 -Wall)。 - `TARGET`:定义了目标程序的名称。 - `SRCS`:定义了源代码文件的名称。 - `OBJS`:定义了目标文件的名称(通过将源文件的扩展名 .cpp 替换为 .o 而得到)。 - `all`:这是一个默认目标,用于构建目标程序。它依赖于 $(TARGET)。 - `$(TARGET)`:这个规则用于构建目标程序。它依赖于 $(OBJS)。通过 $(CC) 命令将目 标文件链接在一起生成最终的可执行文件。

Makefile.am文件的实例讲解

Makefile.am⽂件的实例讲解Makefile.am是⼀种⽐Makefile更⾼层次的编译规则,可以和configure.in⽂件⼀起通过调⽤automake命令,⽣成Makefile.in⽂件,再调⽤./configure的时候,就将Makefile.in⽂件⾃动⽣成Makefile⽂件了。

所以Makefile.am⽂件是⽐Makefile⽂件更⾼的抽象。

下⾯我根据⾃⼰的⼯作中的⼀些应⽤,来讨论Makefile.am的编写。

我觉得主要是要注意的问题是将编译什么⽂件?这个⽂件会不会安装?这个⽂件被安装到什么⽬录下?可以将⽂件编译成可执⾏⽂件来安装,也可以编译成静态库⽂件安装,常见的⽂件编译类型有下⾯⼏种:1. PROGRAMS。

表⽰可执⾏⽂件2. LIBRARIES。

表⽰库⽂件3. LTLIBRARIES。

这也是表⽰库⽂件,前⾯的LT表⽰libtool。

4. HEADERS。

头⽂件。

5. SCRIPTS。

脚本⽂件,这个可以被⽤于执⾏。

如:example_SCRIPTS,如果⽤这样的话,需要我们⾃⼰定义安装⽬录下的example⽬录,很容易的,往下看。

6. DATA。

数据⽂件,不能执⾏。

⼀,可执⾏⽂件先看⼀个实例:bin_PROGRAMS = clientclient_SOURCES = key.c connect.c client.c main.c session.c hash.cclient_CPPFLAGS = -DCONFIG_DIR=\"$(sysconfdir)\" -DLIBRARY_DIR=\"$(pkglibdir)\"client_LDFLAGS = -export-dynamic -lmemcachednoinst_HEADERS = client.hINCLUDES = -I/usr/local/libmemcached/include/client_LDADD = $(top_builddir)/sx/ \$(top_builddir)/util/ 上⾯就是⼀个全部的Makefile.am⽂件,这个⽂件⽤于⽣成client可执⾏应⽤程序,引⽤了两个静态库和MC等动态库的连接。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2.3 实例—使用make及Makefile文件一个工程有3个头文件(head1.h、head2.h、exam2.h)和8个C文件(main.c、exam1.c、exam2.c、exam3.c、exam4.c、exam5.c、exam6.c、exam7.c),建立一个Makefile文件(文件名为makefile),内容如下。

注意,上述12个文件位于同一个目录中。

example : main.o exam1.o exam2.o exam3.o exam4.o exam5.o exam6.o exam7.ogcc -o example main.o exam1.o exam2.o exam3.o exam4.o exam5.o exam6.o exam7.omain.o : main.c head1.hgcc -c main.cexam1.o : exam1.c head1.h exam2.hgcc -c exam1.cexam2.o : exam2.c head1.h exam2.hgcc -c exam2.cexam3.o : exam3.c head1.h head2.hgcc -c exam3.cexam4.o : exam4.c head1.h head2.hgcc -c exam4.cexam5.o : exam5.c head1.h head2.hgcc -c exam5.cexam6.o : exam6.c head1.h head2.h exam2.hgcc -c exam6.cexam7.o : exam7.c head1.hgcc -c exam7.cclean :rm example main.o exam1.o exam2.o exam3.o exam4.o exam5.o exam6.o exam7.omakefile文件告诉make命令如何编译和链接这几个文件。

在当前路径下执行make命令,就可以生成可执行文件example。

如果要删除可执行文件和所有的中间目标文件,只需执行make clean命令即可。

Makefile文件的操作规则是:①如果该工程没有编译过,所有C文件都要编译并被链接。

②如果该工程的某几个C文件被修改,只需编译被修改的C文件,并链接目标程序。

③如果该工程的头文件被改变,需要编译包含这些头文件的C文件,并链接目标程序。

在这个Makefile文件中,目标文件(target)有:执行文件example和中间目标文件(*.o);依赖文件(prerequisites)有:冒号后面的.c文件和.h文件。

每一个.o文件都有一组依赖文件,而这些.o文件又是执行文件example的依赖文件。

依赖关系是指目标文件由哪些文件生成。

在定义好依赖关系后,规则命令定义了如何生成目标文件,其一定要以一个Tab键打头。

make会比较targets文件和prerequisites文件的时间戳,如果prerequisites文件的日期比targets文件的日期要新,或者target不存在,make就会执行相应的规则命令。

默认方式下,执行make命令时,make会在当前目录下找Makefile,如果找到,make 会找文件中的第一个目标文件(target),上面的例子是example文件,并把这个文件作为最终的目标文件。

如果example文件不存在,或example所依赖的.o文件的修改时间比example 文件新,make就会执行相应的规则命令生成example文件。

如果example所依赖的.o文件不存在,make会在当前目录中找目标为.o文件的依赖文件(C文件和H文件),如果找到,则根据规则生成.o文件,然后再用.o文件生成make的最终结果,也就是可执行文件example。

有上可知,make会一层一层地去找文件的依赖关系,直到最终编译出第一个目标文件。

在寻找的过程中,如果出现错误(比如被依赖的文件找不到)make就会直接退出,并报错。

clean不是一个文件,只是一个动作名字,类似于C语言中的lable,冒号后什么也没有,这样make就不会自动去找文件的依赖性,也就不会自动执行其后所定义的规则命令。

要执行其后的命令,就要在make命令后显式的指出这个lable的名字,例如执行make clean命令。

1.在Makefile文件中使用变量其中字符串(main.o exam1.o exam2.o exam3.o exam4.o exam5.o exam6.o exam7.o)被重复了两次。

如果这个工程需要加入一个新的.o文件,需要在三个位置插入该字符串。

如果工程很大,Makefile文件也会很复杂,就要对更多的地方进行修改,因此就容易出错,从而会导致编译失败。

所以,为了Makefile文件的易维护,在Makefile文件中可以使用变量。

Makefile 文件的变量也就是一个字符串(类似于C语言中的宏)。

可以在Makefile文件中以$(objects)的方式来使用这个变量。

改进后的Makefile文件如下:objects = main.o exam1.o exam2.o exam3.o exam4.o exam5.o exam6.o exam7.oexample : $(objects)gcc -o example $(objects)main.o : main.c head1.hgcc -c main.cexam1.o : exam1.c head1.h exam2.hgcc -c exam1.cexam2.o : exam2.c head1.h exam2.hgcc -c exam2.cexam3.o : exam3.c head1.h head2.hgcc -c exam3.cexam4.o : exam4.c head1.h head2.hgcc -c exam4.cexam5.o : exam5.c head1.h head2.hgcc -c exam5.cexam6.o : exam6.c head1.h head2.h exam2.hgcc -c exam6.cexam7.o : exam7.c head1.hgcc -c exam7.cclean :rm example $(objects)2.让make自动推导依赖关系make可以自动推导文件以及文件依赖关系后面的命令,因此没有必要在每一个.o文件后都写上类似的命令。

只要make看到一个.o文件,就会自动把.c文件加在依赖关系中,比如make看到hello.o,就会将hello.c作为hello.o的依赖文件,并且会自动推导出gcc -c hello.c。

修改后的Makefile文件如下:这种方法也就是make的隐含规则。

.PHONY表示clean是个伪目标文件。

伪目标并不是一个文件,只是一个标签。

由于伪目标不是文件,所以make无法生成它的依赖关系和决定它是否要执行,只有通过显式地指明这个目标才能让其生效。

当然,伪目标的取名不能和文件名重名,不然其就失去了伪目标的意义了。

为了避免和文件重名这种情况,可以使用一个特殊的标记.PHONY(假)来显式地指明一个目标是伪目标,告诉make,不管是否有这个文件,这个目标就是伪目标。

在Linux中,软件发布时,特别是GNU这种开放源代码的软件发布时,其Makefile文件都包含了编译、安装、打包等功能。

可以参照这种规则来书写Makefile文件中的目标。

一些常用的伪目标及其功能见表2.10。

表2.10 伪目标及其功能3.清空目标文件的规则每个Makefile文件都应该有一个清空目标文件(.o和执行文件)的规则,这不仅便于在rm命令前面加上一个减号(在Tab键之后),作用是如果某些文件出现问题将被忽略,继续进行后面的操作。

另外,clean规则不要放在Makefile文件的开头,否则会变成make 的默认目标。

不成文的规矩是clean规则放在文件的最后。

4.重新认识Makefile文件Makefile文件主要包含5部分内容:显式规则、隐含规则、变量定义、文件指示和注释。

见表2.11。

表2.11 Makefile文件内容默认情况下,make命令会在当前目录下按顺序寻找文件名为GNUMakefile、makefile、Makefile的文件,找到后解释这个文件。

在这3个文件名中,最好使用Makefile这个文件名。

不要用GNUMakefile文件名。

大多数的make都支持makefile和Makefile这两种默认的文件名。

当然,可以使用别的文件名来书写Makefile文件,此时要使用make的-f或--file选项。

在Makefile文件中使用include关键字可以把别的Makefile文件包含进来,被包含的文件会保持原来的状态,并被放在当前文件的包含位置。

include的语法是:include <filename><filename>可以是当前操作系统Shell的文件模式(可以包含路径和通配符)。

在include 前面可以有一些空字符,但是一定不能以[Tab]键开始。

include和<filename>可以用一个或多个空格隔开。

如果<filename>没有指定绝对路径或相对路径,make会在当前目录下首先寻找,如果当前目录下没有找到,make还会在下面的几个目录下寻找:①如果make有-I或--include-dir参数,就会在该参数所指的目录下去寻找。

②如果目录<prefix>/include存在,make也会去寻找。

如果找到Makefile文件,make命令会将其内容安置在当前的位置。

如果没有找到Makefile文件,make命令会生成一条警告信息,但不会马上出现致命错误信息,它会继续载入其它文件,一旦完成Makefile文件的读取,make会再重试这些没有找到或是不能读取的文件,如果还是不行,make才会出现一条致命错误信息。

如果想让make 忽略那些无法读取的文件,而继续执行,可以在include前加一个减号。

例如:-include <filename>表示无论include过程中出现什么错误,都不会报错而是继续执行。

和其它版本的make 兼容的相关命令是sinclude,其作用和inculde相同。

GNU的make工作时的执行步骤如下:①读入所有的Makefile文件。

②读入被include包括的其它Makefile文件。

③初始化文件中的变量。

④推导隐含规则,并分析所有规则。

⑤为所有的目标文件创建依赖关系链。

⑥根据依赖关系,决定哪些目标要重新生成。