数字电路_第三章答案

(完整版)数字电路与逻辑设计课后习题答案蔡良伟(第三版)

0 1 1 0

0 1 1 1

1 0 0 0

1 0 0 1

1 0 1 0

1 0 1 1

1 1 0 0

1 1 0 1

1 1 1 0

1 1 1 1

0 0 0 0

0 0 0 1

0 0 1 0

0 0 1 1

0 1 0 0

0 1 0 1

0 1 1 0

0 1 1 1

1 0 0 0

1 0 0 1

1 0 1 0

3-6

3-7

3-8

3-9

3-10

求减数的补码,然后与被减数相加即可。电路图如下:

3-11

3-12

(1)

(2)

(3)

(4)

(5)

(6)

(7)

(8)

3-13

(1)真值表:

(2)电路图

3-14

3-15

第四章习题

4-1

4-2

4-3

4-4

4-5

4-6

4-7

4-8

4-9

4-10

RSDRSJK RST

4-11

(1)转换真值表

1 1 0 1

1 1 1 0

1 1 1 1

1 0 1 0

0 0 0 0

0 0 0 1

0 0 1 0

00 11

0 1 0 0

0 1 0 1

0 1 1 0

0 1 1 1

1 0 0 0

1 0 0 1

××××

××××

××××

××××

××××

1×0×1×0×

0×0×0××1

0×0××1 1×

0×0××0×1

0××1 1×1×

数字电路第三章习题答案

数字电路第三章习题答案

3-10

F S 1 A S 0 B A S 0 B A B S 0 A B S 1 S 0 A B F F S 1 A S 0 B A S 0 B A B S 0 A B S 1 S 0 A B

数字电路第三章习题答案

3-11

试用六个与非门设计一个水箱控制电路。图为水箱示意图。A、B、C是三个电极。 当 电极被水浸没时,会有信号输出。水面在A,B间为正常状态,点亮绿灯G;水面在B、 C间或在A以上为异常状态,点亮黄灯Y;水面在C以下为危险状态.点亮红灯R。

3531736半加器的设计1半加器真值表2输出函数3逻辑图输入输出被加数a加数b4逻辑符号31837ab改为用与非门实现函数表达式变换形式

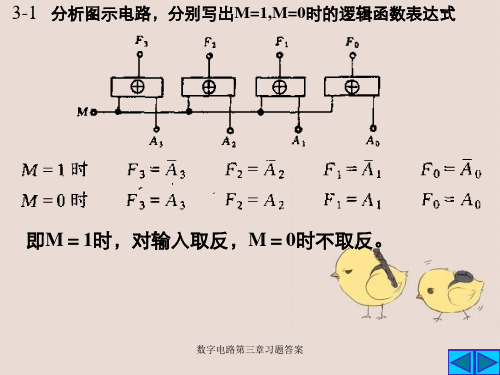

3-1 分析图示电路,分别写出M=1,M=0时的逻辑函数表达式

即M=1时,对输入取反,M=0时不取反。

数字电路第三章习题答案

3-2 分析图示补码电路,要求写出逻辑函数表达式,列出真值表。

3-10 试用与非门设计一个逻辑选择电路。

S1、S0为选择端,A、B为数据输入端。 选择电路的功能见下表。选择电路可 以有反变量输入。

数字电路第三章习题答案

3-10

F S 1 A S 0 B A S 0 B A B S 0 A B S 1 S 0 A B F F S 1 A S 0 B A S 0 B A B S 0 A B S 1 S 0 A B FS 1 S 0A B S 1 S 0(A B )S 1 S 0(A BA)B

数字电路第三章习题答案

3-5

Ai 0 0 0 0 1 1 1 1

Si Ai BiCi Ai BiCi Ai BiCi Ai BiCi

《数字电子技术基础》课后习题答案

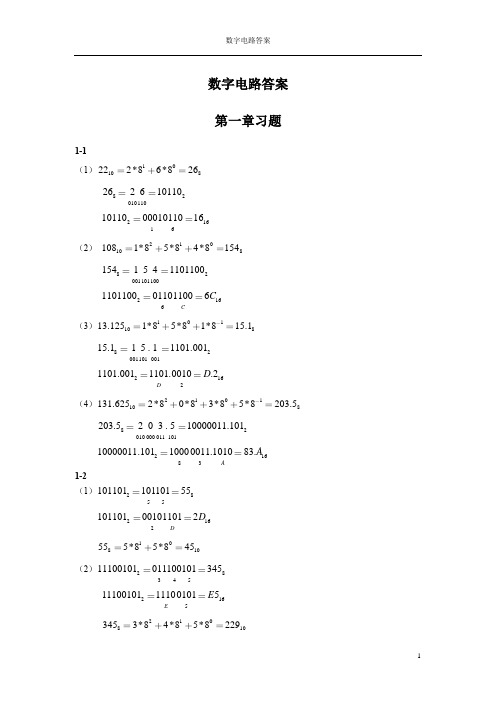

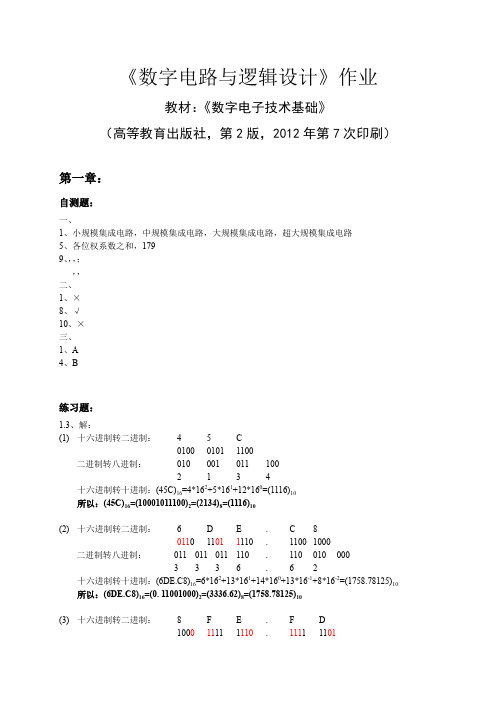

《数字电路与逻辑设计》作业教材:《数字电子技术基础》(高等教育出版社,第2版,2012年第7次印刷)第一章:自测题:一、1、小规模集成电路,中规模集成电路,大规模集成电路,超大规模集成电路5、各位权系数之和,1799、,,;,,二、1、×8、√10、×三、1、A4、B练习题:1.3、解:(1) 十六进制转二进制: 4 5 C0100 0101 1100二进制转八进制:010 001 011 1002 13 4十六进制转十进制:(45C)16=4*162+5*161+12*160=(1116)10所以:(45C)16=(10001011100)2=(2134)8=(1116)10(2) 十六进制转二进制: 6 D E . C 80110 1101 1110 . 1100 1000 二进制转八进制:011 011 011 110 . 110 010 0003 3 3 6 . 6 2十六进制转十进制:(6DE.C8)16=6*162+13*161+14*160+13*16-1+8*16-2=(1758.78125)10 所以:(6DE.C8)16=(0. 11001000)2=(3336.62)8=(1758.78125)10(3) 十六进制转二进制:8 F E . F D1000 1111 1110. 1111 1101二进制转八进制:100 011 111 110 . 111 111 0104 3 7 6 . 7 7 2十六进制转十进制:(8FE.FD)16=8*162+15*161+14*160+15*16-1+13*16-2=(2302.98828125)10 所以:(8FE.FD)16=(1.11111101)2=(437 6.772)8=(2302.98828125)10(4) 十六进制转二进制:7 9 E . F D0111 1001 1110 . 1111 1101二进制转八进制:011 110 011 110 . 111 111 0103 6 3 6 . 7 7 2十六进制转十进制:(79E.FD)16=7*162+9*161+14*160+15*16-1+13*16-2=(1950. )10 所以:(8FE.FD)16=0.11111101)2=(3636.772)8=(1950.98828125)101.5、解:(74)10 =(0111 0100)8421BCD=(1010 0111)余3BCD(45.36)10 =(0100 0101.0011 0110)8421BCD=(0111 1000.0110 1001 )余3BCD(136.45)10 =(0001 0011 0110.0100 0101)8421BCD=(0100 0110 1001.0111 1000 )余3BCD (374.51)10 =(0011 0111 0100.0101 0001)8421BCD=(0110 1010 0111.1000 0100)余3BCD1.8、解(1)(+35)=(0 100011)原= (0 100011)补(2)(+56 )=(0 111000)原= (0 111000)补(3)(-26)=(1 11010)原= (1 11101)补(4)(-67)=(1 1000011)原= (1 1000110)补。

数字电子技术基础(第4版)课后习题答案详解

(b)当v i=0V时, vB为负值 ∴ T截止 vo=5V

当

v

i=5V时,

I

=

B

5-0.7 54。7

−

8.7 18

=

0.42 mA

I BS

≈

5 50 × 2

= 0.05mA <

IB

∴ T饱和

vo ≈ 0.2V (0 ~ 0.3V都行)

悬空时,

I

=

B

5-0.7 4.7

−

8.7 18

=

0.08 mA

I BS

(5)Y =1

2

Y = ABC + ABC + ABC

(2)Y = CD + ACD (4)Y = BC + B D

(2)Y = B + AD + AC (4)Y = A + B D (6)Y = CD + B D + AC

数字电路 习题答案 (第二章)

第二章

2.1 解:

2

数字电路 习题答案 (第二章)

2.10 (1) vi2 = 1.4V (2) vi2 = 0.2V (3) vi2 = 1.4V (4) vi2 = 0.2V (5) vi2 = 1.4V

2.11 各种情况均为 1.4V 2.12 解:

输出为高电平时:Vo = Vcc − (0.2 × 2 − iL )RL = 4.6 + iL RL

114化简下列逻辑函数bdce120将下列函数化为最简与或式wwwplczonecom数字电路习题答案第二章第二章213010截止负值悬空时都行饱和悬空时都行饱和截止为负值200200ililil1010ihccihccih2002ohol系数输出为高电平时扇出系数输出为低电平时扇出所以n2025为输入端的个数分母中的系数输出为高电平时扇出系数输出为低电平时扇出2imaxohol所以n5wwwplczonecom数字电路习题答案第二章26解

数字电路第五版(康华光)课后答案

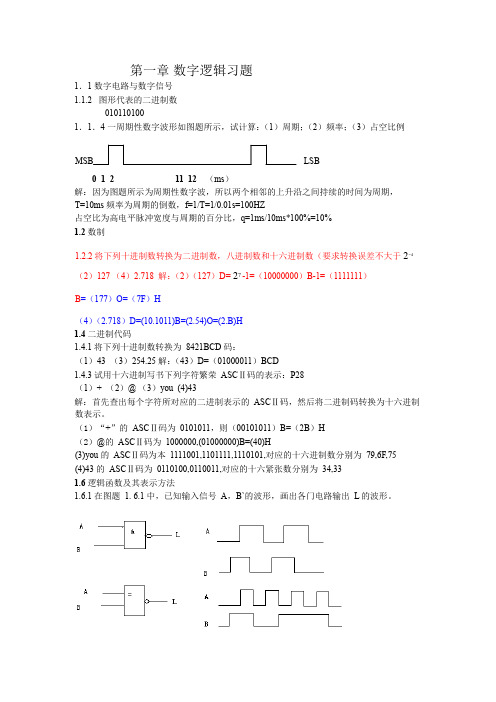

第一章数字逻辑习题1.1 数字电路与数字信号1.1.2 图形代表的二进制数0101101001.1.4 一周期性数字波形如图题所示,试计算:(1)周期;(2)频率;(3)占空比例MSB LSB0 1 2 11 12 (ms)解:因为图题所示为周期性数字波,所以两个相邻的上升沿之间持续的时间为周期,T=10ms 频率为周期的倒数,f=1/T=1/0.01s=100HZ占空比为高电平脉冲宽度与周期的百分比,q=1ms/10ms*100%=10%1.2 数制1.2.2 将下列十进制数转换为二进制数,八进制数和十六进制数(要求转换误差不大于2−4(2)127 (4)2.718解:(2)(127)D= 27 -1=(10000000)B-1=(1111111)B=(177)O=(7F)H(4)(2.718)D=(10.1011)B=(2.54)O=(2.B)H1.4 二进制代码1.4.1 将下列十进制数转换为8421BCD 码:(1)43 (3)254.25 解:(43)D=(01000011)BCD1.4.3 试用十六进制写书下列字符繁荣ASCⅡ码的表示:P28(1)+ (2)@ (3)you (4)43解:首先查出每个字符所对应的二进制表示的ASCⅡ码,然后将二进制码转换为十六进制数表示。

(1)“+”的ASCⅡ码为0101011,则(00101011)B=(2B)H(2)@的ASCⅡ码为1000000,(01000000)B=(40)H(3)you 的ASCⅡ码为本1111001,1101111,1110101,对应的十六进制数分别为79,6F,75(4)43 的ASCⅡ码为0110100,0110011,对应的十六紧张数分别为34,331.6 逻辑函数及其表示方法1.6.1 在图题1. 6.1 中,已知输入信号A,B`的波形,画出各门电路输出L 的波形。

解: (a)为与非, (b)为同或非,即异或第二章逻辑代数习题解答2.1.1 用真值表证明下列恒等式(3)A⊕ =B AB AB+ (A⊕B)=AB+AB解:真值表如下由最右边2栏可知,A⊕B与AB+AB的真值表完全相同。

数电第五版(阎石)第三章课后习题及答案

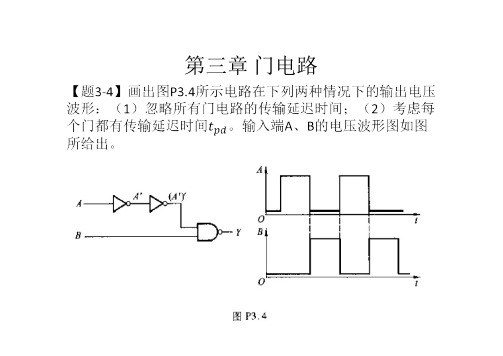

第三章门电路解:两种情况下的电压波形图如图A3.4所示。

【题3.7】试分析图3.7中各电路图的逻辑功能,写出输出的逻辑函数式。

(a )图P3.7(a )电路可划分为四个反相器电路和一个三输入端的与非门电路,如图所示。

从输入到输出逐级写出输出的逻辑函数式,'111'1'1'1)(,,,C B A D C C B B A A ''''111')(C B A C B A C B A D Y(b )图P3.7(b )电路可划分为五个反相器电路和一个或非门电路,如图所示。

从输入到输出逐级写出输出的逻辑函数式:'111''''()()YA B C A B C ABC(c )图P3.7(c )电路可划分为三个与非门电路、两个反相器电路和一个或非门电路,如图所示。

从输入到输出逐级写出输出的逻辑函数式:''')(,)(,)'(,)(G INHH EF G CD F AB E '''''()()'()'()()Y I H AB CD INH AB CD INH(d)图P3.7(d)电路可划分为两个反相器电路和两个传输门电路,如图所示。

从输入到输出逐级写出输出的逻辑函数式:'YBAAB'【题3.8】试画出图3-8(a)(b)两个电路的输出电压波形,输入电压波形如图(c)所示。

输出电压波形如右图所示:【题3.9】 在图3-21所示电路中,G 1和G 2是两个OD 输出结构的与非门74HC03,74HC03输出端MOS 管截止电流为 导通时允许的最大负载电流为这时对应的输出电压V OL (max )=0.33V 。

负载门G 3-G 5是3输入端或非门74HC27,每个输入端的高电平输入电流最大值为 ,低电平输入电流最大值为 ,试求在 、、、、并且满足 ,的情况下, 的取值的允许范围。

数字集成电路习题(第三章)

0. Explain qualitatively

4

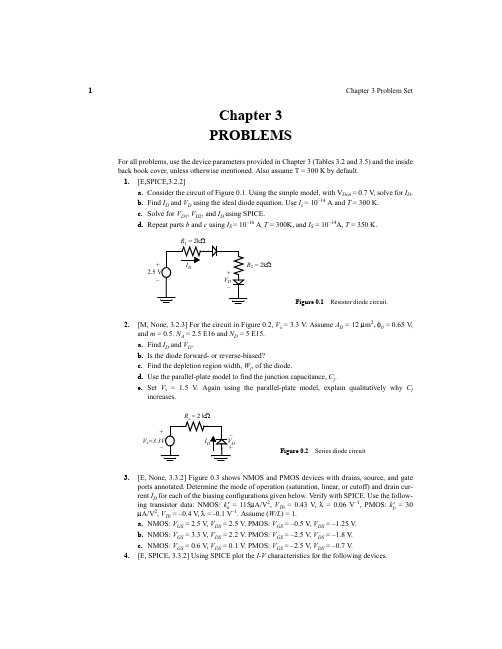

Chapter 3 Problem Set a. Write down the equations (and only those) which are needed to determine the voltage at node X. Do NOT plug in any values yet. Neglect short channel effects and assume that λp = 0. b. Draw the (approximative) load lines for both MOS transistor and resistor. Mark some of the significant points. c. Determine the required width of the transistor (for L = 0.25µm) such that X equals 1.5 V. d. We have, so far, assumed that M1 is a long-channel device. Redraw the load lines assuming that M1 is velocity-saturated. Will the voltage at X rise or fall?

Table 0.2 Measurements taken from the MOS device, at different terminal voltages.

Measurement number 1 2 3 4 5 6 7 8.

VGS (V) -2.5 1 -0.7 -2.0 -2.5 -2.5 -2.5

R1 = 2kΩ + 2.5 V – ID R2 = 2kΩ

数字电子技术基础(第四版)课后习题答案_第三章

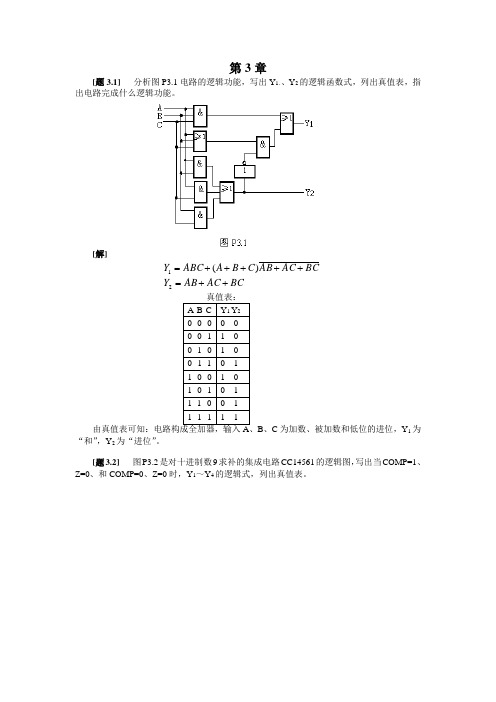

第3章[题3.1] 分析图P3.1电路的逻辑功能,写出Y 1、、Y 2的逻辑函数式,列出真值表,指出电路完成什么逻辑功能。

[解]BCAC AB Y BCAC AB C B A ABC Y ++=+++++=21)(B 、C 为加数、被加数和低位的进位,Y 1为“和”,Y 2为“进位”。

[题3.2] 图P3.2是对十进制数9求补的集成电路CC14561的逻辑图,写出当COMP=1、Z=0、和COMP=0、Z=0时,Y 1~Y 4的逻辑式,列出真值表。

[解](1)COMP=1、Z=0时,TG 1、TG 3、TG 5导通,TG 2、TG 4、TG 6关断。

3232211 , ,A A Y A Y A Y ⊕===, 4324A A A Y ++=(2)COMP=0、Z=0时,Y 1=A 1, Y 2=A 2, Y 3=A 3, Y 4=A 4。

COMP =0、Z=0的真值表从略。

[题3.3] 用与非门设计四变量的多数表决电路。

当输入变量A 、B 、C 、D 有3个或3个以上为1时输出为1,输入为其他状态时输出为0。

[解] 题3.3的真值表如表A3.3所示,逻辑图如图A3.3所示。

ABCD D ABC D C AB CD B A BCD A Y ++++= BCD ACD ABC ABC +++=B C D A C D A B D A B C ⋅⋅⋅=[题3.4] 有一水箱由大、小两台泵M L 和M S 供水,如图P3.4所示。

水箱中设置了3个水位检测元件A 、B 、C 。

水面低于检测元件时,检测元件给出高电平;水面高于检测元件时,检测元件给出低电平。

现要求当水位超过C 点时水泵停止工作;水位低于C 点而高于B 点时M S 单独工作;水位低于B 点而高于A 点时M L 单独工作;水位低于A 点时M L 和M S 同时工作。

试用门电路设计一个控制两台水泵的逻辑电路,要求电路尽量简单。

[解] 题3.4的真值表如表A3.4所示。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

= B ABC A ABC C ABC

= B ABC + A ABC + C ABC

= ABC ( A + B + C )

= ( A + B + C )( A + B + C )

= A BC + AB C + ABC + A B C + A BC + AB C

(2)真值表

A

B

3 组合逻辑电路习题解答

8

图 P3.11

解:由图(a)写出逻辑函数并化简,得

L = Y 0 Y 2 Y 5 Y 7 = Y0 + Y2 + Y5 + Y7

= A B C + A B C + A BC + ABC = AC + AC

[P3.12]电路如图 P3.12 所示,图中①~⑤均为 2 线—4 线译码器。 (1)欲分别使译码器①~④处于工作状态,对应的 C、D 应输入何种状态(填表 P3.12-1);

解:Y = ABC + ABC + ABC = AB + AC

Y = AB + AC = AB ⋅ AC

PDF 文件使用 "pdfFactory Pro" 试用版本创建

3 组合逻辑电路习题解答

4

A

&

B

&

C

&

Y

[P3.4]试分析如图 P3.4 所示逻辑电路的功能,写出逻辑表达式和真值表。

输出信号为比较结果:Y(A>B) 、Y(A=B)和 Y(A<B),则 Y(A>B)的逻辑表达式为 AB 。

[T3.9]下列电路中,不属于组合逻辑电路的是

。

(A)译码器 (B)全加器 (C)寄存器 (D)编码器

[T3.10]译码器 74LS138 的使能端 E1 E2 E3 取值为

时,处于允许状态。

(A)011

(B)100

(C)101

(D)010

[T3.11]在二进制译码器中,若输入有 4 位代码,则输出有

个信号。

(A)2

(B)4

(C)8

(D)16

[T3.12]组合逻辑电路中的险象是由于

引起的。

(A)电路未达到最简

(B)电路有多个输出

(C)电路中的时延

(D)逻辑门类型不同

[T3.13]用取样法消除两级与非门电路中可能出现的冒险,以下说法哪一种是正确并

图 P3.1

解: CO=AB+BC+AC S = ABC +(A + B + C)CO = ABC +(A + B + C)AB + BC + AC

真值表 A B C S CO 0 0 000 0 0 110 0 1 010 0 1 101 1 0 010 1 0 101 1 1 001 1 1 111

解: E = A B CD + ABCD + ABC D + ABC D = AC + C D

[P3.8]由 4 选 1 数据选择器构成的组合逻辑电路如图 P3.8 所示,请画出在输入信号 作用下,L 的输出波形。

PDF 文件使用 "pdfFactory Pro" 试用版本创建

A

B

C

F

A

B

C

F

0

0

0

0

1

0

0

1

0

0

1

1

1

0

1

0

0

1

0

1

1

1

0

0

0

1

1

0

1

1

1

1

(2) F = ABC + ABC + AB C + ABC = A BC ⋅ ABC ⋅ AB C ⋅ ABC

(3)逻辑图略 [P3.14]已知 X=X2X1X0 代表 3 位二进制数。设计一个组合电路,当 X≥3 时输出 Y

Y0 Y1 Y2 Y3

⑤

A1 A0

S

AB

CD

图 P3.12

解:

处于工作状 态的译码器

① ② ③ ④

C、D 应输入的状态

C

D

0

0

0

1

1

0

1

1

A

B

Y10

Y11

Y12

Y13

0

0

0

1

1

1

0

1

1

0

1

1

1

0

1

1

0

1

1

1

1

1

1

0

逻辑功能:由 74LS139 构成的 4 线—16 线译码器

[P3.13]试用与非门设计一组合逻辑电路,其输入为 3 位二进制数,当输入中有奇数 个 1 时输出为 1,否则输出为 0。要求列出真值表,写出逻辑函数表达式,画出逻辑图(输 入变量允许有反变量)。 解:(1)真值表

电路功能:一位全加器,S 是相加的和,CO 是进位 [P3.2]已知逻辑电路如图 P3.2 所示,试分析其逻辑功能。

PDF 文件使用 "pdfFactory Pro" 试用版本创建

3 组合逻辑电路习题解答

3

图 P3.2

解:(1)逻辑表达式

P1 = ABC

P2 = BP1 = B ABC P3 = AP1 = AABC P4 = CP1 = C ABC

F

=

1

0

0 ≤ E < 8 或 12 ≤ E < 15 其它

E3 E2 E1 E0 F E3 E2 E1 E0 F 000011 0 000 000111 0 010 001011 0 100 001111 0 110 010011 1 001 010111 1 011

PDF 文件使用 "pdfFactory Pro" 试用版本创建

(2)试分析当译码器①工作时,请对应 A、B 的状态写出 Y10 ~ Y13 的状态(填表 P3.12-2); (3)说明图 P3.12 的逻辑功能。

表 P3.12-1

表 P3.12-2

处于工作状 态的译码器

① ② ③ ④

C、D 应输入的状态

C

D

A

B

Y10

Y11

Y12

Y13

0

0

0

1

1

0

1

1

PDF 文件使用 "pdfFactory Pro" 试用版本创建

Y

0

0

0

0

1

0

0

1

0

0

1

0

1

0

1

1

0

1

0

0

1

1

0

1

0

1

1

1

1

1

1

1

(2)求最简与-或式

(3)电路图

F = X 2+ X 1 X 0 = X 2 X 1 X 0

X2

F

X1 X0

[P3.15]4 位二进制数 E 为 E3E2E1E0,E≥0,没有符号位。请设计一个组合逻辑电 路实现

的判别。 解:(1)真值表:

Y10 Y11 Y12 Y13

Y0 Y1 Y2 Y3 ①

A1 A0

S

3 组合逻辑电路习题解答

Y20 Y21 Y22 Y23

Y0 Y1 Y2 Y3 ②

A1 A0

S

Y30 Y31 Y32 Y33

Y0 Y1 Y2 Y3 ③

A1 A0

S

9

Y40 Y41 Y42 Y43

Y0 Y1 Y2 Y3 ④

A1 A0

S

3 组合逻辑电路习题解答

11

(2)表达式

011011 1 101 0 1 1 1 11 1 1 1 0

F E1E0 00 01 11 10

E3E2 00 1 1 1 1 01 1 1 1 1 11 1 1 0 1 10 0 0 0 0

图 P3.1

解; Z =(NMQ + N MQ)P +(N MQ + NMQ)P = NMQP + N MQP + N MQP + NMQP = NQP + N QP [P3.11]写出图 P3.11 所示电路的逻辑函数,并化简为最简与-或表达式。

PDF 文件使用 "pdfFactory Pro" 试用版本创建

3 组合逻辑电路习题解答

1

自我检测题

[T3.1]组合逻辑电路任何时刻的输出信号,与该时刻的输入信号 有关 ,与电路以 前的输入信号 无关 。

[T3.2]在组合逻辑电路中,当输入信号改变状态时,输出端可能出现虚假过渡干扰 脉冲的现象称为 竞争冒险 。

[T3.3]8 线—3 线优先编码器 74LS148 的优先编码顺序是 I7 、 I6 、 I5 、…、 I0 ,输 出 Y2 Y1 Y0 。输入输出均为低电平有效。当输入 I7 I6 I5 … I0 为 11010101 时,输出 Y2 Y1 Y0 为 010 。

3 组合逻辑电路习题解答

6

EN

C

图 P3.8

解:4 选 1 数据选择器的逻辑表达式为:

Y = A1 A0 D0 + A1 A0 D1 + A1 A0 D2 + A1 A0 D3

将 A1=A,A0=B,D0=1,D1=C, D2 = C ,D3=C 代入得

Y = A B + ABC + AB C + ABC = A B C + A BC + ABC + AB C + ABC