cadence原理图输入工具composer使用

Composer 编程软件使用步骤

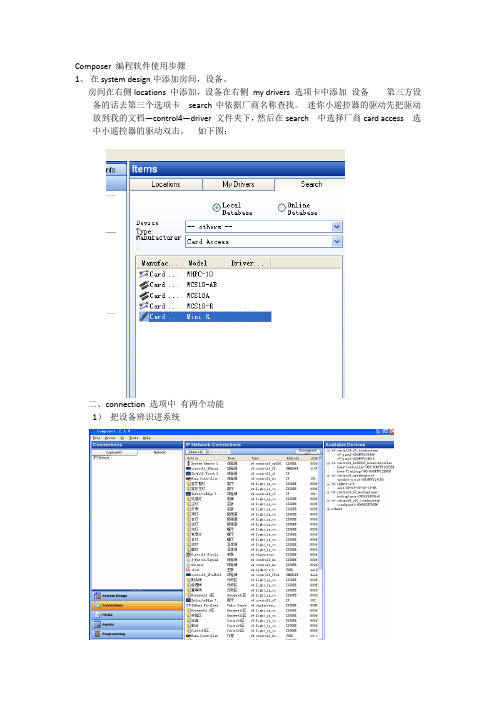

Composer 编程软件使用步骤1、在system design中添加房间,设备。

房间在右侧locations 中添加,设备在右侧my drivers 选项卡中添加设备第三方设备的话去第三个选项卡search中依据厂商名称查找。

迷你小遥控器的驱动先把驱动放到我的文档—control4—driver 文件夹下,然后在search 中选择厂商card access 选中小遥控器的驱动双击。

如下图:二、connection 选项中有两个功能1)把设备辨识进系统注意:辨识完主机要返回system design中创建zigbee网络,否则其他的zigbee设备无法辨识然后返回connection选项卡中继续辨识其他设备。

2) 将音视频设备以及红外或232等的控制在软件里做相应连接,模拟重现物理上的实际连接。

注意:此部分一定要做,而且具体细节很多,要注意。

三、media选项卡用于编辑音乐界面及将U盘歌曲扫描进主机。

左边栏中选中U盘,点击右侧的scan 等待一段时间,如果歌曲比较多可能扫描会比较慢,等待时间5-20分钟。

出文件以后双击歌曲,在弹出的对话框中可编辑图片,专辑以及歌曲的名称。

注意:1)音乐格式最好是MP3格式的。

点scan弹出的对话框选择MP3格式,点击确定。

2)U盘里歌曲命名如果是中文的会出现乱码,所以在优盘里放歌可用拼音代替。

具体自己试试看。

四、agents选项卡,用于定义编程需要的变量,计时器,场景模式,日程安排等,类似于C++语言中的定义变量和类。

具体自己可以进一步尝试。

五、programming编程左边栏为要对其进行编程的对象,右侧为可以要控制的对象。

中间为程序编译栏。

cadence实验报告三实验报告

实验报告三:Cadence实验报告

1. 实验目的

本实验旨在熟悉Cadence软件的使用,并通过设计和仿真一个简单的2输入AND门,学习使用更多的Cadence工具。

2. 实验步骤及结果

2.1 绘制原理图

首先使用Cadence软件新建一个库文件,命名为“And2_lib”,并打开Library Manager工具,如下图所示:

Library Manager

Library Manager

在Library Manager工具中,我们可以进行各种管理操作,包括新建、删除、重命名库文件等操作,还可以查看库文件中的各种信息。

接下来,我们使用Schematic Composer工具绘制2输入AND门的原理图,如下图所示:2-input AND Gate Schematic

2-input AND Gate Schematic

其中,我们使用了以下基本元件:

•Pmosa:NMOS器件

•Nmosa:PMOS器件

•Resistor:电阻器件

•Vdc:直流电源

•Vground:地电源

绘制完成后,使用“Save As”命令将原理图保存为“And2”即可。

2.2 设计Layout布局

在完成原理图设计后,接下来需要对其进行布局设计。

我们首先在Design Manager工具中打开“And2”原理图文件,并使用Create Cell View工具为该原理图新建一个Layout布局,如下图所示:

Create Cell View

Create Cell View

然后,我们进入Virtuoso Layout Editor工具,选中。

cadence简介和使用基础

CMOS电路原理图设计

或者CIW窗口→File→Open(打开已有的 Cellview)。

CMOS电路原理图设计

也可以在Library Manager中直接打开。

Cadence的使用基础

双击Schematics,出现原理图编辑器

Cadence的使用基础

之后出现Symbol Generation Options窗口。

Cadence的使用基础

出现界面:

Cadence的使用基础

可将上图修改为惯用图形,以CMOS反相器为例。

CMOS电路原理图设计

电路仿真 仿真环境简介

Schematic图形窗口→Tools→Analog Environment。

Cadence的使用基础

Cadence的使用基础

基本工作环境

局域网资源

Cadence的使用基础

用户登陆 微机登陆后,点击桌面X-manager 图标,

Cadence的使用基础

打开X-manager图标后,点击xstart 图标,出现对话 框,进行如下设置:

Cadence的使用基础

登录时出现Linux-CDE (Common Desktop Environment) 界面

一、 cadence简介和使用

集成电路设计软件技术介绍

EDA技术的概念

EDA技术是在电子CAD技术基础上发展起来 的计算机软件系统,是指以计算机为工作平台, 融合了应用电子技术、计算机技术、信息处理 及智能化技术的最新成果,进行电子产品的自 动设计

EDA工具的功能

利用EDA工具,电子设计师可以从概念、算法、 协议等开始设计电子系统,大量工作可以通过 计算机完成,并可以将电子产品从电路设计、

自-Cadence Concept HDL原理图输入

Allegro DesignEntry HDL原理图输入方式孙海峰Design EntryHDL是Cadence公司原有的原理图设计输入系统,提供了一个全面、高效、灵活的原理图设计环境,具有强大的操作编辑功能。

设计者在HDL环境中能够完成整个原理图设计流程,可以进行层次原理图和平面原理图输入、原理图检查、生成料单、生成网表等工作。

HDL还能与Allegro工具很好的集成在一个工程中,可很方便的实现原理图到PCB的导入,以及PCB改动反标到原理图等交互式操作。

接下来,按照原理图设计输入流程,我来详细阐述Design Entry HDL原理图的输入方式。

一、进入Design Entry HDL用户界面进入HDL原理图输入界面的步骤如下。

1、执行“开始/程序/Cadence 16.3/Design Entry HDL”命令,将弹出产品选择对话框2、进入产品界面,弹出Open Project对话框其中Open Recent用以打开最后运行的项目;Open Open anExisting Project用以打开一个已有的项目;CreateaNew Project用以新建一个项目。

3、点击Createa New Project新建项目,则进入新建项目向导,填入新建项目名称和保存位置,如下图。

4、点击下一步,进入ProjectLibraries对话框,在可用元件库中为项目添加元件库5、点击下一步,进入Design Name对话框,Library中选择需要的元件库,Design 中可以填写新建项目名称,也可以选择已有元件,对其进行修改。

6、点击下一步,进入Summary对话框,显示前面步骤所设置的所有内容。

7、点击Finish按钮,在接下来的对话框中均确定就可以完成项目的新建,并出现原理图工作界面。

其中:(1)标题栏——显示文件所在路径和文件名称;(2)菜单栏——项目所有相关操作的集合;包含了文件菜单、编辑菜单、视图菜单、元件菜单、画线菜单、文本菜单、模块菜单、群组菜单、显示菜单、仿真菜单、RF-PCB菜单、工具菜单、窗口菜单和帮助菜单。

cadence仿真工具介绍1

( TB ( TO ( GT ( W1 ( A1 ( W2 ( A2 ( W3 ( A3

"nwell" ) "diff" ) "poly" ) "cut" ) "metal" ) "cut" ) "metal" ) "cut" ) "metal" )

COPYRIGHT FOR ZHOUQN

COPYRIGHT FOR ZHOUQN

原理图编辑窗口结构分类编辑命令菜单常用快捷命令菜单1instance调用库单元cellview浏览器librarycellviewnameoption阵列行数列数旋转x镜像y镜像variable如果有2addpin调用端口pinpinnames总线命名方式总线名放置方式pin的旋转和镜像3addwire连线narroworwide4wirename连线命名连线规则连线粗细连线名称连线名称的相关属性10属性参数修改9undo11chechandsave12save5放大缩小8删除6stretch拉动保持连接7copy从分类菜单中可以看到命令的快捷键和许多其它命令仿真环境设置版图设计基本过程和要求在一定工艺下根据电路的要求依据版图设计规则设计每个器件的图形并完成排版布线形成一套完整的电路光刻掩膜版图形

COPYRIGHT FOR ZHOUQN

版图主要编辑命令 (2)修改类命令 ) Undo, Redo , Move, Copy, 拉动,改变形状, 拉动,改变形状, 删除,查找, 删除,查找, 合并图形, 合并图形, 制作单元, 制作单元, 打散单元, 打散单元, 劈切图形, 劈切图形, 胀缩图形, 胀缩图形, 旋转图形等等。 旋转图形等等。

Cadence使用初步简介

Cadence使用初步简介在早期的ASIC 设计中电路图起着更为重要的作用作为流行的CAD软件Cadence 提供了一个优秀的电路图编辑工具Composer。

Composer不但界面友好操作方便而且功能非常强大电路图设计好后其功能是否正确性能是否优越必须通过电路模拟才能进行验证Cadence 同样提供了一个优秀的电路模拟软件Analog Artist由于Analog Artist 通过Cadence 与Hspice 的接口调用Hspice 对电路进行模拟。

但是我们的虚拟机中并没有安装Hspice软件,所以我们使用Cadence自带的仿真软件进行仿真。

本章将介绍电路图设计工具Composer 和电路模拟软件Analog Artist 的设置启动界面及使用方法简单的示例以及相关的辅助文件以便大家能对这两种工具有一个初步的理解。

一、Cadence平台的启动:①右击桌面,在弹出菜单中单击open Terminal②在弹出的终端中输入icfb&然后按回车启动Cadence③Cadence启动过程④Cadence启动完成后,关闭提示信息二、设计项目的建立①点击Tools—Library Manager…启动设计库管理软件②启动设计库管理软件③点击File—New--Library新建设计库文件④在弹出的菜单项中输入你的设计的库的名称,比如MyDesign,点击OK⑤选择关联的工艺库文件,我们选择关联已有的工艺库文件,点击OK⑥在弹出菜单中的Technology Library下拉菜单中选择我们需要的TSMC35mm 工艺库,然后点击OK。

⑦设计的项目库文件建立完成,然后我们在这个项目库的基础上建立其子项目。

点击选择mydesign,然后点击File-New-Cell View…⑧输入子项目的名称及子项目的类型,多种类型,目前课程设计中用到的主要是电路图编辑和版图编辑。

在设计版图之前我们假定先设计原理图:所以我们选择,然后点击OK。

cadence原理图设计实例教程

仿真波形测量

➢ 执行Plot/Label/Mark命令,显示该波形顶峰标尺坐标

仿真波形测量

➢ 第一位置坐标为顶峰处时间数值 ➢ 第二位置坐标为顶峰处电压数值

仿真波形测量

➢ 执行Trace/Cursor/Trough命令, Plot/Label/Mark命令,测量该波形谷底坐标

仿真波形测量

声音信号触发后灯亮保持时间的测量: 执行Trace/Cursor/Display命令,使测量坐标处于显示状态

仿真波形测量

➢ 点击分析窗口左下角“V(U2:OUTPUT)”, 再点击该波形在声音 触发下,由低电平变成高平处的位置,执行Plot/Label/Mark,读 出该处的时间为795us,同样测量出该信号由高电平变成低电平 处的时间为11.321ms,两者相减约10.526ms。

3、电路原理图编辑

实验仿真

开始绘制电路图 :进入Schematic窗口,则在窗口右边 会出现下图的工具栏:

放置总线引出管脚

放置端口

指示管脚不连接

Place junction

放置阶层

放置阶层引脚

添பைடு நூலகம்文字

Place part

Place Bus

Place GND

绘制无电气性质符号

Place wire

Place power

印制版设计

2、启动OrCAD/ Layout

选择“开始”→“程序”→“OrCAD Release 9.1”→“Layout”

印制版设计

3、 启动File>New命令或按钮 4、 指定所要启用的板框档(*.tpl)或技术档(*.tch),查找范 围Orcad/Layout/Data 如下图,查找DEFAULT文件,打开

schematic composer关于cadence原理图

电路图编辑工具 Composer

Schematic Composer

编辑Schematic Composer的一般流程 图

Schematic composer

输入指令icfb启动工具

Schematic composer

建新一个library : select File-New-library

AnalogLib AnalogLib AnalogLib

nmos4(2个)

res cap vdd,vss

mos管的主要参数

multiplier 表示几个管子并联数 Length 表示沟道长度,设计时我们按照长沟道设计L取值>=1um Total Width 表示总的沟道宽度 Finger Width 表示一个finger的宽度

Schematic composer

•

添加器件(view一般选择symbol)

所用器件清单

Library

AnalogLib AnalogLib AnalogLib

Cell

pnp(3个) npn(2个) pmos4

Properties/Comments

Model Name=trpnp Model Name=trpnp Model Name=trpnp, Length=8u,Width=iPar( “1”)*16

全加器(verilog)

再新建一个cellview,Tool选择Composer-Symbol,点ok进入。 在 amplifier schematic 窗口中,依次选择:design→create cellview→From cellview, 打开Cellview From Cellview 窗口,From view name 为adder1(这就是之前的verilog 代码),To View Name 为symbol,点ok。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

建立新单元

视图(view) 同一个单元会有不同的视图; 对于不同视图是不同的文件,但代表同一个电路; 建立新单元:

建立原理图视图 建立符号图

<13页> 2011/9/15 16:01

建立新单元

建立原理图视图步骤:

(1)在库管理中选择工作库;

<14页> 2011/9/15 16:01

建立新单元

(4) 原理图编辑 示例:标准单元库中的一个门或用户曾设计好的单元; 添加示例: Add→Instance或快捷键 i 或F3

<19页> 2011/9/15 16:01

建立新单元

弹出对话框

Component Browser对话

框 AddInstance

对话框

库 单元 视图 示例名

<20页> 2011/9/15 16:01

晶体管级原理图

晶体管可以用来设计基本“门”单元; 用在verilog中内建的晶体管开关模型来仿真,也可用

Spectre或Spice模拟仿真器仿真。 通用晶体管部件库NCSU_Analog_Parts

<54页> 2011/9/15 16:01

晶体管级原理图

<55页> 2011/9/15 16:01

<35页> 2011/9/15 16:01

建立新单元

(9)关闭窗口 Windows→Close 或 ctrl+w

<36页> 2011/9/15 16:01

建立新单元

问题:下图全加器与书中全加器比较,两者区别, 书中所画全加器优点?

<37页> 2011/9/15 16:01

建立新单元

与非门

<38页> 2011/9/15 16:01

晶体管级原理图

<60页> 2011/9/15 16:01

晶体管级原理图

(5)建立与非门符号 Design →Create Cellview →From Cellview

<61页> 2011/9/15 16:01

晶体管级原理图

打印原理图 Design→Plot →Submit

PlotOptions选项 Top section Middle section Bottom section

Composer工具可以完成

设计小单元的晶体管级原理图 大电路的门级原理图 同时含逻辑门和Verilog代码的复杂电路原理图

<3页> 2011/9/15 16:01

概述

Composer工具与Verilog仿真器集成在一起,用户可以 自动将一幅原理图输出到仿真器中。

原理图

Composer/Verilog

<5页> 2011/9/15 16:01

主要内容

概述 启动cadence建立一个新的工作库 建立新的单元 晶体管级原理图 命名规则

<6页> 2011/9/15 16:01

建立新的工作库

工作库(Library) 是按某种原因将许多单元组合在一起建立的集合。

在库管理(Library Manager)中建立工作库步骤:

晶体管级原理图

<58页> 2011/9/15 16:01

晶体管级原理图

(3)添加电源连线,vdd和gnd (4)晶体管长度和宽度参数定义

• 添加示例时修改 • 改变晶体管属性 修改晶体管属性步骤:

选择要修改的晶体管 Edit→Properties →Objects 或快捷键q

<59页> 2011/9/15 16:01

Add→wire(wide)或快捷键 W

<48页> 2011/9/15 16:01

建立新单元

两位加法器

<49页> 2011/9/15 16:01

建立新单元

总线的标注方法 命名方式A<1:0>,B<1:0>

总线中的每条导线必须按照这条总线标注符的展开 来命名

Cadence中总线沿用端口的名字,而从总线抽出 的分支线沿用总线的名字

快捷功能按钮工具 • 检查和保存(check and save) • 保存(save) • 放大(zoom in by 2) • 缩小(zoom out by 2) • 拉伸(Stretch) • 复制(Copy) • 删除(Delete) • 撤销(undo)

<18页> 2011/9/15 16:01

<46页> 2011/9/15 16:01

建立新单元

对话框 库名 单元名 视图名 工具 库路径文件

<47页> 2011/9/15 16:01

建立新单元

(3)在原理图编辑窗口,以下操作: Add→Instance 或 快捷键 i

(4)在原理图编辑窗口放入俩个全加器示例 (5)按连接关系添加俩个全加器之间的连接总线,构 成两位加法器。

建立新单元

在Component Browser对话框中选择要添加的逻辑门

<21页> 2011/9/15 16:01

建立新单元

在原理图编辑窗口中加入要添加的逻辑门

Esc键退出上一命令模式

<22页> 2011/9/15 16:01

建立新单元

(5)添加逻辑门之间的连接导线 添加导线: Add→wire(narrow)或快捷键 w

Verilog网表 测试程序包

网表(netlist) 列网表(netlisting) 测试程序包(testbench wrapper)

<4页> 2011/9/15 16:01

概述

Composer可以与Virtuoso-XL版图工具链接 Composer可以与affirma模拟信号环境链接 原理图生成方式 手工完成原理图 从verilog的结构网表自动生成原理图

建立新单元

(8)检查并保存设计 Design→check and Save 或 F8

<34页> 2011/9/15 16:01

建立新单元

Check and Save命令与Save命令区别

Save命令不对原理图做任何检查,在原理图编辑过中 使用; Check and Save命令是在完成原理图最终操 作后,需要对原理图进行检查,确认是否有错误。 错误信息显示在CIW窗口中

<23页> 2011/9/15 16:01

建立新单元

<24页> 2011/9/15 16:01

建立新单元

导线

Narrow Wide Name Esc键退出连线命令模式

<25页> 2011/9/15 16:01

建立新单元

(6)添加端口 端口(pin):是进入或离开原理图的连接点,对应于原 理图符号视图上的端口。 Add→pin 或 快捷键 p 或编辑窗口左侧的工具图标

<42页> 2011/9/15 16:01

建立新单元

[@partName] [@instanceName]

<43页> 2011/9/15 16:01

建立新单元

修改符号图名[@partName] Add→Note →Note Text

修改符号形状 Add→Shape

<44页> 2011/9/15 16:01

<50页> 2011/9/15 16:01

建立新单元

总线命名

<51页> 2011/9/15 16:01

建立新单元

为原理图加边框

<52页> 2011/9/15 16:01

主要内容

概述 启动cadence建立一个新的工作库 建立新的单元 晶体管级原理图 命名规则

<53页> 2011/9/15 16:01

<29页> 2011/9/15 16:01

建立新单元

(7)为原理图画出边框

<30页> 2011/9/15 16:01

建立新单元

<31页> 2011/9/15 16:01

建立新单元

<32页> 2011/9/15 16:01

建立新单元

Sheet edit title

<33页> 2011/9/15 16:01

建立新单元---建立符号视图

建立新单元:

建立原理图视图 建立符号图

建立符号图的作用 可方便电路用在其他原理图中,提高设计效率

符号图与原理图是同一个单元的不同视图

注意:符号端口必须与原理图内部的端口一一匹配,名 字也必须相同。

<39页> 2011/9/15 16:01

建立新单元

集成电路CAD设计 ------Composer原理图输入工具

主要内容

概述 启动cadence建立一个新的工作库 建立新的单元 晶体管级原理图 命名规则

<2页> 2011/9/15 16:01

概述

Composer工具

DFII设计工具中的原理图输入工具

原理图(schematic) 把一个单元表示为基本部件的互连或层次化定义的 部件结构

建立新单元

(2)在库管理菜单中File→New →Cellview

<15页> 2011/9/15 16:01

建立新单元

弹出的对话框 库名 单名名 视图名 工具 库的路径文件

<16页> 2011/9/15 16:01

建立新单元

<17页> 2011/9/15 16:01