基于Xilinx-ISE-12.4的FPGA使用例子

ISE开发环境使用指南[FPGA开发教程

ISE开发环境使用指南简介ISE(Integrated Software Environment)是Xilinx公司开发的一套FPGA设计软件工具。

本文档将为您介绍如何使用ISE开发环境进行FPGA开发,包括环境的安装、基本操作和常见问题解决方法。

环境安装1.在Xilinx官网上下载最新版本的ISE软件。

2.双击安装文件,按照向导指示完成安装过程。

3.完成安装后,打开ISE软件,进行必要的设置和配置。

基本操作创建工程1.打开ISE软件,选择“File” -> “New Project”。

2.在弹出的对话框中输入工程名称和路径,选择FPGA型号等相关参数,点击“Next”。

3.添加源文件和约束文件,点击“Next”。

4.点击“Finish”完成工程创建。

编译工程1.在ISE软件中选择“Project” -> “Run Implementation”进行工程编译。

2.检查编译过程中是否有错误,根据提示进行修正。

下载到FPGA1.将FPGA与电脑连接,选择“Tools” -> “iMPACT”打开下载工具。

2.配置下载参数,选择对应的FPGA型号和文件路径。

3.点击“Program”开始下载程序到FPGA。

常见问题解决方法编译错误•检查代码中是否有语法错误或逻辑问题。

•检查约束文件是否设置正确。

下载失败•检查FPGA与电脑的连接是否正常。

•检查下载工具配置是否正确。

总结通过本文档的介绍,您应该对如何使用ISE开发环境进行FPGA开发有了一定了解。

希望您在实际操作中能够顺利完成项目的开发和调试。

如果遇到任何问题,可以参考本文档中提供的常见问题解决方法或参考Xilinx官方文档进行进一步学习和搜索。

Xilinx-FPGA配置的一些细节

Xilinx-FPGA配置的一些细节Xilinx FPGA配置的一些细节2010年07月03日星期六 14:260 参考资料(1) Xilinx: Development System Reference Guide. dev.pdf, v10.1在Xilinx的doc目录下有。

(2) Xilinx: Virtex FPGA Series Configuration and Readback. XAPP138 (v2.8) March 11, 2005在Xilinx网站上有,链接/bvdocs/appnotes/xap p138.pdf(3)Xilinx: Using a Microprocessor to Configure Xilinx FPGAs via Slave Serial or SelectMAP Mode.XAPP502 (v1.5) December 3, 2007在Xilinx网站上有,链接/bvdocs/appnotes/xap p502.pdf注:此外xapp139和xapp151也是和配置相关的。

(4)Xilinx: Virtex-4 Configuration Guide. UG071 (v1.5) January 12, 2007(5) Tell me about the .BIT file format.链接:/FAQ_Pages/0026_Tell_me_about_bit_files.htm1 Xilinx配置过程主要讲一下Startup Sequence。

Startup Sequence由8个状态组成.除了7是固定的之外,其它几个的顺序是用户可设置的,而且Wait for DCM和DCI是可选的。

其中默认顺序如下:这些在ISE生成bit文件时通过属性页设定。

这几个状态的具体含义如下:Release_DONE : DONE信号变高GWE : 使能CLB和IOB,FPGA的RAMs和FFs可以改变状态GTS : 激活用户IO,之前都是高阻。

fpGa_CPLD设计工具xilinxISE使用详解

1.第一章:FPGA/CPLD简介●FPGA一般是基于SRAM工艺的,其基于可编程逻辑单元通常是由查找表(LUT,look up table)和寄存器(register)组成。

其中内部的查找表通常是4输入的,查找表一般完成纯组合逻辑功能;●Xilinx可编程逻辑单元叫做slice,它由上下两部分组成,每部分都由一个register加上一个LUT组成,被称为LC(logic cell,逻辑单元),两个LC之间有一些共用逻辑,可以完成LC之间的配合工作与级连;●Altera可编程逻辑单元叫做LE(Logic Element,逻辑单元),由一个register加上一个LUT构成;Lattice的底层逻辑单元叫做PFU(programmable Function unit,可编程功能单元),它由8个LUT和9个register组成。

●Ram和dpram/spram/伪双口RAM,CAM(content addressable memory)。

Fpga中其实没有专业的rom硬件资源,实现ROM是对RAM赋初置,并且保存此初值●CAM,即内容地址储存器,在其每个存储单元都包含了一个内嵌的比较逻辑,写入cam的数据会和其内部存储的每一个数据进行比较,并返回与端口数据相同的所以内部数据的地址。

总结:RAM是一种根据地址读/写数据的存储单元;而CAM 和RAM恰恰相反,它返回的是与端口数据相匹配的内部地址。

使用很广,比如路由器中的地址交换表等等●Xilinx块ram大小是4kbit和18kbit两种结构。

Lattice块ram是9kbit●分布式ram适合用于多块小容量的ram的设计;●Dll(delay-locked loop)延迟锁定回环或者pll(phase locked loop)锁相环,可以用以完成时钟的高精度,地抖动的倍频/分频/占空比调整/移相等功能。

Xilinx主要集成的是DLL,叫做CLKDLL,在高端的FPGA中,CLKDLL的增强型模块为DCM (digital clock manager,数字时钟管理模块)。

关于基于Xilinx FPGA 的高速Viterbi回溯译码器的性能分析和应用介绍

关于基于Xi1inXFPGA的高速Viterbi回溯译码器的性能分析和应用介绍新一代移动通信系统目前主要采用多载波传输技术,基带传输速率较3G有很大提高,一般要求业务速率能达到30Mb/s以上。

约束长度卷积码以及Viterbi 译码器由于其性能和实现的优点,在新一代通信系统中仍然占有一席之地。

这就要求进一步提高Viterbi译码器的译码速率,同时优化Viterbi设计以减少由速率提高和约束长度的增加带来的硬件实现复杂度。

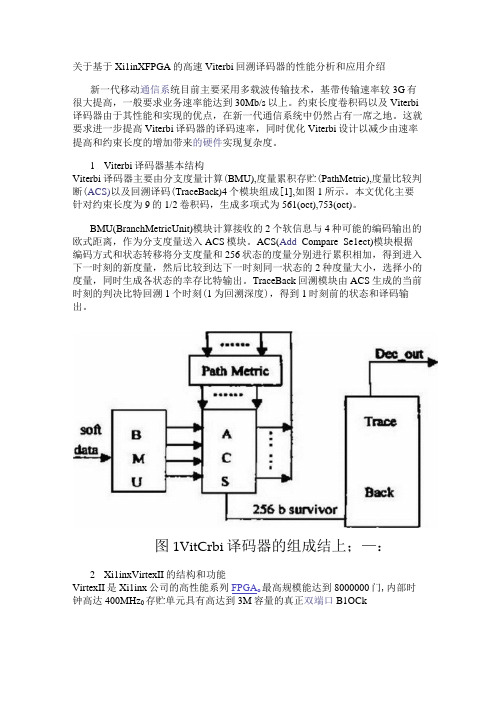

1Viterbi译码器基本结构Viterbi译码器主要由分支度量计算(BMU),度量累积存贮(PathMetric),度量比较判断(ACS)以及回溯译码(TraceBack)4个模块组成[1],如图1所示。

本文优化主要针对约束长度为9的1/2卷积码,生成多项式为561(oct),753(oct)。

BMU(BranchMetricUnit)模块计算接收的2个软信息与4种可能的编码输出的欧式距离,作为分支度量送入ACS模块。

ACS(Add_Compare_Se1ect)模块根据编码方式和状态转移将分支度量和256状态的度量分别进行累积相加,得到进入下一时刻的新度量,然后比较到达下一时刻同一状态的2种度量大小,选择小的度量,同时生成各状态的幸存比特输出。

TraceBack回溯模块由ACS生成的当前时刻的判决比特回溯1个时刻(1为回溯深度),得到1时刻前的状态和译码输出。

图1VitCrbi译码器的组成结上;—:2Xi1inxVirtexII的结构和功能VirtexII是Xi1inx公司的高性能系列FPGA o最高规模能达到8000000门,内部时钟高达400MHz0存贮单元具有高达到3M容量的真正双端口B1OCkRamo 运算单元中包括最多168b 的专用乘法器。

VirtexII 中的可配置单元为C1B(Configurab1e1og ic B1occks)。

C1B 中的资源可以灵活配置成多种结构。

用ISE与Modelsim进行FPGA后仿真(时序仿真)的两种方法

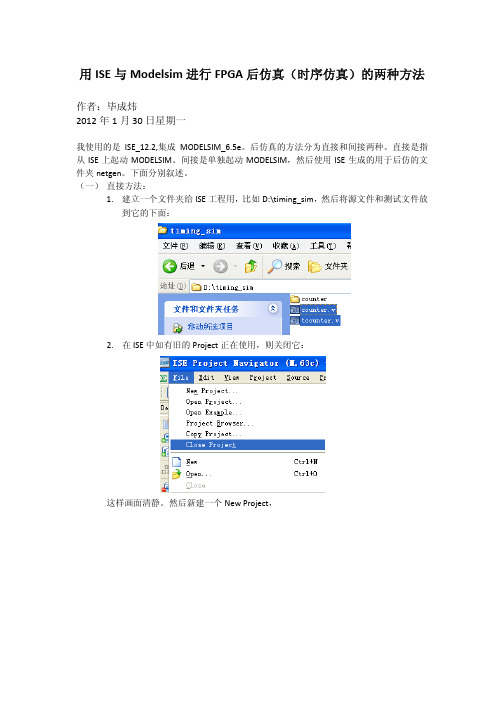

用ISE与Modelsim进行FPGA后仿真(时序仿真)的两种方法作者:毕成炜2012年1月30日星期一我使用的是ISE_12.2,集成MODELSIM_6.5e。

后仿真的方法分为直接和间接两种。

直接是指从ISE上起动MODELSIM。

间接是单独起动MODELSIM,然后使用ISE生成的用于后仿的文件夹netgen。

下面分别叙述。

(一) 直接方法:1.建立一个文件夹给ISE工程用,比如D:\timing_sim,然后将源文件和测试文件放到它的下面:2.在ISE中如有旧的Project正在使用,则关闭它:这样画面清静。

然后新建一个New Project,点Next,选好器件和仿真器:点Next,点Finish.为了能够在ISE中直接唤起MODELSIM,还需要一些设置,主要是两处:双击器件:保证下图红圈处选中你要的仿真器:点OK后,在主菜单中点:保证在红圈处指定好MODELSIM执行文件所在的位置编译仿真库可以在这里双击Compile HDL Simulation Libraries,也可以在C:\Xilinx\12.2\ISE_DS\ISE\bin\nt下面找到,双击它,注意红圈处所标的是你的ISE版本所支持的MODELSIM版本,不能低于它。

否则仿真过程可能出问题。

点Next,点Next,选定你针对什么器件编译仿真库,点Next,点Next,注意,ISE可能最初不带modelsim.ini,它在此步会自动生成这个文件,并且是可写的,即它的“只读”属性是已经自动去掉的。

生成仿真库的映射关系自动写入了ISE的这个modelsim.ini,位于C:\Xilinx\12.2\ISE_DS\ISE\bin\nt,但是,它并不会自动去更新MODELSIM软件的modelsim.ini,而且MODELSIM使用的是它自己的modelsim.ini,位于C:\modeltech_6.5e。

所以需要把ISE的modelsim.ini中的映射关系再COPY到MODELSIM自己的modelsim.ini中。

FPGA开发全攻略——ISE基本操作

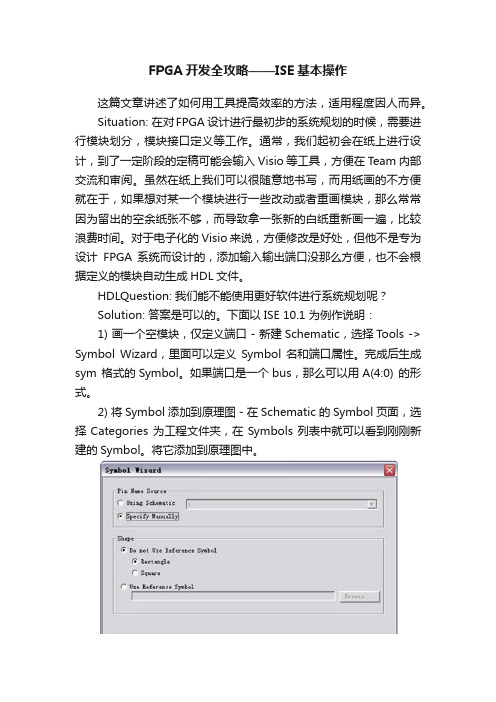

FPGA开发全攻略——ISE基本操作这篇文章讲述了如何用工具提高效率的方法,适用程度因人而异。

Situation: 在对FPGA 设计进行最初步的系统规划的时候,需要进行模块划分,模块接口定义等工作。

通常,我们起初会在纸上进行设计,到了一定阶段的定稿可能会输入Visio 等工具,方便在T eam 内部交流和审阅。

虽然在纸上我们可以很随意地书写,而用纸画的不方便就在于,如果想对某一个模块进行一些改动或者重画模块,那么常常因为留出的空余纸张不够,而导致拿一张新的白纸重新画一遍,比较浪费时间。

对于电子化的Visio 来说,方便修改是好处,但他不是专为设计FPGA 系统而设计的,添加输入输出端口没那么方便,也不会根据定义的模块自动生成HDL文件。

HDLQuestion: 我们能不能使用更好软件进行系统规划呢?Solution: 答案是可以的。

下面以ISE 10.1 为例作说明:1) 画一个空模块,仅定义端口 - 新建Schematic,选择Tools -> Symbol Wizard,里面可以定义Symbol名和端口属性。

完成后生成sym 格式的Symbol。

如果端口是一个bus,那么可以用A(4:0) 的形式。

2) 将Symbol 添加到原理图 - 在Schematic 的Symbol 页面,选择Categories 为工程文件夹,在Symbols列表中就可以看到刚刚新建的Symbol。

将它添加到原理图中。

3) 重复1-2 步骤,建立所有Symbol,并连接端口。

如果需要修改连线的名字或者模块的例化名,可以选择需要修改名字的元件然后按右键--> Object Properties --> 在Name/InstName 窗格中填入需要的名字。

4) 如需修改Symbol,可以直接在sym 文件中修改 - 可以按右键-> Add -> Pin 等等添加,也可以Copy已存在的Pin,然后改变PinName。

ISE软件使用说明

说明这个说明主要介绍了使用开发板可能使用到的3个工具,主要以串口功能的实现作为例子,讲述了ISE, Plantform和EDK的使用方法以及操作的基本流程。

ISE的使用一.启动Xilinx ISE:开始Æ所有程序ÆXilinx ISE 7.1iÆProject Navigator二.新建/打开一个工程:如果已经有了工程,则在FileÆOpen Project弹出的对话框里面选择你的工程。

如果没有合适的工程就需要通过FileÆNew Project来新建一个工程。

具体操作步骤如下:分别在Project Name和Project Location里面填写您想要创建的工程的名称和路径。

在Top-Level Module Type的下拉菜单里面选择您的工程的顶层模块的类型。

本次串口通信的实验的顶层为原理图,所以选择Schematic。

然后点击下一步:在这个对话框的上半部分选择您使用的芯片的族(Spartan3),型号(xc3s400),封装(pq208)和速度(-4)。

下面选择您要使用编译和综合的软件,建议使用ISE自带的软件,一是使用简便,二是Xilinx公司对自己的FPGA了解程度比第三方要高很多,所以使用Xilinx公司自己的软件有的时候会获得意想不到的收获。

具体参数选择如图,然后单击下一步:在这个对话框里面新建工程里面的文件,这步也可以放到后面来实现,这里我们先选择下一步:这一步用来添加已经存在的文件,同样,我们在后面实现这步。

点击下一步:在最后这个对话框里面显示了我们即将建立的工程的详细信息,确认无误以后点击完成,ISE将为您创建一个名字为uart_test的工程:三.为刚创建的工程添加源文件:1.添加已经存在的源文件:选中屏幕右上的xc3s400-4pq208,单击ProjectÆAdd Source,在弹出的对话框里面选择您已经存在的程序文件(.v .vhd)。

xilinxISE使用错误和警告

xilinx ISE使用错误和警告(2012-03-22 15:46:49)转载▼标签:xilinx(1)编dcm时钟控制测试程序时,设置好了ip,例化输出,综合时出现错误ERROR:Xst:2035 - Port <clk> has illegal connections. This port is connected to an input buffer and other components.查到的解决方法是禁掉自动I/O Buffer insertion 功能,具体的做法是右击synthesize,然后properties->Xilinx Specific Options,把add I/O buffer 的勾去掉,综合通过。

但是这样处理了之后在map时又引入了许多的warning,而且还会引发错误。

方法出处一会转帖出来。

(2)dac8812的控制时序测试时,综合没问题,但是map时出现错误Pack:198 - NCD was not produced. All logic was removed from design. 其实这个错误的来源是下面的这几个warning导致MapLib:701 - Signal clk connected to top level port clk has been removed.MapLib:701 - Signal dad connected to top level port dad has been removed.以下省略很多这样的warning,这个问题之前一直没注意,后来才知道问题出在我在问题(1)中的处理,按照同样的流程把add I/O buffer 勾上,综合到route都没什么问题,可见warning也是不能忽略的呀。

(3)刚才不知道怎么了,行为仿真的时候出现下面的errorERROR:HDLParsers:3482 - Could not resolve instantiated unit dacinter in Verilog module work/datest_top in any library意思好像是找不到我top里例化的模块了,重新添加了一下,好用了。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于ISE 12.4的FPGA设计基本流程关键字:FPGA XILINX ISE 12.4ISE设计流程时序仿真信息化调查找茬投稿收藏评论好文推荐打印社区分享ISE是使用XILINX的FPGA的必备的设计工具,它可以完成FPGA开发的全部流程,包括设计输入、仿真、综合、布局布线、生成BIT文件、配置以及在线调试等,功能非常强大。

本文主要通过一个最简单的“点亮LED灯”实例介绍了基于ISE 12.4软件的FPGA设计流程,包括设计输入、仿真、约束、下载等。

0 前言一套完整的FPGA设计流程包括电路设计输入、功能仿真、设计综合、综合后仿真、设计实现、添加约束、布线后仿真和下载、调试等主要步骤。

图1 FPGA设计流程目前赛灵思公司FPGA设计软件的最新版本是ISE 13,由于笔者暂未用到该版本,本文中以ISE 12.4为例。

ISE 9以后的版本的安装文件都是集成到了一个包当中,安装起来很方便。

软件包里面包含四个大的工具,ISE Design Tools、嵌入式设计工具EDK、PlanAhead、Xtreme DSP设计工具System Generator。

ISE设计工具中包含ISE Project Navigator、ChipScope Pro 和以下工具:图2 ISE软件包中部分工具做一般的FPGA逻辑设计时只需要用到ISE设计工具,下面通过一个最简单的“点亮LED 灯”实例,具体讲解ISE设计工具的使用,并介绍基于ISE的FPGA设计基本流程。

1 创建工程(1)在桌面快捷方式或开始→所有程序→Xilinx ISE Design Suite 12.4→ISE Design Tools中打开ISE Project Navigator。

(2)单击File→New Project...出现下图所示对话框。

图3 新建工程对话框在该界面输入工程名、选择工程存放路径、选择顶层模块类型,其中顶层模块类型有硬件描述语言(HDL)、原理图(Schematic)、SynplifyPro默认生成的网表文件(EDIF)、Xilinx IP Core和XST生成的网表文件(NGC/NGO)这四种选项,这里我们使用Verilog模块作为顶层输入,所以选HDL。

(3)单击Next >进入下一步,弹出下图所示对话框。

图4 工程参数设置对话框这里主要设置FPGA器件型号,速度等级,综合工具和仿真工具的选择,其余的一般默认即可。

器件大类(Product Category)中有ALL、民用级General Purpose、工业级Automotive、军用级Military/Hi-Reliability、航空防辐射级Radiation Tolerant五个选项,这里选择默认的ALL。

芯片型号选择笔者最近用到的spartan6 XC6SLX45T,封装FGG484,速度等级-2(数值越大,速度越快)。

综合工具选择ISE自带的XST,仿真工具也选择ISE自带的ISim。

这里综合工具和仿真工具都可以选择第三方的工具,如常用的SynplifyPro和Modelsim。

(4)单击Next >按钮,然后单击Finish完成新工程的创建。

图5 新建工程概要该窗口会显示新建工程的概要,核对无误后点击Finish完成工程创建。

分页2 设计输入(1)在源代码窗口中单击右键,在弹出的菜单中选择New Source。

图6 新建源文件向导在源文件类型中选择Verilog Module,输入文件名,其余使用软件默认即可。

(2)单击Next >按钮,弹出的窗口是模块创建向导界面,这里我们不使用该功能,直接单击单击Next >按钮到下一步,点击Finish完成新源文件的创建。

图7 模块创建向导界面(3)ISE会自动打开源代码编辑界面,在该界面输入源代码,点击保存。

图8 源代码编辑界面在该界面下,我们输入以下源代码。

这段代码的功能就是点亮一个LED灯,让它闪烁起来。

选用板子上外接的一个33.3MHZ 的晶振,对其进行分频后达到人眼能够辨别的跳变速率。

3 功能仿真(1)加入仿真激励源,也就是testbench,这里选择用verilog HDL编写。

在源代码窗口中单击右键,在弹出的菜单中选择New Source,然后选择Verilog Test Fixture。

图9 源代码仿真关联选择界面在该界面选择关联上test1源代码,这样关联之后生成出来的测试文件中会自动加入对源文件的例化代码,然后单击Next >,在弹出的报告界面确认信息无误后点击Finish。

在自动弹出的代码编辑界面输入以下测试激励代码,保存。

(2)行为级仿真。

在主窗口左侧的Design窗口中选择Simulation→下拉栏中选行为级Behavioral→选中仿真激励文件→在Processes窗口就会出现ISim仿真软件了,第一个功能是行为级语法检查,在编写完testbench之后可以用于排查语法错误。

双击第二个选项Simulate Behavior Model即可启动行为级仿真了。

图10 启动行为级仿真(3)使用Sim仿真设计时序。

图11 ISim仿真界面界面打开之后默认只跑1us,由于计数器计数较长,需要多运行一会才能看到led信号的跳变。

点击操作栏上的按钮让它多运行一会就可以了,暂停时点击按钮。

另外可将Objects窗口中的信号通过右键选择加入到仿真窗口中以方便观测。

分页4 综合(1)将Design窗口中的View项切换为Implementation,然后选中顶层文件,在下面的Processes窗口中就会出现综合实现的工具选项。

这里双击Synthesize –XST就开始运行综合了。

图12 综合综合过程中出现的各种警告或是错误报告会出现在Console窗口中,综合完成后状态显示为,双击Errors and Warnings中的就可以打开综合报告。

双击View RTL Schematic,打开设计综合后的RTL级视图。

双击后会弹出下图所示的对话框,第一个是打开一个窗口文件管理向导,第二个是直接进入顶层设计的浏览。

默认为第二个,点击OK。

图13 设置RTL查看设置下图就是打开后能看到的顶层模块视图。

可以看到最外层的输入和输出接口,一般复杂一点的设计就可以同过顶层视图来确定个模块之间的端口是否正确连接。

图14 顶层模块双击顶层模块就可进入与之相应的模块内部RTL视图,在RTL级视图里,可以清楚地看到每一条语句是被综合工具综合成了什么逻辑器件。

核对一下是否是自己预想的逻辑电路。

图15 RTL级视图综合工具中还有一个View Technology Schematic选项,工艺级视图,比RTL级电路更详细,更接近综合后在芯片中要形成的实际电路和资源使用情况。

可以看到各个逻辑部件内部的寄存器和门电路。

图16 工艺级视图5 时序仿真在主窗口左侧的Design窗口中选择Simulation→下拉栏中选Post-T ranslate→选中仿真激励文件→在Processes窗口就会出现ISim仿真软件了,双击Simulate Post-Translate Model即可启动时序仿真。

图17 时序仿真时序仿真由于加入了门级延迟,所以比行为级仿真的运算量大,仿真起来速度也会慢很多。

点击Run之后多等几分钟。

图18 时序仿真结果ISim还能做映射(Post-Map)和布局布线(Post-Route)之后的仿真,时序能更贴近真实情况。

一般在高速和时序非常复杂的设计中才会用到,使用方法与上面类似,这里不再赘述。

6 实现(1)添加管脚约束。

在源代码窗口中单击右键,在弹出的菜单中选择New Source,然后选择,输入文件名,点击下一步。

在弹出的窗口确认信息无误后点击Finish。

软件会自动打开约束文件编辑窗口,输入以下代码,点击保存。

约束文件也可以通过选择操作窗口中的User Constraints→I/O Pin Planning启动PlanAhead来通过图形界面添加生成。

(2)运行实现。

实现的步骤包括翻译,映射,布局布线三个步骤。

在Design窗口中选中顶层文件后双击操作窗口中的Implement Design,软件就会自动运行实现的三个步骤。

图19 运行实现工具完成后状态显示为,各项操作过程中出现的错误和警告信息可以在Errors and Warnings窗口中选择查看。

分页7 下载调试双击操作窗口中的Configure Target Device启动下载程序。

这个过程中会自动生成编程文件(Xilinx的FPGA配置文件为.bit后缀),并启动iMPACT软件。

在软件运行的过程中你可以连接好下JTAG载线,将板子通上电。

图20 选择配置目标器件运行完成之后会自动弹出iMPACT软件界面,在该界面中双击Boundary Scan,然后单击工具栏上的图标,软件就会自动扫描JTAG链路上的目标器件。

图21 iMPACT界面软件会自动打开配置文件选择窗口,将路径引导到工程目录,选择我们刚才生成的bit 文件。

软件还会询问是否需要添加外挂的PROM芯片,这里选否。

然后点击OK。

如果硬件连接正确且工作正常,就能看到下图所示的界面。

选中芯片后在点击右键,选择Program。

图22 下载界面如果提示Programmed successfully就表明下载成功了,接下来你就能看到板子上的LED开始闪烁了。

8 总结本篇通过一个简单的实例讲解了整个设计的流程,对初学者入门有一定的帮助,但这些操作只是涉及到了ISE强大功能中很小的一部分,更深入的功能有待于大家继续摸索。