LVDS接口与MIPI接口培训讲学

液晶屏MIPI接口与LVDS接口区别(总结)

液晶屏MIPI接口与LVDS接口区别(总结)液晶屏接口类型有LVDS接口、MIPI DSIDSI接口(下文只讨论液晶屏LVDS接口,不讨论其它应用的LVDS接口,因此说到LVDS接口时无特殊说明都是指液晶屏LVDS接口),它们的主要信号成分都是5组差分对,其中1组时钟CLK,4组DATA(MIPI DSI接口中称之为lane),它们到底有什么区别,能直接互联么?在网上搜索“MIPI DSI接口与LVDS 接口区别”找到的答案基本上是描述MIPI DSI接口是什么,LVDS接口是什么,没有直接回答该问题。

深入了解这些资料后,有了一些眉目,整理如下。

首先,两种接口里面的差分信号是不能直接互联的,准确来说是互联后无法使用,MIPI DSI 转LVDS比较简单,有现成的芯片,例如ICN6201、ZA7783;LVDS转MIPI DSI比较复杂暂时没看到通用芯片,基本上是特制模块,而且原理也比较复杂。

其次,它们的主要区别总结为两点:1、LVDS接口只用于传输视频数据,MIPI DSI不仅能够传输视频数据,还能传输控制指令;2、LVDS接口主要是将RGB TTL信号按照SPWG/JEIDA格式转换成LVDS信号进行传输,MIPI DSI接口则按照特定的握手顺序和指令规则传输屏幕控制所需的视频数据和控制数据。

从传输的内容可以更直观看到两种接口的区别,具体传输的内容如下:1、LVDS接口表上slot0到slot6表示时钟周期,CHx_DATA0到CHx_DATA3分别表示数据差分对1到4组,而后面跟着的G0等视频帧就是数据2、MIPI DSI接口图2 MIPI DSI接口每个lane里面传输的内容图3 一个SP或者LgP的展开图通道里面按需要以短包(SP)或者长包(LgP)的形式传送数据,具体的包格式参考相关资料。

在此就能看出LVDS接口和MIPI DSI接口物理介质同是差分线对,但是传输的内容确实完全不同的。

LVDS接口与MIPI接口培训讲学

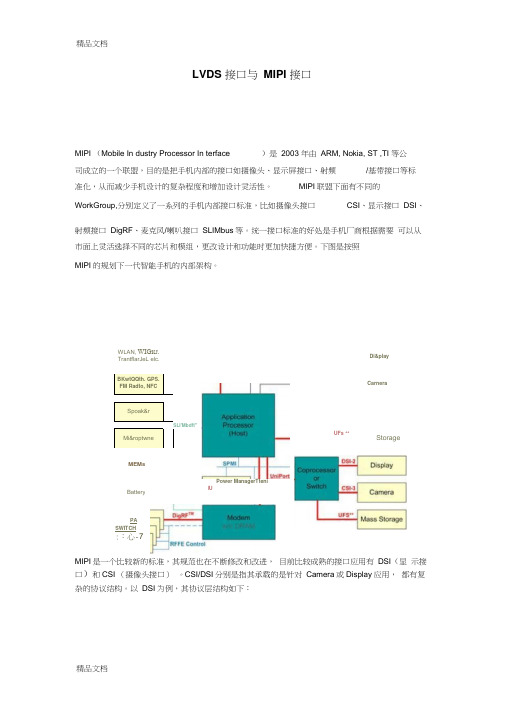

LVDS 接口与 MIPI 接口MIPI (Mobile In dustry Processor In terface )是 2003 年由 ARM, Nokia, ST ,TI 等公司成立的一个联盟,目的是把手机内部的接口如摄像头、显示屏接口、射频 /基带接口等标准化,从而减少手机设计的复杂程度和增加设计灵活性。

MIPI 联盟下面有不同的WorkGroup,分别定义了一系列的手机内部接口标准,比如摄像头接口CSI 、显示接口 DSI 、射频接口 DigRF 、麦克风/喇叭接口 SLIMbus 等。

统一接口标准的好处是手机厂商根据需要 可以从市面上灵活选择不同的芯片和模组,更改设计和功能时更加快捷方便。

下图是按照 MIPI 的规划下一代智能手机的内部架构。

MIPI 是一个比较新的标准,其规范也在不断修改和改进, 目前比较成熟的接口应用有 DSI (显 示接口)和CSI (摄像头接口) 。

CSI/DSI 分别是指其承载的是针对 Camera 或Display 应用, 都有复杂的协议结构。

以 DSI 为例,其协议层结构如下:Di&playBKwtQQth. GPS. FM Radto, NFCSLI'Mbdft"Spoak&rMi&roptwneCarneraBatteryWLAN, WIG KJ . TrantflarJeL elc.MEMsPower ManagerTteniIUPA SWITCH::心-7UFs ++StorageApptic^tlQnD J <J CortroiSnnxod Gtntralwn ■' ImefpfeLirtXiApplication Dita Cweral"7T Dau〔::8W1DataCentralLow Ltvtl Ptoweo) DdU C#<ratControlPHY L^ytrLane Dhsinbuuon and Lterqinqstn of Packet EJKI of PacketSenaiczef i Deseriaiizef Ckxrk Management (DDR F EtKlncaJ Ljyef (StVS,L^nt|ControlPHY LaytrLane 0 - Hi^h Spee^ Data gp 曲阳lly BkhrMigol in IP Mo<Jei *t tLarte N 一 High Speed tian J :I DataCSI/DSI 的物理层(Phy Layer )由专门的 WorkGroup 负责制定,其目前的标准是 D-PHY D-PHY 采用1对源同步的差分时钟和1〜4对差分数据线来进行数据传输 。

基于FPGA的LVDS学习报告ppt课件

3.2 Multidrop

多落点总线具有一个驱动器,同一总线上有多个接收器,这里的通信 同样也是单向的。 优点: 互联数更少 无需中央交换芯片 可以实现数据的串行化 — 引线更少,连接器更小。 缺点: 电气路径有一定的复杂性 开机状态下的插拔很棘手

信号分发问题

对LVDS信号进行分发处理,即将一路 LVDS信号发送到多个接收器件,是我们经 常会用到的。 直接连接方式 采用专用芯片对LVDS信号进行处理

注:ISI是Inter System Interference缩写,其中文名:码间干扰

片上100W电阻 在LVDS I/O引脚进行7kV ESD(Electro-Static discharge )测试,保护相邻器件 3 mm x 3 mm,8引脚WSON封装

DS25BR110引脚框图和控制引脚真值表

From:DS25BR120 3.125 Gbps LVDS Buffer with Transmit Pre-Emphasis

DS25BR110

3.125 Gbps LVDS Buffer with Receive Equalization

DS25BR110 特点

直流-3.125Gbps 低抖动,高抗干扰性,低功率运行 Four Levels of Receive Equalization (Reduce ISI Jitter)

2、LVDS接口电路原理示意图

LVDS接口电路连接图

DS92LV18框图

DS92LV18特点

15–66 MHz 18:1/1:18 串行/解串器(2.376Gbps full duplex throughput) 3.3V供电 内置锁相环(PLL) Robust BLVDS serial transmission across backplanes and cables for low EMI 具有各自的时钟,使能端和电源端进行独立的发送和接收 热插拔保护 低功率: 90mA (典型值) 发送

显示器芯片级维修课程-LVDS 屏线以及接口(第十讲)

4、根据屏参数选择对应的驱动程序。 例: PC-202S

指SCALER 芯片型号

例:LTM150XN07-XGA-5V-SI8L-NA-5KEY 注:尺寸、显示模式、色差对得上的程序都可以刷,没有原程序后找其他程序。

注:薄屏全部3.3V供电,厚屏全部红5V供电。 如何确定屏接口类型:

1、量供电脚和接地脚。 2、量每组差分之间值一致,在100欧或120欧左右。

点屏配板和刷写程序 1、根据屏的型号确定屏的参数:

例:LTM150XKN07-

生产厂家(三星) 屏幕大小尺寸(15寸) XGA显示模式:1280*768

2、根据客户需求配板: 接口: PC+DVI AV TV HDMI USB SD CF

1

3

5

7

11

13 15

17 时 19 色 21 23

25 27 时 29 色 31

色度差分

钟度

差

差 色度差分

钟度 差差

分分

分分

SI6L(四组双绞线) SI8L(五组双绞线)

D06L(八组双绞线)

D08L(十组双绞线)

LVDS屏线采用双绞差分传输,按接口类型分为: 片插:FIX 30P/SI6L 、SI8L、D06L、D08L 20P/SI6L、SI8L 针插:DF-14(最厚、孔最大):30P/D08L 20P/D06L、SI6L、SI8L DF-19(最薄、孔最小):14P/SI6L 20P/SI6L、SI8L 30P/D08L 51146:20P/SI6L、SI8L、D06L 30P/D08L LG专用 D08L东芝专用 FIS:IBM早期专用

偶数

(完整版)LVDS接口详解

1.LVDS输出接口概述液晶显示器驱动板输出的数字信号中,除了包括RGB数据信号外,还包括行同步、场同步、像素时钟等信号,其中像素时钟信号的最高频率可超过28MHz。

采用TTL接口,数据传输速率不高,传输距离较短,且抗电磁干扰(EMI)能力也比较差,会对RGB数据造成一定的影响;另外,TTL 多路数据信号采用排线的方式来传送,整个排线数量达几十路,不但连接不便,而且不适合超薄化的趋势。

采用LVDS输出接口传输数据,可以使这些问题迎刃而解,实现数据的高速率、低噪声、远距离、高准确度的传输。

那么,什么是LVDS输出接口呢?LVDS,即Low Voltage Differential Signaling,是一种低压差分信号技术接口。

它是美国NS公司(美国国家半导体公司)为克服以TTL电平方式传输宽带高码率数据时功耗大、EMI电磁干扰大等缺点而研制的一种数字视频信号传输方式。

LVDS输出接口利用非常低的电压摆幅(约350mV)在两条PCB走线或一对平衡电缆上通过差分进行数据的传输,即低压差分信号传输。

采用LVDS输出接口,可以使得信号在差分PCB线或平衡电缆上以几百Mbit/s的速率传输,由于采用低压和低电流驱动方式,因此,实现了低噪声和低功耗。

目前,LVDS输出接口在17in及以上液晶显示器中得到了广泛的应用。

2.LVDS接口电路的组成在液晶显示器中,LVDS接口电路包括两部分,即驱动板侧的LVDS输出接口电路(LVDS发送器)和液晶面板侧的LVDS输入接口电路(LVDS接收器)。

LVDS发送器将驱动板主控芯片输出的17L电平并行RGB数据信号和控制信号转换成低电压串行LVDS信号,然后通过驱动板与液晶面板之间的柔性电缆(排线)将信号传送到液晶面板侧的LVDS接收器,LVDS接收器再将串行信号转换为TTL电平的并行信号,送往液晶屏时序控制与行列驱动电路。

图1所示为LVDS接口电路的组成示意图。

图1 LVDS接口电路的组成示意图在数据传输过程中,还必须有时钟信号的参与,LVDS接口无论传输数据还是传输时钟,都采用差分信号对的形式进行传输。

LVDS、MIPI、EDP、VGA、DVI、HDMI、DP3.0(雷电接口)

LVDS、MIPI、EDP、VGA、DVI、HDMI、DP3.0(雷电接⼝)

1.LVDS

2.mipi

3.EDP:Embedded DisplayPort

4.VGA

VGA接⼝的特性:

1)理论上能够⽀持2048x1536分辨率画⾯传输。

2)VGA由于是模拟信号传输,所以容易受⼲扰,信号转换容易带来信号的损失。

3)在1080P分辨率下,⽤户就可以通过⾁眼明显感受到画⾯的损失。

4)建议1080P分辨率以下显⽰器采⽤。

5)⾼分辨率⽆法达到应有刷新率及只有图像输⼊没有声⾳输⼊

5.DVI

6.HDMI:High-Definition Multimedia Interface⾼清晰度多媒体接⼝(TMDS协议)

7.DP

1)DP接⼝,是DVI的继任者,现在常见的主要有DisplayPort接⼝和苹果开发的miniDP接⼝。

DP接⼝相对于DVI来说,进步了很多,在带宽和可定制性上⾯,都有了质的变化。

2)PC⽀持完美,⽀持3屏到6屏输出

DP和HDMI的转换:

1、dp(DisplayPort)是数字形式、微封包传输,⽬前版本可同时传输六路1080i视频+⾳频信号

2、HDMI 是数字形式专线传输、只能同时传输⼀路视频+⾳频信号

3、DP转换成hdmi需要才能转换,因此,是⼀个⼩,⾥⾯装有可以把dp中的多路视频+⾳频信号解包,分路,这类转换器是⼀路dp线输⼊,⽽⽬前版本输出最多可达到六路输出(包括hdmi、DVI、VGA)

4、dp输出分路多寡,还需要⽀持。

lvds液晶屏幕接口详解

1.LVDS输出交心概括之阳早格格创做液晶隐现器启动板输出的数字旗号中,除了包罗RGB数据旗号中,还包罗止共步、场共步、像素时钟等旗号,其中像素时钟旗号的最下频次可超出28MHz.采与TTL交心,数据传输速率没有下,传输距离较短,且抗电磁搞扰(EMI)本领也比较好,会对付RGB数据制成一定的做用;其余,TTL多路数据旗号采与排线的办法去传递,所有排线数量达几十路,没有单连交便当,而且没有符合超薄化的趋势.采与LVDS输出交心传输数据,不妨使那些问题迎刃而解,真止数据的下速率、矮噪声、近距离、下准确度的传输.那么,什么是LVDS输出交心呢?LVDS,即Low V oltage Differential Signaling,是一种矮压好分旗号技能交心.它是好国NS公司(好国国家半导体公司)为克服以TTL电仄办法传输宽戴下码率数据时功耗大、EMI电磁搞扰大等缺面而研制的一种数字视频旗号传输办法.LVDS输出交心利用非常矮的电压晃幅(约350mV)正在二条PCB走线大概一对付仄稳电缆上通过好分举止数据的传输,即矮压好分旗号传输.采与LVDS输出交心,不妨使得旗号正在好分PCB线大概仄稳电缆上以几百Mbit/s的速率传输,由于采与矮压战矮电流启动办法,果此,真止了矮噪声战矮功耗.暂时,LVDS输出交心正在17in及以上液晶隐现器中得到了广大的应用.2.LVDS交心电路的组成正在液晶隐现器中,LVDS交心电路包罗二部分,即启动板侧的LVDS输出交心电路(LVDS收支器)战液晶里板侧的LVDS 输进交心电路(LVDS交支器).LVDS收支器将启动板主控芯片输出的17L电仄并止RGB数据旗号战统制旗号变换成矮电压串止LVDS旗号,而后通过启动板与液晶里板之间的柔性电缆(排线)将旗号传递到液晶里板侧的LVDS交支器,LVDS交支器再将串止旗号变换为TTL电仄的并止旗号,支往液晶屏时序统制与止列启动电路.图1所示为LVDS交心电路的组成示企图.图1 LVDS交心电路的组成示企图正在数据传输历程中,还必须奇尔钟旗号的介进,LVDS 交心无论传输数据仍旧传输时钟,皆采与好分旗号对付的形式举止传输.所谓旗号对付,是指LVDS交心电路中,每一个数据传输通道大概时钟传输通道的输出皆为二个旗号(正输出端战背输出端).需要证明的是,分歧的液晶隐现器,其启动板上的LVDS 收支器没有尽相共,有些LVDS收支器为一片大概二片独力的芯片(如DS90C383),有些则集成正在主控芯片中(如主控芯片gm5221内里便集成了LVDS收支器).3.LVDS输出交心电路典型与TTL输出交心相共,LVDS输出交心也分为以下四种典型:(l)单路6位LVDS输出交心那种交心电路中,采与单路办法传输,每个基色(即RGB三色中的其中所有一种颜色)旗号采与6位数据(XOUT0+、TXOUT0-,TXOUT1+、TXOUT1-,TXOUT2+、TXOUT2-),共18位RGB(6bit X 3(RGB3色))数据,果此,也称18位大概18bit LVDS交心.此,也称18位大概18bit LVDS 交心.(2)单路6位LVDS输出交心那种交心电路中,采与单路办法传输,每个基色旗号采与6位数据,其中奇路数据为18位,奇路数据为18位,共36位RGB数据,果此,也称36位大概36bit LVDS交心.(3)单路8位1TL输出交心那种交心电路中,采与单路办法传输,每个基色旗号采与8位数据(XOUT0+、TXOUT0-,TXOUT1+、TXOUT1-,TXOUT2+、TXOUT2-,TXOUT3+,TXOUT3),共24位RGB 数据(8bit X 3),果此,也称24位大概24bit LVDS交心.(4)单路8位1TL输出位交心那种交心电路中,采与单路办法传输,每个基色旗号采与8位数据,其中奇路数据为24位,奇路数据为24位,共48位RGB数据,果此,也称48位大概48bit LVDS交心4.典型LVDS收支芯片介绍典型的LVDS收支芯片分为四通道、五通道战十通道几种,底下简要举止介绍.(1)四通道LVDS收支芯片图2 所示为四通道LVDS收支芯片(DS90C365)内里框图.包罗了三个数据旗号(其中包罗RGB、数据使能DE、止共步旗号HS、场共步旗号VS)通道战一个时钟旗号收支通道.图2 4通道LVDS收支芯片内里框图4通道LVDS收支芯片主要用于启动6bit液晶里板.使用四通道LVDS收支芯片不妨形成单路6bit LVDS交自电路战奇/奇单路6bit LVDS交心电路.(2)五通道LVDS收支芯片图3 所示为五通道LVDS收支芯片(DS90C385)内里框图.包罗了四个数据旗号(其中包罗RGB、数据使能DE、止共步旗号IIS、场共步旗号vs)通道战一个时钟旗号收支通道.图3 5通道LVDS收支芯片内里框图五通道LVDS收支芯片主要用于启动8bit液晶里板.使用五通道LVDS收支芯片主要用去形成单路8bit LVDS交心电路战奇/奇单路8bit LVDS交心电路.(3)十通道LVDS收支芯片图4所示为十通道LVDS收支芯片(DS90C387)内里框图.包罗了八个数据旗号(其中包罗RGB、数据使能DE、止共步旗号HS、场共步旗号VS)通道战二个时钟旗号收支通道.图4 十通道LV DS收支芯片内里框图十通道LVDS收支芯片主要用于启动8bit液晶里板.使用十通道LYDS收支芯片主要用去形成奇/奇单路8bit LVDS位交心电路.正在十通道LVDS收支芯片中,树坐了二个时钟脉冲输出通道,那样搞的手段是不妨越收机动的符合分歧典型的LVDS 交支芯片.当LVDS交支电路共样使用一片十通道LVDS交支芯片时,只需使用一个通道的时钟旗号即可;当LVDS交支电路使用二片五通道LVDS交支芯片时,十通道LYDS收支芯片需要为每个LVDS交支芯片提供单独的时钟旗号.5.LVDS收支芯片的输进与输出旗号(1)LVDS收支芯片的输进旗号LVDS收支芯片的输进旗号去自决控芯片,输进旗号包罗RGB数据旗号、时钟旗号战统制旗号三大类.①数据旗号:为了证明的便当,将RGB旗号以及数据选通DE战止场共步旗号皆算做数据旗号.正在供6bit液晶里板使用的四通道LVDS收支芯片中,公有十八个RGB旗号输进引足,分别是R0~R5白基色数据(6bit 白基色数据,R0为最矮灵验位,R5为最下灵验位)六个,G0~G5绿基色数据六个,B0~B5蓝基色数据六个;一个隐现数据使能旗号DE(数据灵验旗号)输进引足;一个止共步旗号HS输进引足;一个场共步旗号VS输进引足.也便是道,正在四通道LYDS收支芯片中,公有二十一个数据旗号输进引足.正在供8bit液晶里板使用的五通道LVDS收支芯片中,公有二十四个RGB旗号输进引足,分别是白基色数据R0~W(8bit白基色数据,R0为最矮灵验位,R7为最下灵验位)八个,绿基色数据G0~G7八个,蓝基色数据B0~B7八个;一个灵验隐现数据使能旗号DE(数据灵验旗号)输进引足;一个止共步旗号HS输进引足;一个场共步旗号VS输进引足;一个各用输进引足.也便是道,正在五通道LVDS收支芯片中,公有二十八个数据旗号输进引足.该当注意的是,液晶里板的输进旗号中皆必须要有DE旗号,然而有的液晶里板只使用简单的DE旗号而没有使用止场共步旗号.果此,应用于分歧的液晶里板时,有的LVDS收支芯片大概只需输进DE旗号,而有的需要共时输进DE战止场共步旗号.②输进时钟旗号:即像素时钟旗号,也称为数据移位时钟(正在LVDS收支芯片中,将输进的并止RGB数据变换成串止数据时要使用移位寄存器).像素时钟旗号是传输数据战对付数据旗号举止读与的基准.③待机统制旗号(POWER DOWN):当此旗号灵验时(普遍为矮电通常),将关关LVDS收支芯片中时钟PLL锁相环电路的供电,停止IC的输出.④数据与样面采用旗号:用去采用使用时钟脉冲的降下沿仍旧下落沿读与所输进的RGB数据.有的LVDS收支芯片大概本去没有树坐待机统制旗号战数据与样面采用旗号,然而也有的除了上述二个统制旗号还树坐有其余一些统制旗号.(2)LVDS收支芯片的输出旗号LVDS收支芯片将以并止办法输进的TTL电仄RGB数据旗号变换成串止的LVDS旗号后,曲交支往液晶里板侧的LVDS 交支芯片.LVDS收支芯片的输出是矮晃幅好分对付旗号,普遍包罗一个通道的时钟旗号战几个通道的串止数据旗号.由于LVDS收支芯片是以好分旗号的形式举止输出,果此,输出旗号为二条线,一条线输出正旗号,另一条线输出背旗号.①时钟旗号输出:LVDS收支芯片输出的时钟旗号频次与输进时钟旗号(像素时钟旗号)频次相共.时钟旗号的输出常表示为:TXCLK+战TXCLK-,时钟旗号占用LVDS收支芯片的一个通道.②LVDS串止数据旗号输出:对付于四通道LVDS收支芯片,串止数据占用三个通道,其数据输出旗号常表示为TXOUT0+、TXOUT0-,TXOUT1+、TXOUT1-,TXOUT2+、TXOUT2-.对付于五通道LVDS收支芯片,串止数据占用四个通道,其数据输出旗号常表示为TXOUT0+、TXOUT0-,TXOUT1+、TXOUTI-,TXOUT2+、TXOUT2-,TXOUT3+、TXOUT3-.对付于十通道LVDS收支芯片,串止数据占用八个通道,其数据输出旗号常表示为TXOUT0+、TXOUT0-,TXOUT1+、TXOUT1-,TXOUT2+、TXOUT2-,TXOUT3+、TXOUT3-,TXOUT4+、TXOUT4-,TXOUT5+、TXOUT5-,TXOUT6+、TXOUT6-,TXOUT7+、TXOLT7-.如果只瞅电路图,是没有克没有及从LVDS收支芯片的输出旗号TXOUT-、TXOUT0+中瞅出其内里到底包罗哪些旗号数据,以及那些数据是何如排列的(大概者道那些数据的圆法是何如的).究竟上,分歧厂家死产的LVDS收支芯片,其输出数据排列办法大概是分歧的.果此,液晶隐现器启动板上的LVDS收支芯片的输出数据圆法必须与液晶里板LVDS交支芯片央供的数据圆法相共,可则,启动板与液晶里板没有匹配.那也是调换液晶里板时必须思量的一个问题.博家面拔LVDS收支芯片正在一个时钟脉冲周期内,每个数据通道皆输出7bit的串止数据旗号,而没有是罕睹的8bit数据,如图5所示图5LVDS交心电路正在一个时钟脉冲周期内传输7bit数据(3)LVDS收支芯片输出旗号的圆法LVDS收支芯片输出旗号的圆法,即LVDS收支芯片输进的RGB数据,以及止共步旗号HS、场共步旗号VS、灵验隐现数据使能旗号DE正在各个输出通道中数据位的排列程序.由于几个大的LYDS芯片死产厂家制定了分歧的尺度,果此,存留着几种分歧的LVDS收支芯片数据输出圆法,正在调换液晶隐现器启动板大概调换液晶里板时,必须弄浑LVDS交心液晶里板所央供的LVDS旗号圆法,使液晶隐现器启动板侧LVDS 收支芯片的输出数据圆法与液晶里板LVDS交支芯片所央供的数据圆法相共.①单路6bit LVDS收支芯片数据输出圆法:单路6bit LVDS收支电路使用四通道LVDS收支芯片,输出旗号圆法如图6所示.图6 单路6bit LVDS收支芯片数据输出圆法图6中NA的意义是已使用.此例为统制旗号仅使用DE的模式,已使用止共步旗号HS战场共步旗号VS.关于DE、IIS、VS旗号的使用问题,将正在第9章举止介绍.当统制旗号为DE+止场共步旗号模式时,图中的二个NA调换为场共步旗号VS战止共步旗号HS.②单路6bit LVDS收支芯片数据输出圆法:单路6bit LVDS 收支电路使用二片四通道LVDS收支芯片,输出旗号圆法如图7所示.图7 单路6bit LVDS收支芯片数据输出圆法从图7中不妨瞅出,单路6bit LVDS收支芯片数据输出圆法与单路6bit LVDS收支芯片数据输出圆法是相共的,只没有过一路传递奇数像素RGB数据,另工路传递奇数像素RGB数据.OR0、OR1、…中的“O”代表奇数像素,ER0、ER1、…中的“E”代表奇数像素.③单路8bit LVDS收支芯片数据输出圆法:单路8bit LVDS收支电路使用五通道LVDS收支芯片,输出旗号圆法有多种,底下只介绍其中的二种.图8所示是其中的一种输出旗号圆法.图9所示是爆收那种数据旗号圆法的电路交法.图8 单路8bit LVDS收支芯片数据输出圆法之一图9 所示数据输出圆法的电路交法图10 所示为单路8bit LVDS收支芯片的另一种数据输出圆法.图10 单路8bit LVDS收支芯片数据输出圆法之二图11 所示圆法中的统制旗号仅使用DE模式,当统制旗号为DE+止场共步旗号模式时,第二数据通道TXOUT2中的二个NA应调换为场共步旗号VS战止共步旗号HS(通过对付启动板编程可改写).从以上二种输出圆法中不妨瞅出,数据旗号的排列程序没有共很大,没有过,要念让其排列普遍,真足不妨通过对付启动板编程去完毕.图11 单路8bit LVDS收支芯片数据输出圆法之一④单路8bit LVDS收支芯片数据输出圆法:单路8bit LVDS收支电路使用二片五通道LVDS收支芯片大概一片十通道LVDS收支芯片,单路8bit LVDS收支芯片数据输出圆法也有多种形式,图11所示是其中的一种.上头咱们了解了屏的型号战交心了,然而是咱们还没有了解那个是几位的屏战几的供电,为了让大家沉快搞会那一步,咱们拿一个单6位LVDS的屏去剖析一下,此款屏的型号为:LP141X3(20针插交心)屏交心定义正在液晶屏那内里出现了二组数据每组中皆有一对付时钟旗号,那个屏咱们便能瞅出那是一个30针单8位屏,屏的供电为5V.罕睹的LVDS交心定义20PIN单6定义:1:电源2:电源3:天4:天5:R0 6:R0+ 7:天8:R1 9:R1+ 10:天11:R2 12:R2+ 13:天14:CLK 15:CL K+ 16空17空18空19空20空每组旗号线之间电阻为(数字表100欧安排)指针表20-100欧安排(4组相共阻值)20PIN单6定义:1:电源2:电源3:天4:天5:R0 6:R0+ 7:R1 8:R1+ 9:R2 10:R2+ 11:CLK 12:CLK+ 1 3:RO1 14:RO1+ 15:RO2 16:RO2+ 17:RO3 18:RO 3+ 19:C L K120:C L K1+每组旗号线之间电阻为(数字表100欧安排)指针表20-100欧安排(8组相共阻值)20PIN单8定义:1:电源2:电源3:天4:天5:R0 6:R0+ 7:天8:R1 9:R1+ 10:天11:R2 12:R2+ 13:天14:C L K15:C L K+16:R317:R3+ 每组旗号线之间电阻为(数字表100欧安排)指针表20-100欧安排(5组相共阻值)30PIN单8定义:1:电源2:电源3:电源4:空5:空6:空7:天8:R0 9:R0+ 10:R1 11:R1+ 12:R2 13:R2+ 14:天15:CLK 16:CLK + 17:天18:R3 19:R3+ 20:RB0 21:RB0+ 22:RB1 2 3:RB1+ 24:天25:RB2 26:RB2+ 27:CLK2 28:C L K2+29:R B330:R B3+ 每组旗号线之间电阻为(数字表100欧安排)指针表20-100欧安排(10组相共阻值)普遍14PIN、20PIN、30PIN 为LVDS交心,15寸(含15寸)以下多为3.3V供电17(含17)以上多为5V供电.那不过罕睹屏是那样程序,而没有是所有的皆是那样.罕睹TTL的屏交心定义列:那是一个罕睹的41扣TTL的屏交心去瞅瞅与LVDS 的屏有什么辨别(屏型号为M12153DS 41扣单六位TTL屏)知识面:TTL交心的屏线明隐比LVDS的屏线多罕睹31扣41扣30+50 60扣70扣80扣TTL的屏也有单组数据战单组数据之分以此类推便不妨了罕睹TTL屏线D6T(单6位TTL):31扣针,41扣针.对付应屏的尺寸主要为条记原液晶屏(8寸,10寸,11寸,12寸),另有部分台式机屏15寸为41扣针交心.S6T(单6位TTL):30+45针硬排线,60扣针,70扣针,80扣针.主要为台式机的14寸,15寸液晶屏.S8T(单8位TTL):有,很少睹80扣针(14寸,15寸)。

lvds液晶屏幕接口详解之欧阳歌谷创作

1.LVDS输出接口概述欧阳歌谷(2021.02.01)液晶显示器驱动板输出的数字信号中,除了包括RGB数据信号外,还包括行同步、场同步、像素时钟等信号,其中像素时钟信号的最高频率可超过28MHz。

采用TTL接口,数据传输速率不高,传输距离较短,且抗电磁干扰(EMI)能力也比较差,会对RGB数据造成一定的影响;另外,TTL多路数据信号采用排线的方式来传送,整个排线数量达几十路,不但连接不便,而且不适合超薄化的趋势。

采用LVDS输出接口传输数据,可以使这些问题迎刃而解,实现数据的高速率、低噪声、远距离、高准确度的传输。

那么,什么是LVDS输出接口呢?LVDS,即Low V oltage Differential Signaling,是一种低压差分信号技术接口。

它是美国NS公司(美国国家半导体公司)为克服以TTL电平方式传输宽带高码率数据时功耗大、EMI电磁干扰大等缺点而研制的一种数字视频信号传输方式。

LVDS输出接口利用非常低的电压摆幅(约350mV)在两条PCB走线或一对平衡电缆上通过差分进行数据的传输,即低压差分信号传输。

采用LVDS输出接口,可以使得信号在差分PCB 线或平衡电缆上以几百Mbit/s的速率传输,由于采用低压和低电流驱动方式,因此,实现了低噪声和低功耗。

目前,LVDS输出接口在17in及以上液晶显示器中得到了广泛的应用。

2.LVDS接口电路的组成在液晶显示器中,LVDS接口电路包括两部分,即驱动板侧的LVDS输出接口电路(LVDS发送器)和液晶面板侧的LVDS输入接口电路(LVDS接收器)。

LVDS发送器将驱动板主控芯片输出的17L电平并行RGB数据信号和控制信号转换成低电压串行LVDS信号,然后通过驱动板与液晶面板之间的柔性电缆(排线)将信号传送到液晶面板侧的LVDS接收器,LVDS接收器再将串行信号转换为TTL电平的并行信号,送往液晶屏时序控制与行列驱动电路。

图1所示为LVDS接口电路的组成示意图。

lvds液晶屏幕接口详解 (2)

1.LVDS输出接口概述液晶显示器驱动板输出的数字信号中,除了包括RGB数据信号外,还包括行同步、场同步、像素时钟等信号,其中像素时钟信号的最高频率可超过28MHz。

采用TTL接口,数据传输速率不高,传输距离较短,且抗电磁干扰(EMI)能力也比较差,会对RGB数据造成一定的影响;另外,TTL 多路数据信号采用排线的方式来传送,整个排线数量达几十路,不但连接不便,而且不适合超薄化的趋势。

采用LVDS输出接口传输数据,可以使这些问题迎刃而解,实现数据的高速率、低噪声、远距离、高准确度的传输。

那么,什么是LVDS输出接口呢?LVDS,即Low Voltage Differential Signaling,是一种低压差分信号技术接口。

它是美国NS公司(美国国家半导体公司)为克服以TTL电平方式传输宽带高码率数据时功耗大、EMI电磁干扰大等缺点而研制的一种数字视频信号传输方式。

LVDS输出接口利用非常低的电压摆幅(约350mV)在两条PCB走线或一对平衡电缆上通过差分进行数据的传输,即低压差分信号传输。

采用LVDS输出接口,可以使得信号在差分PCB线或平衡电缆上以几百Mbit/s的速率传输,由于采用低压和低电流驱动方式,因此,实现了低噪声和低功耗。

目前,LVDS输出接口在17in及以上液晶显示器中得到了广泛的应用。

2.LVDS接口电路的组成在液晶显示器中,LVDS接口电路包括两部分,即驱动板侧的LVDS输出接口电路(LVDS发送器)和液晶面板侧的LVDS输入接口电路(LVDS接收器)。

LVDS发送器将驱动板主控芯片输出的17L电平并行RGB数据信号和控制信号转换成低电压串行LVDS信号,然后通过驱动板与液晶面板之间的柔性电缆(排线)将信号传送到液晶面板侧的LVDS接收器,LVDS接收器再将串行信号转换为TTL电平的并行信号,送往液晶屏时序控制与行列驱动电路。

图1所示为LVDS接口电路的组成示意图。

图1 LVDS接口电路的组成示意图在数据传输过程中,还必须有时钟信号的参与,LVDS接口无论传输数据还是传输时钟,都采用差分信号对的形式进行传输。

二、液晶屏LVDS接口常用功能信号_液晶彩色电视机维修从入门到精通_[共2页]

第8章 逻辑板电路分析与检修– 199 –续表脚 号符 号 功 能备 注ERX0+ 偶像数LVDS 差分信号输入0+ ERX1− 偶像数LVDS 差分信号输入1− ERX1+ 偶像数LVDS 差分信号输入1+ ERX2− 偶像数LVDS 差分信号输入2− ERX2+ 偶像数LVDS 差分信号输入2+ GND 接地ECLK − 偶像数时钟信号− ECLK+ 偶像数时钟信号+ GND 接地ERX3− 偶像数LVDS 差分信号输入3− ERX3+ 偶像数LVDS 差分信号输入3+ NC 空脚 NC 空脚 NC 空脚 NC 空脚 GND 接地 GND 接地 GND 接地 GND 接地VCC 12V 或18V 供电 VCC 12V 或18V 供电VCC 12V 或18V 供电VCC12V 或18V 供电二、液晶屏LVDS 接口常用功能信号LVDS 接口除了接收主板的供电(5V 或12V )、LVDS 差分数据外,不同厂家的液晶屏还设有一些其他功能,如:LVDS 数据格式选择(SEL LVDS 或LVDS OPTION )、显示模式控制信号、帧频选择信号(50Hz/60Hz )等,下面分别介绍上述几类控制信号。

1.LVDS 数据格式选择信号液晶面板具有适应多种LVDS 信号格式的功能,通过LVDS 数据格式选择信号的设置(高电平或低电平),可以使液晶面板适应主板送来的LVDS 信号格式。

LVDS 数据格式选择信号常用SEL LVDS 或LVDS OPTION 表示。

目前,大多数TFT 液晶面板都支持VESA LVDS 信号格式和JEIDA LVDS 信号格式。

除三星液晶屏默认格式为JEIDA 外,其余各厂家(LG-Philips 、CM 、AU 、CH )的液晶屏默认格式为VESA。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

LVDS接口与MIPI接口

MIPI (Mobile Industry Processor Interface) 是2003年由ARM, Nokia, ST ,TI等公司成立的一个联盟,目的是把手机内部的接口如摄像头、显示屏接口、射频/基带接口等标准化,从而减少手机设计的复杂程度和增加设计灵活性。

MIPI联盟下面有不同的WorkGroup,分别定义了一系列的手机内部接口标准,比如摄像头接口CSI、显示接口DSI、射频接口DigRF、麦克风 /喇叭接口SLIMbus等。

统一接口标准的好处是手机厂商根据需要可以从市面上灵活选择不同的芯片和模组,更改设计和功能时更加快捷方便。

下图是按照MIPI的规划下一代智能手机的内部架构。

MIPI是一个比较新的标准,其规范也在不断修改和改进,目前比较成熟的接口应用有DSI(显示接口)和CSI(摄像头接口)。

CSI/DSI分别是指其承载的是针对Camera或Display应用,都有复杂的协议结构。

以DSI为例,其协议层结构如下:

CSI/DSI的物理层(Phy Layer)由专门的WorkGroup负责制定,其目前的标准是D-PHY。

D-PHY 采用1对源同步的差分时钟和1~4对差分数据线来进行数据传输。

数据传输采用DDR方式,即在时钟的上下边沿都有数据传输。

D- PHY的物理层支持HS(High Speed)和LP(Low Power)两种工作模式。

HS模式下采用低压

差分信号,功耗较大,但是可以传输很高的数据速率(数据速率为80M~1Gbps); LP模式下采用单端信号,数据速率很低(<10Mbps),但是相应的功耗也很低。

两种模式的结合保证了MIPI总线在需要传输大量数据(如图像)时可以高速传输,而在不需要大数据量传输时又能够减少功耗。

下图是用示波器捕获的MIPI信号,可以清楚地看到HS和LP信号。

MIPI 还是一个正在发展的规范,其未来的改进方向包括采用更高速的嵌入式时钟的M-PHY 作为物理层、CSI/DSI向更高版本发展、完善基带和射频芯片间的 DigRF V4接口、定义高速存储接口UFS(主要是JEDEC组织)等。

当然,MIPI能否最终成功,还取决于市场的选择。

什么是LVDS?

现在的液晶显示屏普遍采用LVDS接口,那么什么是LVDS呢?

LVDS(Low Voltage Differential Signaling)即低压差分信号传输,是一种满足当今高性能数据传输应用的新型技术。

由于其可使系统供电电压低至 2V,因此它还能满足未来应用的需要。

此技术基于 ANSI/TIA/EIA-644 LVDS 接口标准。

LVDS 技术拥有 330mV 的低压差分信号 (250mV MIN and 450mV MAX) 和快速过渡时间。

这可以让产品达到自 100 Mbps 至超过 1 Gbps 的高数据速率。

此外,这种低压摆幅可以降低功耗消散,同时具备差分传输的优点。

LVDS 技术用于简单的线路驱动器和接收器物理层器件以及比较复杂的接口通信芯片组。

通道链路芯片组多路复用和解多路复用慢速 TTL 信号线路以提供窄式高速低功耗 LVDS 接口。

这些芯片组可以大幅节省系统的电缆和连接器成本,并且可以减少连接器所占面积所需的物理空间。

LVDS 解决方案为设计人员解决高速 I/O 接口问题提供了新选择。

LVDS 为当今和未来的高带宽数据传输应用提供毫瓦每千兆位的方案。

更先进的总线 LVDS (BLVDS)是在LVDS 基础上面发展起来的,总线 LVDS (BLVDS) 是基于 LVDS 技术的总线接口电路的一个新系列,专门用于实现多点电缆或背板应用。

它不同于标准的 LVDS,提供增强的驱动电流,以处理多点应用中所需的双重传输。

BLVDS 具备大约 250mV 的低压差分信号以及快速的过渡时间。

这可以让产品达到

自 100 Mbps 至超过 1Gbps 的高数据传输速率。

此外,低电压摆幅可以降低功耗和噪声至最小化。

差分数据传输配置提供有源总线的 +/-1V 共模范围和热插拔器件。

BLVDS 产品有两种类型,可以为所有总线配置提供最优化的接口器件。

两个系列分别是线路驱动器和接收器和串行器/解串器芯片组。

总线 LVDS 可以解决高速总线设计中面临的许多挑战。

BLVDS 无需特殊的终端上拉轨。

它无需有源终端器件,利用常见的供电轨(3.3V 或 5V),采用简单的终端配置,使接口器件的功耗最小化,产生很少的噪声,支持业务卡热插拔和以 100 Mbps 的速率驱动重载多点总线。

总线 LVDS 产品为设计人员解决高速多点总线接口问题提供了一个新选择。