芯片74LS139_中文资料

SN74LS139N中文资料

4

5

6

7

12 11 10 9

VCC = PIN 16 GND = PIN 8

4

5

6

7

12

11

10

9

O0a

O1a

O2a

O3a

O0b

O1b

O2b

ቤተ መጻሕፍቲ ባይዱ

O3b

FAST AND LS TTL DATA 5-235

元器件交易网

SN54/74LS139

FUNCTIONAL DESCRIPTION The LS139 is a high speed dual 1-of-4 decoder/demultiplexer fabricated with the Schottky barrier diode process. The device has two independent decoders, each of which accept two binary weighted inputs (A0, A1) and provide four mutually exclusive active LOW outputs (O0 – O3). Each decoder has an active LOW Enable (E). When E is HIGH all outputs are forced HIGH. The enable can be used as the data input for a 4-output demultiplexer application. Each half of the LS139 generates all four minterms of two variables. These four minterms are useful in some applications, replacing multiple gate functions as shown in Fig. a, and thereby reducing the number of packages required in a logic network.

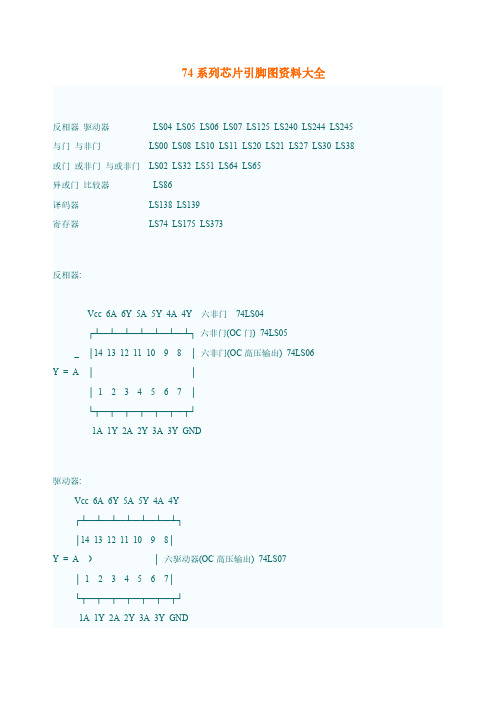

74系列芯片引脚图资料大全(74serieschippindataDaquan)

74系列芯片引脚图资料大全(74 series chip pin data Daquan)74 series chip pin data DaquanAuthor: anonymous sources: the original hits: 57623 update: 07 2007 26 June [font: Small]In order to facilitate everyone, I have collected the following 74 series chip pin data, if necessary, please go to the electronic forum /bbs/Inverter driver LS04, LS05, LS06, LS07, LS125, LS240, LS244, LS245LS00 LS08 LS10 LS11 LS20 NAND gate LS21 LS27 LS30 LS38Or gate or gate or gate and the LS02 LS32 LS51 LS64 LS65Exclusive OR gate comparator LS86Decoder LS138 LS139Register LS74, LS175, LS373Inverter:Vcc 6A 6Y 5A 5Y 4A 4Y six 74LS04 gateThe top - the top - the top - viewpoint of "top - the top - the top - the top six via gate (OC gate) 74LS05_ / 141312111098 / six gates (OC output voltage) 74LS06Y = A),Of the 1234567,: - - - -::::::: "-1A, 1Y, 2A, 2Y, 3A, 3Y, GNDDriver:Vcc, 6A, 6Y, 5A, 5Y, 4A, 4YThe top - the top - the top chrysene - - - - the top top top top grosseserrataOf the 141312111098,Y = A (OC), the six driver output voltage) 74LS07Of the 1234567,: - - - -::::::: "-1A, 1Y, 2A, 2Y, 3A, 3Y, GNDVcc, -4C, 4A, 4Y, -3C, 3A, 3YThe top - the top - the top chrysene - - - - the top top top top grosseserrata_ / 141312111098 /Y =A+C), four bus three state gate 74LS125Of the 1234567,: - - - -::::::: "--1C, 1A, 1Y, -2C, 2A, 2Y, GNDVcc, -G, B1, B2, B3, B4, B8, B6, B8, B7The top - the top - the top chrysene - - - - the top top top top top top top grosseserrata - - - 8 bus driver 74LS2452019181716151413 / 1211 /DIR=1, A=>B)12345678 / 910 / DIR=0 B=>A: - - - -::::::: - - - - -:: "DIR, A1, A2, A3, A4, A5, A6, A7, GND, A8Top gate, driver and gate, or gate NAND gate, or gate XOR gate, comparator decoder registerPositive logic and gate NAND gate:Vcc, 4B, 4A, 4Y, 3B, 3A, 3YThe top - the top - the top chrysene - - - - the top top top top grosseserrataOf the 141312111098,Y = AB), 2 input four positive and 74LS08Of the 1234567,: - - - -::::::: "-1A, 1B, 1Y, 2A, 2B, 2Y, GNDVcc, 4B, 4A, 4Y, 3B, 3A, 3YThe top - the top - the top chrysene - - - - the top top top top grosseserrata__ / 141312111098 /y = (ab) │ 2输入四正与非门 74ls00│ 1 2 3 4 5 6 7│└┬ - ┬ - ┬ - ┬ - ┬ - ┬ - ┬┘1a, 1b, 2a, 2b gnd 1y 2yvcc 1c, 1y 3c, 3b, 3a 3y┌┴ - ┴ - ┴ - ┴ - ┴ - ┴ - ┴┐_ _ _ │14 13 12 11 10 9 8│y = abc) 3输入三正与非门│ 74ls10│ 1 2 3 4 5 6 7│└┬ - ┬ - ┬ - ┬ - ┬ - ┬ - ┬┘1a, 1b, 2a, 2b, 2c gnd 2yvcc h g y┌┴ - ┴ - ┴ - ┴ - ┴ - ┴ - ┴┐│14 13 12 11 10 9 8││ 8输入与非门 74ls30)│ 1 2 3 4 5 6 7│ _ _ _ _ _ _ _ _└┬ - ┬ - ┬ - ┬ - ┬ - ┬ - ┬┘ y = abcdefgha b c d e f gnd页首非门, 驱动器与门, 与非门或门, 或非门异或门, 比较器译码器寄存器正逻辑或门, 或非门:vcc 4b, 3b, 3a, 4a 4y 3y┌┴ - ┴ - ┴ - ┴ - ┴ - ┴ - ┴┐ 2输入四或门 74ls32 │14 13 12 11 10 9 8││ y = (a + b)│ 1 2 3 4 5 6 7│└┬ - ┬ - ┬ - ┬ - ┬ - ┬ - ┬┘1a, 1b, 2a, 2b gnd 1y 2yvcc 4y 4b, 4a 3y 3b, 3a┌┴ - ┴ - ┴ - ┴ - ┴ - ┴ - ┴┐ 2输入四或非门 74ls02 │14 13 12 11 10 9 8│ _ _ _│ y = (a + b)│ 1 2 3 4 5 6 7│└┬ - ┬ - ┬ - ┬ - ┬ - ┬ - ┬┘1a, 1b, 2a, 2b gnd 1y 2yvcc 2y 2b, 2a 2d 2e 1f┌┴ - ┴ - ┴ - ┴ - ┴ - ┴ - ┴┐ 双与或非门 74s51│14 13 12 11 10 9 8│ _ _ _ _ _│ 2y) = ab + de│ 1 2 3 4 5 6 7│ _ _ _ _ _ _ _└┬ - ┬ - ┬ - ┬ - ┬ - ┬ - ┬┘ 1y = abc + def1a, 1b, 1c, 1e, 1d gnd 1yvcc d c b c j y┌┴ - ┴ - ┴ - ┴ - ┴ - ┴ - ┴┐ 4 - 2 - 3 - 2与或非门 74s64 74s65 (oc门)│14 13 12 11 10 9 8│ _ _ _ _ _ _ _ _ _ _ _ _ _ _y = abcd) │ ghi jk = + ef + +│ 1 2 3 4 5 6 7│└┬ - ┬ - ┬ - ┬ - ┬ - ┬ - ┬┘a e f g h i gnd页首非门, 驱动器与门, 与非门或门, 或非门异或门, 比较器译码器寄存器2输入四异或门 74ls86vcc 4b, 4a 4y 3y 3b, 3a┌┴ - ┴ - ┴ - ┴ - ┴ - ┴ - ┴┐│14 13 12 11 10 9 8││ _ _)│ 1 2 3 4 5 6 7│ y = ab + ab└┬ - ┬ - ┬ - ┬ - ┬ - ┬ - ┬┘1a, 1b, 2a, 2b gnd 1y 2y8 * 2输入比较器 74ls688_vcc b6 b7 a7, b8 a6 a8 y of b5, a5┌┴-┴-┴-┴-┴-┴-┴-┴-┴-┴┐8×2输入比较器74LS688 │20 19 18 17 16 15 14 13 12 11│)││1 2 3 4 5 6 7 8 9 10│└┬-┬-┬-┬-┬-┬-┬-┬-┬-┬┘A1、B1、A2、B2、B3 CE A3 A4 B4 GND_Y = A1 A2 B1 B2 + +⊙⊙A3⊙B3 + A4⊙B4 + A5⊙B5 + A6 A7B7⊙B6+⊙A8⊙B8页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器3-8译码器74LS138VCC - Y0 Y1 Y2 Y3 -——-——————__ Y4 Y5 Y6 _ _ _ __ _ _ __ _ _ __ _┌┴-┴-┴-┴-┴-┴-┴-┴┐y0 = A B C Y1 Y2 = = B B A B C Y3 = A B C│16 15 14 13 12 11 10 9│)│__ _ _ __ _ __ _ __│1 2 3 4 5 6 7 8│Y4 = A B C A B C Y6 Y5 = =,= A B C A B C└┬-┬-┬-┬-┬-┬-┬-┬┘A B C - CS0 cs1 CS2 Y7 GND双2-4译码器74ls139VCC -2G 2a 2b - Y0 Y1 Y2和Y3 __ -——- __ __ __ __ __ __ __┌┴-┴-┴-┴-┴-┴-┴-┴┐y0 = 2a 2b Y1 Y2 = = 2a 2b 2a 2b y3=2a 2b│16 15 14 13 12 11 10 9│)│__ __ __ __ __ __ __ __│1 2 3 4 5 6 7 8│y0 = 1a 1b Y1 Y2 = = 1A 1B 1a 1b Y3 = 1A 1B└┬-┬-┬-┬-┬-┬-┬-┬┘·- 1 1a 1b - Y0 Y1 Y2 Y3 GND -————8×2输入比较器74LS688_VCC Y B8 A8 A6 A7 B7 B6,B5 A5┌┴-┴-┴-┴-┴-┴-┴-┴-┴-┴┐8×2输入比较器74LS688│20 19 18 17 16 15 14 13 12 11│)││1 2 3 4 5 6 7 8 9 10│└┬-┬-┬-┬-┬-┬-┬-┬-┬-┬┘A1、B1、A2、B2、B3 CE A3 A4 B4 GND_Y = A1 A2 B1 B2 + +⊙⊙A3⊙B3 + A4⊙B4 + A5⊙B5 + A6 A7 B7⊙B6+⊙A8⊙B8寄存器:第二2d VCC 2cr 2ck 2q-2q┌┴-┴-┴-┴-┴-┴-┴┐双D触发器74LS74│14 13 12 11 10 9 8│)││1 2 3 4 5 6 7│└┬-┬-┬-┬-┬-┬-┬┘1cr 1d 1ck第一1q:GNDVCC 8q 8d 7d 7q 6q 6d 5d 5q麦酒┌┴-┴-┴-┴-┴-┴-┴-┴-┴-┴┐位锁存器74LS373 8│20 19 18 17 16 15 14 13 12 11│)││1 2 3 4 5 6 7 8 9 10│└┬-┬-┬-┬-┬-┬-┬-┬-┬-┬┘- OE 1q 1D和2D、3D、4D 2q 3q 4q GND等。

74193中文资料

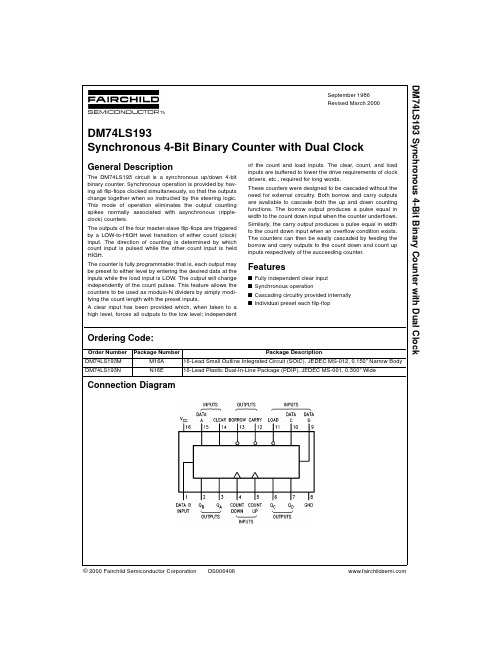

© 2000 Fairchild Semiconductor Corporation DS006406September 1986Revised March 2000DM74LS193 Synchronous 4-Bit Binary Counter with Dual ClockDM74LS193Synchronous 4-Bit Binary Counter with Dual ClockGeneral DescriptionThe DM74LS193 circuit is a synchronous up/down 4-bit binary counter. Synchronous operation is provided by hav-ing all flip-flops clocked simultaneously, so that the outputs change together when so instructed by the steering logic.This mode of operation eliminates the output counting spikes normally associated with asynchronous (ripple-clock) counters.The outputs of the four master-slave flip-flops are triggered by a LOW-to-HIGH level transition of either count (clock)input. The direction of counting is determined by which count input is pulsed while the other count input is held HIGH.The counter is fully programmable; that is, each output may be preset to either level by entering the desired data at the inputs while the load input is LOW. The output will change independently of the count pulses. This feature allows the counters to be used as modulo-N dividers by simply modi-fying the count length with the preset inputs.A clear input has been provided which, when taken to a high level, forces all outputs to the low level; independent of the count and load inputs. The clear, count, and load inputs are buffered to lower the drive requirements of clock drivers, etc., required for long words.These counters were designed to be cascaded without the need for external circuitry. Both borrow and carry outputs are available to cascade both the up and down counting functions. The borrow output produces a pulse equal in width to the count down input when the counter underflows.Similarly, the carry output produces a pulse equal in width to the count down input when an overflow condition exists.The counters can then be easily cascaded by feeding the borrow and carry outputs to the count down and count up inputs respectively of the succeeding counter.Featuress Fully independent clear input s Synchronous operations Cascading circuitry provided internally s Individual preset each flip-flopOrdering Code:Connection DiagramOrder Number Package NumberPackage DescriptionDM74LS193M M16A 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150” Narrow Body DM74LS193NN16E16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300” Wide 2D M 74L S 193Logic Diagram DM74LS193Timing DiagramNote A: Clear overrides load, data, and count inputsNote B: When counting up, count-down input must be HIGH; when counting down, count-up input must be HIGH. 4D M 74L S 193Absolute Maximum Ratings (Note 1)Note 1: The “Absolute Maximum Ratings” are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the Electrical Characteristics tables are not guaranteed at the absolute maximum ratings.The “Recommended Operating Conditions” table will define the conditions for actual device operation.Recommended Operating ConditionsNote 2: C L = 15 pF, R L = 2 k Ω, I A = 25°C and V CC = 5V.Note 3: C L = 50 pF, R L = 2 k Ω, I A = 25°C and V CC = 5V.Note 4: T A = 25°C and V CC = 5V.DC Electrical CharacteristicsNote 5: All typicals are at V CC = 5V, T A = 25°C.Note 6: Not more than one output should be shorted at a time, and the duration should not exceed one second.Note 7: I CC is measured with all outputs open, CLEAR and LOAD inputs grounded, and all other inputs at 4.5V.Operating Free Air Temperature Range −0°C to +70°CSupply Voltage 7V Input Voltage7VStorage Temperature Range−65°C to +125°CSymbol ParameterMin Nom Max Units V CC Supply Voltage4.7555.25V V IH HIGH Level Input Voltage 2V V IL LOW Level Input Voltage 0.8V I OH HIGH Level Output Current −0.4mA I OL LOW Level Output Current 8mA f CLK Clock Frequency (Note 2)025MHz Clock Frequency (Note 3)t W Pulse Width of any Input (Note 4)20ns t SU Data Setup Time (Note 4)20ns t H Data Hold Time (Note 4)0ns t EN Enable Time to Clock (Note 4)40ns T AFree Air Operating Temperature70°CSymbol ParameterConditionsMin Typ Max Units (Note 5)V I Input Clamp Voltage V CC = Min, I I = −18 mA −1.5V V OH HIGH Level Output V CC =Min,I OH =Max 2.5 3.4VVoltageV IL = Max, V IH = Min 2.73.4V OLLOW Level Output V CC =Min,I OL =Max 0.250.4VoltageV IL = Max, V IH = Min 0.350.5V I OL =4mA,V CC =Min 0.250.4I I Input Current @ Max Input Voltage V CC = Max, V I = 7V 0.1mA I IH HIGH Level Input Current V CC = Max, V I = 2.7V 20µA I IL LOW Level Input Current V CC = Max, V I = 0.4V −0.4mA I OS Short Circuit V CC = Max −20−100mA Output Current (Note 6)−20−100I CCSupply CurrentV CC = Max (Note 7)1934mADM74LS193 AC Electrical CharacteristicsFrom (Input)R L= 2 kΩSymbol Parameter To (Output)C L= 15 pF C L= 50 pF UnitsMin Max Min Maxf MAX Maximum Clock Frequency2520MHzt PLH Propagation Delay Time Count Up2630ns LOW-to-HIGH Level Output to Carryt PHL Propagation Delay Time Count Up2436ns HIGH-to-LOW Level Output to Carryt PLH Propagation Delay Time Count Down2429ns LOW-to-HIGH Level Output to Borrowt PHL Propagation Delay Time Count Down2432ns HIGH-to-LOW Level Output to Borrowt PLH Propagation Delay Time Either Count3845ns LOW-to-HIGH Level Output to Any Qt PHL Propagation Delay Time Either Count4754ns HIGH-to-LOW Level Output to Any Qt PLH Propagation Delay Time Load to4041ns LOW-to-HIGH Level Output Any Qt PHL Propagation Delay Time Load to4047ns HIGH-to-LOW Level Output Any Qt PHL Propagation Delay Time Clear to3544ns HIGH-to-LOW Level Output Any Q 6D M 74L S 193Physical Dimensionsinches (millimeters) unless otherwise noted16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0150” Narrow BodyPackage Number M16APhysical Dimensions inches (millimeters) unless otherwise noted (Continued)16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300” WidePackage Number N16EFairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.LIFE SUPPORT POLICYFAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:1.Life support devices or systems are devices or systemswhich, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be rea-sonably expected to result in a significant injury to the user.2. A critical component in any component of a life supportdevice or system whose failure to perform can be rea-sonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness. DM74LS193 Synchronous 4-Bit Binary Counter with Dual Clock。

74LS系列芯片引脚图资料大全

74系列芯片引脚图资料大全作者:佚名来源:本站原创点击数:57276 更新时间:2007年07月26日【字体:大中小】为了方便大家我收集了下列74系列芯片的引脚图资料,如还有需要请上电子论坛/b bs/反相器驱动器LS04 LS05 LS06 LS07 LS125 LS240 LS244 LS245与门与非门LS00 LS08 LS10 LS11 LS20 LS21 LS27 LS30 LS38或门或非门与或非门LS02 LS32 LS51 LS64 LS65异或门比较器LS86译码器LS138 LS139寄存器LS74 LS175 LS373反相器:Vcc 6A 6Y 5A 5Y 4A 4Y 六非门 74LS04┌┴—┴—┴—┴—┴—┴—┴┐六非门(OC门) 74LS05_ │14 13 12 11 10 9 8│六非门(OC高压输出) 74LS06 Y = A )││ 1 2 3 4 5 6 7│└┬—┬—┬—┬—┬—┬—┬┘1A 1Y 2A 2Y 3A 3Y GND驱动器:Vcc 6A 6Y 5A 5Y 4A 4Y┌┴—┴—┴—┴—┴—┴—┴┐│14 13 12 11 10 9 8│Y = A )│六驱动器(OC高压输出) 74LS07 │ 1 2 3 4 5 6 7│└┬—┬—┬—┬—┬—┬—┬┘1A 1Y 2A 2Y 3A 3Y GNDVcc -4C 4A 4Y -3C 3A 3Y┌┴—┴—┴—┴—┴—┴—┴┐_ │14 13 12 11 10 9 8│Y =A+C )│四总线三态门74LS125 │ 1 2 3 4 5 6 7│└┬—┬—┬—┬—┬—┬—┬┘-1C 1A 1Y -2C 2A 2Y GNDVcc -G B1 B2 B3 B4 B8 B6 B7 B8┌┴—┴—┴—┴—┴—┴—┴—┴—┴—┴┐ 8位总线驱动器74LS245│20 19 18 17 16 15 14 13 12 11│)│ DIR=1 A=>B│ 1 2 3 4 5 6 7 8 9 10│ DIR=0 B=>A└┬—┬—┬—┬—┬—┬—┬—┬—┬—┬┘DIR A1 A2 A3 A4 A5 A6 A7 A8 GND页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器正逻辑与门,与非门:Vcc 4B 4A 4Y 3B 3A 3Y┌┴—┴—┴—┴—┴—┴—┴┐│14 13 12 11 10 9 8│Y = AB )│ 2输入四正与门74LS08│1 2 3 4 5 6 7│└┬—┬—┬—┬—┬—┬—┬┘1A 1B 1Y 2A 2B 2Y GNDVcc 4B 4A 4Y 3B 3A 3Y┌┴—┴—┴—┴—┴—┴—┴┐__ │14 13 12 11 10 9 8│Y = AB )│ 2输入四正与非门74LS00│ 1 2 3 4 5 6 7│└┬—┬—┬—┬—┬—┬—┬┘1A 1B 1Y 2A 2B 2Y GNDVcc 1C 1Y 3C 3B 3A 3Y┌┴—┴—┴—┴—┴—┴—┴┐___ │14 13 12 11 10 9 8│Y = ABC )│ 3输入三正与非门74LS10│ 1 2 3 4 5 6 7│└┬—┬—┬—┬—┬—┬—┬┘1A 1B 2A 2B 2C 2Y GNDVcc H G Y┌┴—┴—┴—┴—┴—┴—┴┐│14 13 12 11 10 9 8│)│ 8输入与非门74LS30│ 1 2 3 4 5 6 7│ ________└┬—┬—┬—┬—┬—┬—┬┘ Y = ABCDEFGHA B C D E F GND页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器正逻辑或门,或非门:Vcc 4B 4A 4Y 3B 3A 3Y┌┴—┴—┴—┴—┴—┴—┴┐ 2输入四或门74LS32│14 13 12 11 10 9 8│)│ Y = A+B│ 1 2 3 4 5 6 7│└┬—┬—┬—┬—┬—┬—┬┘1A 1B 1Y 2A 2B 2Y GNDVcc 4Y 4B 4A 3Y 3B 3A┌┴—┴—┴—┴—┴—┴—┴┐ 2输入四或非门74LS02│14 13 12 11 10 9 8│___)│Y = A+B│ 1 2 3 4 5 6 7│└┬—┬—┬—┬—┬—┬—┬┘1Y 1A 1B 2Y 2A 2B GNDVcc 2Y 2B 2A 2D 2E 1F┌┴—┴—┴—┴—┴—┴—┴┐双与或非门74S51│14 13 12 11 10 9 8│_____)│ 2Y = AB+DE│ 1 2 3 4 5 6 7│_______└┬—┬—┬—┬—┬—┬—┬┘ 1Y = ABC+DEF1Y 1A 1B 1C 1D 1E GNDVcc D C B K J Y┌┴—┴—┴—┴—┴—┴—┴┐ 4-2-3-2与或非门74S64 74S65(OC门)│14 13 12 11 10 9 8│ ______________)│ Y = ABCD+EF+GHI+JK│ 1 2 3 4 5 6 7│└┬—┬—┬—┬—┬—┬—┬┘A E F G H I GND页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器2输入四异或门74LS86Vcc 4B 4A 4Y 3Y 3B 3A┌┴—┴—┴—┴—┴—┴—┴┐│14 13 12 11 10 9 8│)│ _ _│ 1 2 3 4 5 6 7│ Y=AB+AB└┬—┬—┬—┬—┬—┬—┬┘1A 1B 1Y 2Y 2A 2B GND8*2输入比较器74LS688_Vcc Y B8 A8 B7 A7 B6 A6 B5 A5┌┴—┴—┴—┴—┴—┴—┴—┴—┴—┴┐ 8*2输入比较器74LS688│20 19 18 17 16 15 14 13 12 11│)││ 1 2 3 4 5 6 7 8 9 10│└┬—┬—┬—┬—┬—┬—┬—┬—┬—┬┘CE A1 B1 A2 B2 A3 B3 A4 B4 GND_Y=A1⊙B1+A2⊙B2+A3⊙B3+A4⊙B4+A5⊙B5+A6⊙B6+A7⊙B7+A8⊙B8页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器3-8译码器74LS138Vcc -Y0 -Y1 -Y2 -Y3 -Y4 -Y5 -Y6 __ _ _ _ __ _ _ __ _ _ __ _┌┴—┴—┴—┴—┴—┴—┴—┴┐ Y0=A B C Y1=A B B Y2=A B C Y3=A B C │16 15 14 13 12 11 10 9 │)│ __ _ _ __ _ __ _ __│ 1 2 3 4 5 6 7 8│ Y4=A B C Y5=A B C Y6=A B C Y7=A B C └┬—┬—┬—┬—┬—┬—┬—┬┘A B C -CS0 -CS1 CS2 -Y7 GND双2-4译码器74LS139Vcc -2G 2A 2B -Y0 -Y1 -Y2 -Y3 __ __ __ __ __ __ __ __┌┴—┴—┴—┴—┴—┴—┴—┴┐ Y0=2A 2B Y1=2A 2B Y2=2A 2B Y3=2A 2B │16 15 14 13 12 11 10 9 │)│ __ __ __ __ __ __ __ __│ 1 2 3 4 5 6 7 8│ Y0=1A 1B Y1=1A 1B Y2=1A 1B Y3=1A 1B └┬—┬—┬—┬—┬—┬—┬—┬┘-1G 1A 1B -Y0 -Y1 -Y2 -Y3 GND8*2输入比较器74LS688_Vcc Y B8 A8 B7 A7 B6 A6 B5 A5┌┴—┴—┴—┴—┴—┴—┴—┴—┴—┴┐ 8*2输入比较器74LS688│20 19 18 17 16 15 14 13 12 11│)││ 1 2 3 4 5 6 7 8 9 10│└┬—┬—┬—┬—┬—┬—┬—┬—┬—┬┘CE A1 B1 A2 B2 A3 B3 A4 B4 GND_Y=A1⊙B1+A2⊙B2+A3⊙B3+A4⊙B4+A5⊙B5+A6⊙B6+A7⊙B7+A8⊙B8寄存器:Vcc 2CR 2D 2Ck 2St 2Q -2Q┌┴—┴—┴—┴—┴—┴—┴┐双D触发器74LS74│14 13 12 11 10 9 8 │)││ 1 2 3 4 5 6 7│└┬—┬—┬—┬—┬—┬—┬┘1Cr 1D 1Ck 1St 1Q -1Q GNDVcc 8Q 8D 7D 7Q 6Q 6D 5D 5Q ALE┌┴—┴—┴—┴—┴—┴—┴—┴—┴—┴┐ 8位锁存器74LS373 │20 19 18 17 16 15 14 13 12 11│)││ 1 2 3 4 5 6 7 8 9 10│└┬—┬—┬—┬—┬—┬—┬—┬—┬—┬┘-OE 1Q 1D 2D 2Q 3Q 3D 4D 4Q GND等.下面介绍一下常用的74芯片,以便大家在电路中遇到了查询----------------------------------------------------型号内容----------------------------------------------------74ls00 2输入四与非门74ls01 2输入四与非门(oc)74ls02 2输入四或非门74ls03 2输入四与非门(oc)74ls04 六倒相器74ls05 六倒相器(oc)74ls06 六高压输出反相缓冲器/驱动器(oc,30v) 74ls07 六高压输出缓冲器/驱动器(oc,30v)74ls08 2输入四与门74ls09 2输入四与门(oc)74ls10 3输入三与非门74ls11 3输入三与门74ls12 3输入三与非门(oc)74ls13 4输入双与非门(斯密特触发)74ls14 六倒相器(斯密特触发)74ls15 3输入三与门(oc)74ls16 六高压输出反相缓冲器/驱动器(oc,15v) 74ls17 六高压输出缓冲器/驱动器(oc,15v)74ls18 4输入双与非门(斯密特触发)74ls19 六倒相器(斯密特触发)74ls20 4输入双与非门74ls21 4输入双与门74ls22 4输入双与非门(oc)74ls23 双可扩展的输入或非门74ls24 2输入四与非门(斯密特触发)74ls25 4输入双或非门(有选通)74ls26 2输入四高电平接口与非缓冲器(oc,15v) 74ls27 3输入三或非门74ls28 2输入四或非缓冲器74ls30 8输入与非门74ls31 延迟电路74ls32 2输入四或门74ls33 2输入四或非缓冲器(集电极开路输出) 74ls34 六缓冲器74ls35 六缓冲器(oc)74ls36 2输入四或非门(有选通)74ls37 2输入四与非缓冲器74ls38 2输入四或非缓冲器(集电极开路输出) 74ls39 2输入四或非缓冲器(集电极开路输出) 74ls40 4输入双与非缓冲器74ls41 bcd-十进制计数器74ls42 4线-10线译码器(bcd输入)74ls43 4线-10线译码器(余3码输入)74ls44 4线-10线译码器(余3葛莱码输入)74ls45 bcd-十进制译码器/驱动器74ls46 bcd-七段译码器/驱动器74ls47 bcd-七段译码器/驱动器74ls48 bcd-七段译码器/驱动器74ls49 bcd-七段译码器/驱动器(oc)74ls50 双二路2-2输入与或非门(一门可扩展) 74ls51 双二路2-2输入与或非门74ls51 二路3-3输入,二路2-2输入与或非门74ls52 四路2-3-2-2输入与或门(可扩展)74ls53 四路2-2-2-2输入与或非门(可扩展) 74ls53 四路2-2-3-2输入与或非门(可扩展) 74ls54 四路2-2-2-2输入与或非门74ls54 四路2-3-3-2输入与或非门74ls54 四路2-2-3-2输入与或非门74ls55 二路4-4输入与或非门(可扩展)74ls60 双四输入与扩展74ls61 三3输入与扩展74ls62 四路2-3-3-2输入与或扩展器74ls63 六电流读出接口门74ls64 四路4-2-3-2输入与或非门74ls65 四路4-2-3-2输入与或非门(oc)74ls70 与门输入上升沿jk触发器74ls71 与输入r-s主从触发器74ls72 与门输入主从jk触发器74ls73 双j-k触发器(带清除端)74ls74 正沿触发双d型触发器(带预置端和清除端)74ls75 4位双稳锁存器74ls76 双j-k触发器(带预置端和清除端)74ls77 4位双稳态锁存器74ls78 双j-k触发器(带预置端,公共清除端和公共时钟端) 74ls80 门控全加器74ls81 16位随机存取存储器74ls82 2位二进制全加器(快速进位)74ls83 4位二进制全加器(快速进位)74ls84 16位随机存取存储器74ls85 4位数字比较器74ls86 2输入四异或门74ls87 四位二进制原码/反码/oi单元74ls89 64位读/写存储器74ls90 十进制计数器74ls91 八位移位寄存器74ls92 12分频计数器(2分频和6分频)74ls93 4位二进制计数器74ls94 4位移位寄存器(异步)74ls95 4位移位寄存器(并行io)74ls96 5位移位寄存器74ls97 六位同步二进制比率乘法器74ls100 八位双稳锁存器74ls103 负沿触发双j-k主从触发器(带清除端)74ls106 负沿触发双j-k主从触发器(带预置,清除,时钟) 74ls107 双j-k主从触发器(带清除端)74ls108 双j-k主从触发器(带预置,清除,时钟)74ls109 双j-k触发器(带置位,清除,正触发)74ls110 与门输入j-k主从触发器(带锁定)74ls111 双j-k主从触发器(带数据锁定)74ls112 负沿触发双j-k触发器(带预置端和清除端)74ls113 负沿触发双j-k触发器(带预置端)74ls114 双j-k触发器(带预置端,共清除端和时钟端) 74ls116 双四位锁存器74ls120 双脉冲同步器/驱动器74ls121 单稳态触发器(施密特触发)74ls122 可再触发单稳态多谐振荡器(带清除端)74ls123 可再触发双单稳多谐振荡器74ls125 四总线缓冲门(三态输出)74ls126 四总线缓冲门(三态输出)74ls128 2输入四或非线驱动器74ls131 3-8译码器74ls132 2输入四与非门(斯密特触发)74ls133 13输入端与非门74ls134 12输入端与门(三态输出)74ls135 四异或/异或非门74ls136 2输入四异或门(oc)74ls137 八选1锁存译码器/多路转换器74ls138 3-8线译码器/多路转换器74ls139 双2-4线译码器/多路转换器74ls140 双4输入与非线驱动器74ls141 bcd-十进制译码器/驱动器74ls142 计数器/锁存器/译码器/驱动器74ls145 4-10译码器/驱动器74ls147 10线-4线优先编码器74ls148 8线-3线八进制优先编码器74ls150 16选1数据选择器(反补输出)74ls151 8选1数据选择器(互补输出)74ls152 8选1数据选择器多路开关74ls153 双4选1数据选择器/多路选择器74ls154 4线-16线译码器74ls155 双2-4译码器/分配器(图腾柱输出)74ls156 双2-4译码器/分配器(集电极开路输出) 74ls157 四2选1数据选择器/多路选择器74ls158 四2选1数据选择器(反相输出)74ls160 可预置bcd计数器(异步清除)74ls161 可预置四位二进制计数器(并清除异步) 74ls162 可预置bcd计数器(异步清除)74ls163 可预置四位二进制计数器(并清除异步) 74ls164 8位并行输出串行移位寄存器74ls165 并行输入8位移位寄存器(补码输出)74ls166 8位移位寄存器74ls167 同步十进制比率乘法器74ls168 4位加/减同步计数器(十进制)74ls169 同步二进制可逆计数器74ls170 4*4寄存器堆74ls171 四d触发器(带清除端)74ls172 16位寄存器堆74ls173 4位d型寄存器(带清除端)74ls174 六d触发器74ls175 四d触发器74ls176 十进制可预置计数器74ls177 2-8-16进制可预置计数器74ls178 四位通用移位寄存器74ls179 四位通用移位寄存器74ls180 九位奇偶产生/校验器74ls181 算术逻辑单元/功能发生器74ls182 先行进位发生器74ls183 双保留进位全加器74ls184 bcd-二进制转换器74ls185 二进制-bcd转换器74ls190 同步可逆计数器(bcd,二进制) 74ls191 同步可逆计数器(bcd,二进制) 74ls192 同步可逆计数器(bcd,二进制) 74ls193 同步可逆计数器(bcd,二进制) 74ls194 四位双向通用移位寄存器74ls195 四位通用移位寄存器74ls196 可预置计数器/锁存器74ls197 可预置计数器/锁存器(二进制) 74ls198 八位双向移位寄存器74ls199 八位移位寄存器74ls210 2-5-10进制计数器74ls213 2-n-10可变进制计数器74ls221 双单稳触发器74ls230 八3态总线驱动器74ls231 八3态总线反向驱动器74ls240 八缓冲器/线驱动器/线接收器(反码三态输出) 74ls241 八缓冲器/线驱动器/线接收器(原码三态输出) 74ls242 八缓冲器/线驱动器/线接收器74ls243 4同相三态总线收发器74ls244 八缓冲器/线驱动器/线接收器74ls245 八双向总线收发器74ls246 4线-七段译码/驱动器(30v)74ls247 4线-七段译码/驱动器(15v)74ls248 4线-七段译码/驱动器74ls249 4线-七段译码/驱动器74ls251 8选1数据选择器(三态输出)74ls253 双四选1数据选择器(三态输出)74ls256 双四位可寻址锁存器74ls257 四2选1数据选择器(三态输出)74ls258 四2选1数据选择器(反码三态输出)74ls259 8为可寻址锁存器74ls260 双5输入或非门74ls261 4*2并行二进制乘法器74ls265 四互补输出元件74ls266 2输入四异或非门(oc)74ls270 2048位rom (512位四字节,oc)74ls271 2048位rom (256位八字节,oc)74ls273 八d触发器74ls274 4*4并行二进制乘法器74ls275 七位片式华莱士树乘法器74ls276 四jk触发器74ls278 四位可级联优先寄存器74ls279 四s-r锁存器74ls280 9位奇数/偶数奇偶发生器/较验器74ls28174ls283 4位二进制全加器74ls290 十进制计数器74ls291 32位可编程模74ls293 4位二进制计数器74ls294 16位可编程模74ls295 四位双向通用移位寄存器74ls298 四-2输入多路转换器(带选通)74ls299 八位通用移位寄存器(三态输出)74ls348 8-3线优先编码器(三态输出)74ls352 双四选1数据选择器/多路转换器74ls353 双4-1线数据选择器(三态输出)74ls354 8输入端多路转换器/数据选择器/寄存器,三态补码输出74ls355 8输入端多路转换器/数据选择器/寄存器,三态补码输出74ls356 8输入端多路转换器/数据选择器/寄存器,三态补码输出74ls357 8输入端多路转换器/数据选择器/寄存器,三态补码输出74ls365 6总线驱动器74ls366 六反向三态缓冲器/线驱动器74ls367 六同向三态缓冲器/线驱动器74ls368 六反向三态缓冲器/线驱动器74ls373 八d锁存器74ls374 八d触发器(三态同相)74ls375 4位双稳态锁存器74ls377 带使能的八d触发器74ls378 六d触发器74ls379 四d触发器74ls381 算术逻辑单元/函数发生器74ls382 算术逻辑单元/函数发生器74ls384 8位*1位补码乘法器74ls385 四串行加法器/乘法器74ls386 2输入四异或门74ls390 双十进制计数器74ls391 双四位二进制计数器74ls395 4位通用移位寄存器74ls396 八位存储寄存器74ls398 四2输入端多路开关(双路输出) 74ls399 四-2输入多路转换器(带选通)74ls422 单稳态触发器74ls423 双单稳态触发器74ls440 四3方向总线收发器,集电极开路74ls441 四3方向总线收发器,集电极开路74ls442 四3方向总线收发器,三态输出74ls443 四3方向总线收发器,三态输出74ls444 四3方向总线收发器,三态输出74ls445 bcd-十进制译码器/驱动器,三态输出74ls446 有方向控制的双总线收发器74ls448 四3方向总线收发器,三态输出74ls449 有方向控制的双总线收发器74ls465 八三态线缓冲器74ls466 八三态线反向缓冲器74ls467 八三态线缓冲器74ls468 八三态线反向缓冲器74ls490 双十进制计数器74ls540 八位三态总线缓冲器(反向)74ls541 八位三态总线缓冲器74ls589 有输入锁存的并入串出移位寄存器74ls590 带输出寄存器的8位二进制计数器74ls591 带输出寄存器的8位二进制计数器74ls592 带输出寄存器的8位二进制计数器74ls593 带输出寄存器的8位二进制计数器74ls594 带输出锁存的8位串入并出移位寄存器74ls595 8位输出锁存移位寄存器74ls596 带输出锁存的8位串入并出移位寄存器74ls597 8位输出锁存移位寄存器74ls598 带输入锁存的并入串出移位寄存器74ls599 带输出锁存的8位串入并出移位寄存器74ls604 双8位锁存器74ls605 双8位锁存器74ls606 双8位锁存器74ls607 双8位锁存器74ls620 8位三态总线发送接收器(反相)74ls621 8位总线收发器74ls622 8位总线收发器74ls623 8位总线收发器74ls640 反相总线收发器(三态输出)74ls641 同相8总线收发器,集电极开路74ls642 同相8总线收发器,集电极开路74ls643 8位三态总线发送接收器74ls644 真值反相8总线收发器,集电极开路74ls645 三态同相8总线收发器74ls646 八位总线收发器,寄存器74ls647 八位总线收发器,寄存器74ls648 八位总线收发器,寄存器74ls649 八位总线收发器,寄存器74ls651 三态反相8总线收发器74ls652 三态反相8总线收发器74ls653 反相8总线收发器,集电极开路74ls654 同相8总线收发器,集电极开路74ls668 4位同步加/减十进制计数器74ls669 带先行进位的4位同步二进制可逆计数器74ls670 4*4寄存器堆(三态)74ls671 带输出寄存的四位并入并出移位寄存器74ls672 带输出寄存的四位并入并出移位寄存器74ls673 16位并行输出存储器,16位串入串出移位寄存器74ls674 16位并行输入串行输出移位寄存器74ls681 4位并行二进制累加器74ls682 8位数值比较器(图腾柱输出)74ls683 8位数值比较器(集电极开路)74ls684 8位数值比较器(图腾柱输出)74ls685 8位数值比较器(集电极开路)74ls686 8位数值比较器(图腾柱输出)74ls687 8位数值比较器(集电极开路)74ls688 8位数字比较器(oc输出)74ls689 8位数字比较器74ls690 同步十进制计数器/寄存器(带数选,三态输出,直接清除)74ls691 计数器/寄存器(带多转换,三态输出)74ls692 同步十进制计数器(带预置输入,同步清除)74ls693 计数器/寄存器(带多转换,三态输出)74ls696 同步加/减十进制计数器/寄存器(带数选,三态输出,直接清除) 74ls697 计数器/寄存器(带多转换,三态输出)74ls698 计数器/寄存器(带多转换,三态输出)74ls699 计数器/寄存器(带多转换,三态输出)74ls716 可编程模n十进制计数器74ls718 可编程模n十进制计数器【发表评论】【告诉好友】【收藏此文】【关闭窗口】上一篇:74LS74引脚图(双D触发器)下一篇:DAC0832引脚图及接口电路。

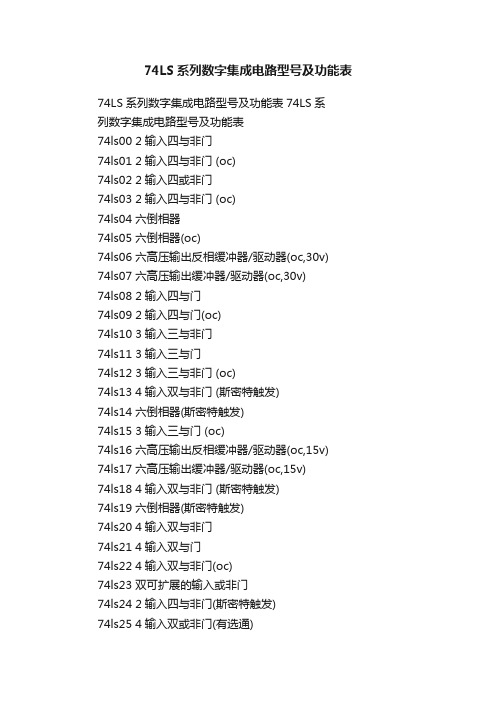

74LS系列数字集成电路型号及功能表

74LS系列数字集成电路型号及功能表74LS系列数字集成电路型号及功能表74LS系列数字集成电路型号及功能表74ls00 2输入四与非门74ls01 2输入四与非门 (oc)74ls02 2输入四或非门74ls03 2输入四与非门 (oc)74ls04 六倒相器74ls05 六倒相器(oc)74ls06 六高压输出反相缓冲器/驱动器(oc,30v) 74ls07 六高压输出缓冲器/驱动器(oc,30v)74ls08 2输入四与门74ls09 2输入四与门(oc)74ls10 3输入三与非门74ls11 3输入三与门74ls12 3输入三与非门 (oc)74ls13 4输入双与非门 (斯密特触发)74ls14 六倒相器(斯密特触发)74ls15 3输入三与门 (oc)74ls16 六高压输出反相缓冲器/驱动器(oc,15v) 74ls17 六高压输出缓冲器/驱动器(oc,15v)74ls18 4输入双与非门 (斯密特触发)74ls19 六倒相器(斯密特触发)74ls20 4输入双与非门74ls21 4输入双与门74ls22 4输入双与非门(oc)74ls23 双可扩展的输入或非门74ls24 2输入四与非门(斯密特触发)74ls25 4输入双或非门(有选通)74ls26 2输入四高电平接口与非缓冲器(oc,15v) 74ls27 3输入三或非门74ls28 2输入四或非缓冲器74ls30 8输入与非门74ls31 延迟电路74ls32 2输入四或门74ls33 2输入四或非缓冲器(集电极开路输出) 74ls34 六缓冲器74ls35 六缓冲器(oc)74ls36 2输入四或非门(有选通)74ls37 2输入四与非缓冲器74ls38 2输入四或非缓冲器(集电极开路输出) 74ls39 2输入四或非缓冲器(集电极开路输出) 74ls40 4输入双与非缓冲器74ls41 bcd-十进制计数器74ls42 4线-10线译码器(bcd输入)74ls43 4线-10线译码器(余3码输入)74ls44 4线-10线译码器(余3葛莱码输入)74ls45 bcd-十进制译码器/驱动器74ls46 bcd-七段译码器/驱动器74ls47 bcd-七段译码器/驱动器74ls48 bcd-七段译码器/驱动器74ls49 bcd-七段译码器/驱动器(oc)74ls50 双二路2-2输入与或非门(一门可扩展) 74ls51 双二路2-2输入与或非门74ls51 二路3-3输入,二路2-2输入与或非门74ls52 四路2-3-2-2输入与或门(可扩展)74ls53 四路2-2-2-2输入与或非门(可扩展) 74ls53 四路2-2-3-2输入与或非门(可扩展) 74ls54 四路2-2-2-2输入与或非门74ls54 四路2-3-3-2输入与或非门74ls54 四路2-2-3-2输入与或非门74ls55 二路4-4输入与或非门(可扩展)74ls60 双四输入与扩展74ls61 三3输入与扩展74ls62 四路2-3-3-2输入与或扩展器74ls63 六电流读出接口门74ls64 四路4-2-3-2输入与或非门74ls65 四路4-2-3-2输入与或非门(oc)74ls70 与门输入上升沿jk触发器74ls71 与输入r-s主从触发器74ls72 与门输入主从jk触发器74ls73 双j-k触发器(带清除端)74ls74 正沿触发双d型触发器(带预置端和清除端)74ls75 4位双稳锁存器74ls76 双j-k触发器(带预置端和清除端)74ls77 4位双稳态锁存器74ls78 双j-k触发器(带预置端,公共清除端和公共时钟端) 74ls80 门控全加器74ls81 16位随机存取存储器74ls82 2位二进制全加器(快速进位)74ls83 4位二进制全加器(快速进位)74ls84 16位随机存取存储器74ls85 4位数字比较器74ls86 2输入四异或门74ls87 四位二进制原码/反码/oi单元74ls89 64位读/写存储器74ls90 十进制计数器74ls91 八位移位寄存器74ls92 12分频计数器(2分频和6分频)74ls93 4位二进制计数器74ls94 4位移位寄存器(异步)74ls95 4位移位寄存器(并行io)74ls96 5位移位寄存器74ls97 六位同步二进制比率乘法器74ls100 八位双稳锁存器74ls103 负沿触发双j-k主从触发器(带清除端)74ls106 负沿触发双j-k主从触发器(带预置,清除,时钟) 74ls107 双j-k主从触发器(带清除端)74ls108 双j-k主从触发器(带预置,清除,时钟)74ls109 双j-k触发器(带置位,清除,正触发)74ls110 与门输入j-k主从触发器(带锁定)74ls111 双j-k主从触发器(带数据锁定)74ls112 负沿触发双j-k触发器(带预置端和清除端)74ls113 负沿触发双j-k触发器(带预置端)74ls114 双j-k触发器(带预置端,共清除端和时钟端)74ls116 双四位锁存器74ls120 双脉冲同步器/驱动器74ls121 单稳态触发器(施密特触发)74ls122 可再触发单稳态多谐振荡器(带清除端)74ls123 可再触发双单稳多谐振荡器74ls125 四总线缓冲门(三态输出)74ls126 四总线缓冲门(三态输出)74ls128 2输入四或非线驱动器74ls131 3-8译码器74ls132 2输入四与非门(斯密特触发)74ls133 13输入端与非门74ls134 12输入端与门(三态输出)74ls135 四异或/异或非门74ls136 2输入四异或门(oc)74ls137 八选1锁存译码器/多路转换器74ls138 3-8线译码器/多路转换器74ls139 双2-4线译码器/多路转换器74ls140 双4输入与非线驱动器74ls141 bcd-十进制译码器/驱动器74ls142 计数器/锁存器/译码器/驱动器74ls145 4-10译码器/驱动器74ls147 10线-4线优先编码器74ls148 8线-3线八进制优先编码器74ls150 16选1数据选择器(反补输出)74ls151 8选1数据选择器(互补输出)74ls152 8选1数据选择器多路开关74ls153 双4选1数据选择器/多路选择器74ls154 4线-16线译码器74ls155 双2-4译码器/分配器(图腾柱输出)74ls156 双2-4译码器/分配器(集电极开路输出) 74ls157 四2选1数据选择器/多路选择器74ls158 四2选1数据选择器(反相输出)74ls160 可预置bcd计数器(异步清除)74ls161 可预置四位二进制计数器(并清除异步) 74ls162 可预置bcd计数器(异步清除)74ls163 可预置四位二进制计数器(并清除异步) 74ls164 8位并行输出串行移位寄存器74ls165 并行输入8位移位寄存器(补码输出)74ls166 8位移位寄存器74ls167 同步十进制比率乘法器74ls168 4位加/减同步计数器(十进制)74ls169 同步二进制可逆计数器74ls170 4*4寄存器堆74ls171 四d触发器(带清除端)74ls172 16位寄存器堆74ls173 4位d型寄存器(带清除端)74ls174 六d触发器74ls175 四d触发器74ls176 十进制可预置计数器74ls177 2-8-16进制可预置计数器74ls178 四位通用移位寄存器74ls179 四位通用移位寄存器74ls180 九位奇偶产生/校验器74ls181 算术逻辑单元/功能发生器74ls182 先行进位发生器74ls183 双保留进位全加器74ls184 bcd-二进制转换器74ls185 二进制-bcd转换器74ls190 同步可逆计数器(bcd,二进制)74ls191 同步可逆计数器(bcd,二进制)74ls192 同步可逆计数器(bcd,二进制)74ls193 同步可逆计数器(bcd,二进制)74ls194 四位双向通用移位寄存器74ls195 四位通用移位寄存器74ls196 可预置计数器/锁存器74ls197 可预置计数器/锁存器(二进制)74ls198 八位双向移位寄存器74ls199 八位移位寄存器74ls210 2-5-10进制计数器74ls213 2-n-10可变进制计数器74ls221 双单稳触发器74ls230 八3态总线驱动器74ls231 八3态总线反向驱动器74ls240 八缓冲器/线驱动器/线接收器(反码三态输出) 74ls241 八缓冲器/线驱动器/线接收器(原码三态输出) 74ls242 八缓冲器/线驱动器/线接收器74ls243 4同相三态总线收发器74ls244 八缓冲器/线驱动器/线接收器74ls245 八双向总线收发器74ls246 4线-七段译码/驱动器(30v)74ls247 4线-七段译码/驱动器(15v)74ls248 4线-七段译码/驱动器74ls249 4线-七段译码/驱动器74ls251 8选1数据选择器(三态输出)74ls253 双四选1数据选择器(三态输出)74ls256 双四位可寻址锁存器74ls257 四2选1数据选择器(三态输出)74ls258 四2选1数据选择器(反码三态输出)74ls259 8为可寻址锁存器74ls260 双5输入或非门74ls261 4*2并行二进制乘法器74ls265 四互补输出元件74ls266 2输入四异或非门(oc)74ls270 2048位rom (512位四字节,oc)74ls271 2048位rom (256位八字节,oc)74ls273 八d触发器74ls274 4*4并行二进制乘法器74ls275 七位片式华莱士树乘法器74ls276 四jk触发器74ls278 四位可级联优先寄存器74ls279 四s-r锁存器74ls280 9位奇数/偶数奇偶发生器/较验器74ls28174ls283 4位二进制全加器74ls290 十进制计数器74ls291 32位可编程模74ls293 4位二进制计数器74ls294 16位可编程模74ls295 四位双向通用移位寄存器74ls298 四-2输入多路转换器(带选通)74ls299 八位通用移位寄存器(三态输出)74ls348 8-3线优先编码器(三态输出)74ls352 双四选1数据选择器/多路转换器74ls353 双4-1线数据选择器(三态输出)74ls354 8输入端多路转换器/数据选择器/寄存器,三态补码输出74ls355 8输入端多路转换器/数据选择器/寄存器,三态补码输出74ls356 8输入端多路转换器/数据选择器/寄存器,三态补码输出74ls357 8输入端多路转换器/数据选择器/寄存器,三态补码输出74ls365 6总线驱动器74ls366 六反向三态缓冲器/线驱动器74ls367 六同向三态缓冲器/线驱动器74ls368 六反向三态缓冲器/线驱动器74ls373 八d锁存器74ls374 八d触发器(三态同相)74ls375 4位双稳态锁存器74ls377 带使能的八d触发器74ls378 六d触发器74ls379 四d触发器74ls381 算术逻辑单元/函数发生器74ls382 算术逻辑单元/函数发生器74ls384 8位*1位补码乘法器74ls385 四串行加法器/乘法器74ls386 2输入四异或门74ls390 双十进制计数器74ls391 双四位二进制计数器74ls395 4位通用移位寄存器74ls396 八位存储寄存器74ls398 四2输入端多路开关(双路输出)74ls399 四-2输入多路转换器(带选通)74ls422 单稳态触发器74ls423 双单稳态触发器74ls440 四3方向总线收发器,集电极开路74ls441 四3方向总线收发器,集电极开路74ls442 四3方向总线收发器,三态输出74ls443 四3方向总线收发器,三态输出74ls444 四3方向总线收发器,三态输出74ls445 bcd-十进制译码器/驱动器,三态输出74ls446 有方向控制的双总线收发器74ls448 四3方向总线收发器,三态输出74ls449 有方向控制的双总线收发器74ls465 八三态线缓冲器74ls466 八三态线反向缓冲器74ls467 八三态线缓冲器74ls468 八三态线反向缓冲器74ls490 双十进制计数器74ls540 八位三态总线缓冲器(反向)74ls541 八位三态总线缓冲器74ls589 有输入锁存的并入串出移位寄存器74ls590 带输出寄存器的8位二进制计数器74ls591 带输出寄存器的8位二进制计数器74ls592 带输出寄存器的8位二进制计数器74ls593 带输出寄存器的8位二进制计数器74ls594 带输出锁存的8位串入并出移位寄存器74ls595 8位输出锁存移位寄存器74ls596 带输出锁存的8位串入并出移位寄存器74ls597 8位输出锁存移位寄存器74ls598 带输入锁存的并入串出移位寄存器74ls599 带输出锁存的8位串入并出移位寄存器74ls604 双8位锁存器74ls605 双8位锁存器74ls606 双8位锁存器74ls607 双8位锁存器74ls620 8位三态总线发送接收器(反相)74ls621 8位总线收发器74ls622 8位总线收发器74ls623 8位总线收发器74ls640 反相总线收发器(三态输出)74ls641 同相8总线收发器,集电极开路74ls642 同相8总线收发器,集电极开路74ls643 8位三态总线发送接收器74ls644 真值反相8总线收发器,集电极开路74ls645 三态同相8总线收发器74ls646 八位总线收发器,寄存器74ls647 八位总线收发器,寄存器74ls648 八位总线收发器,寄存器74ls649 八位总线收发器,寄存器74ls651 三态反相8总线收发器74ls652 三态反相8总线收发器74ls653 反相8总线收发器,集电极开路74ls654 同相8总线收发器,集电极开路74ls668 4位同步加/减十进制计数器74ls669 带先行进位的4位同步二进制可逆计数器74ls670 4*4寄存器堆(三态)74ls671 带输出寄存的四位并入并出移位寄存器74ls672 带输出寄存的四位并入并出移位寄存器74ls673 16位并行输出存储器,16位串入串出移位寄存器74ls674 16位并行输入串行输出移位寄存器74ls681 4位并行二进制累加器74ls682 8位数值比较器(图腾柱输出)74ls683 8位数值比较器(集电极开路)74ls684 8位数值比较器(图腾柱输出)74ls685 8位数值比较器(集电极开路)74ls686 8位数值比较器(图腾柱输出)74ls687 8位数值比较器(集电极开路)74ls688 8位数字比较器(oc输出)74ls689 8位数字比较器74ls690 同步十进制计数器/寄存器(带数选,三态输出,直接清除) 74ls691 计数器/寄存器(带多转换,三态输出)74ls692 同步十进制计数器(带预置输入,同步清除)74ls693 计数器/寄存器(带多转换,三态输出)74ls696 同步加/减十进制计数器/寄存器(带数选,三态输出,直接清除) 74ls697 计数器/寄存器(带多转换,三态输出)74ls698 计数器/寄存器(带多转换,三态输出) 74ls699 计数器/寄存器(带多转换,三态输出) 74ls716 可编程模n十进制计数器74ls718 可编程模n十进制计数器。

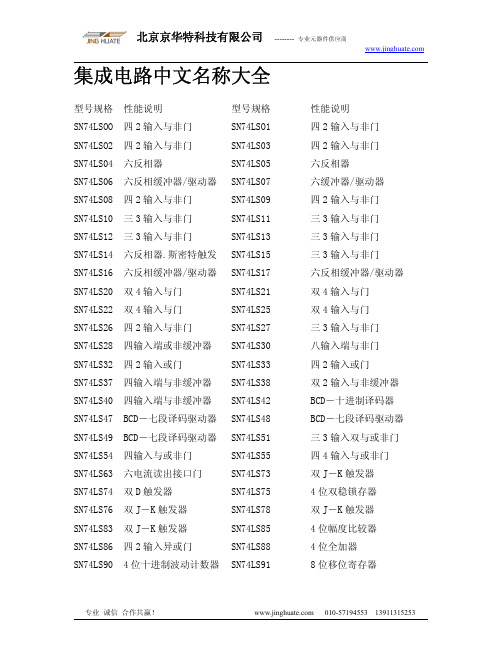

集成电路IC芯片中文名称大全

专业 诚信 合作共赢!

010-57194553 13911315253

北京京华特科技有限公司 -------- 专业元器件供应商

SN7407 六缓冲器/驱动器

SN74HC03

SN7414 六缓冲器/驱动器

SN74HC04

SN7416 六反相缓冲器/驱动器 SN74HC05

SN74LS126

SN74LS133 13 输入与非门

SN74LS132

SN74LS137 地址锁存 3-8 线译码器 SN74LS136

SN74LS139 双 2-4 线译码-转换器 SN74LS138

SN74LS147 10-4 线优先编码器 SN74LS145

SN74LS153 双 4 选 1 数据选择器 SN74LS148

专业 诚信 合作共赢!

010-57194553 13911315253

北京京华特科技有限公司 -------- 专业元器件供应商

SN74LS92 12 分频计数器

SN74LS93

SN74LS96 5 位移位寄存器

SN74LS95

SN74LS273

SN74LS283 4 位二进制全加器

SN74LS276

SN74LS293 4 位二进制计数器

SN74LS280

SN74LS365 六缓冲器带公用启动器 SN74LS290

SN74LS367 六总线三态输出缓冲器 SN74LS295

SN74LS373 8D 锁存器 SN74LS375 4 位双稳锁存器 SN74LS386 四 2 输入异或门 SN74LS393 双 4 位二进制计数器 SN74LS574 8 位 D 型触发器

SN74LS155 双 2-4 线多路分配器 SN74LS151

芯片74LS139_中文资料

II 最大输入电压时

VI=5.5V

1

Vcc=5V

mA

输入电流

VI=7V

0.1

IIH 输入高电平电 流

Vcc=最大 VIH=2.7V

50

20 μA

VIL=0.4

-0.4

VIL 输入低电平电

V

Vcc=最大

mA

流

VIL=0.5

-2

V

IOS 输出短路电流

Vcc=最大

54 -40 -100 -6 -40 mA

TPHL

(2 级)

【2】:TPLH 输出由低电平到高电平传输延迟时间

TPHL 输出由高电平到低电平传输延迟时间

‘S139 最大

7.5

10 12 12 8 10

‘LS139 最大

20

33 29 38 24 32

单位 ns ns ns

PD 300mW 34mW

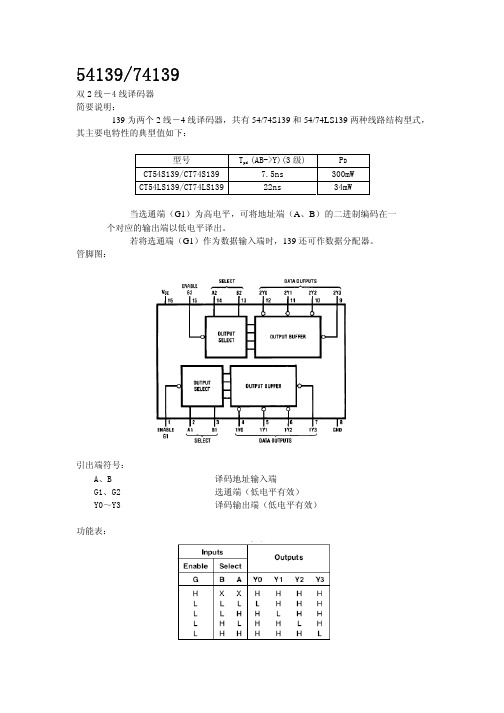

当选通端(G1)为高电平,可将地址端(A、B)的二进制编码在一 个对应的输出端以低电平译出。

若将选通端(G1)作为数据输入端时,139 还可作数据分配器。 管脚图:

引出端符号: A、B G1、G2 Y0~Y3

功能表:

译码地址输入端 选通端(低电平有效) 译码输出端(低电平有效)

-1.5 2.5

单位

V V

IC资料查询网站: 电子工程技术论坛:/bbs

压

VIH=2V,VIL=最大,

74 2.7

2.7

IOH=最大

VOL 输出低电平电

VCC=最

54

0.5

小,VIH=2V,VIL=最

压

大,IOL=最大

74

0.5

0.4 V

74LS系列芯片引脚图资料大全

└┬—┬—┬—┬—┬—┬—┬┘

1A 1B 1Y 2A 2B 2Y GND

Vcc 4Y 4B 4A 3Y 3B 3A ┌┴—┴—┴—┴—┴—┴—┴┐ 2 输入四或非门 74LS02

│14 13 12 11 10 9 8│ ___

)

│ Y = A+B

│ 1 2 3 4 5 6 7│

└┬—┬—┬—┬—┬—┬—┬┘

74 系列芯片引脚图资料大全

反相器 驱动器

LS04 LS05 LS06 LS07 LS125 LS240 LS244 LS245

与门 与非门

LS00 LS08 LS10 LS11 LS20 LS21 LS27 LS30 LS38

或门 或非门 与或非门 LS02 LS32 LS51 LS64 LS65

1Y 1A 1B 2Y 2A 2B GND

Vcc 2Y 2B 2A 2D 2E 1F ┌┴—┴—┴—┴—┴—┴—┴┐ 双与或非门 74S51

│14 13 12 11 10 9 8│ _____

)

│ 2Y = AB+DE

│ 1 2 3 4 5 6 7│ _______

└┬—┬—┬—┬—┬—┬—┬┘ 1Y = ABC+DEF

异或门 比较器

LS86

译码器

LS138 LS139

寄存器

LS74 LS175 LS373

反相器:

Vcc 6A 6Y 5A 5Y 4A 4Y 六非门 74LS04 ┌┴—┴—┴—┴—┴—┴—┴┐ 六非门(OC 门) 74LS05 _ │14 13 12 11 10 9 8 │ 六非门(OC 高压输出) 74LS06

└┬—┬—┬—┬—┬—┬—┬┘

1A 1Y 2A 2Y 3A 3Y GND

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Icc 电源电流

Vcc=最大

90

11 mA

【1】:测试条件中的“最大”和“最小”用推荐工作条件中的相应值。

动态特性(TA=25℃)

参数【2】

测试条件

TPLH AB->Y

TPHL TPLH TPHL TPLH

(2 级)

AB->Y (3 级) /G->Y

Vcc=5V

CL=15pF RL=280Ω (‘LS139 为 2KΩ)

2

2

V

54

0.8

0.7

V

74

0.8

0.8

-1000

-400 µA

54

20

4

mA

74

20

8

逻辑图

静态特性(TA 为工作环境温度范围)

参数

测试条件【1】

VIK 输入钳位电压 Vcc 最小 IIK=-12mA

VOH 输出高电平电

Vcc=最小,

54

`S139 最小 最大

-1.2 2.5

`LS139 最小 最大

PD 300mW 34mW

当选通端(G1)为高电平,可将地址端(A、B)的二进制编码在一 个对应的输出端以低电平译出。

若将选通端(G1)作为数据输入端时,139 还可作数据分配器。 管脚图:

引出端符号: A、B G1、G2 Y0~Y3

功能表:

译码地址输入端 选通端(低电平有效) 译码输出端(低电平有效)

H=高电平 L=低电平 X=任意 极限值 电源电压------------------------------------------------7V 输入电压 54/74S139----------------------------------------5.5V 54/74LS139---------------------------------------7V 工作环境温度 54×××------------------------------ -55~125℃ 74×××------------------------------------0~70℃ 贮存温度-------------------------------------- -65~150℃

54139/74139

双 2 线-4 线译码器 简要说明:

139 为两个 2 线-4 线译码器,共有 54/74S139 和 54/74LS139 两种线路结构型式, 其主要电特性的典型值如下:

型号 CT54S139/CT74S139 CT54LS139/CT74LS139

Tpd (AB->Y)(3 级) 7.5ns 22ns

0.5

II 最大输入电压时

VI=5.5V

1

Vcc=5V

mA

输入电流

VI=7V

0.1

IIH 输入高电平电 流

Vcc=最大 VIH=2.7V

50

20 μA

VIL=0.4

-0.4

VIL 输入低电平电

V

Vcc=最大

mA

流

VIL=0.5

-2

V

IOS 输出短路电流

Vcc=最大

54 -40 -100 -6 -40 mA

-1.5 2.5

单位

V V

IC资料查询网站: 电子工程技术论坛:/bbs

压

VIH=2V,VIL=最大,

74 2.7

2.7

IOH=最大

VOL 输出低电平电

VCC=最

54

0.5

小,VIH=2V,VIL=最

压

大,IOL=最大

74

0.5

0.4 V

TPHL

(2 级)

【2】:TPLH 输出由低电平到高电平传输延迟时间

TPHL 输出由高电平到低电平传输延迟时间

‘S139 最大

7.5

10 12 12 8 10

‘LS139 最大

20

33 29 38 24 32

单位 ns ns ns

推荐 工作条件:

电源电压 Vcc

输入高电平电压 VIH 输入低电平电压 VIL 输出高电平电流 IOH 输出低电平电流 IOL

CT54S139/CT74S139 最小 额定 最大

CT54LS139/CT74LS139 最小 额定 最大

单位

54 4.5 74 4.75

5

5.5 4.5 5

5.5

V

5 5.25 4.75 5 5.25