数字控制振荡器

dcxo工作原理

dcxo工作原理DCXO(Digitally Controlled Crystal Oscillator)是一种数字控制晶体振荡器,它是通过数字控制电路来调节晶体振荡频率的。

它的工作原理是利用晶体振荡器的特性,通过数字控制电路来改变晶体振荡频率,从而实现精确稳定的时钟信号输出。

DCXO的核心部件是晶体振荡器。

晶体振荡器是一种利用晶体的特性进行振荡的电子元件,其基本原理是利用晶体的压电效应和谐振效应。

晶体振荡器由晶体谐振器、放大器和反馈网络组成。

晶体谐振器是通过将晶体片与电容和电感等元件连接在一起来实现的。

当通过谐振频率的电压信号作用于晶体片时,晶体片会发生压电效应,从而使晶体片振动,产生稳定的振荡信号。

放大器将晶体振荡器产生的弱振荡信号放大,然后通过反馈网络将一部分输出信号再反馈到晶体谐振器上,使晶体振荡器保持稳定的振荡。

通过调节晶体谐振器的电容和电感等元件的数值,可以改变晶体振荡器的振荡频率。

DCXO通过数字控制电路来调节晶体振荡器的电容和电感等元件的数值,从而改变晶体振荡器的振荡频率。

数字控制电路通常由微控制器、数字逻辑电路和数字-模拟转换器(DAC)等组成。

微控制器负责接收外部输入的控制信号,然后通过数字逻辑电路进行处理,最终将处理结果转换成模拟信号输出到DAC。

DAC将模拟信号转换成电压或电流信号,然后通过控制电路调节晶体振荡器的电容和电感等元件的数值。

DCXO的工作原理可以简单概括为以下几个步骤:首先,微控制器接收外部输入的控制信号,根据控制信号的数值确定需要调节的振荡频率。

然后,数字逻辑电路根据控制信号的数值计算出相应的调节数值。

接下来,数字-模拟转换器将计算结果转换成模拟信号输出到DAC。

最后,DAC将模拟信号转换成电压或电流信号,通过控制电路调节晶体振荡器的电容和电感等元件的数值,从而改变振荡频率。

DCXO广泛应用于各种需要精确稳定时钟信号的领域,如通信系统、计算机网络、无线电设备等。

数字控制振荡器工作原理

数字控制振荡器工作原理

数字控制振荡器(Digital Controlled Oscillator,DCO)是一种基于数字信号处理技术的振荡器,其工作原理是通过控制数字信号的频率来实现振荡器的频率调节。

DCO广泛应用于数字通信、音频处理、频率合成等领域。

DCO的核心是一个数字控制的振荡器电路,其基本结构包括振荡器核心、数字控制单元和输出缓冲器。

振荡器核心是由一个电感和一个电容组成的谐振电路,其频率与电感和电容的数值有关。

数字控制单元通过改变电容的数值来改变振荡器的频率,从而实现频率的调节。

输出缓冲器将振荡器的输出信号放大并输出到外部电路中。

DCO的频率调节是通过改变电容的数值来实现的。

数字控制单元通过控制电容的开关状态来改变电容的数值,从而改变振荡器的频率。

具体来说,数字控制单元将一个二进制数值转换为一组开关控制信号,这些信号控制电容的开关状态,从而改变电容的数值。

通过改变二进制数值,可以实现振荡器频率的微调和精确控制。

DCO的优点是频率调节范围广、精度高、稳定性好、功耗低等。

与传统的模拟振荡器相比,DCO具有更高的频率调节范围和更好的频率稳定性。

此外,DCO的功耗较低,适合用于低功耗应用场景。

总之,数字控制振荡器是一种基于数字信号处理技术的振荡器,其工作原理是通过控制数字信号的频率来实现振荡器的频率调节。

DCO具有频率调节范围广、精度高、稳定性好、功耗低等优点,广泛应用于数字通信、音频处理、频率合成等领域。

ltc6904 范例

ltc6904 范例LTC6904是一款高性能的数字控制电压控制振荡器(DCVCO),由ADI (安富利)公司生产。

它可以通过I2C接口进行配置和控制,提供了高精度的频率合成功能。

LTC6904的范例应用广泛,本文将介绍其工作原理以及在实际应用中的一些案例。

我们来了解一下LTC6904的基本原理。

它是一种基于电容的振荡器,通过改变电容的充放电时间来调节输出频率。

LTC6904内部有一个电容阵列,可以通过配置寄存器来选择不同的电容组合,进而实现不同的频率输出。

此外,LTC6904还可以通过I2C接口调节电压控制输入(VCOIN)来进一步微调频率。

LTC6904的工作电压范围为2.7V至5.5V,输出频率范围为0.1Hz至20MHz。

它具有非常低的频率漂移和相位噪声,能够提供高度稳定的频率输出。

此外,LTC6904还提供了多种工作模式,包括连续振荡模式、单次振荡模式和脉冲振荡模式,可以满足不同应用的需求。

在实际应用中,LTC6904可以广泛应用于时钟生成、频率合成、数字信号处理等领域。

下面我们将介绍一些具体的应用案例。

首先是时钟生成。

在很多系统中,需要一个稳定的时钟信号来同步各个模块的工作。

LTC6904可以提供高精度的时钟信号,且可以通过I2C接口实时调节频率。

这使得它在通信系统、数据采集系统等领域中得到广泛应用。

其次是频率合成。

频率合成是将多个不同频率的信号合成为一个特定频率的信号。

LTC6904可以通过调节电容组合和VCOIN输入,实现精确的频率合成。

这在无线通信系统、雷达系统等需要频率合成的应用中非常常见。

LTC6904还可以用于数字信号处理。

在数字信号处理中,需要对信号进行数字化、滤波、解调等处理。

LTC6904可以提供稳定的时钟信号,为数字信号处理提供精确的时间基准。

这在音频处理、图像处理等领域中非常重要。

LTC6904是一款功能强大的数字控制振荡器,具有高精度、稳定性好的特点。

它可以通过I2C接口进行配置和控制,广泛应用于时钟生成、频率合成、数字信号处理等领域。

实验三 用定时器实现数字振荡器

实验三 用定时器实现数字振荡器1 实验目的在数字信号处理中,会经常使用到正弦/余弦信号。

通常的方法是讲某个频率的正弦/余弦值余弦计算出来后制成一个表,DSP 工作时仅作查表运算即可。

在本实验中将介绍另一种获得正弦/余弦信号的方法,即利用数字振荡器用叠代方法产生正弦信号。

本实验除了学习数字振荡器的DSP 实现原理外,同时还学习C54X 定时器使用以及中断服务程序编写。

另外,在本实验中我们将使用汇编语言和C 语言分别完成源程序的编写。

2 实验要求本实验利用定时器产生了一个2kHz 的正弦信号,定时器被设置成每25uS 产生一次中断,(等效于采样速率未40k )利用该中断,在该中断服务程序中用叠代算法计算出一个SNT 值,病利用CCS 的图形显示功能查看波形。

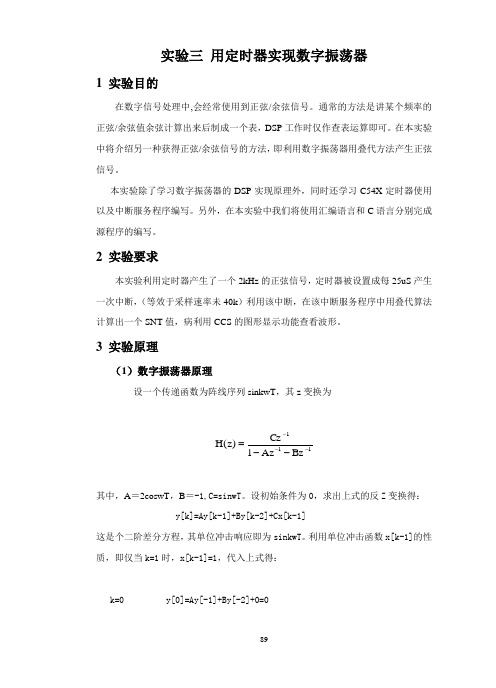

3 实验原理(1)数字振荡器原理设一个传递函数为阵线序列sinkwT ,其z 变换为111BzAz 1Cz )z (H -----=其中,A =2coswT ,B =-1,C=sinwT 。

设初始条件为0,求出上式的反Z 变换得: y[k]=Ay[k-1]+By[k-2]+Cx[k-1]这是个二阶差分方程,其单位冲击响应即为sinkwT 。

利用单位冲击函数x[k-1]的性质,即仅当k=1时,x[k-1]=1,代入上式得:k=0 y[0]=Ay[-1]+By[-2]+0=0k=1 y[1]=Ay[0]+By[-2]+c=ck=2 y[2]=Ay[1]+By[0]+0=Ay[1]k=3 y[3]=Ay[2]+By[1]k=n y[n]=Ay[n-1]+By[n-2]在k ﹥2以后,y[k]能用y[k -1]和y[k-2]算出,这是一个递归得方法。

根据上面得说明,我们可以开始数字振荡器得设计。

设该振荡器得频率为2kHz,采样率为40kHz (通过定时器设置,每隔25us 中断一次,即产生一个y[n])则递归得差分方程系数为:A =2coswT=2cos(2×PI ×2000/40000)=2×0.95105652B=-1C=sinwT=sin(2×PI ×2000/40000)=0.3090169979BC 22A 15=⨯ C00022B 15=⨯ 13C722C 15=⨯ 为了便于定点DSP 处理,我们将所有系数除以2,然后用16为定点格式表示为: 这便是本实验中查生2kHz 阵线信号的三个系数。

MS中文数据手册

晶振,XIN,XOUT

注释:1.晶体两端都需要连接电容,电容值由晶体制造商规定。

2.仅当使用一个外部逻辑水平时钟源时适用,使用晶体或谐振器时不适用。

注释:x为P2口的位标识符6到7,在元件上没有与这两位对应的外部引脚

注释:将P2口未连接的两位6和7用作中断标志是一种良好的应用方法,除了软件其他信号不会影响到这两个中断标志,从而它们被用作软件中断。

JTAG熔丝检查模式

上电复位(POR)后第一次使用JTAG口,在TEST端有熔丝的MSP430设备有一个熔丝检查模式,可以检测熔丝的通断。该模式有效时,如果熔丝没烧断,将有一个熔丝检查电流Itf(电压3V时1mA,电压5V时2.5mA)从TEST引脚流到地,必须防止意外激活熔丝检查模式,以免增加系统功耗。

可选电阻,独立可编程(参阅注释1)

注释1:在标准OTP或者EPROM设备MSP430P112或MSP430E112中,用于上拉或下拉的可选电阻R optx 是不可编程的。

从低电压模式唤醒响应时间(LPMx)

注释1:这个参数是保持程序存储器(RAM)中数据不丢失所需的最小电压,在这个电压下,程序不能执行。

2.数字端口引脚的泄露电流要单个测量。端口引脚必须选择为输入并且没有选择上拉或下拉电阻。

输出 P2x,Tax

输出P1口和P2口

注释:1.对于所有输出组合,最大总电流I OH(max)和I OL(max)不能超过±12mA,以便输出电压满足输出电压下降标准。

2.对于所有输出组合,最大总电流I OH(max)和I OL(max)不能超过±36mA,以便输出电压满足输出电压下降标准。

NCO和DDS技术

波形和其波形序列指令都存在仪器所带的RAM中。

任意波形发生器

波形生成序列通常从 TTL硬件触发器开始。各种波形由许多 单个的样本构成,而生成采样率由仪器的采样时钟确定。从

内部采样时钟时基(100 MHz VCXO)中导出采样时钟有几种

不同模式,包括DDS定时Div/N时钟,以及几种提供不同外部 时钟的模式。另外,对于用于仪器的锁相环的频率基准,也

真思考如何为以后的发展开好头。

Thank you

函数发生器

函数发生器产生固定波形,如正弦波、方波(矩形波)阶梯波 或三角波(锯齿波),频率可调节。函数发生器无需来自计 算机或大容量存储缓冲器的连续输入,因为设备本身能够产 生这些波形。 函数发生器可以基于模拟技术,也可以基于数字技术。模拟 函数发生器利用模拟硬件来产生简单的函数,并在需要指定 频率的静态正弦波或方波时经常使用。而数字函数发生器采 用直接数字综合( DDS),DAC,数字信号处理,以及一个单 周期存储缓冲器来产生信号。 DDS技术依赖数字控制的方法, 利用单基准时钟频率来实现一个模拟频率源。DDS能够实现 高精度和高分辨率,高温度稳定度,高宽带,以及随机的和 相位连续的频率切换。 许多信号源通过对一个内部时基进行整数分频来产生时钟信 号,这被称为除N方法。但是,用除N方法来产生时钟,只能 产生有限的时钟频率。AWG,甚至几个时钟频率产生器,可 以采用DDS技术来产生具有非常精细的更新频率时钟信号, 而这是除NCO方法无法实现的。

CORDIC算法(参见论文-苏凯雄.基于FPGA的数控振荡器的设计与实现)

Walther JS于1971年提出了统一的CORDIC形式。 假定初始向量V1(x1 ,y1)旋转角度θ后得到向量V2(x2,y2),即:

9~11GHz数字控制LC振荡器

r e a l i z e d a n d t h e p h a s e n o i s e a t 9 . 3 8 GHz i s一 1 1 1 . 0 2 d B c / Hz a t 1 M Hz o f f s e t .

Ke y wor ds: a l l di g i t a l s y nt h e s i z e r; o s c i l l a t o r wi t h c o m pl e me nt ar y s t r u c t u r e; pha s e no i s e; f r e q ue nc y r e s o l u t i o n

( S t a t e Ke y L a b o r a t o r y o f A S I C&S y s t e m, F u d a n U n i v e r s i t y, S h a n g h a i ,2 0 1 2 0 3 , C HN )

Ab s t r a c t :A d i g i t a l — c o n t r o l l e d LC o s c i l l a t o r i s i mp l e me n t e d i n TS MC 6 5 n m CM OS p r o c e s s , wh i c h i s u s e d i n a l l d i g i t a l f r e q u e n c y s y n t h e s i z e r wi t h a n o u t p u t f r e q u e n c y r a n g e f r o m 8 . 9 5 GHz t o 1 1 . O 2 GH z .I n o r d e r t o r e d u c e t h e p h a s e n o i s e,t h e c o mp l e me n t a r y s t r u c t u r e wi t h t a i l i n d u c — t o r s i s u s e d .Th e c a p a c i t o r b a n k s a r e d i v i d e d i n t o t h r e e p a r t s i n o r d e r t o c o o r d i n a t e wi t h t h e t h r e e s t e p s o f f r e q u e n c y l o c k i n g p r o c e s s o f t h e s y n t h e s i z e r . Un d e r a s u p p l y o f 1 V ,t h e p o we r c o n — s u mp t i o n i s 3 . 5 3 mW .Ac c o r d i n g t o t h e me a s u r e me n t r e s u l t s ,a f r e q u e n c y r e s o l u t i o n o f 4 0 k Hz i s

数字高频调谐器原理与结构分析

数字高频调谐器原理与结构分析数字高频调谐器是一种用于调节高频信号频率的装置,它在无线通信、雷达、卫星通信等领域起着重要的作用。

本文将详细介绍数字高频调谐器的原理和结构,并分析其工作过程。

一、原理数字高频调谐器的原理基于频率合成和滤波技术。

其主要功能是将输入的高频信号调整到指定的频率范围内,并滤除不需要的频率分量。

其原理主要包括以下几个方面:1. 数字频率合成数字高频调谐器采用数字信号处理技术,通过数字频率合成器将输入的高频信号调整到目标频率范围内。

数字频率合成器是由相位锁定环路(PLL)和数字控制振荡器(DCO)组成的。

相位锁定环路用于锁定输入信号的相位,而数字控制振荡器则根据相位锁定环路的输出生成目标频率的高频信号。

2. 数字滤波数字高频调谐器还需要进行滤波处理,以滤除不需要的频率分量。

滤波器通常采用数字滤波器,其主要功能是在目标频率范围内增强信号的幅度,并在其他频率范围内削弱信号的幅度。

数字滤波器可以通过滤波算法实现,常用的算法包括有限脉冲响应(FIR)滤波器和无限脉冲响应(IIR)滤波器。

3. 数字控制数字高频调谐器还需要进行数字控制,以实现对频率和滤波参数的调节。

数字控制可以通过微处理器或可编程逻辑器件实现,通过调节相位锁定环路和数字滤波器的参数,可以实现对输入信号的精确调谐。

二、结构数字高频调谐器的结构主要包括输入端、数字频率合成器、数字滤波器和输出端。

下面将对每个部分进行详细介绍。

1. 输入端输入端主要用于接收外部的高频信号。

它通常包括天线、前置放大器和滤波器。

天线用于接收无线信号,并将其转换为电信号。

前置放大器用于放大电信号的幅度,以提高信号的强度。

滤波器用于滤除不需要的频率分量,以减少噪声和干扰。

2. 数字频率合成器数字频率合成器是数字高频调谐器的核心部分。

它由相位锁定环路和数字控制振荡器组成。

相位锁定环路用于锁定输入信号的相位,以实现相位同步。

数字控制振荡器根据相位锁定环路的输出生成目标频率的高频信号。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

背景知识:

在实际的通信系统中,携带数字信息的信号通常是由某种类型的载波调制方式发送的,传送信号的带宽限制在以载波为中心的一个频段上,如双边带调制,或在邻近载波的频段上,如单边带调制。

无论何种调制方式,在发送端均需要一个高频载波将信息调制上去,以减小信号衰落,相干解调时在接收端也需要一个与发送端同频同相的高频载波将信息从高频上解调下来。

为了产生这个高频载波,在数字电路中是采用数控振荡器(NCO),也称为直接数字频率合成器〔DDS),它的输出频率和相位可以受人为控制,从而满足各种需要。

基本原理:

下图为NCO的工作原理框图:

数控振荡器一般由基准时钟(fclk)、相位字寄存器、相位累加器以及幅度/相位转换电路等部分组成。

在基准时钟的作用下,每一个时钟周期存贮在相位字寄存器里的值都由相位累加器进行累加,相位果加器的输出作为查找表的输人,从而得到相对应的幅度值。

根据奈奎斯特采样定律,输出信号的频率应小于基准时钟的1/2。

相位累加器输出(△Ф)的数值和系统的频率(fclk)决定了输出频率(fout),它门的关系如下:

N是相位寄存器的位数,N值的大小决定了频率分辨率(fres ),有

在这里假设,fclk=128MHz, N=32,可以计算出NCO的频率分辨率

fres=0.0298Hz

相位累加器是决定NCO电路性能的一个关键部分。

我们可以采用了Altera 的加法器宏功能模块形成一个32bit的累加器,它以流水线处理方式进行工作。

相位/幅度转换电路是NCO电路中的另一个关键部分,在设计中面临的主要问题就是资源的开销。

一般电路采用ROM结构,相位累加器的输出是一种数字式锯齿波,通过取它的若干位作为ROM的地址输人,而后通过查表和运算,ROM就能输出所需波形的量化数据。

在APEX器件中,ROM由EAB实现,ROM表的尺寸随着地址位数或数据位数的增加成指数递增关系,因此在满足信号性能的前提条件下,如何减少资源的开销就是一个重要的问题。

在实际设计时,要充分利用信号周期内的对称性和算术关系来减少EAB的开销。

上图为产生正弦信号的相位/幅度转换电路,相位累加器累加值的最高位(MSB )和次最高位(MSB-1)的组合作为象限确定模块的输人,由此来确定输出信号所在的相平面和极性符号,如表所示。

正弦查找表存贮了1/4周期的正弦幅度数据,通过象限确定模块就可以完成完整的正弦波的形成。

这里采用了一个256 x 8的ROM宏模块。

地址线和数据线输出均为8bit, 8bit地址分别对应相位累加器的30-23bit的输出数据。

正弦查找表的输出是无符号的8bit数据,并不能代表正弦波形。

求补模块根据象限确定模块的输出符号位的极性来对查找表输出数据进行求补,并把此符号位和正弦查找表输出的高7bit组合作为最终正弦波输出信号。