半导体专业用语

半导体专业用语

金属前介质层(PMD)金属间介质层(IMD)W塞(W PLUG)钝化层(Passivation)acceptor 受主,如B,掺入Si中需要接受电子Acid:酸actuator激励ADI After develop inspection显影后检视AEI After etching inspection蚀科后检查AFM atomic force microscopy 原子力显微ALD atomic layer deposition 原子层淀积Align mark(key):对位标记Alignment 排成一直线,对平Alloy:合金Aluminum:铝Ammonia:氨水Ammonium fluoride:NHFAmmonium hydroxide:NHOHAmorphous silicon:α-Si,非晶硅(不是多晶硅)amplifier 放大器AMU 原子质量数Analog:模拟的analyzer magnet 磁分析器Angstrom:A(E-m)埃Anisotropic:各向异性(如POL Y ETCH)Antimony(Sb)锑arc chamber 起弧室ARC:anti-reflect coating 防反射层Argon(Ar)氩Arsenic trioxide(AsO)三氧化二砷Arsenic(As)砷Arsine(AsH)ASHER 一种干法刻蚀方式Asher:去胶机ASI 光阻去除后检查ASIC 特定用途集成电路Aspect ration:形貌比(ETCH中的深度、宽度比)ATE 自动检测设备Back end:后段(CONTACT以后、PCM测试前)Backside Etch 背面蚀刻Backside 晶片背面Baseline:标准流程Beam-Current 电子束电流Benchmark:基准BGA ball grid array 高脚封装Bipolar:双极Boat:扩散用(石英)舟Cassette 装晶片的晶舟CD:critical dimension 关键性尺寸,临界尺寸Chamber 反应室Chart 图表Child lot 子批chiller 制冷机Chip (die) 晶粒Chip:碎片或芯片。

半导体专业词汇汇总

半导体专业词汇汇总

1. “晶圆”呀,这就像是半导体世界里的小舞台,所有的精彩都在这上面展开!比如,我们手机里的芯片就是在晶圆上制造出来的哦。

2. “晶体管”,那可是半导体的大功臣啊!就好像是电路里的小开关,控制着电流的通断呢。

你看电脑的运行不就靠它嘛!

3. “集成电路”简直太厉害啦!这不就是把好多好多的晶体管啥的都集成在一起嘛,就像一个超级团队一样!像我们家里的各种电器都有它的功劳呀。

4. “半导体材料”,这可是基础呀!没有它哪来的半导体器件呢?好比盖房子的砖头,没有砖头怎么能有坚固的房子呢?这半导体材料就类似于这样重要的存在啊。

5. “封装”,把芯片保护起来的重要一步呀!就如同给宝贝穿一件坚固的外衣,让它能更好地工作和发挥作用呢。

像我们平常看到的那些芯片,都是经过封装的哟。

6. “光刻”,哇,这可是个精细活呢!它就像是在晶圆上画画,得超级仔细才行。

这个步骤要是没做好,那后面可就都乱啦!

7. “掺杂”,这可是改变半导体性能的关键呀!就好像给它加点特别的调料,让它变得更独特和好用。

很多半导体器件的特性可都是靠掺杂来实现的呢!

8. “蚀刻”,把不需要的部分去掉,这就像是给半导体做一次精准的修剪。

有了它,才能让半导体呈现出我们想要的形状和功能呀!

总之,这些半导体专业词汇可都太重要啦,它们共同构建了半导体这个神奇的领域!。

半导体行业术语

半导体行业术语半导体行业术语是专门用于描述和解释半导体技术和相关概念的专业词汇。

在描述半导体行业的相关术语时,需要确保清晰度和准确性。

以下是一些常见的半导体行业术语及其解释:1.半导体:半导体是一种电子材料,具有介于导体和绝缘体之间的电导特性。

半导体材料通常可以控制电流的流动,是构成电子器件和集成电路的基本元件。

2.集成电路(IC):集成电路是一种由多个电子元件(如晶体管、电容、电阻等)以及连接器件(如导线、金属线等)组成的电路系统。

集成电路可用于执行各种计算、存储和处理任务。

3.晶体管:晶体管是一种半导体器件,可以放大和控制电流。

晶体管由三层材料组成,其中包括一个控制区域、一个输入区域和一个输出区域。

晶体管被广泛用于电子设备和电路中。

4.功耗:功耗是指半导体器件在正常运行时消耗的电能。

功耗通常以瓦特(W)为单位进行衡量,是半导体行业中一个重要的考虑因素。

5.时钟频率:时钟频率是计量半导体器件工作速度的指标,通常以赫兹(Hz)为单位。

时钟频率越高,半导体器件的数据处理和运行速度越快。

6.互连:互连是指将不同的半导体器件或电子组件连接在一起的过程。

互连通常使用导线、金属线、连接器等来完成。

7.工艺技术:工艺技术是指用于制造半导体器件和集成电路的特定技术过程。

包括一系列的步骤,如沉积、蚀刻、掩膜制备等,用于制造和构建电子器件。

8.掩膜:掩膜是一种用于制造半导体器件的模板。

掩膜通常是由光刻工艺制备的,可以在半导体材料上形成特定的图案和结构,用于制造电子器件的特定组件。

9.封装:封装是将半导体芯片和连接线封装在外壳中的过程。

封装有助于保护芯片和电路,并提供适当的物理连接和支持。

10.微纳加工技术:微纳加工技术是一种用于制造微小尺度结构和器件的技术。

在半导体行业中,微纳加工技术被广泛应用于制造芯片和集成电路,以及其他微小尺度的器件。

以上是一些常见的半导体行业术语及其解释。

了解和熟悉这些术语对于了解半导体技术和行业发展趋势非常重要。

半导体专业术语.doc

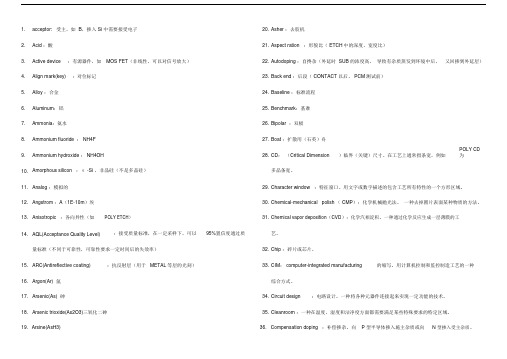

1. acceptor: 受主,如 B,掺入 Si 中需要接受电子20. Asher :去胶机2. Acid :酸21. Aspect ration :形貌比( ETCH中的深度、宽度比)3. Active device :有源器件,如MOS FET(非线性,可以对信号放大)22. Autodoping :自搀杂(外延时 SUB的浓度高,导致有杂质蒸发到环境中后,又回掺到外延层)4. Align mark(key) :对位标记23. Back end :后段( CONTACT以后、 PCM测试前)5. Alloy :合金24. Baseline :标准流程6. Aluminum:铝25. Benchmark:基准7. Ammonia:氨水26. Bipolar :双极8. Ammonium fluoride : NH4F 27. Boat :扩散用(石英)舟9. Ammonium hydroxide : NH4OH 28. CD:(Critical Dimension )临界(关键)尺寸。

在工艺上通常指条宽,例如POLY CD 为10. Amorphous silicon :α -Si ,非晶硅(不是多晶硅)多晶条宽。

11. Analog :模拟的29. Character window :特征窗口。

用文字或数字描述的包含工艺所有特性的一个方形区域。

12. Angstrom :A(1E-10m)埃30. Chemical-mechanical polish ( CMP):化学机械抛光法。

一种去掉圆片表面某种物质的方法。

13. Anisotropic :各向异性(如POLY ETCH)31. Chemical vapor deposition(CVD):化学汽相淀积。

一种通过化学反应生成一层薄膜的工14. AQL(Acceptance Quality Level) :接受质量标准,在一定采样下,可以95%置信度通过质艺。

半导体专业术语

专业术语1 Active Area 主动区(工作区)主动晶体管(ACTIVE TRANSI STOR)被制造的区域即所谓的主动区(ACTIVE AREA)。

在标准之MO S制造过程中ACTI VE AREA是由一层氮化硅光罩即等接氮化硅蚀刻之后的局部场区氧化所形成的,而由于利用到局部场氧化之步骤,所以ACTI VE AREA会受到鸟嘴(BIRD’SBEAK)之影响而比原先之氮化硅光罩所定义的区域来的小,以长0.6UM之场区氧化而言,大概会有0.5UM之BI RD’SBEAK 存在,也就是说AC TIVEAREA比原在之氮化硅光罩所定义的区域小0.5UM。

2 ACTONE丙酮 1. 丙酮是有机溶剂的一种,分子式为CH3COCH3。

2. 性质为无色,具刺激性及薄荷臭味之液体。

3. 在FAB内之用途,主要在于黄光室内正光阻之清洗、擦拭。

4. 对神经中枢具中度麻醉性,对皮肤黏膜具轻微毒性,长期接触会引起皮肤炎,吸入过量之丙酮蒸汽会刺激鼻、眼结膜及咽喉黏膜,甚至引起头痛、恶心、呕吐、目眩、意识不明等。

5. 允许浓度1000PPM。

3 ADI 显影后检查1.定义:AfterDevelo pingInspec tion之缩写2.目的:检查黄光室制程;光阻覆盖→对准→曝光→显影。

发现缺点后,如覆盖不良、显影不良…等即予修改,以维护产品良率、品质。

3.方法:利用目检、显微镜为之。

4 AEI 蚀刻后检查1. 定义:AEI即Af ter Etchin g Inspec tion,在蚀刻制程光阻去除前及光阻去除后,分别对产品实施全检或抽样检查。

2.目的:2-1提高产品良率,避免不良品外流。

2-2达到品质的一致性和制程之重复性。

2-3显示制程能力之指针2-4阻止异常扩大,节省成本3.通常AEI检查出来之不良品,非必要时很少作修改,因为重去氧化层或重长氧化层可能造成组件特性改变可靠性变差、缺点密度增加,生产成本增高,以及良率降低之缺点。

半导体行业专业词汇

半导体行业专业词汇. acceptance testing (WAT: wafer acceptance testing)2. acceptor: 受主,如B,掺入Si中需要接受电子3. ACCESS:一个EDA(Engineering Data Analysis)系统4. Acid:酸5. Active device:有源器件,如MOS FET(非线性,可以对信号放大)6. Align mark(key):对位标记7. Alloy:合金8. Aluminum:铝9. Ammonia:氨水10. Ammonium fluoride:NH4F11. Ammonium hydroxide:NH4OH12. Amorphous silicon:α-Si,非晶硅(不是多晶硅)13. Analog:模拟的14. Angstrom:A(1E-10m)埃15. Anisotropic:各向异性(如POLY ETCH)16. AQL(Acceptance Quality Level):接受质量标准,在一定采样下,可以95%置信度通过质量标准(不同于可靠性,可靠性要求一定时间后的失效率)17. ARC(Antireflective coating):抗反射层(用于METAL等层的光刻)18. Antimony(Sb)锑19. Argon(Ar)氩20. Arsenic(As)砷21. Arsenic trioxide(As2O3)三氧化二砷22. Arsine(AsH3)23. Asher:去胶机24. Aspect ration:形貌比(ETCH中的深度、宽度比)25. Autodoping:自搀杂(外延时SUB的浓度高,导致有杂质蒸发到环境中后,又回掺到外延层)26. Back end:后段(CONTACT以后、PCM测试前)27. Baseline:标准流程28. Benchmark:基准29. Bipolar:双极30. Boat:扩散用(石英)舟31. CD:(Critical Dimension)临界(关键)尺寸。

半导体专业术语

1.acceptance testing (WAT: wafer acceptance testing)2.acceptor: 受主,如B,掺入Si中需要接受电子3.Acid:酸4.Active device:有源器件,如MOS FET(非线性,可以对信号放大)5.Align mark(key):对位标记6.Alloy:合金7.Aluminum:铝8.Ammonia:氨水9.Ammonium fluoride:NH4F10.Ammonium hydroxide:NH4OH11.Amorphous silicon:α-Si,非晶硅(不是多晶硅)12.Analog:模拟的13.Angstrom:A(1E-10m)埃14.Anisotropic:各向异性(如POLY ETCH)15.AQL(Acceptance Quality Level):接受质量标准,在一定采样下,可以95%置信度通过质量标准(不同于可靠性,可靠性要求一定时间后的失效率)16.ARC(Antireflective coating):抗反射层(用于METAL等层的光刻)17.Argon(Ar)氩18.Arsenic(As)砷19.Arsenic trioxide(As2O3)三氧化二砷20.Arsine(AsH3)21.Asher:去胶机22.Aspect ration:形貌比(ETCH中的深度、宽度比)23.Autodoping:自搀杂(外延时SUB的浓度高,导致有杂质蒸发到环境中后,又回掺到外延层)24.Back end:后段(CONTACT以后、PCM测试前)25.Baseline:标准流程26.Benchmark:基准27.Bipolar:双极28.Boat:扩散用(石英)舟29.CD:(Critical Dimension)临界(关键)尺寸。

在工艺上通常指条宽,例如POLY CD 为多晶条宽。

30.Character window:特征窗口。

半导体 标准术语

半导体标准术语

半导体是指电导率介于导体和绝缘体之间的材料。

标准术语是指在半导体领域中被广泛接受和使用的术语和定义。

以下是一些半导体领域常见的标准术语:

1. PN结:由p型半导体和n型半导体构成的结,具有整流性质。

2. 硅:半导体材料中最常用的元素之一,常用符号为Si。

3. 锗:半导体材料中常用的元素之一,常用符号为Ge。

4. 掺杂:向半导体材料中引入少量杂质,改变其电导性质的过程。

5. 芯片:由半导体材料制成的微小电子器件,常用于集成电路中。

6. 导带:半导体中的能带,带有自由电子,可导电。

7. 价带:半导体中的能带,带有能够容纳电子的轨道。

8. 势垒:在PN结中形成的电势差,阻止电流的流动。

9. 禁带宽度:导带和价带之间的能量差,决定了半导体的导电性质。

10. 整流器:利用PN结的整流性质将交流电转换为直流电的

器件。

这些是半导体领域中常见的一些标准术语,但并不包括全部。

半导体科学和技术的发展不断涌现出新的术语和概念,因此标准术语也在不断更新和发展。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

金属前介质层(PMD)金属间介质层(IMD)W塞(W PLUG)钝化层(Passivation)acceptor 受主,如B,掺入Si中需要接受电子Acid:酸actuator激励ADI After develop inspection显影后检视AEI After etching inspection蚀科后检查AFM atomic force microscopy 原子力显微AlignmentAlloy:合金AluminumAmmoniaamplifierAMUAnalogAngstrom:Anisotropicarc chamberARC:Argon(Ar)氩Arsenic(As)Arsine(AsH)ASHERAsherASIASICAspect rationATE 自动检测设备Back end:后段(CONTACT以后、PCM测试前)Backside Etch 背面蚀刻Backside 晶片背面Baseline:标准流程Beam-Current 电子束电流Benchmark:基准BGA ball grid array 高脚封装Bipolar:双极Boat:扩散用(石英)舟Cassette 装晶片的晶舟CD:critical dimension 关键性尺寸,临界尺寸Chamber 反应室Chart 图表Child lot 子批chiller 制冷机Chip (die) 晶粒Doping 掺杂Dose 剂量Downgrade 降级DRC design rule check 设计规则检查Dry Clean 干洗Due date 交期Dummy wafer 挡片E/R etch rate 蚀刻速率EE 设备工程师ELS extended life source 高寿命离子源enclosure 外壳BPSG 含有硼磷的硅玻璃Break 中断,stepper机台内中途停止键cassette 晶片盒End Point 蚀刻终点e-shower 中性化电子子发生器ET etch 蚀刻Exhaust 排气(将管路中的空气排除)Exposure 曝光extrantion electrode 高压吸极FAB 工厂fabField Oxidefilamentfilmflat aligenerflat:平边Flatnessflow velocityflow volumefluxFocus 焦距FoundryFSGFurnacegate oxidegowninggray area:灰区gyro drive 两方向偏转hard bake:后烘,坚烘,soft bake (软烘) HCI hot carrier injection 热载流子注入HDP:high density plasma高密度等离子体heat exchange 热交换机High-V oltage 高压host:主机Hot bake 烘烤ICP inductive couple plasma感应等离子体ID 辨认,鉴定IGBT 绝缘门双极晶体管images:去掉图形区域的版implant 注入Implant 植入impurity n 掺杂majority carrier n多数载流子Mask (reticle) 光罩masks, device series of n一成套光刻版material n 原料matrix n 矩阵mean n 平均值measured leak rate n 测得漏率median n 中间值memory n 记忆体Merge 合并metal n 金属Metal Via 金属接触窗MFG 制造部Mid-Current 中电流Module 部门nanometer (nm) n :纳米nanosecond (ns) n :纳秒NIT SiN 氮化硅nitride etch n :氮化物刻蚀方photomask n :光刻版,用于光刻的版photomask, negative n:反刻photomask, positive n:正刻Pilot 实验的PVD 物理气相淀积PW p-doped well P阱quad rupole lens 磁聚焦透镜quartz carrier n 石英舟。

Queue time 等待时间内层介电层(ILD)、hot carriers:热载流子hydrophilic:亲水性hydrophobic:疏水性pn junction n:pn结Pod 装晶舟与晶片的盒子Polymer 聚合物POR Process of recordpost accel 后加速器Plasma 电浆PMD premetal dielectric 电容PP p-doped plus(P+) P型重掺杂pure water nPVDQueue time显影前烘焙驻波效应R/C runcardSOGSOG填能力”以CVD临的孔洞问题Spacer :过在PLOY漏横向扩散形成的沟道效应。

LPTEOS主要用于SPACER及电容氧化层。

TEOS = Si(O C2H5)4名称:正硅酸乙脂,又称四乙氧基硅烷Si(O C2H5)4 →BIST,Built-in Self Test 内建的自测试Bus Route 总线布线Carbide碳circuit diagram 电路图Circuit 电路基准Clementine 专用共形开线设计Cluster Placement 簇布局Electromagnetic Noise 电磁噪声EMC,Elctromagnetic Compatibilt 电磁兼容EMI,Electromagnetic Interference 电磁干扰Emulation 硬件仿真Ensemble 多层平面电磁场仿真ESD 静电释放Expansion膨胀Fall Time 下降时间False Clocking 假时钟FEP 氟化乙丙烯FFT,Fast Fourier Transform 快速傅里叶变换Float License 网络浮动Ground Bounce 地弹反射GUI,Graphical User Interface 图形用户界面Harmonica 射频微波电路仿真HFSS 三维高频结构电磁场仿真HMDS (六甲基二硅胺):涂胶前处理,增加圆片衬底与光刻胶的粘附性集成电路液晶Module 液Diode 发光多芯Design非线性设ODB++ Open Data Base 公开数据库OEM 原设备制造商OLE Automation 目标连接与嵌入On-line DRC 在线设计规则检查ONO:氧化层-氮化层-氧化层介质;用作电容介质Optimetrics 优化和参数扫描OSD On Screen Display 在屏上显示Overshoot 过冲TM top mental 顶层金属层Undershoot 下冲Uniform Distribution 均匀分布Variant 派生SiO2 +4C2H4 +2H2O它的设备结构和LPSi3N4基本类似。

Under Etch 蚀刻不足USG undoped 硅玻璃vacuum 真空。

vaporizer 蒸发器W (Tungsten) 钨watt(W) 瓦。

能量单位。

WEEwell 阱。

wrench 扳手专业术语A/D [军AC PhaseAccuracyAdhesionAggressor自动光学检查ASIC装配版本输出AttributesInspectionBacklight -Period 周期Phase Alrernating LinePAL制式(逐行倒相制式)Physical Design Reuse 物理设计可重复PI,Power Integrity 电源完整性Piece-Wise-linear Source 分段线性源POD 装晶舟和晶片的盒子Preview 输出预览PSG 硼硅玻璃Pulse Width 脉冲宽度Pulsed V oltage 脉冲电压Quiescent Line 静态线Radial Array Placement极坐标方式的元件布局Reflection 反射Refractive折射Reticle 光罩Reuse 实现设计重用Rise Time 上升时间Rnging 振荡,信号的振铃Rounding 环绕振荡Rules Driven 规则驱动设计Runcard 运作卡Scratch 刮伤SDG如SDG得到源漏栅Setting 设置Settling TimeShape BaseShoveSimulationSketchSkew 偏移Solvent 溶剂Spin 旋转Sputter 溅射StripSymphonyTime domainCycle timeDamage:损伤。

对于单晶体来说,有时晶格缺陷在表面处理后形成无法修复的变形也可以叫做损伤。

Depletion implant:耗尽注入。

一种在沟道中注入离子形成耗尽晶体管的注入工艺。

(耗尽晶体管指在栅压为零的情况下有电流流过的晶体管。

)Depletion layer:耗尽层。

可动载流子密度远低于施主和受主的固定电荷密度的区域。

Depletion width:耗尽宽度。

中提到的耗尽层这个区域的宽度。

Deposition:淀积。

一种在圆片上淀积一定厚度的且不和下面层次发生化学反应的薄膜的一种方法。

design of experiments (DOE):为了达到费用最小化、降低试验错误、以及保证数据结果的统计合理性等目的,所设计的初始工程批试验计划。

develop:显影(通过化学处理除去曝光区域的光刻胶,形成所需图形的过程)diborane (BH):乙硼烷,一种无色、易挥发、有毒的可燃气体,常用来作为半导体生产中的硼源dichloromethane (CHCL):二氯甲,一种无色,不可燃,不可爆的液体。

dichlorosilane (DSC):二氯甲硅烷,一种可燃,有腐蚀性,无色,在潮湿环境下易水解的物质,常用于硅外延或多晶硅的成长,以及用在沉积二氧化硅、氮化硅时的化学气氛中。

die:硅片中一个很小的单位,包括了设计完整的单个芯片以及芯片邻近水平和垂直方向上的部分划片槽区域。

dielectric:Ⅰ)介质,一种绝缘材料;Ⅱ)用于陶瓷或塑料封装的表面材料,可以提供电绝缘功能。

diffused layer:扩散层,即杂质离子通过固态扩散进入单晶硅中,在临近硅表面的区域形成与衬底材料反型的杂质离子层。

disilane (SiH):乙硅烷,一种无色、无腐蚀性、极易燃的气体,燃烧时能产生高火焰,暴露在空气中会自燃。

在生产光电单元时,乙硅烷常用于沉积多晶硅薄膜。

drive-indry etch程。