第七章_常用Verilog语法之五

Verilog中的一些语法和技巧

Verilog中的⼀些语法和技巧1、.2、.3、Reg型的数据类型默认初始值为X。

reg型数据可以赋正值也可以赋负值,但是当⼀个reg型数据是⼀个表达式的操作数的时候,他的值被当做⽆符号数及正值。

4、在数据类型中?和Z均表⽰⾼阻态。

5、Reg型只表⽰被定义的信号将⽤在“always”模块内,并不是说reg型⼀定是寄存器或触发器的输出。

虽然reg型信号常常是寄存器或触发器的输出但是并不⼀定总是这样。

6、Verilog语⾔中没有多维数组的存在。

Memory型数据类型是通过扩展reg型数据的弟⼦和范围来⽣成的。

其格式如下reg[n-1:0]存储器名[m-1:0];7、在除法和取余的运算中结果的符号和第⼀个操作数的符号位是相同的。

8、不同长度的数据进⾏运算:两个长度不同的数据进⾏位运算时,系统会⾃动地将两者按有端对齐,位数少的操作数会在相应的⾼位⽤0填满以便连个操作数安慰进⾏操作。

9、= = =与!= = =和= =与!= =的区别:后者称为逻辑等是运算符,其结果是2个操作数的值决定的。

由于操作书中某些位可能不定值x和⾼阻态z结果可能是不定值x。

⽽ = = =和!= = =运算符对操作数的⽐较时对某些位的⾼阻态z和不定值x也进⾏⽐较,两个操作数必须完全⼀致,其结果才是1,否则是0.10、⾮阻塞和阻塞赋值⽅式:⾮阻塞赋值⽅式(如a<=b)上⾯语句所赋得变量值不能⽴即被下⾯语句所⽤,(2)快结束后才能完成这次赋值操作 3在编写克综合的时序逻辑模块时这是最常⽤的赋值⽅法。

阻塞赋值(如a=b)赋值语句执⾏完后,块才结束 2 b的值在赋值语句完成后⽴即执⾏ 3在时序逻辑使⽤中,可能产⽣意想不到的结果。

11、模块的描述⽅式:(RTL为寄存器传输级描述)“(1)数据流描述⽅式:数据流⾏描述主要⽤来描述组合功能,具体⽤“assign”连续赋值语句来实现。

分为两种a、显式连续赋值语句;连线型变量类型[连线型变量为快]连线型变量名Assign #(延时量)连线型变量名=赋值表达式;显式连续赋值语句包含了两条语句;第⼀条是对连线型变量的进⾏类型说明的说明语句;第⼆句是对这个已得到声明的连线型变量进⾏连续赋值语句。

(完整版)VerilogHDL数字设计与综合(第二版)第七章课后习题答案

1.声明一个名为oscillate的寄存器变量并将它初始化为0。

使其每30个时间单位进行一次取反操作。

不要使用always语句。

提示:使用forever循环。

答:代码如下:reg oscillate;initialbeginoscillate<=0;forever #30 oscillate<=~oscillate;end2.设计一个周期为40个时间单位的时钟信号,其占空比为25%。

使用always和initial块进行设计。

将其在仿真0时刻的值初始化为0。

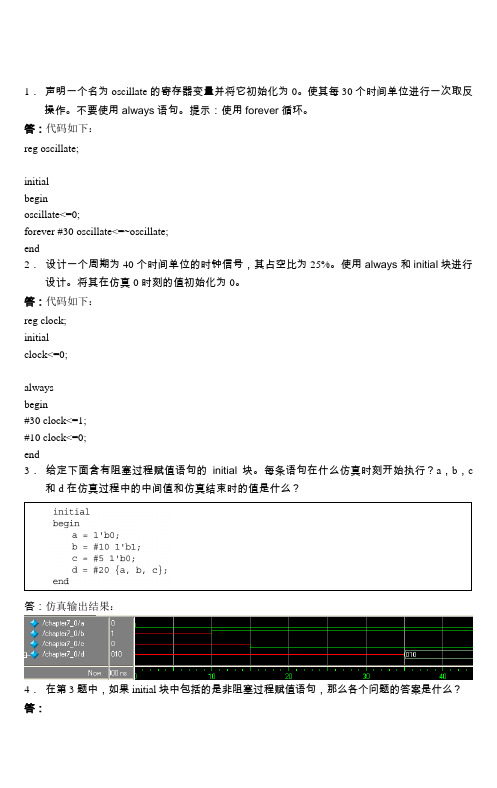

答:代码如下:reg clock;initialclock<=0;alwaysbegin#30 clock<=1;#10 clock<=0;end3.给定下面含有阻塞过程赋值语句的initial块。

每条语句在什么仿真时刻开始执行?a,b,c 和d在仿真过程中的中间值和仿真结束时的值是什么?答:仿真输出结果:4.在第3题中,如果initial块中包括的是非阻塞过程赋值语句,那么各个问题的答案是什么?答:第7章行为级建模79最终d没有输出,因为d<= #20 {a,b,c};语句执行的是先将a,b,c取值存储,在20个时间单位后将存储的值赋给d,因为b,c在初始时刻没有值,所以d值也是不确定的。

5.指出在下面的Verilog代码中各条语句的执行顺序。

其中是否含有不确定的执行顺序?a,b,c和d的最终值是什么?答:先执行a=1’b0,b=1’b1,然后执行#0 c=b,#0 d=a,执行顺序不确定,最终输出结果a=0,b=1,c=1,d=0. 6.在下面的例子中,d的最终值是什么?答:仿真输出波形如下,最终输出结果d=1。

0时刻b|c的值是1,在25个时间刻度后赋给d。

7.使用带有同步清零端的D触发器(清零端高电平有效,在时钟下降沿执行清零操作)设计一个下降沿触发的D触发器,只能使用行为语句。

提示:D触发器的输出q应当声明为寄存器变量。

veriloga基础语法

veriloga基础语法VerilogA是一种硅谷团队开发的建模语言,它被广泛应用于集成电路(IC)的设计和仿真中。

本文旨在介绍VerilogA的基础语法。

1. 模块声明在VerilogA中,每个模块都需要进行声明。

声明的语法如下:module 模块名(输入端口1,输入端口2,...输入端口n,输出端口1,输出端口2,...输出端口m);<模块定义代码>endmodule其中,模块名可以由字母、数字和下划线组成,不能以数字开头;输入端口和输出端口可以是标量或向量。

2. 参数声明VerilogA允许在模块中声明参数,以便在实例化时进行配置。

语法如下:parameter 参数名 = 值;参数可以通过assign语句进行连接,也可以在实例化时进行配置。

3. 变量声明在VerilogA中,可以使用不同的变量类型进行声明,如实数、整数、布尔值等。

real: 实数类型,用于存储实数值。

integer: 整数类型,用于存储整数值。

boolean: 布尔类型,用于存储真/假值。

语法如下:real 变量名;integer 变量名;boolean 变量名;4. 函数和任务在VerilogA中,可以使用函数和任务来实现特定的功能。

函数是一段可重用的代码,它接收输入参数并返回一个值。

函数的语法如下:function 返回类型函数名(输入参数);<函数定义代码>return 返回值;endfunction任务是一段可重用的代码,不返回值,但可以通过参数进行输入和输出。

任务的语法如下:task 任务名(输入参数);<任务定义代码>endtask5. 运算符VerilogA支持各种常见的数学和逻辑运算符,如加减乘除、取余、与或非等。

加法运算符:+减法运算符:-乘法运算符:*除法运算符:/取余运算符:%与运算符:&&或运算符:||非运算符:!6. 控制结构在VerilogA中,可以使用if-else、for、while等控制结构来实现条件判断和循环。

verilog 运算符号

verilog 运算符号Verilog 是一种硬件描述语言(HDL),常用于数字电路的设计与验证。

在 Verilog 中,运算符是用于执行各种操作的特殊符号。

本文将介绍常用的 Verilog 运算符,包括算术运算符、位运算符、关系运算符、逻辑运算符、条件运算符和位选择运算符。

1. 算术运算符:- 加法:用 "+" 表示,例如 A + B- 减法:用 "-" 表示,例如 A - B- 乘法:用 "*" 表示,例如 A * B- 除法:用 "/" 表示,例如 A / B- 求余:用 "%" 表示,例如 A % B2. 位运算符:- 位与:用 "&" 表示,例如 A & B- 位或:用 "|" 表示,例如 A | B- 位异或:用 "^" 表示,例如 A ^ B- 位取反:用 "~" 表示,例如 ~A- 左移:用 "<<" 表示,例如 A << 1- 右移:用 ">>" 表示,例如 A >> 13. 关系运算符:- 等于:用 "==" 表示,例如 A == B- 不等于:用 "!=" 表示,例如 A != B- 大于:用 ">" 表示,例如 A > B- 大于等于:用 ">=" 表示,例如 A >= B- 小于:用 "<" 表示,例如 A < B- 小于等于:用 "<=" 表示,例如 A <= B4. 逻辑运算符:- 逻辑与:用 "&&" 表示,例如 A && B- 逻辑或:用 "||" 表示,例如 A || B- 逻辑非:用 "!" 表示,例如 !A5. 条件运算符:- 三目运算符:用 "?" 和 ":" 表示,例如 (A > B) ? A : B6. 位选择运算符:- 指定位置运算符:用 "[]" 表示,例如 A[3:0] 表示提取 A 中的3-0 位- 拼接运算符:用 "{}" 表示,例如 {A, B} 表示将 A 和 B 拼接在一起以上是 Verilog 中常用的运算符。

Verilog中各种语句含义及用法简述

Verilog中各种语句含义及⽤法简述Verilog中各种语句含义及⽤法简述⼀般认为Verilog HDL在系统级抽象⽅⾯⽐VHDL略差⼀些,⽽在门级开关电路描述⽅⾯⽐VHDL要强的多写了第⼀个verilog程序,是⼀个加法器内容如下module adder(count,sum,a,b,cin);input[2:0] a,b;input cin;output count;output [2:0] sum;assign{count,sum}=a+b+cin;endmodule开始编译出现了⼏次错误,后来发现给实体的命名和程序中实体要⼀致⽽且⼤⼩写要⼀样,整个程序是嵌套再module和endmodule当中的⽽其中的注释和C/C++类似,⽤//和来标明module compare(equal,a,b);output equal;input [1:0] a,b;assign equal=(a==b)?1:0;//和C语⾔中的相同endmoduleverilog的基本设计单元是“模块(BLOCK)”。

⼀个模块由两个部分组成,⼀部分描述端⼝,⼀部分描述逻辑功能,即定义输⼊是如何影响输出的。

如下module block(a,b,c,d);input a,b;output c,d;assign c="a|b";assign d="a"&b;endmodule模块中最重要的部分是逻辑功能定义。

有三种⽅法可以再模块中产⽣逻辑。

1、⽤“assign”声明语句如:assign a="b"&c;2、⽤实例元件,如同调⼊库元件⼀样如:and and_inst(q,a,b);3、⽤“always”块如:always @(posedge clk or posedge clr) //always块⽣成了⼀个带有异步清除端的D触发器。

beginif(clr) q<=0;else if(en) q<=d;end采⽤assign语句是最常⽤的⽅法之⼀。

FPGA笔记之verilog语言(基础语法篇)

FPGA笔记之verilog语言(基础语法篇)笔记之verilog语言(基础语法篇)写在前面:verilogHDL语言是面对硬件的语言,换句话说,就是用语言的形式来描述硬件线路。

因此与等软件语言不同,假如想要在实际的中实现,那么在举行verilog语言编写时,就需要提前有个硬件电路的构思和主意,同时,在编写verilog语言时,应当采纳可综合的语句和结构。

1. verilog 的基础结构1.1 verilog设计的基本单元——module在数字电路中,我们经常把一些复杂的电路或者具有特定功能的电路封装起来作为一个模块用法。

以后在运用这种模块化的封装时,我们只需要知道:1.模块的输入是什么;2.模块的输出是什么;3.什么样的输入对应什么样的输出。

而中间输入是经过什么样的电路转化为输出就不是我们在用法时需要特殊重视的问题。

当无数个这样的模块互相组合,就能构成一个系统,解决一些复杂的问题。

verilog语言的基础结构就是基于这种思想。

verilog中最基本的模块是module,就可以看做是一个封装好的模块,我们用verilog来写无数个基本模块,然后再用verilog描述多个模块之间的接线方式等,将多个模块组合得到一个系统。

那么一个module应当具有哪些要素呢?首先对于一个module,我们应当设计好其各个I/O,以及每个I/O的性质,用于与模块外部的信号相联系,让用法者知道如何连线。

第二,作为开发者,我们需要自己设计模块内部的线路来实现所需要的功能。

因此需要对模块内部浮现的变量举行声明,同时通过语句、代码块等实现模块的功能。

综上所述,我们把一个module分成以下五个部分:模块名端口定义I/O解释第1页共9页。

Verilog 常用语法及举例

常用语句之五 for

for (i == 0; i< 100 ; i= i+1)

1,用于循环语句中。 2,循环次数必须是个常量。 3,i为integer(整型)类型。

小练习

1,分频电路设计,设计一个8分频。 2,设计一个0~23的计数器,在数码管上显示出来。 3,改进上述计数器,增加一个拨码输入,当拨码 为0时,数码管上显示一个固定值。当拨码为1时, 计数器继续计数。 4,按键去抖设计。每按键一次,数码管显示加1。 5,电子密码锁设计。

阻塞赋值与非阻塞赋值

阻塞赋值用在组合逻辑中。在always中使用 符号 = 非阻塞赋值用在时序逻辑中。在always中使 用符号 <=

阻塞赋值与非阻塞赋值

阻塞赋值 always @ (a,b,c) begin b = a; c = b; end

a

a

非阻塞赋值

always @ (posedge clk) begin b <= a; c <= b; end

常用语句之三 begin end

If (a == b)

begin c <= d; e <= f; g <= h; end 1,begin—end里面的所 有语句都是顺序执行。

常用语句之四 assign

assign a = b & c; assign a = (d ==1’b0) ? 0 : 1;

a b c b c

组合逻辑和时序逻辑

时序逻辑

时序逻辑需要时钟,输入变化不会引起输出立即变化。 而是要参考时钟沿的变化。 只能用非阻塞赋值的always语句实现。 结果会生产寄存器。

verillog语法

verillog语法

Verilog是一种硬件描述语言,用于描述数字电路和系统。

以下是Verilog 的基本语法:

1. 注释:Verilog中的注释以“//”开头,一直延续到该行的末尾。

另外,多行注释以“/”开始,以“/”结束。

2. 数字表达方式:在Verilog中,数字的表示方式可以是十进制、八进制或二进制。

例如,8'b表示一个8位的二进制数。

3. 数据类型:Verilog中有四种数据类型,分别是wire(线网型)、reg (寄存器型)、integer(整数型)和parameter(参数型)。

其中,wire 类型用于表示物理连线,reg类型表示数据存储单元。

4. 模块:Verilog中的模块是电路的基本单元,由输入、输出和内部信号组成。

模块的端口用于连接外部信号,内部信号用于描述电路的行为。

5. 语句:Verilog中的语句可以分为赋值语句、控制语句和过程语句。

赋值语句用于给变量赋值,控制语句用于控制流程,过程语句用于描述电路的行为。

6. 任务和函数:Verilog中的任务和函数用于实现特定的功能。

任务和函数的使用可以减少代码的重复,提高代码的可维护性。

7. 系统任务和系统函数:系统任务和系统函数是Verilog提供的用于实现特定系统级功能的任务和函数。

例如,$display系统任务用于在仿真时显示信息。

以上是Verilog的基本语法,当然还有更多的语法和概念需要学习和掌握。

建议查阅相关的Verilog教程或书籍,以深入了解Verilog的语法和用法。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2006-3-22

宏定义 `define `undef

• • • • • 宏名建议大写 有效范围为定义命令之后到源文件结束 引用时加“~” 可以刷新宏定义 不加;

2006-3-22

29

文件包含处理 `include

• 一个源文件将另一个源文件的全部内容 包含进来。 • `include “文件名” • 常用的宏定义或task组成一个文件,用 include命令包含到源文件中

18

$time

• $time显示时刻受时间尺度比例的影响, 即$time输出的时刻总是时间尺度的倍数 • $time总是输出整数

2006-3-22

19

$realtime

~timescale 10ns/1ns module test; reg set; parameter p=1.6; initial $monitor ($time,,”set=“,set); #p set = 0; #p set = 1; end 2006 -3-22 endmodule

监视信号值—$monitor

2006-3-22

15

监示信号值—$monitor

2006-3-22

16

仿真时间

访问仿真时间 • • • • • $time,$realtime,和$stime函数返回当前仿真时间。 这些函数的返回值使用调用模块中`timescale定义的 时间单位 $time返回一个64位整数时间值。 $stime返回一个32位整数时间值。 $realtime返回一个实数时间值。 $stime函数返回一个32位整数时间值。对大于232 的时间,返回模232的值。使用它可以节省显示及打 印空间。

31

条件编译~ifdef, ~else, ~endif

`ifdef 宏名 语句块1 `else 语句块2 `endif

2006-3-22

33

example

module compile(out,A,B); output out; input A,B; `ifdef add assign out=A+B; `else assign out=A-B; `endif endmodule

显示信号值—$write和$strobe

2006-3-22

14

• $monitor持续监视参数列表中的变量。 • 在一个时间片中,参数表中任何信号发生变化, $monitor将在仿真时间前进前显示参数表的信号值。 • 后面的$monitor将覆盖前面的$monitor。 • 可以用系统任务$monitoron和$monitoroff控制持续监 视。 • $monitor支持多种基数。缺省为十进制。 $monitor ($ time, “%b \t %h \t %d \t %o”, sig1, sig2, sig3, sig4);

显示信号值 — $display

2006-3-22

9

显示信号值 — $display

格式符

%h %o %d %b %c %s %v %m %t hex octal decimal binary ASCII string strength module time

转义符

\t \n \\ tab 换行 反斜杠 制数

2006-3-22

5

• 文件输入/输出类 $fopen $fclose ; $fdisplay $fwrite $fstrobe $fmonitor ; $readmem

2006-3-22

6

系统任务和函数

$<标识符> ‗$‘ 符号表示 Verilog 的系统任务和函数 常用的系统任务和函数有下面几种: 1) $time //找到当前的仿真时间 2) $display, $monitor //显示和监视信号值的变化 3) $stop //暂停仿真 4) $finish //结束仿真

2006-3-22 7

验证系统中的任务(task)及函数(function)

• Verilog读取当前仿真时间的系统函数 $time $stime $realtime • Verilog支持文本输出的系统任务: $display $strobe $write $monitor

2006-3-22 8

2006-3-22

\" \< 1-3 digit octal number> %0d 双引号 上述的ASCII表示 无前导0的十进

10

module disp; initial begin $display(“\\\t%%\n\”\123”); end endmodule

example

2006-3-22

20

文件输出

... integer MCD1; MCD1 = $fopen("<name_of_file>"); $fdisplay( MCD1, P1, P2, .., Pn); $fwrite( MCD1, P1, P2, .., Pn); $fstrobe( MCD1, P1, P2, .., Pn); $fmonitor( MCD1, P1, P2, .., Pn); $fclose( MCD1); ...

11

自动调节输出数据宽度

• $display (“=%0h =%0h”data, addr);

2006-3-22

12

显示信号值—$write和$strobe

• $write与$display相同,不同的是不会自动换行。 $write($time, ―%b \t %h \t %d \t %o \t‖, sig1, sig2, sig3, sig4); • $strobe与$display相同,不同的是在仿真时间前进之 前的信号值。而$display和$write立即显示信号值。也 就是说$strobe显示稳定状态信号值,而$display和 $write可以显示信号的中间状态值。 $strobe($time, ―%b \t %h \t %d \t %o \t‖, sig1, sig2, sig3, sig4); • $write和$strobe都支持多种数基,缺省为十进制。 $writeb $strobeb $writeo $strobeo $writeh $strobeh 13 2006-3-22

2006-3-22 22

系统任务$finish

• • • • • $finish; $finish(n); 0:不输出任何信息 1:输出当前仿真时刻和位置 2:输出当前仿真时刻,位置和仿真过程 中所用memory及CPU时间的统计

23

2006-3-22

系统任务$stop

• $stop; • $stop(n); • 仿真器设置为暂停模式

2006-3-22 17

$time

~timescale 10ns/1ns module test; reg set; parameter p=1.6; initial $monitor ($time,,”set=“,set); #p set = 0; #p set = 1; end 2006 -3-22 endmodule

-------------------------------------------------------

例: initial $monitor($time,,”a=%b, b=%h”, a, b);

//每当a 或b值变化时该系统任务都显示当前的仿真时刻并分别用二进制 和十六进制显示信号a和 b的值

2006-3-22

3

系统任务和系统函数分类

• 显示、探测、监视类系统任务: $write $display $write $display 遇到语句执行 $display(“格式控制字符串”,输出变量名表项); • 进程控制类系统任务:$finish $stop

2006-3-22

4Hale Waihona Puke • 仿真时标类系统任务 $printtimescale $timeformat • 仿真时标类系统函数 $time $stime $realtime

• $fopen打开参数中指定的文件并返回一个32位无符号 整数 MCD,MCD是与文件一一对应的多通道描述符。如果文 件不能打开并进行写操作,它返回0。 • $fclose关闭MCD指定的通道。 • 输出信息到log文件和标准输出的四个格式化显示任务 ($display, $write, $monitor, $strobe)都有相对应的任务用 于向指定文件输出。 • 这些对应的任务($fdisplay,$fwrite,$fmonitor,$fstrobe)的 参数形式与对应的任务相同,只有一个例外:第一个参数 必须是一个指定向何哪个文件输出的MCD。MCD可以是 一个表达式,但其值必须是一个32位的无符号整数。这个 值决定了该任务向哪个打开的文件写入。 • MCD可以看作由32个标志构成的组,每个标志代表一个 单一的输出通道。

第七章 常用Verilog语法 (五)

周晓波 北京交通大学电子信息学院 xbzhou@ 51683626

2006-3-22 1

内容提要

• 系统函数与任务 • 编译预处理

2006-3-22

2

系统任务与系统函数分类

• • • • • 输入输出控制类系统任务 模拟时间标记类系统函数 进程控制类系统任务 文件读写类系统任务 其他

• $fopen打开一个文件并返回一个多通道描述符(MCD)。

– MCD是与文件唯一对应的32位无符号整数。 – 如果文件不能打开并进行写操作,MCD将等于0。 – 如果文件成功打开,MCD中的一位将被置位。

• 以$f开始的显示系统任务将输出写入与MCD相对应的文件中。

2006-3-22 21

文件输出

2006-3-22

24

系统任务$random

• 提供了一个产生随机数的手段,函数被 调用时返回一个32位的随机数(带符号)