南京理工大学本科电路笔记dxja12_4

南理工电工电子综合实验二

南理工电工电子综合实验二Document number:WTWYT-WYWY-BTGTT-YTTYU-2018GT数字电子计时报警器电路设计班级:学号:姓名:彭浩洋一、实验内容简介及设计要求综合利用所学集成电路的工作原理和使用方法,在单元电路的基础上进行小型数字系统设计。

使用集成电路芯片,设计并实际组装一个一小时内的数字计时器,可以完成0分00秒~59分59秒的计时功能,并在控制电路的作用下具有清零、快速校分、定点报时的功能。

通过综合实验,加深对数字逻辑电路基本概念的理解,掌握数字电路设计的一般方法,进一步培养分析问题解决问题的能力和实际动手能力,提高设计电路和调试电路的实验技能。

实验具体需要实现如下的设计要求:1.应用CD4511BCD码译码器﹑LED双字共阴显示器﹑300Ω限流电阻设计﹑安装调试四位BCD译码显示电路实现译码显示功能。

2.应用NE555时基电路、3KΩ、1KΩ电阻、0·047UF电容和CD4040计数分频器设计,安装,调试秒脉冲发生器电路(输出四种矩形波频率f1=1HZf2=2HZf3≈≈1000Hz)。

500Hzf43.应用CD4518BCD码计数器、门电路,设计、安装、实现00′00″---59′59″时钟加法计数器电路。

4.应用门电路,触发器电路设计,安装,调试校分电路且实现校分时停秒功能(校分时F2=2Hz)。

设计安装任意时刻清零电路。

5.应用门电路设计、安装、调试报时电路59′53″,59′55″,59′57″低声报时(频率f3≈500Hz),59′59″高声报时(频率f4≈1000Hz)。

整点报时电路。

H=59′53″·f3+59′55″·f3+59′57″·f3+59′59″·f46.联接试验内容1.—5.各项功能电路,实现电子计时器整点计时﹑报时、校分、清零电路功能。

二、数字电子计时器电路设计框图数字计时器是由脉冲发生器电路、译码显示器、计数电路和控制电路等几部分组成,其中的控制电路按照设计要求可以由校分电路、清零电路和报时电路组成。

南京理工大学本科电路笔记dxja8_2

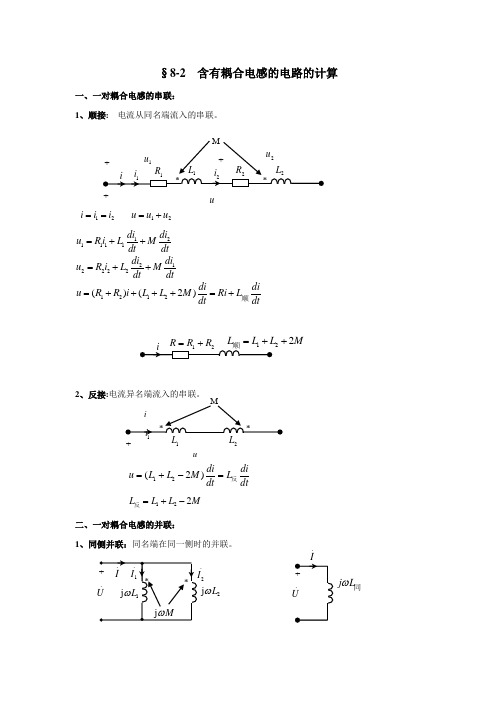

§8-2 含有耦合电感的电路的计算一、一对耦合电感的串联:1、顺接: 电流从同名端流入的串联。

1212i i i u u u ===+121111di diu R i L M dt dt =++ 212222di diu R i L M dt dt=++1212()(2)di diu R R i L L M Ri L dt dt=++++=+顺2、反接:电流异名端流入的串联。

12(2)di di u L L M L dt dt=+-=反 122L L L M =+-反二、一对耦合电感的并联:1、同侧并联:同名端在同一侧时的并联。

R R R =+ 122L L L M =++2j L ω.2.j L ω同1L2RLM+ _+_ u1u 2uu12...1112...2221...122...12122121222U j L I j M I U j L I j M I I I I L L M U j I j L IL L M L L M L L L Mωωωωωω=+=+=+-==+--=+-同同2、异侧并联:同名端不在同一侧时的并联。

212121212122212121212............220............20.......20............0.......22L L M L L L L L ML L L L L M L L L M M L L M L L M L L M L L M L L M-=>+++=++>=+-><--=>=><+-++同异顺反同反异 三、耦合系数k :反映耦合松紧程度。

kM M ω==四、一对耦合电感的三端联接 1、同名端相接2j L ω.2j L ω异121312123212di di u L M dt dt di diu L M dt dti i i =+=+=+在u 13表达式中消去i 2;在u 23表达式中消去i 1,经整理后,得3121131132122322()()di di di diu L M L M M dt dt dt dtdi di di diu L M L M M dt dt dt dt =+=-+=+=-+ 由此式画出去耦等效电路,如下图。

南理工模电22

(2) 恒压降模型

如果外加正向电压远远大于二极管的管压 降,则二极管导通且导通压降为恒定值。 外加反向电压时,二极管截止且iD=0。

导通压降硅锗管管::

vD vD

0.7V 0.3V

(3) 小信号模型

VD1 VDQ vD I D1 I DQ iD

rd

vD iD

(3) 小信号模型

如果工作中,二极管的

外加正向电压升高,N 区空穴积累将增加, P区电子的积累也同样 增加,相当于电容的 充电。反之,外加正 向电压降低时,相当 于电容的放电。

外加反向电压时,由于扩散电流小,扩散电容可忽略

(c) PN结和二极管的高频等效电路

r 结r电结阻电阻

r'

半导体体电阻和 电极接触电阻

C 扩C散扩和势散垒和电势容垒电容

外加反向电 压时,空间 电荷区宽度 变化更大, 势垒电容效 应更明显, 但其值减小

外加正向电压降低 空间电荷区变宽 表明有部分电子和空穴离开了空间电荷区, 相当于电容的放电

(b) 扩散电容CD

PN结的扩散电容是用来描述外加电压作用下载流子 在扩散过程中的积累情况。

外加正向电压时,P区 空穴扩散进入N区后会 形成浓度梯度分布,越 靠近PN结边缘的空穴 浓度越高,即N区有空 穴的积累。同样,电子 在P区的情况也类似。

(4) 极间电容

若PN结两端加上随时间变化的电压,PN结会 显示电容特性。结电容分为两种:势垒电容 CB和扩散电容CD。

(a) 势垒电容CB

PN结的势垒电容是用来描述势垒区的空间电 荷随电压变化而产生的电容效应的。

外加正向电压升高 空间电荷区变薄

表明有部分电子和空穴进入空间电荷区中和 了施主正离子和受主负离子,相当于电子和 空穴向电容充电

南京理工大学电工电子综合实验

电工电子综合实验实验报告数字计时器设计姓名:学号:学院:自动化学院专业:自动化2013-9-6一、实验目的:1、掌握常见集成电路实现单元电路的设计过程。

2、了解各单元再次组合新单元的方法。

二、实验要求:实现0分0秒到59分59秒的可整点报时的数字计时器。

三、实验内容:1、设计实现信号源的单元电路。

2、设计实现0分0秒到59分59秒的计时单元电路。

3、设计实现快速校分单元电路,含防抖动电路。

4、加入任意时刻复位单元电路。

5、设计实现整点报时的单元电路。

四、实验所用元件及功能介绍元件型号数量NE555 1片CD4040 1片CD4518 2片CD4511 2片74LS00 3片74LS20 1片74LS21 3片74LS74 1片电容0.047uf 1个电阻1504个电阻1k1个电阻3k1个单字屏共阴极数码管2块蜂鸣器1个开关2个2、主要芯片引脚图及功能表2.2.1、CD4511译码器图2.2.1 CD4511译码器引脚图表2.2.1 CD4511译码器功能表输入输出LT BI LE D4 D3 D2 D1 g f e d c b a 字符测灯0 ×××××× 1 1 1 1 1 1 1 8 灭零 1 0 ×0 0 0 0 0 0 0 0 0 0 0 消隐锁存 1 1 1 ××××显示LE=0→1时数据译码1 1 0 0 0 0 0 0 1 1 1 1 1 1 0 1 1 0 0 0 0 1 0 0 0 0 1 1 0 1 1 1 0 0 0 1 0 1 0 1 1 0 1 1 2 1 1 0 0 0 1 1 1 0 0 1 1 1 1 3 1 1 0 0 1 0 0 1 1 0 0 1 1 0 4 1 1 0 0 1 0 1 1 1 0 1 1 0 1 5 1 1 0 0 1 1 0 1 1 1 1 1 0 0 6 1 1 0 0 1 1 1 0 0 0 0 1 1 1 7 1 1 0 1 0 0 0 1 1 1 1 1 1 1 8 1 1 0 1 0 0 1 1 1 0 0 1 1 1 92.2.2、CD4518计数器图2.2.2 CD4518BCD码计数器引脚图表2.2.2 CD4518BCD码计数器功能表:输入输出CR CP EN Q3 Q2 Q1 Q0 清零 1 ××0 0 0 0 计数0 ↑ 1 BCD码加法计数保持0 ×0 保持计数0 0 ↓BCD码加法计数保持0 1 ×保持2.2.3、CD4040分频器图2.2.3 CD4040分频器引脚图2.2.4、NE555定时器图2.2.2 NE555定时器引脚图表2.2.2 NE555定时器功能表Vi1(引脚6) Vi2(引脚2) VO(引脚3) (引脚4 )0 ××01 >2/3Vcc >1/3Vcc 01 <2/3 Vcc <1/3Vcc 11 <2/3 Vcc >1/3Vcc 不变2.2.5、74LS74 D触发器图2.2.5 74LS74D触发器引脚图表2.2.5 74LS74D触发器功能表输入输出CP D清零×0 1 ×0 1 置“1”× 1 0 × 1 0 送“0”↑ 1 1 0 0 1 送“1”↑ 1 1 1 1 0 保持0 1 1 ×保持不允许×0 0 ×不确定2.2.6、74LS00 双四与非门图2.2.6 74LS00双四与非门引脚图2.2.7、74LS20 四入双与非门图2.2.7 74LS20 四入双与非门引脚图2.2.8、74LS21四入双与门图2.2.8 74LS21四入双与门引脚图3、电子计时器设计原理3.1、各部分电路解析3. 1.1、脉冲发生电路脉冲发生电路即为电子计时器产生脉冲的电路,本文采用NE555振荡器和CD4040分频器产生实验所需要的脉冲信号频率其中:f0=1.44/[(R1+2R2)C]=4.38kHz R1=1KΩ,R2=3KΩ,C=0,047uF。

02受控源和电阻等效变换

1.7 受控源

受 控 源的分类

电压控制电流源 (VCCS: Voltage Controlled Current Source)

.1 + i1=0 . u_ 1

1’

i2 . 2

gu1

+ u2

i2 gu1

._ 2’

g — 电导量纲:转移电导

电路

南京理工大学电光学院

1.7 受控源

受 控 源的分类

电路

南京理工大学电光学院

1.7 受控源

R1 i1

i2 R2

i2 i1

三极管在一定条件下可用下图所示的模型表示:

R1 i1

i2 R2

i1

电路

南京理工大学电光学院

1.7 受控源

受控源与独立源的区别

独立电源可作电路的输入或激励,它为电路提

供按给定时间函数变化的电压和电流,从而在电

路中产生电压和电流。 受控源则描述电路中两条支路电压和电流间的

20Ω

+ 140V _

a

6A d

5Ω

6Ω

+

_ 90V

10A

c 4A

+140V

简化图:

b

a

20Ω

5Ω

6Ω

6A d

+90V

10A

b

电路

南京理工大学电光学院

1.6 电位的计算

c 4A

20Ω

+ 140V _

a

6A d

5Ω

6Ω

+

_ 90V

10A

b

各节点电位:

U b 0V U a 610 60V U c 140V U d 90V

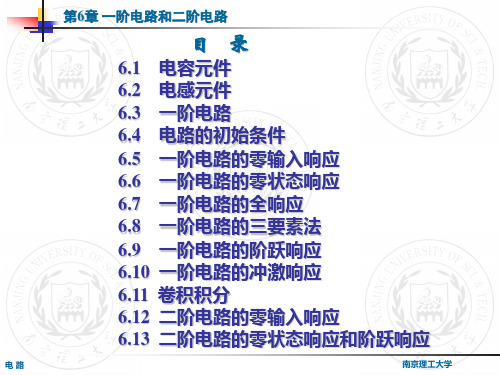

第6章 一阶电路和二阶电路

6.4 电路的初始条件

换路定理 换路:改变电路状态的统称。如:

1 . 电路接通、断开电源

2 . 电路中电源电压的升高或降低

3 . 电路中元件参数的改变

…………..

电路 南京理工大学

6.4 电路的初始条件

换路定理: 在换路瞬间,电容上的电压、 电感中的电流不能突变。

设:t=0 时换路

0 ---

南京理工大学

6.5 一阶电路的零输入响应

3、能量变化

+ uR _

R

iC C uC

+

uC (t ) U 0e

t RC

t 0

t RC

_

duC U0 iC (t ) C e dt R

t 0

2 WR iC ( t ) Rdt 0

0

U 0 t 2 1 2 ( e ) Rdt CU 0 WC (0) R 2

换路前瞬间

0 --- 换路后瞬间

则:

uC (0 ) uC (0 )

i L (0 ) i L (0 )

电路 南京理工大学

6.4 电路的初始条件

初始值的确定

初始值(起始值):设t =0时换路,则电路中 u、i在 t =0+ 时的大小就称电路的初始值。 求解要点:

uC (0 ) uC (0 ) i L (0 ) i L (0 )

电路 南京理工大学

6.4 电路的初始条件

初始值的计算

2. 画0+时的等效电路

uC (0 ) uC (0 ), iL (0 ) iL (0 )

换路前后电压(流)不变的为电压(流)源: C — 电压源, L — 电流源

南京理工大学本科电路笔记dxja5_3

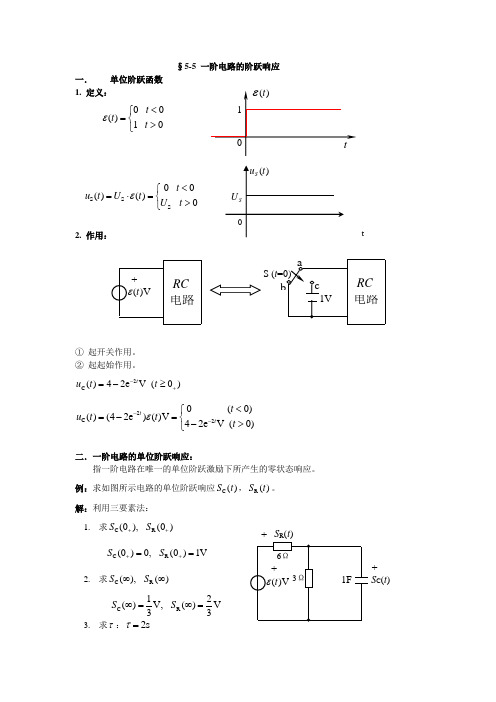

§5-5 一阶电路的阶跃响应一.单位阶跃函数 1. 定义: 00()10t t t ε<⎧=⎨>⎩S S S 00()()0t u t U t U t ε<⎧=⋅=⎨>⎩2. 作用:① 起开关作用。

② 起起始作用。

2C ()42e V (0)t u t t -+=-≥2C 20(0)()(42e )()V 42e V (0)ttt u t t t ε--<⎧=-=⎨->⎩二.一阶电路的单位阶跃响应:指一阶电路在唯一的单位阶跃激励下所产生的零状态响应。

例:求如图所示电路的单位阶跃响应C ()S t ,R ()S t 。

解:利用三要素法: 1. 求C R (0),(0)S S ++C R (0)0,(0)1V S S ++==2. 求C R (),()S S ∞∞C R 12()V,()V 33S S ∞=∞=3. 求τ:2s τ=S (t C (t ) _S (t )_t2C 1()(1e )()3t S t t V ε-∴=-2R 21()(e )()V 33tS t t ε-=+零状态(输入)响应是线性响应,全响应不是S S ()()u t U t ε=⋅ C S C ()()u t U S t =⋅ R S R ()()u t U S t =⋅0()t t ε-=S ()()(1)3(2)(4)u t t t t t εεεε=+---+-四.一阶电路的延时单位阶跃响应指一阶电路在唯一的延时单位阶跃激励下所引起的零状态响应。

如前例电路在延时单位阶跃函数激励下,02C 001()(1e )()V3t tS t t t t ε---=--由于零状态响应为线性响应,满足齐性原理和叠加定理,所以前例电路在上述分段函数作用下的零状态响应为:1242222C 1111()(1e )()(1e )(1)(3)(1e )(2)(1e )(4)V3333t t t t u t t t t t εεεε-------=-+--+-⨯--+--若该电路中已知:C (0)2V u =,'"C C C ()u t u u =+,"2C2e t u -=,'u 为上述所示。

南京理工大学电工电子综合实验II讲解

南京理工大学电子电工综合实验II2015/10/02一、实验要求实现从00′00″到59′59″的多功能数字计时器,并且满足规定的清零,快速校分以及报时功能的要求。

二、实验内容1.应用CD4511BCD 码译码器、LED 双字共阴显示器、300Ω限流电阻设计、安装调试四位BCD 译码显示电路实现译码显示功能。

2.应用NE555时基电路、3k Ω、1k Ω电阻、0.047μF 电容和CD4040计数分频器设计,安装,调试秒脉冲发生器电路(输出四种矩形波频率 f 1=1Hz f 2=2 Hz f 3≈500 Hz f 4≈1000 Hz )。

3.应用CD4518BCD 码计数器、门电路设计、安装、实现00′00″——59′59″时钟加法计数器电路。

4.应用门电路,触发器电路设计,安装,调试校分电路且实现校分时停秒功能(校分时f 2=2H Z )。

设计安装任意时刻清零电路。

5.应用门电路设计、安装、调试报时电路59′53″, 59′55″,59′57″低声报时(频率f 3≈500Hz ),59′59″高声报时(频率f 4≈1000Hz ),整点报时电路,233"59'59"55'5959'53"H f f f ⋅+⋅+⋅=。

三、实验元件清单1、 集成电路:NE5551片 (多谐振荡) CD4040 1片 (分频)CD4518 2片 (8421BCD 码十进制计数器) CD4511 4片 (译码器) 74LS00 3片 (与非门) 74LS20 1片 (4输入与非门) 74LS21 2片 (4输入与门) 74LS741片(D 触发器)2、 电阻:1K Ω 1只 3K Ω 1只 330Ω28只3、 电容:0.047uf1只4、 共阴极双字屏显示器两块。

四、实验器件引脚图及功能表 1.NE555(1)引脚布局图:12345678NE555VccDTH COGND TR OUT RD(2)逻辑功能表:2.CD4040(1)引脚布局图:12345616151413121178910CD4040V DDQ 11Q 10Q 8Q 9CR CP Q 1Q 12Q 6Q 5Q 7Q 4Q 3Q 2Vss(2)逻辑功能说明:CD4040是一种常用的12分频集成电路。