BSIM460_ReleaseNotes

BSIM464_ReleaseNotes

BSIM 4.6.4

UC Berkeley - 2

Bug 1: Uninitialized Variable Problem

Reported by Ben Gu and Chip Workman (Freescale) Bug: Uninitialized variable “Vtm” is used (b4temp.c line

Fix: Redundant lines are removed

UC Berkeley - 5

BSIM 4.6.4

Bug 4: Thermal Noise Model (tnoiMod=1)

Bug: (b4noi.c line 235):

gspr = gspr / (1.0 + npart_theta * npart_theta * gspr / here->BSIM4IdovVds); …… gdpr = gdpr / (1.0 + npart_theta * npart_theta * gdpr / here->BSIM4IdovVds);

BSIM Bug Report

BSIM Group University of California, Berkeley

BSIM 4.6.4

BSIM 4.6.4

Bug Description

Uninitialized variable Vtm Implementation error in tempMod=3 mobMod=3 temperature coefficients updated twice Thermal noise error (tnoiMod=1) ‘Esat’ not updated in Velocity overshoot model

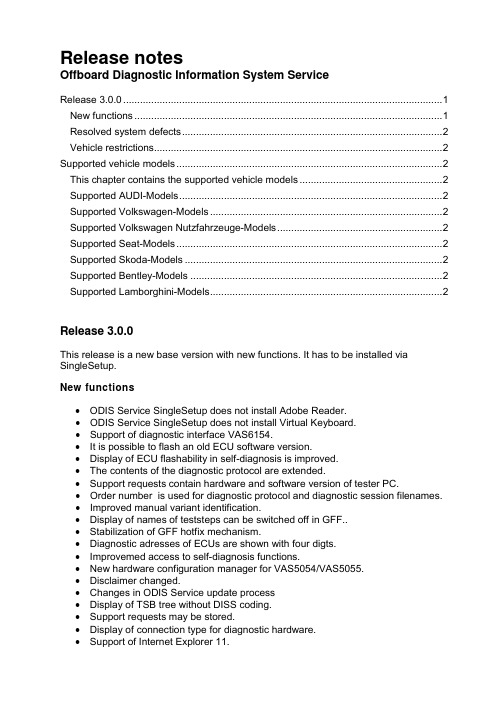

releasenotes

Release notesOffboard Diagnostic Information System ServiceRelease 3.0.0 (1)New functions (1)Resolved system defects (2)Vehicle restrictions (2)Supported vehicle models (2)This chapter contains the supported vehicle models (2)Supported AUDI-Models (2)Supported Volkswagen-Models (2)Supported Volkswagen Nutzfahrzeuge-Models (2)Supported Seat-Models (2)Supported Skoda-Models (2)Supported Bentley-Models (2)Supported Lamborghini-Models (2)Release 3.0.0This release is a new base version with new functions. It has to be installed via SingleSetup.New functions•ODIS Service SingleSetup does not install Adobe Reader.•ODIS Service SingleSetup does not install Virtual Keyboard.•Support of diagnostic interface VAS6154.•It is possible to flash an old ECU software version.•Display of ECU flashability in self-diagnosis is improved.•The contents of the diagnostic protocol are extended.•Support requests contain hardware and software version of tester PC.•Order number is used for diagnostic protocol and diagnostic session filenames.•Improved manual variant identification.•Display of names of teststeps can be switched off in GFF..•Stabilization of GFF hotfix mechanism.•Diagnostic adresses of ECUs are shown with four digts.•Improvemed access to self-diagnosis functions.•New hardware configuration manager for VAS5054/VAS5055.•Disclaimer changed.•Changes in ODIS Service update process•Display of TSB tree without DISS coding.•Support requests may be stored.•Display of connection type for diagnostic hardware.•Support of Internet Explorer 11.Resolved system defects•Search in Measured Value Tables did not work correctly.•Increased occurence of error 4009E•Some immobilizers could not be adapted.•Missing timestamp when sending support request in diagnostic protocol Vehicle restrictions•For brand AUDI, the Flash mode is supported.•For brand Volkswagen PKW, the Flash mode is restricted. The usage is only allowed if described in technical bulletins.•Flash mode is not supported for all other brands.•Only immobilizer components are diagnosable in LT2 vehicles.Supported vehicle modelsThis chapter contains the supported vehicle modelsSupported AUDI-Models•All AUDI vehicle models are supported.Supported Volkswagen-Models•All Volkswagen vehicle models are supported.Supported Volkswagen Nutzfahrzeuge-Models•2K - Caddy 2004 >•7H/7J - Transporter 2004 >•2C - Caddy 2011 >•7E/7F - Transporter 2010 >•2H - Amarok 2010 >•2E/2F - Crafter 2006-2015 >Supported Seat-Models•All Seat vehicle models are supported.Supported Skoda-Models•All Skoda vehicle models are supported.Supported Bentley-Models•All Bentley vehicle models are supported.Supported Lamborghini-Models•All Lamborghini vehicle models are supported.。

ST STGIPS14K60 数据手册

November 2011Doc ID 15927 Rev 61/20STGIPS14K60SLLIMM™ (small low-loss intelligent molded module)IPM, 3-phase inverter - 14 A, 600 V short-circuit rugged IGBTFeatures■IPM 14 A, 600 V 3-phase IGBT inverter bridge including control ICs for gate driving and free-wheeling diodes■Short-circuit rugged IGBTs■V CE(sat) negative temperature coefficient ■3.3 V, 5 V, 15 V CMOS/TTL inputscomparators with hysteresis and pull down / pull up resistors ■Undervoltage lockout ■Internal bootstrap diode ■Interlocking function ■Shutdown function■Comparator for fault protection against overtemperature and overcurrent ■DBC substrate leading to low thermal resistance■Isolation rating of 2500 Vrms/minApplications■3-phase inverters for motor drives■Home appliances, such as washing machines, refrigerators, air conditioners and sewing machinesDescriptionThis intelligent power module provides acompact, high performance AC motor drive in a simple, rugged design. Combining ST proprietary control ICs with the most advanced short-circuit-rugged IGBT system technology, this device is ideal for 3-phase inverters in applications such as home appliances and air conditioners. SLLIMM™ is a trademark of STMicroelectronics.Table 1.Device summaryOrder code Marking Package Packaging STGIPS14K60GIPS14K60SDIP-25LT ubeContents STGIPS14K60Contents1Internal block diagram and pin configuration . . . . . . . . . . . . . . . . . . . . 32Electrical ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52.1Absolute maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52.2Thermal data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63Electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73.1Control part . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93.2Waveforms definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 4Smart shutdown function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 135Applications information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 145.1Recommendations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15 6Package mechanical data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16 7Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 192/20 Doc ID 15927 Rev 61 Internal block diagram and pin configurationDoc ID 15927 Rev 63/20Table 2.Pin descriptionPin n°Symbol Description1OUT U High side reference output for U phase2V boot U Bootstrap voltage for U phase3LIN U Low side logic input for U phase4HIN U High side logic input for U phase5V CC Low voltage power supply6OUT V High side reference output for V phase7V boot V Bootstrap voltage for V phase8GND Ground9LIN V Low side logic input for V phase10HIN V High side logic input for V phase11OUT W High side reference output for W phase12V boot W Bootstrap voltage for W phase13LIN W Low side logic input for W phase14HIN W High side logic input for W phase15SD / OD Shut down logic input (active low) / open drain (comparator output)16CIN Comparator input17N W Negative DC input for W phase18W W phase output19P Positive DC input20N V Negative DC input for V phase21V V phase output22P Positive DC input23N U Negative DC input for U phase24U U phase output25P Positive DC input4/20 Doc ID 15927 Rev 6STGIPS14K60Electrical ratingsDoc ID 15927 Rev 65/202 Electrical ratings2.1Absolute maximum ratingsTable 3.Inverter partSymbol ParameterValue Unit V PN Supply voltage applied between P - N U , N V , N W 450V V PN(surge)Supply voltage (surge) applied between P - N U ,N V , N W500V V CES Each IGBT collector emitter voltage (V IN (1) = 0)1.Applied between HIN i , LIN i and GND for i = U, V , W 600V ± I C (2)2.Calculated according to the iterative formula:Each IGBT continuous collector current at T C = 25°C14A ± I CP (3)3.Pulse width limited by max junction temperatureEach IGBT pulsed collector current 30A P TOT Each IGBT total dissipation at T C = 25°C 42W t scwShort circuit withstand time, V CE = 0.5 V (BR)CES T J = 125 °C, V CC = V boot = 15 V , V IN (1)= 0 ÷ 5 V5µsTable 4.Control partSymbol ParameterValueUnit V OUT Output voltage applied between OUT U, OUT V , OUT W - GND V boot - 21 to V boot + 0.3V V CC Low voltage power supply -0.3 to +21V V CIN Comparator input voltage-0.3 to V CC +0.3V V boot Bootstrap voltage applied between V boot i - OUT i for i = U, V , W-0.3 to 620V V IN Logic input voltage applied between HIN, LIN and GND-0.3 to 15V V SD/OD Open drain voltage -0.3 to 15V dV OUT /dtAllowed output slew rate50V/nsI C T C ()T j max ()T C–R thj c –V CE sat ()max ()T j max ()I C T C (),()×-------------------------------------------------------------------------------------------------------=Electrical ratingsSTGIPS14K606/20 Doc ID 15927 Rev 62.2 Thermal dataTable 5.Total systemSymbol ParameterValue Unit V ISO Isolation withstand voltage applied between each pin and heatsink plate (AC voltage, t = 60 sec.)2500V T j (1)1.The maximum junction temperature rating of the power chips integrated within the SDIP module is 150°C(@T C ≤ 100°C). To ensure safe operation of the SDIP module, the average junction temperature should be limited to T j(avg) ≤ 125°C (@T C ≤ 100°C).Operating junction temperature -40 to 150°C T CModule case operation temperature-40 to 125°CTable 6.Thermal dataSymbol ParameterValue Unit R thJCThermal resistance junction-case single IGBT 3°C/W Thermal resistance junction-case single diode5.5°C/WSTGIPS14K60Electrical characteristicsDoc ID 15927 Rev 67/203 Electrical characteristicsT J = 25 °C unless otherwise specified.Note:t ON and t OFF include the propagation delay time of the internal drive. t C(ON) and t C(OFF) are the switching time of IGBT itself under the internally given gate driving condition.Table 7.Inverter partSymbolParameterTest conditionsValueUnitMin.Typ.Max.V CE(sat)Collector-emitter saturation voltageV CC = V boot = 15 V , V IN (1)= 0 ÷ 5 V ,I C = 7 A- 2.1 2.5V V CC = V boot = 15 V , V IN (1)= 0 ÷ 5 V ,I C = 7 A, T J = 125 °C- 1.8I CES Collector-cut off current (V IN (1)= 0 “logic state”)V CE = 600 V , V CC = V Boot = 15 V -150µA V FDiode forward voltageV IN (1) = 0 “logic state”, I C = 7 A- 2.1VInductive load switching time and energyt on T urn-on time V DD = 300 V ,V CC = V boot = 15 V , V IN (1) = 0 ÷ 5 V , I C = 7 A(see Figure 5)-270nst c(on)Crossover time (on)-130t off T urn-off time -320t c(off)Crossover time (off)-110t rr Reverse recovery time -130E on T urn-on switching losses -150µJ E offT urn-off switching losses-901.Applied between HIN i , LIN i and GND for i = U, V , W (LIN inputs are active-low).Electrical characteristics STGIPS14K60Note:Figure 4 "Switching time definition" refers to HIN inputs (active high). For LIN inputs (active low), VIN polarity must be inverted for turn-on and turn-off.8/20 Doc ID 15927 Rev 6STGIPS14K60Electrical characteristicsDoc ID 15927 Rev 69/203.1 Control partTable 8.Low voltage power supply (V CC = 15 V)Symbol ParameterTest conditionsMin.Typ.Max.Unit V cc_hys V cc UV hysteresis 1.2 1.5 1.8V V cc_thON V cc UV turn ON threshold 11.51212.5V V cc_thOFF V cc UV turn OFF threshold 1010.511V I qccuUndervoltage quiescentsupply currentV CC = 10 VSD/OD = 5 V; LIN = 5 V; HIN = 0, CIN = 0450µAI qccQuiescent current V cc = 15 VSD/OD = 5 V; LIN = 5 V HIN = 0, CIN = 03.5mAV refInternal comparator (CIN) reference voltage0.50.540.58VTable 9.Bootstrapped voltage (V CC = 15 V)Symbol ParameterTest conditionsMin.Typ.Max.Unit V BS_hys V BS UV hysteresis 1.2 1.5 1.8V V BS_thONV BS UV turn ON threshold10.611.512.4V V BS_thOFF V BS UV turn OFF threshold 9.11010.9V I QBSUUndervoltage V BS quiescent currentV BS = 10 VSD/OD = 5 V; LIN and HIN = 5 V; CIN = 070110µAI QBS V BS quiescent current V BS = 15 VSD/OD = 5 V; LIN and HIN = 5 V; CIN = 0150210µA R DS(on)Bootstrap driver on resistanceLVG ON120ΩTable 10.Logic inputs (V CC = 15 V)Symbol ParameterTest conditionsMin.Typ.Max.Unit V il Low logic level voltage 0.8V V ih High logic level voltage 2.25V I HINh HIN logic “1” input bias current HIN = 15 V 110175260µA I HINl HIN logic “0” input bias current HIN = 0 V 1µA I LINlLIN logic “1” input bias current LIN = 0 V 3620µA I LINh LIN logic “0” input bias current LIN = 15 V 1µA I SDh SD logic “0” input bias current SD = 15 V 30120300µA I SDl SD logic “1” input bias current SD = 0 V 3µA DtDead timesee Figure 7600nsElectrical characteristics STGIPS14K6010/20 Doc ID 15927 Rev 6Note:X: don’t careTable 11.Sense comparator characteristics (V CC = 15 V)Symbol ParameterTest conditions Min.Typ.Max.Unit I ib Input bias currentV CP+ = 1 V -3µA V ol Open drain low level output voltageI od = - 3 mA-0.5V t d_comp Comparator delay SD/OD pulled to 5 V through 100 k Ω resistor-90130ns SR Slew rateC L = 180 pF; R pu = 5 k Ω-60V/µsect sd Shut down to high / low side driver propagation delayV OUT = 0, V boot = V CC , V IN = 0 to 3.3 V50125200nst isdComparator triggering to high / low side driver turn-off propagation delay Measured applying a voltage step from 0 V to 3.3 V to pin CIN i50200250Table 12.Truth tableConditionLogic input (V I )OutputSD/ODLIN HIN LVG HVG Shutdown enablehalf-bridge tri-state L X X L L Interlockinghalf-bridge tri-state H L H L L 0 ‘’logic state” half-bridge tri-state H H L L L 1 “logic state”low side direct driving H L L H L 1 “logic state”high side direct drivingHHHLHSTGIPS14K60Electrical characteristicsDoc ID 15927 Rev 611/20Figure 5.Maximum I C(RMS) current vs.(1)Figure 6.Maximum I C(RMS) current vs. f SINE(1)1.Simulated curves refer to typical IGBT parameters and maximum R thj-c.Electrical characteristics STGIPS14K6012/20 Doc ID 15927 Rev 63.2 Waveforms definitionsFigure 7.Dead time and interlocking waveforms definitionsLINHINLVG HVGLINHIN LVGHVGLINHIN LVGHVGLINHIN LVGHVGDT LHDT HLDT LHDT HLDT LHDT HLDT LHDT HLgate driver outputs OFF(HALF-BRIDGE TRI-STATE)C I N T E R L OK I N GCONTROL SIGNAL EDGES OVERLAPPED:INTERLOCKING + DEAD TIMECONTROL SIGNALS EDGES SYNCHRONOUS (*): DEAD TIMECONTROL SIGNALS EDGES NOT OVERLAPPED,BUT INSIDE THE DEAD TIME:DEAD TIMECONTROL SIGNALS EDGES NOT OVERLAPPED,OUTSIDE THE DEAD TIME:DIRECT DRIVING(*) HIN and LIN can be connected together and driven by just one control signalC I N T E R L OK I N Ggate driver outputs OFF (HALF-BRIDGE TRI-STATE)gate driver outputs OFF (HALF-BRIDGE TRI-STATE)gate driver outputs OFF (HALF-BRIDGE TRI-STATE)gate driver outputs OFF (HALF-BRIDGE TRI-STATE)gate driver outputs OFF (HALF-BRIDGE TRI-STATE)gate driver outputs OFF (HALF-BRIDGE TRI-STATE)gate driver outputs OFF (HALF-BRIDGE TRI-STATE)STGIPS14K60Smart shutdown functionDoc ID 15927 Rev 613/204 Smart shutdown functionThe STGIPS14K60 integrates a comparator for fault sensing purposes. The comparatornon-inverting input (CIN) can be connected to an external shunt resistor in order to implement a simple over-current protection function. When the comparator triggers, the device is set in shutdown state and both its outputs are set to low level leading the half-bridge in tri-state. In the common overcurrent protection architectures the comparator output is usually connected to the shutdown input through a RC network, in order to provide a mono-stable circuit, which implements a protection time that follows the fault condition. Our smart shutdown architecture allows to immediately turn-off the output gate driver in case of overcurrent, the fault signal has a preferential path which directly switches off the outputs. The time delay between the fault and the outputs turn-off is no more dependent on the RC values of the external network connected to the shutdown pin. At the same time the internal logic turns on the open drain output and holds it on until the shutdown voltage goes below the logic input lower threshold. Finally the smart shutdown function provides the possibility to increase the real disable time without increasing the constant time of the external RC network.Note:Pls refer to Table 11: Sense comparator characteristics (VCC = 15 V) for internal propagation delay time details.Applications informationSTGIPS14K6014/20Doc ID 15927 Rev 65 Applications informationSTGIPS14K60Applications informationDoc ID 15927 Rev 615/205.1 Recommendations●Input signal HIN is active high logic. A 85 k Ω (typ.) pull down resistor is built-in for each high side input. If an external RC filter is used, for noise immunity, pay attention to the variation of the input signal level.●Input signal /LIN is active low logic. A 720 k Ω (typ.) pull-up resistor, connected to an internal 5V regulator through a diode, is built-in for each low side input.●To prevent the input signals oscillation, the wiring of each input should be as short as possible.●By integrating an application specific type HVIC inside the module, direct coupling to MCU terminals without any opto-coupler is possible.●Each capacitor should be located as nearby the pins of IPM as possible.●Low inductance shunt resistors should be used for phase leg current sensing.●Electrolytic bus capacitors should be mounted as close to the module bus terminals as possible. Additional high frequency ceramic capacitor mounted close to the module pins will further improve performance.●The SD/OD signal should be pulled up to 5 V / 3.3 V with an external resistor (see Section 4: Smart shutdown function for detailed info).Table 13.Recommended operating conditionsSymbolParameter ConditionsValueUnitMin.Typ.Max.V PN Supply VoltageApplied between P-Nu, Nv, Nw300400V V CC Control supply voltage Applied between V CC -GND 13.51518V V BS High side bias voltage Applied between V BOOTi -OUT i for i = U, V , W1318V t dead Blanking time to prevent Arm-short For each input signal 1µs f PWMPWM input signal-40°C < T c < 100°C -40°C < T j < 125°C20kHzPackage mechanical data STGIPS14K60 6 Package mechanical dataIn order to meet environmental requirements, ST offers these devices in different grades ofECOPACK® packages, depending on their level of environmental compliance. ECOPACK®specifications, grade definitions and product status are available at: .ECOPACK® is an ST trademark.Please refer to dedicated technical note TN0107 for mounting instructions.Table 14.SDIP-25L mechanical data(mm.)Dim.Min.Typ.Max.A43.9044.4044.90A1 1.15 1.35 1.55A2 1.40 1.60 1.80A338.9039.4039.90B21.5022.0022.50B111.2511.8512.45B224.7025.2025.70C 5.00 5.40 6.00C1 6.507.007.50C211.2011.7012.20e 2.15 2.35 2.55e1 3.40 3.60 3.80e2 4.50 4.70 4.90e3 6.30 6.50 6.70D33.30D1 5.55E11.20E1 1.40F0.85 1.00 1.15F10.350.500.65R 1.55 1.75 1.95T0.450.550.65V0°6°16/20 Doc ID 15927 Rev 6STGIPS14K60Package mechanical dataDoc ID 15927 Rev 617/20Package mechanical data STGIPS14K6018/20 Doc ID 15927 Rev 6STGIPS14K60Revision historyDoc ID 15927 Rev 619/207 Revision historyTable 15.Document revision historyDate RevisionChanges25-Jun-20091Initial release.05-Aug-20092Reduced V CE(sat) value on Table 7.15-Jun-20103Document status promoted from preliminary data to datasheet.Updated package mechanical data, Table 7: Inverter part, Figure 5: Maximum IC(RMS) current vs. switching frequency and Figure 6: Maximum IC(RMS) current vs. fSINE (1).Minor text changes to improve readability.08-Nov-20104Updated T able 3, 5, 8, 9, 10 and T able 11.Modified: Figure 5 and Figure 6.09-Mar-20115Updated title with SLLIMM™ in cover page, added SDIP-25L tube dimensions Figure 11 on page 18.04-Nov-20116Updated title with SLLIMM™ (small low-loss intelligent molded module) IPM, 3-phase inverter - 14 A, 600 V short-circuit rugged IGBT in cover page and SDIP-25L mechanical data T able 14 on page 16, Figure 10 on page 17.STGIPS14K60Please Read Carefully:Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries (“ST”) reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.All ST products are sold pursuant to ST’s terms and conditions of sale.Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.UNLESS OTHERWISE SET FORTH IN ST’S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. UNLESS EXPRESSLY APPROVED IN WRITING BY TWO AUTHORIZED ST REPRESENTATIVES, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER’S OWN RISK.Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.ST and the ST logo are trademarks or registered trademarks of ST in various countries.Information in this document supersedes and replaces all information previously supplied.The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.© 2011 STMicroelectronics - All rights reservedSTMicroelectronics group of companiesAustralia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America20/20 Doc ID 15927 Rev 6。

BSIM4

DVT2 Body-bias coefficient of short-channel effect on Vth -0.032V-1 Yes -

A1 First non-saturation effect parameter 0.0V-1 Yes -

A2 Second non-saturation factor 1.0 Yes -

WINT Channel-width offset parameter 0.0m No -

RSH Source/drain sheet resistance

RSHG Gate electrode sheet resistance

=======================Basic Model Parameters==========================

UA Coefficient of first-order mobility degradation due to vertical field 1.0e-9m/V for MOBMOD =0 and 1; 1.0e-15m/V for MOBMOD =2 Yes -

mobility degradation due to vertical field 1.0e-19m2/ V2 Yes -

DVTP0 First coefficient of drain-inducedVth shift due to for long-channel pocket devices 0.0m Yes Not mod¥eled if binned DVTP0 <=0.0

BSI中国区业务拓展经理任晖《从管控风险到治理IT服务的标准

国际规范

ISO 20000-1:2005 效劳管理(guǎnlǐ)规范

ISO 20000-2:2005

效劳管理实际指南

BIP 系列参考书

认证

ITIL

基于ITIL基础

Foundation

流程定义

第十三页,共20页。

第三页,共20页。

百年声威(shēngwēi) 规范之源

KiteMark

颁布第一个英国标准, 建立第一个英国标准 标志-风筝标志

1926

国际标准化组织 (ISO)创始会员

1946

BS 7750(后转化为ISO 14000)正式颁行

1992

收购KPMG(毕马威 )北美管理 体系认证业务,成为北美最大

第十四页,共20页。

规范之道 --ISO 27001 信息平安(píng ān)管理体 系 和 ISO 20000 IT 效力管理体系

第十五页,共20页。

Manager’s Challenge

Sustainability: Risk 防止(fángzhǐ)失效

ISO 27001/BS 7799/BS 25999

授权/方式/ 损毁彻底

销毁

变更

验证 / 可恢 复 / 发布

访问控制 / 备份

归类 存档

传输

可控 / 平安

第九页,共20页。

Compliance

合规性checklist

Information Security Incident 信息安全事件管理

Compliance

合规性

Compliance 合规性

Access Control 访问控制

bsim4 mos 截止区电流 -回复

bsim4 mos 截止区电流-回复标题:BSIM4 MOS 截止区电流的深入解析在模拟电路设计中,MOSFET(金属氧化物半导体场效应晶体管)是一个非常重要的元件。

而BSIM4模型作为广泛使用的SPICE级MOSFET模型,其对于器件工作特性的描述具有很高的准确性。

本文将详细解析BSIM4模型中的截止区电流,并探讨其影响因素。

一、BSIM4模型简介BSIM4是加州大学伯克利分校开发的一种用于模拟CMOS集成电路的SPICE模型。

与传统的SPICE模型相比,BSIM4模型能够更准确地描述现代亚微米技术下的MOSFET特性。

它包括了对短沟道效应、窄沟道效应、阈值电压滚降、热载流子效应等多种物理现象的建模。

二、MOSFET的工作区域及其特性MOSFET有三个主要的工作区域:饱和区、线性区和截止区。

当MOSFET 的源极和漏极之间没有电压差时,或者即使有电压差但不足以克服阈值电压时,MOSFET处于截止状态,此时的漏极电流称为截止区电流。

三、BSIM4模型中的截止区电流计算在BSIM4模型中,截止区电流由以下公式给出:ID = IS * (1 + ETA_RDS)其中,IS为饱和区漏极电流,ETA_RDS为电阻率相关因子。

四、影响截止区电流的因素1. 阈值电压:阈值电压是决定MOSFET是否导通的关键参数。

当栅源电压低于阈值电压时,MOSFET处于截止状态,漏极电流接近于零。

2. 源漏电压:虽然在截止状态下,源漏电压不能使MOSFET导通,但是过高的源漏电压可能会导致反向偏置PN结击穿,使得截止区电流增大。

3. 温度:温度会影响半导体材料的电阻率和电子迁移率,从而影响截止区电流。

五、总结理解并掌握BSIM4模型中的截止区电流对于优化电路设计和提高电路性能至关重要。

通过调整阈值电压、控制源漏电压以及管理好工作温度,我们可以有效地调控MOSFET的截止区电流,从而满足各种应用需求。

bsim4_manual

Chapter 1: Measurement and Extraction of BSIM4 Model ParametersThe following section summarizes some aspects of UCB’s BSIM4 Model and Agilent’s IC-CAP Modeling Package to measure and extract BSIM4 model parameters.Basic effects modeled in BSIM4:•Short and narrow channel effects on threshold voltage•Non-uniform doping effects•Mobility reduction due to vertical field•Bulk charge effect•Carrier velocity saturation•Drain induced barrier lowering (DIBL)•Channel length modulation (CLM)•Substrate current induced body effect (SCBE)•Parasitic resistance effects•Quantum mechanic charge thickness modelEnhanced drain current model•VTH model for pocket/retrograde technologies•New predictive mobility model•Gate induced drain leakage (GIDL)•Internal/external bias-dependent drain source resistanceRF and high-speed model•Intrinsic input resistance (Rgate) model•Non-Quasi-Static (NQS) model•Holistic and noise-partition thermal noise model•Substrate resistance network•Calculation of layout-dependent parasitic elements•Asymmetrical source/drain junction diode model•I-V and breakdown model•Gate dielectric tunneling current modelKey features of the BSIM4 Modeling Package•The new graphical user interface in Agilent‘s IC-CAP enables the quick setup of tests and measurements followed by automatic parameter extraction routines.• A new data management concept allows a powerful and flexible handling of measurement data using an open and easy data base concept.•The powerful extraction procedures can be easily adopted to different CMOS processes.They support all possible configurations of the BSIM4 model.•Quality assurance procedures are checking every step in the modeling flow frommeasurements to the final export of the SPICE model parameter set.•The fully automatically generation of HTML reports is included to enable web publishing ofa modeling project.•The modeling package will support SPICE3e2 and major commercial simulator formats such as HSPICE, Spectre or Agilent’s ADSThe Modeling Package supports measurements on•DC transistors•Parasitic diodes•Capacitances•Oxide•Overlap•Bulk-drain, source-drain junction•IntrinsicExtractions for•DC transistors•Parasitic diodes•CapacitancesData Structure inside the BSIM4 Modeling PackageMeasurement of MOSFET’s for the BSIM4 ModelThis part of the manual provides some background information to make necessary measurements of your devices. It will provide information on features of the BSIM4 Modeling Package, how to use the graphic user interface (GUI) and give you some hints on how to measure and what to measure using the right devices.The GUI window is opened by double clicking on the BSIM4-Icon in the ICCAP main window. See Figure1-1 for a screen shot of this window.Figure1-1. Starting the BSIM4 GUI from IC-CAP main windowAfter you have double clicked the icon, the GUI window of the BSIM4 Modeling Package (Figure1-2) comes up on your screen.Figure1-2. Part of Graphic User Interface of the BSIM4 Modeling Package.The top row of the GUI shows a group of buttons on the left side to create a New project or to Open an already existing one, to Save or to Delete projects. You will be prompted before the selected action takes place.The project name appears in the middle of the top row. It is shown on blue background, in Figure1-2 the project is called “Example”.On the right side of the GUI’s top row, you will find a Print button, which opens a dialog box. Enter the command line for your specific printing device and press OK. The form will be printed. The next button in the top row - Help - opens up the online manual - the file you are viewing right now.In contrast to the function of this button, you’ll find a Help button on each folders lower left corner, too, which will open a short help document describing the task to be performed using this page. It will only give you information on how to use the buttons and forms associated with this task. Inside this manual, there are some in depth hints for the task, i.e which device geometries to use or how to connect the instrument to the device under test to get the best extraction results from your measurements.The Info button, which is located to the right of the help button, gives you some information about the creators of the BSIM4 Modeling Package.The fourth button in this group is the Demo button. Use this button to explore the BSIM4 modeling package features without starting actual measurements. This means, all measurement device drivers are disabled. Therefore, no measurement is possible in demo mode! This is also a convenient way to create a project without the need of a measurement license!Far to the right of the top row there is a button to Exit the BSIM4 modeling package.Below the top row of buttons you will find a row of seven folders. Basically, each folder is assigned to a specific task in the measurement process. They are intended to be parsed from left to right, but you are not bound to that order.The following paragraphs are assigned to one folder of the GUI each.Project NotesThe notes folder is provided to store notes you take on a specific project, Figure1-3 shows the notes form. You can enter general data like technology used to produce this wafer as well as lot, wafer and chip number. There is a field to enter the operator’s name and the date, the measurement has been taken. Space has been provided to enter notes on that project.The notes you have entered, are saved under the project name in the middle of the top row using the Save button to the left of this form. In our example this project is called “Example”.Figure1-3. Notes folder of the BSIM4 Modeling Package’s GUIMeasurement ConditionsThe next step in the modeling process is to set up measurement conditions for different measurement tasks like DC, CV or diode measurements.This folder is designed for easy setup of conditions for DC Transistor and Capacitance as well as DC Diode measurements. Figure1-4 shows the left part of the form.Figure1-4. Measurement Conditions FormOn the left side of the form, you will find a button to Save your setup under the name of the project in the middle of the top row - in our screen shot the name is “Example”.The measurement conditions form is divided into sections to enter the polarity of the devices to be measured and to define the conditions of DC Transistor, Capacitance and DC Diode measurements. See the chapters on DC Tansistor DUTs, Capacitance DUTs and DC Diode DUTs, respectively, for some background information on connecting the source-measurement units (SMU’s) and the CV instrument to the devices to be measured.Polarity:There is a polarity switch where you can specify whether you are measuring NMOS or PMOS devices by pressing the appropriate button. Shown here is the measurement of NMOS devices. DC Transistor:•Output (I D=f(V D))Here you specify the stimulus voltages used for measuring the output characteristic of your devices. You define “Start”, “Step”, and “Stop” voltages for drain, gate, and bulk nodes, respectively. For some of the values to be specified you will find a gray shaded entry field. This means, no data can be entered into this field to prevent conditions which could lead to inconsistent parameter extraction. Figure1-5 shows a typically measured output characteristic of a MOSFET.Figure1-5. Output diagram of a MOSFET•Transconductance (I D=f(V G))This part of the measurement conditions folder is designed for transfer diagram measurements. You specify “Start”, “Step”, and “Stop” voltages for gate, bulk, and drain nodes. Stop value of drain voltage is set to a fixed value in order to measure the relevant range of voltages for proper extraction of the parameters used to model this device behavior only.Figure1-6 shows the typical form of a transconductance diagram..Figure1-6. Transconductance diagramIf you change the settings of the diagram in the figure above, one of the effects appearing in submicron semiconductors becomes visible. The following Figure1-7 shows a typical transconductance diagram using a logarithmic y-axis to show the influence of the GIDL (gate induced drain leakage) effect on transistor behavior.Figure1-7. Transconductance diagram showing GIDL effectThe following figure shows the right part of the measurement conditions folder.Figure1-8. Right part of measurement conditions folderCapacitance:This section is used to define capacitance measurement conditions for junction, oxide/overlap and intrinsic capacities. See Figure1-9 for a definition of capacitances on a MOSFET.Figure 1-9. Definition of capacitances on a MOSFET•JunctionEnter the “Start”, “Step”, and “Stop” values for the bulk voltage used to measure junction capacitance of drain/bulk and source/bulk junctions.•Oxide/OverlapPlease give values for “Step” and “Stop” voltage used in measuring gate/source, gate/drain and gate/bulk overlap capacities as well as oxide fringing capacity. Start value of the gate voltage is set to a value usually save for the devices to be measured.•IntrinsicHere you can specify values for drain and gate voltages used to measure intrinsic capacitances. DC DiodeThis part of the measurement conditions folder is used to define DC measurements on source/drain-bulk diodes. To be defined is the “Start”, “Step”, and “Stop” voltage for the SMU connected to the drain node. Figure 1-10 shows a cross section of a MOSFET with the source-bulk diode.Region ofintrinsic capacity C GDOL C FC GDOC juncFigure 1-10. Measurement of source/drain-bulk diodesTemperature SetupThis form is intended to define measurements at specified temperatures. Basically, themeasurement of all DUT’s is to be performed at SPICE default temperature TNOM, which should be between 20° and 27° Celsius. This temperature could not be deleted.p +n+Note: Please don’t forget to enter the actual temperature during measurement of the devices. Figure1-11 shows the Temperature Setup folder.Figure1-11. Temperature Setup formUsing the buttons provided on the left side of the form, you can Add new temperatures. Enter the desired temperature into the dialog box. Please be sure to enter the appropriate value in degrees Celsius (°C).If you would like to Delete a measurement temperature, you will be prompted for the temperature to be deleted. If there is a file containing measured data for this temperature, the data file will be deleted if you click OK on the prompt dialog form, see Figure1-12 below.Figure1-12. Dialog boxes to delete temperatures and measured data files, where applicableNote: You cannot delete the nominal temperature TNOM!Adding new measurement temperatures results in adding a new column for each of this temperatures in the three DUTs forms (DC Transistor, Capacitance and DC Diode).Any changes on the Temperature Setup form must be saved prior to selecting another one.Switch MatrixWithin this form, which is shown in Figure1-13, you select the kind of measurement you are using a switch matrix for. There are three options: Use switch matrix for DC Transistor Measurements, for Capacitance Measurements and for Diode Measurements. You can select any one or more than one by activating the predefined button(s).Figure1-13. Defining the use of a switch matrix for measurementsThe Basic Settings provide choice of three different Matrix Models, which are supported by IC-CAP. Enter the appropriate Bus and HP-IB address of the Switch Matrix (22 in our example) as well as the HP-IB-Interface name. See the IC-CAP manual on “Making Measurements” for acomplete description of the HP-IB settings of the switch matrix to be used. Our example shows the use of a 4085 matrix model. For this type of instrument you have to define which port is connected to what SMU or C meter input pin.Again, you have to save your changes prior to leaving this form.The actual pin connections are to be entered into the form selected for use of a switch matrix (one of the DC DUTs, Capacitance DUTs or Diode DUTs form or all of them). For example, if you have selected DC Transistor measurements for use with a switch matrix, you must enter the switch matrix pin numbers in the fields below the node names of the transistors to be measured on the DC Transistor DUTs form. This might be especially useful if you make series measurements on wafers using a probe card e.g. for quality control.DC Tansistor DUTsThe DC Transistor DUTs form is used to enter DUT names, geometries and connections to the appropriate DUTs.Figure1-14 shows the right part of the DC Transistor DUTs form.Figure1-14. Left part of DC Transistor DUTs formFor your convenience, there are predefined DUTs on this form. You can either use those predefined DUTs, only adjusting names, device geometries, connections and so on, or you can delete existing DUTs and add your own ones.•Click the Add button on the left side of the form. You will be prompted for the number of DUTs to add. Enter the desired number and click add. It is also possible to use the arrows to increase or to decrease the number of DUTs to add. New lines are added according to the number you’ve entered.Shown below is the right part of the DC Transistor DUTs form.Figure1-15. Right part of DC Transistor DUTs formFor each line, enter a name for the DUT, gate length and width (L, W), drain and source areas (AD, AS), perimeter length of drain and source (PD, PS) and the number of device fingers (NF) of the transistor to be measured, see Figure1-16 for details on device geometry.If you have no knowledge of drain or source perimeter length, those data is approximated byBSIM4. For further details on how BSIM4 calculates perimeter data, see the BSIM4 manual from the University of California at Berkeley [1].Remember, all geometries are to be given in microns (µm).Geometries:Shown here is a section of a MOSFET where you can find the geometries required by the BSIM4 modeling package.Figure 1-16. .Cross section of a MOSFET showing device geometriesFigure 1-17. Top view of a multifinger MOSFETp +n+LD G SDrain Perimeter PD Drain Area AD W BBulkSourceGateDrain NF =4number of fingers:GD D S S SYou are not bound to an order of entries. That means, it is not required to begin with the large transistor, the short transistor or the narrow one. Just type in the geometries into each line as you like. There are buttons to Sort the entries into an order and to Auto Set the size category of your devices. See the paragraph on Transistors for DC measurements further down in this chapter. You will find a graph of recommended device geometries as a diagram W over L of the transistors whose parameters are to be extracted. After entering your DUTs, use the Display button under Size Category on the left side of your form to get a graph of the actual device geometries.Figure1-18. Display of device geometry distributionYou can compare your settings to the graph shown in Figure1-18 to see, if your entries fulfil the requirements for proper parameter extraction. If the geometries entered fit into the rectangle of device geometries shown in the figure mentioned above, you can use the Auto Set button to set the Size Category of your devices automatically. Otherwise, you are required to enter size category manually using a form as shown in Figure1-19 below.Figure1-19. Set size categoryIf you would like to delete DUTs:•Click the Delete button on the left side of the form. You will be prompted with a list ofDUTs (Figure1-20). Select the DUTs to be deleted and click Delete on the Delete DUTform. A prompt dialog box appears. Select OK if you are satisfied with your choice ofDUTs to be deleted.Figure1-20. Delete DUTs formAccording to your choice of temperatures on the Temperature Setup form, one or more columns marked with the temperatures you’ve entered appear. The fields of those columns show either (0) for no measured data available, (M) for DUT already measured or (-) for DUT not to be measured at that temperature.•To select devices to be measured at different temperatures: Click the Temp Meas button on the left side of the form. You will be prompted with a list of DUTs. Select the devices to be measured at those temperatures entered in the Temperature Setup folder and click OK. Note: You cannot exclude a DUT to be measured at TNOM. All DUTs are measured automatically at that temperature. If you have entered one or more temperatures on the Temperature Setup form, the DUTs selected for temperature measurement are all measured at those temperatures. It is not possible to select a DUT for measurement at temperature T1 but not at another temperature T2. The minimum configuration to extract temperature effects on parameters includes a large, a short and a small device!You can enter a module name and a comment for each DUT. If you are using a switch matrix, you must enter the pin numbers of the switch matrix pin connections to the transistor in the fields below the node names, see Figure1-21 for details.Note: When using module names to measure devices with probe cards, pay attention to the node numbers you are entering. Each device uses 4 connections to the switch matrix. You must enter the correct pin numbers for each DUT and not exceed the total pin count for each port of your matrix. Connections to the DUTs:The following figure Figure 1-21 shows an example for a connected device under test (DUT) to the source measurement unit’s (SMU’s) during DC Transistor measurements.Figure 1-21. SMU connections to the device under testMeasurement of the devicesOnce all DUTs are entered with their respective geometries, switch matrix pin connection and measurement temperatures, the actual measurement of devices can take place. You will find the appropriate buttons under the “Measurement” section on the left side of the DC Transistor DUTs folder.DUTD BSG SMU1SMU2SMU3SMU4Switch matrix Pin #,see the short DUT,Transistor_C,in Fig.1-14,1_151012119•To start measurement of the devices: Click Measure and select the DUT(s) to be measured on the form (Figure1-22) that opens. You can select measurement temperature (if there is a temperature other than TNOM defined in the temperature setup form) as well as a specific DUT or all DUTs in a module. Start measurement with the Measure button on that form. If measuring at elevated temperatures, be sure to wait until your devices are heated up orcooled down to the desired temperature. Please, be aware of the fact, that you must set your chuck temperature manually, because ICCAP does’nt support heated chuck drivers.If you select measurement of all DUTs in a module, all DUTs are measured automatically if the use of a switch matrix activated.Figure1-22. Select devices and measurement temperatures form •If you would like to clear some or all measured data, use the Clear button. You can select whether you would like to clear measured data of some or all DUT(s) at specifiedtemperatures and click Clear Data to delete measured data files.•Using the Synthesize button, you are able to simulate data from existing model parameters.By selecting this feature, already measured data files are overwritten with synthesized data.You will be prompted (Figure1-23) before existing data files are overwritten.Figure1-23. Prompt dialog for synthesizing measurement dataThis synthesized data uses the voltages set on the Measurement Conditions form to generate “measurement” data from a known set of SPICE parameters. This might be especially useful to convert parameters of other models into BSIM4 parameters by loading the created “measurement data” into the extraction routines and extract BSIM4 parameters.•For a glance at the diagrams that are just been measured, use the Display Plots button. You will see a form (Figure1-24) to select which measured data set you would like to display.After choosing the plots, use the Display Plots button on that form to open up the plotsdesired. This is a convenient way to detect measurement errors before starting the extraction routines.Figure1-24. Selecting measured data to be displayed•If you are satisfied with data you have just measured, use the Close Plots button to close the plots of measured data.Test structures for Deep Submicron CMOS ProcessesA very important prerequisite for a proper model parameter extraction is the selection of appropriate test structures. The following subsections describe the necessary test structures for proper determination of CV and DC model parameters. A very detailed description of ideal test structures can be found in the JESSI AC-41 reports [2].Transistors for DC measurementsThe minimum set of devices for a proper extraction of DC model parameters is marked with '' in Figure1-25. This means one transistor with large and wide channel (and therefore showing no short/narrow effects), one transistor with a narrow channel, one transistor with a short channel and one device with both, short and narrow channel. Please note that with this minimum set of devices some parameters cannot be determined correctly (see the chapter “Extraction of parameters”) and they are set to default values during the extraction. For an extraction of all model parameters and a better fit of the simulated devices over the whole range of designed gate length and gate width it is recommended to use more devices with different gate lengths and gate widths as shown in Figure1-25 with ' ' signs. You can use additional devices e.g. for evaluating the extraction results for certain channel lengths and widths used in your process. They are marked ’ ’.Extended design space, extrapolated from extractionDesign spacedirectly covered by extractionForbidden area due toprocess limitationsFigure1-25. Recommended Test Transistor Geometries for proper parameter extractionIf you do not have test structures like the ones shown in Figure1-25, you must be aware, extraction results may not be as accurate as in the ideal case shown above.If your test structures consist of parallel transistors (e.g. 10 NARROW transistors in parallel), perform all the macros as usual. After the measurements are done, change the BSIM4 model parameter NF (number of device fingers) to 10 in our example. After that, you may continue using the extraction routines as usual.Requirements for DevicesLargeFor a proper extraction of the basic model parameters, the short and narrow channel effects should not affect the large device extraction. Also the drain-source-resistance parameters should not have an influence on the simulated behavior of the large device. For a typical0.25 micron CMOS process with a gate oxide thickness of 6 - 7nm a large device withchannel length of 10 microns and channel width of 10 microns was found to meet theserequirements.You can check this prerequisite if you only extract the parameters in the idvg/Large setup and then perform a simulation of the setup idvg/Large. After that simulation, perform the other geometry extractions and re-simulate the idvg/Large setup again. Now, the diagram ID = f(V gs) should not change more than roughly 5% compared to the first simulation. If there is more difference, a larger device should be used to enable a good extraction of basic model parameters.NarrowFor the category'Narrow' you should use a device with the smallest designed gate width of your process. Using more narrow devices will increase the number of parameters which can be extracted and will lead to a better fit of the curves over the range of different channel widths.ShortFor the category 'Short' you should use a device with the shortest designed gate length of your process. Using more short devices will increase the number of parameters which can be extracted and will lead to a better fit of the curves over the range of different channel lengths.SmallFor the category 'Small' you should use a device with the shortest designed gate length and the smallest designed gate width of your process. This small device will incorporate all short and narrow channel effects and will be an indicator how good your parameter extractions are.In generalIt is recommended to use the designed gate lengths and widths. Effects due to underdiffusion or decrease of poly-Si gate length are sufficiently covered by the extractionroutines and the model itself.Capacitance DUTsThis form is used to measure capacitances of devices and to display measured data.Figure1-26. Right part of the Capacitance DUTs formFigure1-27. Left part of the Capacitance DUTs folderWithin this form, you will find fields to enter names of DUTs, geometries and switch matrix connections, and to select temperatures at which to measure the DUTs.•To add new DUTs: Click the Add button on the left side of the form. You will be prompted for a group of capacitances to add DUTs to (Figure1-28). Select the desired group (junctionbulk-drain or bulk-source, oxide, overlap or intrinsic) and click add. New lines are added according to the selection you’ve made.Note: Selecting overlap capacitances actually adds two DUTs: Overlap_GDS and Overlap_GDSB. It is required for proper parameter extraction to measure both DUTs and extract the parameters from both measurements. Therefore, it only makes sense to add those DUTs together.Figure1-28. Add DUTs to measure capacityFor each line, you can change the predefined name for the DUT and enter necessary geometrical data. For your convenience, only relevant data is to be entered for a specific group of capacities. Relevant data fields are shown with white background and can be edited, grey shaded data fields are not editable. For example, DUTs to measure bulk-drain junction capacitances do not require gate length and width (L, W), source area (AS) and perimeter length of source (PS) geometrical data. You only have to enter drain area (AD) and drain perimeter (PD) as well as the number of device fingers (NF) of the transistor to be measured. See Figure1-29 for some details on capacitances and geometries.Remember, all geometries are to be given in microns (µm).Source PerimeterPSFigure1-29. Device geometriesAccording to your choice of temperatures on the Temperature Setup form, one or more columns marked with the temperatures you’ve entered appear. The fields of those columns show either (0) for no measured data available, (M) for DUT already measured or (-) for DUT not to be measured at that temperature.You can enter a module name and a comment for each DUT. When using module names, you are able to measure one complete module with all his DUTs at once. This is intended for use of a prober card and taking measurements using the “step and repeat” function of a wafer prober. If you are using a switch matrix, you must enter the pin numbers of the switch matrix pin connections to the capacity you‘re about to measure. The fields for high and low connection of the CV measuring instrument is marked H or L respectively. See the paragraph on “Test Structures for CV Measurements” for details on device geometries and requirements for proper extraction of capacitances of your devices like test lead connections and so on.•To delete DUTs: Click the Delete button on the left side of the form. You will be prompted with a list of DUTs. Select the DUT(s) to be deleted and click Delete on the Delete DUT form. A prompt dialog box appears. Select OK if you are satisfied with your choice ofDUTs to be deleted.•To select devices to be measured at different temperatures: Click the Temp Meas button on the left side of the form. You will be prompted with a list of DUTs. Select the devices to be measured at those temperatures entered in the Temperature Setup form and click OK. Note: You cannot exclude a DUT to be measured at TNOM. All DUTs are measured automatically at that temperature. If you have entered one or more temperatures on the Temperature Setup form, the DUTs selected for temperature measurement are all measured at those temperatures. It is not possible to select a DUT for measurement at temperature T1 but not at another temperature T2.•To start measurement of the devices: Click Measure and select the DUT(s) to be measured on the form that opens. You can select measurement temperature (if there is a temperature other than TNOM defined in the temperature setup form) as well as a specific DUT or all DUTs. Start measurement with the Measure button on that form. If measuring at elevated temperatures, be sure to wait until your devices are heated up or cooled down to the desired temperature.。

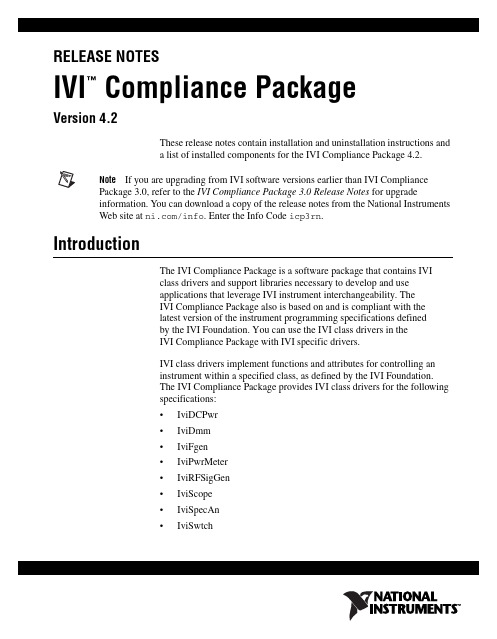

国家仪器 IVI合规性软件包4.2说明书

RELEASE NOTESIVI Compliance Package Version 4.2These release notes contain installation and uninstallation instructions anda list of installed components for the IVI Compliance Package 4.2.Note If you are upgrading from IVI software versions earlier than IVI Compliance Package 3.0, refer to the IVI Compliance Package 3.0 Release Notes for upgradeinformation. You can download a copy of the release notes from the National Instruments Web site at /info . Enter the Info Code icp3rn .IntroductionThe IVI Compliance Package is a software package that contains IVIclass drivers and support libraries necessary to develop and useapplications that leverage IVI instrument interchangeability. TheIVI Compliance Package also is based on and is compliant with thelatest version of the instrument programming specifications definedby the IVI Foundation. You can use the IVI class drivers in theIVI Compliance Package with IVI specific drivers.IVI class drivers implement functions and attributes for controlling aninstrument within a specified class, as defined by the IVI Foundation.The IVI Compliance Package provides IVI class drivers for the followingspecifications:•IviDCPwr •IviDmm •IviFgen •IviPwrMeter •IviRFSigGen •IviScope •IviSpecAn •IviSwtch™•IviCounter•IviUpconverter•IviDownconverter•IviDigitizerIVI specific drivers are drivers for the most popular instruments from allof the currently defined IVI Foundation classes and from the largestinstrument manufacturers including National Instruments, AgilentTechnologies, and Tektronix. You can create IVI specific driversyourself,or download them from /idnet. InstallationNational Instruments recommends that you close all other applicationsbefore you install the IVI Compliance Package.For system requirements, refer to the NI IVI Compliance Package Readme,which you can access by selecting Start»All Programs»NationalInstruments»IVI»IVI Compliance Package Readme.The IVI Compliance Package is included with various NationalInstruments distributions, such as National Instruments Device Drivers,Switch Executive, and Calibration Executive. You also can obtain theIVI Compliance Package as a stand-alone Web-only distribution.If you install a product that is dependent on the IVI Compliance Package,such as Switch Executive, you do not need to install this separateIVI Compliance Package because it is already included in the productinstallation.To install the IVI Compliance Package from the National InstrumentsDevice Drivers media, insert the media and follow the installationsteps.When prompted with feature selections, enable theIVI Compliance Package.To install the stand-alone, Web-only IVI Compliance Package 4.2,complete the following steps:1.Download the IVI Compliance Package 4.2 self-extracting archivefrom /downloads by navigating through the Drivers andUpdates link.2.Double-click the self-extracting archive to launch the installer.3.Click OK to begin installation.4.Follow the directions that appear on the screen.IVI Compliance Package Release © National Instruments Corporation 3IVI Compliance Package Release NotesNoteThe IVI Compliance Package Web distribution does not install NI-Spyor Measurement & Automation Explorer (MAX). NI-Spy tracks the calls your application makes to National Instruments test and measurement drivers, such as NI-VXI and NI-VISA. You can use MAX for IVI configuration support. You can use IVI software without these components, but you will not have the features these products supply unless you install them. If you have installed other National Instruments products, such as the National Instruments Device Drivers media, you might already have NI-Spy and MAX installed.If you install a National Instruments product that installs MAX after installing the Web distribution of the IVI Compliance Package, you must reinstall theIVI Compliance Package to be able to use the updated IVI configuration userinterface in MAX. You must have MAX 4.2.1 or later installed to use the IVI configuration utility in MAX.Installed ComponentsDepending on the software support you select when you install theIVI Compliance Package, the installation includes one or more of thefollowing components:•IVI class drivers •IVI class driver LabWindows ™/CVI ™ support •C++ wrappers for IviDmm , IviScope , IviDCPower , IviSwtch , and IviFGen class drivers for Measurement Studio (Windows XP only)•IVI class driver wrappers for supported versions of LabVIEW •IVI class simulation drivers •IVI-COM adapters (32-bit only)•IVI class driver examples for LabWindows/CVI, LabVIEW, and Measurement Studio •IVI Shared Components 2.1.0•IVI configuration plug-in for MAX 4.2.1 and later •Online helpUninstallationIf you no longer want to use IVI software components, complete thefollowing steps to uninstall them.Note If you installed the IVI Compliance Package as part of another distribution that depends on the IVI Compliance Package, you cannot uninstall theIVI CompliancePackage without uninstalling the dependent product.CVI, LabVIEW, National Instruments, NI, , the National Instruments corporate logo, and theEagle logo are trademarks of National Instruments Corporation. Refer to the Trademark Information at/trademarks for other National Instruments trademarks. The mark LabWindows is usedunder a license from Microsoft Corporation. Windows is a registered trademark of MicrosoftCorporation in the United States and other countries. Other product and company names mentionedherein are trademarks or trade names of their respective companies. For patents coveringNational Instruments products/technology, refer to the appropriate location: Help»Patents in yoursoftware, the patents.txt file on your media, or the National Instruments Patent Noticeat /patents .© 2003–2010 National Instruments Corporation. All rights reserved.370733E-01Aug101.Select Start»Control Panel»Add or Remove Programs .2.Select National Instruments Software and click Change/Remove .3.Select NI IVI Compliance Package 4.2 and click Remove .Note After you uninstall the IVI Compliance Package, IVI Shared Components remain on your computer. To remove the remaining components, select Start»Control Panel»Add or Remove Programs , select IVI Shared Components , and click Change/Remove .LabWindows/CVI Version SupportThe IVI Compliance Package provides support only for the latest versionof LabWindows/CVI installed on your computer. If you install the IVICompliance Package with LabWindows/CVI installed and then upgrade toa later version of LabWindows/CVI, complete the following steps tomodify the IVI Compliance Package installation to get IVI support for thelater version of LabWindows/CVI:1.Select Start»Control Panel»Add or Remove Programs .2.Select National Instruments Software and click Change/Remove .3.Select NI IVI Compliance Package 4.2 and click Modify .4.For the LabWindows/CVI Support feature under IVI Class Drivers , select Remove this feature and complete the installation.5.Repeat steps 1–3.6.For the LabWindows/CVI Support feature under IVI Class Drivers ,selectInstall this feature to a local drive and complete theinstallation.This process removes IVI class driver support for the previous version ofLabWindows/CVI and adds this support for the later version ofLabWindows/CVI.。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

!

!

IGS : DLCIG, AIGS, BIGS, CIGS IGD : DLCIGD, AIGD, BIGD, CIGD

!

The parameters from BSIM4.5.0 are retained for backward compatibility. To maintain backward compatibility with BSIM4.5.0, if AIGSD is specified, then set AIGS = AIGD = AIGSD. The other parameters follow the same rule for backward compatibility.

BSIM4.6.0 Release

UC Berkeley - 5

Gate Tunneling Current IGS / IGD

!

In BSIM4.5.0, the gate tunneling current in the overlapping S/D diffusion regions (IGS / IGD ) share the same set of parameters for both source and drain ( DLCIG, AIGSD, BIGSD, CIGSD). In BSIM4.6.0, the parameters for IGS and IGD are separate. The parameters for IGS and IGD are :

!

!

BSIM4.6.0 Release

UC Berkeley - 3

Junction Diode I-V

!

In BSIM4.5.0, the junction diode current due to the trapassisted tunneling current in space-charge region has same set of parameters for both source and drain junctions. In BSIM4.6.0, the parameters for source and drain side are separate. 6 new parameters are added for the drain side. The parameters for the source and drain side are :

I GISL = AGISL ⋅WeffCJ ⋅ Nf ⋅

BSIM4.6.0 Release

− Vds − Vgde − EGISL 3 ⋅ Toxe

UC Berkeley - 2

GISL / GIDL Leakage Module

!

To maintain backward compatibility with BSIM4.5.0, if AGISL is not given, it defaults to AGIDL. The other three new parameters default in the same way. All the four new parameters AGIDL, BGIDL, CGIDL and EGIDL parameters are binnable and the corresponding L, W and P binning parameters have been added.

BSIM 4.6.0 - Release

BSIM4.6.0 Release

GISL / GIDL Leakage Module

!

In BSIM 4.5.0, both IGISL and IGIDL share the same set of parameters – AGIDL, BGIDL, CGIDL and EGIDL.

µeff =

1 + (UA + UC ⋅ Vbseff U 0 ⋅ f ( Leff ) + 2Vth V ) gsteff TOXE Vth ⋅ TOXE Vgsteff + 2Vth + UB + UD Vgsteff + 2Vth TOXE

T NJTSD (T ) = NJTSD (TNOM ) ⋅ 1 + TNTJSD − 1 TNOM T NJTSSWD(T ) = NJTSSWD (TNOM ) ⋅ 1 + TNJTSSWD − 1 TNOM

T NJTSSWGD(T ) = NJTSSWGD(TNOM ) ⋅ 1 + TNJTSSWGD − 1 TNOM

UC Berkeley - 4

!

BSIM4.6.0 Release

Junction Diode I-V

!

I bs _ total = I bs

The diode I-V model including trap-assisted tunneling for BSIM4.6.0 is :

T − 1 NJTS (T ) = NJTS (TNOM ) ⋅ 1 + TNTJS TNOM T NJTSSW (T ) = NJTSSW (TNOM ) ⋅ 1 + TNJTSSW − 1 TNOM T NJTSSWG (T ) = NJTSSWG(TNOM ) ⋅ 1 + TNJTSSWG − 1 TNOM

! !

!

!

!

Source : NJTS, NJTSSW, NJTSSWG, TNJTS, TNJTSSW, TNJTSSWG. Drain : NJTSD, NJTSSWD, NJTSSWGD, TNJTSD, TNJTSSWD, TNJTSSWGD.

!

To maintain backward compatibility with BSIM4.5.0, if NJTSD is not given, it defaults to NJTS. The other five new parameters default in the same way.

Enhancements over BSIM4.5.0

Mohan V. Dunga, Ali M. Niknejad, Chenming Hu

Dept. of Electrical Engineering and Computer Sciences, University of California, Berkeley December 2006

[

(

)(

)]

!

The new parameters AIGS, BIGS, CIGS, AIGD, BIGD and CIGD are binnable and the corresponding new L, W and P binning parameters have also been added.

I GIDL = AGIDL ⋅ WeffCJ ⋅ Nf ⋅

I GISL = AGIDL ⋅WeffCJ ⋅ DL 3 ⋅ Toxe

3 ⋅ Toxe

3 3 ⋅ Toxe ⋅ BGIDL Vdb ⋅ ⋅ exp − V − V − EGIDL CGIDL + V 3 gse db ds

I bd _ total = I bd − Vbd VTSSWGD − Weffcj ⋅ NF ⋅ J tsswgd (T ) ⋅ exp NJTSSWGD(T ) ⋅Vtm0 ⋅ VTSSWGD − V bd − Vbd VTSSWD − Pd , deff J tsswd (T ) exp ⋅ NJTSSWD(T ) ⋅Vtm0 VTSSWD − V − 1 bd − Vbd VTSD − Ad , deff J tsd (T ) exp NJTSD(T ) ⋅Vtm0 ⋅ VTSD − V − 1 + g `min ⋅Vbd bd − 1

3 Vsb 3 ⋅ Toxe ⋅ BGIDL ⋅ ⋅ exp − − V − V − EGIDL CGIDL + V 3 ds gde sb

− Vds − Vgde − EGIDL

! !

In BSIM 4.6.0, the parameters for IGISL and IGIDL are different. 4 new parameters – AGISL, BGISL, CGISL and EGISL have been added.

BSIM4.6.0 Release

UC Berkeley - 7

Coulomb Scattering Mobility Model

!

A new term was added in the mobility model to capture the Coulomb scattering effect in the BSIM4.5.0 release. mobMod=0

2

2

mobMod=1

µeff =

U 0 ⋅ f ( Leff )

2 Vgsteff + 2Vth Vth ⋅ TOXE Vgsteff + 2Vth 1 + UA + UB 1 + UC ⋅ V + UD ( bseff ) Vgsteff + 2Vth TOXE TOXE 2

I GIDL = AGIDL ⋅WeffCJ ⋅ Nf ⋅ Vds − Vgse − EGIDL 3 ⋅ Toxe