PCF8563 实时时钟日历芯片详细资料(中文版——权威)

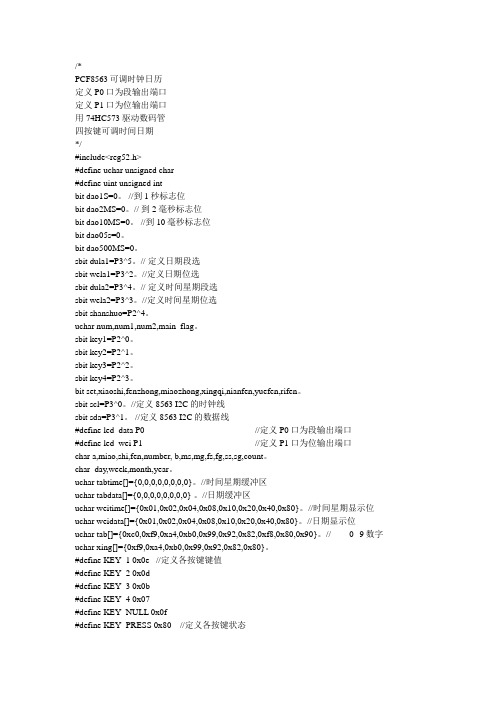

PCF8563C语言可调时钟日历

/*PCF8563可调时钟日历定义P0口为段输出端口定义P1口为位输出端口用74HC573驱动数码管四按键可调时间日期*/#include<reg52.h>#define uchar unsigned char#define uint unsigned intbit dao1S=0。

//到1秒标志位bit dao2MS=0。

// 到2毫秒标志位bit dao10MS=0。

//到10毫秒标志位bit dao05s=0。

bit dao500MS=0。

sbit dula1=P3^5。

// 定义日期段选sbit wela1=P3^2。

//定义日期位选sbit dula2=P3^4。

// 定义时间星期段选sbit wela2=P3^3。

//定义时间星期位选sbit shanshuo=P2^4。

uchar num,num1,num2,main_flag。

sbit key1=P2^0。

sbit key2=P2^1。

sbit key3=P2^2。

sbit key4=P2^3。

bit set,xiaoshi,fenzhong,miaozhong,xingqi,nianfen,yuefen,rifen。

sbit scl=P3^0。

//定义8563 I2C的时钟线sbit sda=P3^1。

//定义8563 I2C的数据线#define led_data P0 //定义P0口为段输出端口#define led_wei P1 //定义P1口为位输出端口char a,miao,shi,fen,number, b,ms,mg,fs,fg,ss,sg,count。

char day,week,month,year。

uchar tabtime[]={0,0,0,0,0,0,0,0}。

//时间星期缓冲区uchar tabdata[]={0,0,0,0,0,0,0,0} 。

//日期缓冲区uchar weitime[]={0x01,0x02,0x04,0x08,0x10,0x20,0x40,0x80}。

实时时钟PCF8563P中文译文

实时时钟芯片PCF8563使用说明一.芯片功能简介-提供年、月、日、星期、时、分、秒时间功能(主时钟为32.768KHz晶振)。

-世纪标志位。

-宽电压供电:1.0V – 5.5V。

-低后台工作电流:典型值为0.25uA(3V供电,25度时)。

-高达400KHz的高速IIC两线串行接口(当Vcc>1.8V时)。

-可编程选择时钟输出功能:32.768KHz、1024Hz、32Hz、1Hz。

-闹钟和定时器输出功能。

-电压过低检测功能。

-内置振荡形成电路。

-IIC总线从机地址:读(A3H)、写(A2H)。

-内部功能开漏中断输出。

二.内部结构三.封装与引脚-OSC1:振荡器的输入端.-OSCO:振荡器的输出端.-INT:芯片内部功能中断输出(开漏输出)。

-VSS:电源地端。

-SDA:IIC总线同步数据线。

-CLKOUT:芯片同部时钟输出端(开漏输出)。

-VDD:电源正端。

四.芯片内部寄存器五.寄存器说明1.00H寄存器(控制/状态寄存器1)以下为其位定义:-TEST1:=0:正常模式.=1:外时钟(EXT_CLK)测试模式.-STOP:=0:模块开始工作.=1:模块停止工作.-TESTC:=0:关闭上电芯片寄存器复位功能(正常使用时应该这样).=1:芯片上电时寄存器清零.2.01H寄存器(控制/状态寄存器2)以下为其位定义:-TI/TP:=0:当TF位置位时INT向外中断.=1:INT-AF:当有闹钟到达时,AF位置位.本位只能靠软件清零.=0:闹钟未到达.=1:闹钟时间到达.-TF:当定时计数器下计数结束时,TF位置位.本位只能靠软件清零.=0:定时时间未到达.=1:定时时间到达.-AIE:用于使能AF置位时是否向外发中断(通过INT端).=0:禁止闹钟中断.=1:使能闹钟中断.-TIE:用于使能TF置位时是否向外发中断(通过INT端).=0:禁止定时器中断.=1:使能定时器中断.3.02H寄存器(秒寄存器)以下为其位定义:-VL:=0:保证可靠的时钟/日历信息.=1:不保证可靠的时钟/日历信息.-SECxx:BCD格式下的秒值,高三位为BCD十位,0-5;低四位为BCD个位,0-9;4.03H寄存器(分寄存器).以下为其位定义:-MINxx:BCD格式下的分值,高三位为BCD十位,0-5;低四位为BCD个位,0-9;5.04H寄存器(时寄存器).-HOUxx:BCD格式下的小时值,采用24小时制,高二位为BCD十位,0-2;低四位为BCD个6.05H寄存器(天寄存器).以下为其位定义:-DAYxx:BCD格式下的天数值,高二位为BCD十位,0-3;低四位为BCD个位,0-9;7.06H寄存器(星期寄存器).以下为其位定义:-WEKxx:记录当前是星期几.0-6.二进制形式.注意:星期天为第一天.值如下:星期天(0);星期一(1);星期二(2);星期三(3);星期四(4);星期五8.07H寄存器(分/世纪寄存器)以下为其位定义:-C:=0:当前年份为20xx.=1:当前个份为19xx.本位在年份从99变至00时自动翻转,当然其意义可由用户自己定义.-MONxx:记录当前是几月份,BCD格式,高一位为十位,0-1;低四位为个位,0-9;9.08H寄存器(年寄存器).-YERxx:记录当前年份值,BCD格式,高四位为十位,0-9;低四位为个位,0-9;10.09H寄存器(闹钟分设置寄存器).以下为其位定义:-AE:=0:闹钟分钟设置有效.=1:闹钟分钟设置无效.说明:当设置无效时,闹钟时间匹配分钟设置将不参于匹配.-MINAxx:闹钟分设置值.BCD格式,高三位为十位,0-5;低四位为个位,0-9;11.0AH寄存器(闹钟时设置寄存器).-AE:=0:闹钟小时设置有效.=1:闹钟小时设置无效.说明:当设置无效时,闹钟时间匹配小时设置将不参于匹配.-HOUAxx:闹钟时设置值.BCD格式,高三位为十位,0-2;低四位为个位,0-9;12.0BH寄存器(闹钟天设置寄存器).-AE:=0:闹钟天设置有效.=1:闹钟天设置无效.说明:当设置无效时,闹钟时间匹配天设置将不参于匹配.-DAYAxx:闹钟天设置值.BCD格式,高三位为十位,0-3;低四位为个位,0-9;13.0CH寄存器(闹钟星期设置寄存器).-AE:=0:闹钟星期设置有效.=1:闹钟星期设置无效.说明:当设置无效时,闹钟时间匹配星期设置将不参于匹配.-WEKAxx:闹钟星期设置值.二进制格式.14.0DH寄存器(外输出时钟频率选择寄存器).-FE:=0:外时钟输出功能禁止.=1:外时钟输出功能使能.说明:当外钟功能输出禁止时,CLKOUT端将保持高阻态.-FDx:外时钟输出频率选择位,如下:15.0EH寄存器(定时器控制寄存器).以下为其位定义:-TE:=0:定时器功能禁止.=1:定时器功能使能.-TDx:定时器定时时钟频率选择位,如下:16.0FH寄存器(定时计数器寄存器).以下为其位定义:Welcome To Download !!!欢迎您的下载,资料仅供参考!。

pcf8563实时时钟/日历芯片

00H 控制/状态寄存器 1 TEST 0 STOP 0

TESTC

0

0

0

01H 控制/状态寄存器 2 0 0 0 TI/TP AF

TF AIE TIE

0DH CLKOUT 频率寄存器 FE - - -

-

- FD1 FD0

0EH 定时器控制寄存器 TE - - -

-

- TD1 TD0

0FH

定时器倒计数数值 寄存器

TESTC=0;电源复位功能失效

3

TESTC

(普通模式时置逻辑 0)

TESTC=1;电源复位功能有效

6,4,2,1,0 0

缺省值置逻辑 0

8.6.2 控制/状态寄存器2

表7:控制/状态寄存器2位描述(地址 01H)

Bit

符号

描述

7,6,5 4 3 2

0 TI/TF

AF TF

缺省值置逻辑 0 TI/TP=0:当 TF 有效时 INT 有效 (取决于 TIE 的状态) TI/TP=1:INT 脉冲有效,参见表 8 (取决于 TIE 的状态)

注意:若 AF 和 AIE 都有效时,则 INT 一直有效 当报警发生时,AF 被置逻辑 1;在定时器倒计数结束时, TF 被置逻辑 1,它们在被软件重写前一直保持原有值, 若定时器和报警中断都请求时,中断源由 AF 和 TF 决定, 若要使清除一个标志位而防止另一标志位被重写,应运

用逻辑指令 AND,标志位 AF 和 TF 值描述参见表 9。

TIMER CONTROL E

TIMER

F

7.管脚配置

7.1 管脚

图 1 方框图

OSCI 1

8 VDD

OSCO 2 PCF8563P 7 CLKOUT PCF8563T

PCF8563时钟芯片

;从机应答查询

Acknowledge: Delay_tLOW

SETB SDA ;查询接收端应答信号,要先释放总线

SETB SCL

Delay_tHIGH

JB SDA,$ ;接收端应答标志:将SDA置低

CLR SCL

RET

;主机应答

MinuteA EQU 09H ;分闹铃寄存器

HourA EQU 0AH ;时闹铃寄存器

DayA EQU 0BH ;天闹铃寄存器

WeekdayA EQU 0CH ;周闹铃寄存器

CO EQU 0DH ;时钟输出控制寄存器

TimerCtrl EQU 0EH ;定时控制寄存器

Delay_tHD_STA

CLR SCL

RET

;结束信号

Stop: Delay_tHD_DAT

CLR SDA ;I2C总线操作结束信号:SCL为高时,SDA由低-->高

SETB SCL

Delay_tSU_STO

SETB SDA ;操作结束后,确保I2C总线处于释放状态

mov a,#MinuteA

mov b,#31h

lcall write

ret

;时间初始化, 11:59:30,压缩BCD码格式(1个字节包含2个BCD码)

mov a,#HourA

mov b,#12h

lcall write

ret

Minute_init: ;分报警设置00分报警;mov a,#cs2 mov b,#02hlcall write

LCALL CS2_Set ;设置控制/状态寄存器2

LCALL DayA_Set ;设置天闹铃寄存器

基于PCF8563时钟芯片的万年历制作

万年历是一种能够显示日期、星期和时间的工具,它不仅能够告诉我们当天是几号,还能显示星期几和当前时间。

在这个项目中,我们将使用PCF8563时钟芯片来制作一个基于PCF8563的万年历。

PCF8563是一种CMOS实时时钟和日历芯片,它可以提供年、月、日、星期和小时、分钟、秒的数据。

它具有电源管理功能,可以通过一个电源低于2V脉冲输入来切换系统电源供电方式。

为了制作这个基于PCF8563的万年历,我们需要以下材料和工具:1. Arduino主控板2.PCF8563时钟芯片3.16x2液晶显示屏4.面包板5.杜邦线6.10k电阻接下来,我们将按照以下步骤来制作基于PCF8563的万年历:第一步:连接电路首先,将Arduino主控板插入面包板。

接着,连接PCF8563时钟芯片到Arduino主控板上的I2C总线。

将SDA引脚连接到A4引脚,将SCL引脚连接到A5引脚。

此外,还需要使用10k电阻将VCC引脚连接到VCC引脚上。

接下来,将16x2液晶显示屏连接到面包板。

连接液晶屏的RS引脚到Arduino主控板的D12引脚,RW引脚到GND引脚,和E引脚到D11引脚。

将液晶屏的D4到D7引脚连接到Arduino主控板的D5到D2引脚。

第二步:编写代码打开Arduino IDE并创建一个新的项目。

然后,编写以下代码:#include <Wire.h>#include <LiquidCrystal_I2C.h>//定义PCF8563的地址#define PCF8563_ADDR 0x51//定义显示屏的尺寸#define LCD_COLUMNS 16#define LCD_ROWS 2LiquidCrystal_I2C lcd(0x27, LCD_COLUMNS, LCD_ROWS);void setup//初始化I2C总线Wire.begin(;//设置时钟芯片为24小时模式Wire.beginTransmission(PCF8563_ADDR);Wire.write(0x02);Wire.write(0x00);Wire.endTransmission(;//初始化液晶显示屏lcd.begin(LCD_COLUMNS, LCD_ROWS);lcd.setCursor(0, 0);lcd.print("Date: ");lcd.setCursor(0, 1);lcd.print("Time: ");void loop//读取PCF8563的日期和时间Wire.beginTransmission(PCF8563_ADDR); Wire.write(0x02);Wire.endTransmission(;Wire.requestFrom(PCF8563_ADDR, 7);int second = bcdToDec(Wire.read( & 0x7F); int minute = bcdToDec(Wire.read();int hour = bcdToDec(Wire.read( & 0x3F); int dayOfWeek = bcdToDec(Wire.read();int dayOfMonth = bcdToDec(Wire.read();int month = bcdToDec(Wire.read( & 0x1F); int year = bcdToDec(Wire.read();//显示日期和时间lcd.setCursor(6, 0); printWithLeadingZero(dayOfMonth);lcd.print("/");printWithLeadingZero(month);lcd.print("/");lcd.print(2000 + year);lcd.setCursor(6, 1); printWithLeadingZero(hour);lcd.print(":");printWithLeadingZero(minute);lcd.print(":");printWithLeadingZero(second);delay(1000);//将BCD码转换为十进制int bcdToDec(int bcd)return (bcd / 16 * 10) + (bcd % 16);//打印带有前导零的数字void printWithLeadingZero(int number)if (number < 10)lcd.print('0');}lcd.print(number);第三步:上传代码将Arduino主控板连接到电脑,并根据需要选择正确的端口和板类型。

PCF8563

石英晶体参数(f=32.768kHz) 串联电阻 并联负载电容 微调电容 CLKOUT 输出 CLKOUT 占空因数 δCLKO UT [1] - 50 - % RS CL CT - - 5 - 10 - 40 - 25 kΩ pF pF

I2C 总线定时特性[2] [3] SCL 时钟周期 起动条件保持时间 fSCL tHDSTA [4] - 0.6 - - 400 - kHz µs

感谢和诚挚的问候! THANKS & BEST REGARDS. -2-

HEC

Semiconductor

最大额定值 参数 电源电压 电源电流 SCL 和 SDA 管脚输入电压 VI OSCI 管脚输入电压 CLKOUT 和 管脚输出电压 VO II IO P TA TS -0.5 -0.5 -10 -10 — -40 -65 VDD+0.5 +6.5 +10 +10 300 +85 +150 V V mA mA mW ℃ ℃ 符号 VDD IDD 最小值 -0.5 -50 -0.5 最大值 +6.5 +50 +6.5 单位 V mA V

HECsemic. 2012 H8563 Datasheet

- - +1

mA mA µA

1、加电时振荡器可靠起动:VDD(最小值,加电时)= VDD(最小值)+0.3V 2、定时器源时钟=1/60Hz;SCL 和 SDA 都为 VDD 3、在样品基础上测试 电气特性参数 交 流 特 性 ( 如 无 特 别 说 明 , VDD=1.8 ~ 5.5V , VSS=0V ; TA=-40 ~ +85℃ ; fosc=32.768kHz;石英晶体 Rs=40kΩ,CL=8pF) 参数 符号 测试条件 振荡器 精确负载电容 振荡器稳定性 CINT ΔfOSC/ fOSC ΔVDD=200mV,T A=25℃ 15 - 25 2×107 35 - pF - 最小值 典型 值 最大 值 单 位

PCF8583中文资料_带有 256×8bit RAM 的 8 引脚日历时钟芯片

PCF8583中文资料 芯片简介:1、PCF8583是P H IL IPS公司制造的带有256×8bit RAM的8引脚日历/时钟芯片,采用I2C2、两线串行总线接口,内含完整的振荡,分频,上电复位电路,并具备计时,日历,定时,闹钟和中断输出功能.3、日历/时钟芯片I2C总线RAM定时器4、带256字节RAM的实时时钟芯片PCF85831.芯片特点●数据保持和时钟工作电压1~6V ,总线工作电压2. 5~6V ;●采用8脚D IP或SO封装形式;●I2C两线串行总线接口;●内含256×8bit静态RAM ;●有定时,定闹功能和中断输出;●内有振荡器,分频器和上电复位电路,可使用32 768Hz石英晶振或外部50Hz时钟;●片内字节地址读写后自动加一;●可用作定时器或计数器.2.引脚功能PCF8583引脚功能如图1所列.芯片结构图1:3.片内寄存器功能描述在256字节RAM中,前16字节(地址00~0F H)是带有特殊功能的寄存器,现分述如下:内部结构如图2:3. 1状态寄存器(地址00H)状态寄存器控制着芯片所有的功能和操作,其内容如图3所列.图3 PCF8583状态寄存器详细说明如下:00寄存器(状态寄存器)8个位名称功能:0、计时器计时器到标志1闹钟定闹时间到标志查询IC价格,上IC酷搜网http://www.icqoso.com/data-PCF8583T.html 查询IC价格,上IC酷搜网http://www.icqoso.com/data-PCF8583T.html 查询IC价格,上IC酷搜网http://www.icqoso.com/data-PCF8583T.html 2闹钟使能(是否闹钟允许)0:禁止;1 :允许3屏蔽05和06字节屏蔽0 :不屏蔽;1 :屏蔽4~5功能模式芯片工作方式00:32768 Hz时钟;01 :50 Hz时钟;10 :计数器模式;11 :测试模式6计数锁存0:计数;1 :锁存7计数停止停止计数标志0:计数;1 :停止计数,分频器复位3. 2时钟计数器(地址01H~06H)查询IC价格,上IC酷搜网http://www.icqoso.com/data-PCF8583T.html 通过设置状态寄存器,可以选择32 768Hz和50Hz时钟模式或计数器模式.各时钟计数器功能如图4-7所列.1/ 100秒,秒,分,小时依次在地址01~04H.年以0~3表示,0为闰年.小时计数器的高2位分别作为12小时或24小时模式选择(0为24h , 1为12h)和上下午指示(0为AM ,1为PM).年份和日期,星期和月份分别在地址05H和06H.如果状态寄存器的屏蔽位有效,当读这些寄存器时,年份和星期的有关位会被屏蔽,这样允许用户直接读取日期和月份.在芯片以计数器方式工作时,计数器对振荡器输入端的脉冲计数,最多可达到6位数.以BCD码格式依次放在地址01~03H中,此时分频器无效.08寄存器(控制寄存器)8位使用说明:(2种模式,由00寄存器4-5位来控制)图8 时钟和日历计数器(时钟方式)地址bit7bit6bit5bit4~0011/ 100秒(0~99)02秒(0~59)03分(0~59)0424/ 12hAM/ PM 小时(0/ 1~24/ 12)05年(0~3)日期(1~28/ 29/ 30/ 31)06星期(0~6)月(1~12)07计时器(0~99)08闹钟控制寄存器09闹钟1/ 100秒0A 闹钟秒0B 闹钟分0C 闹钟小时0D 闹钟日期0E 闹钟月份查询IC价格,上IC酷搜网http://www.icqoso.com/data-PCF8583T.html 查询IC价格,上IC酷搜网http://www.icqoso.com/data-PCF8583T.html 0F闹钟计时器在设置时间时,应设置状态寄存器的停止位停止时钟,否则可能导致时钟混乱.3. 3计时器(地址07H)设置状态寄存器为XX0XX1XX可以打开计时器.在时钟模式中,计时器可以编程为以1/ 100秒,秒,分,小时或天计数.缺省状态下,计时器按天数累计.计时器为百进计数,溢出时,timer标志被置位,这个标志必须由软件来复位,通过设置闹钟寄存器的计时器中断允许位,可以传递到IN T脚引起中断.计时器的分辨率可通过设置定闹寄存器的低3位来编程(如表4所列).3. 4闹钟控制寄存器(地址08H)闹钟控制寄存器是用来控制定闹,定时和中断输出功能的.在时钟和计数器方式下有不同的功能(如表4所列).3. 5闹钟寄存器(地址09H~0F H)设置状态寄存器可以激活闹钟寄存器.设置闹钟控制寄存器可以选择定闹方式,闹钟时间到会使状态寄存器中的alarm标志置高,当alarm中断允许标志为1时,输出IN T引脚被拉低,并一直保持到复位或被软件清除.闹钟寄存器以时钟计数器相同的顺序放在地址09H以后的位置上(如表3所列),当闹钟寄存器每位都符合对应的时钟计数器时产生一个闹钟信号.通过设置闹钟计数器,闹钟可以被编程为控制日期,每天,每周或一段时间后启动;指定日期的闹钟忽略年和周位;日闹钟忽略月和日期位;周闹钟时,周/月寄存器将选择一周相应的一天启动闹钟,此时闹钟月份寄存器(0EH)改为星期寄存器,低七位对应周日到周六,最高位不用.另外,通过设置计时报警位,可以编程为定时闹钟.当计时器(0F H)值和时钟计数器(07H)位相同时,报警启动(alarm标志置1).在12小时模式时,第6和第7位的时寄存器一样.3. 6计数器的模式状态寄存器为XX10XXXX 时,可以选择计数器模式,计数器模式仅使用RAM 的01H~03H 字节,用于对O SC I 端脉冲的计数(O SCO 开路).计数器最大可计到百万(6位BCD 码).如允许计数报警,当计数器的值与09H,0A H,0B H 位的值相同时将发生一次计数报警, alarm 标志被置1 ,设置中断允许可引发中断.在此模式下,计时器(07H)受报警控制寄存器低3位控制,计时器的功能和时钟模式相同.4.芯片其它功能4. 1中断输出IN T 端图10 闹钟控制寄存器bit 名称时钟功能计数器功能0~2timer计时器设置000:无计时器001 :1/ 100秒查询IC价格,上IC酷搜网http://www.icqoso.com/data-PCF8583T.html 010 :秒011 :分100 :小时101 :日110 :不用111 :测试模式计时器设置000:无计时器001 :1010 :100011 :10000100 :1000000101 :禁止110 :禁止111 :测试模式3timer IN Tenable计时器中断允许0:禁止 1 :允许计时器中断允许0:禁止 1 :允许4~5alarm时钟定闹设置00:无闹钟01 :日期闹钟10 :周闹钟11 :每日闹钟定闹设置00:无定闹01 :定闹方式10 ,11 :禁止6timer alarm enable计时器报警允许 0:禁止 1 :允许计时器报警允许0:禁止 1 :允许7alarmIN Tenable报警中断允许0:禁止 1 :允许报警中断允许0:禁止 1 :允许与89c5252连接图,定时int输出控制cpu外部中断0 唤醒休眠中的cpu也可一唤醒掉电的cpu。

pcf8563中文资料

包

装

描述

塑料双列直插式封装;8 脚(300mil)

小塑料封装装 8 脚 宽 3.0mm

6 方框图

版本 SOT97-1 SOT96-1 SOT505-1

7 管脚配置

图 1 方框图 图 2 管脚配置

图 3 二极管保护图 -2-

管脚描述 符号 OSCI OSCO /INT VSS SDA SCL CLKOUT VDD

z 开漏中断引脚

3 应用

z 复费率电度表 IC 卡水表 IC 卡煤气表 z 便携仪器 z 传真机 移动电话

z 电池电源产品

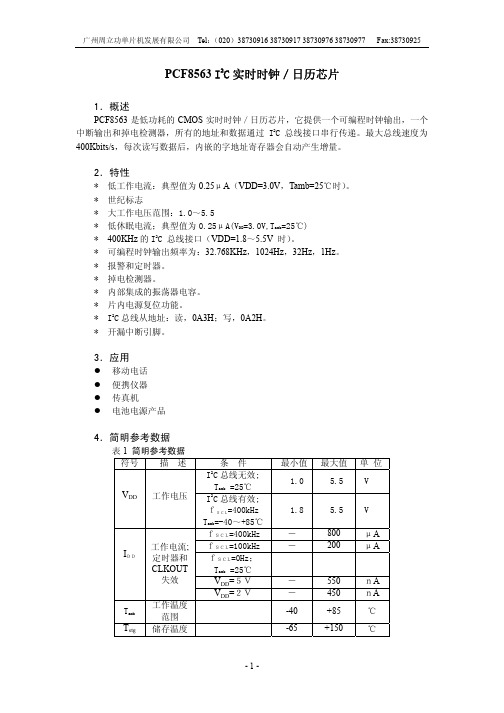

4 简明参考数据

描述

条件

符号

I2C 总线无效;

VDD 工作电压

Tamb =25 I2C 总线有效;

=400kHz

Tamb=-40 +85

=400kHz

=100kHz

工作电流;定时

PCF8563 实时时钟 日历芯片选型指南

1. 概述

PCF8563 是低功耗的 CMOS 实时时钟 日历芯片 它提供一个可编程时钟输出 一个中断输出和掉 电检测器 所有的地址和数据通过 I2C 总线接口串行传递 最大总线速度为 400Kbits/s 每次读写数据后 内嵌的字地址寄存器会自动产生增量

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

例程:1.进入EXT_CLK测试模式,设置Control/Status1寄存器的7位TEST1=1;

2.设置Control/Status1寄存器的5位STOP=1;

3.清除Control/Status1寄存器的5位STOP=0;

2

TF

1

AIE

当AF或TF被置位,AIE和TIE有效或无效,产生中断。中断是两种情况的逻辑或,因此AIE和TIE都要置位。

AIE = 0:报警器中断无效; AIE = 1:报警器中断有效.

TIE = 0:定时器中断无效; TIE = 1:定时器中断有效.

0

TIE

表8 INT操作(位TI/TP=1)

时钟源

位VL用于检测在电池供电情况下,VDD慢慢降低到Vlow的情况。在VDD低于Vlow之前应该把VDD从新拉高。这种情况下,时间可能被损坏。

8.6 寄存器结构

表4 寄存器概述

位标记‘–’无效;‘0’标记的,应始终与写入逻辑0。

表5BCD编码格式寄存器概述

位标记‘–’无效;[1]不是BCD编码格式。

8.6.1Control/Status 1寄存器(内存地址00H)

PCF8563实时时钟日历芯片选型指南

1.概述

PCF8563是低功耗的CMOS实时时钟日历芯片。它提供一个可编程时钟输出一个中断输出和掉电检测器所有的地址和数据,通过I2C总线接口串行传递最大总线速度为400Kbits/s,每次读写数据后内嵌的字地址寄存器会自动产生增量。

2.特性

低工作电流典型值:0.25 A,VDD=3.0VTamb=25时;

4.设置时间寄存器(Seconds,Minutes,Hours,Days,Weekdays,Months/Century,Years)期望值;

5.向CLOCKOUT提供32个时钟脉冲;

6.读取时间寄存器,看第一次变化;

7.向CLOCKOUT提供64个时钟脉冲;

8.读取时间寄存器,看Second寄存器变化;

秒、分钟、小时、天、月、年、以及每分钟报警、小时报警、日报警寄存器都以BCD格式编码。平日和星期报警寄存器不以BCD格式编码。

当一个RTC寄存器被读取,所有的寄存器的内容被冻结。因此可以避免在读指令跳转期间,读取时钟/日历时发生错误。

8.1报警功能模式

通过清除一个或多个报警寄存器最高有效位(位AE=报警启用),相应的报警条件将被激活。这种方式可以产生从每分钟至每周一次的报警。报警条件设置报警标志,AF(控制/状态寄存器2的第3位),AF可用于产生一个中断(INT),AF只能通过软件清零。

I2C总线从地址:读0A3H写0A2H;

开漏中断引脚。

3.应用

复费率电度表IC、卡水表IC、卡煤气表

便携仪器

传真机移动电话

电池电源产品

4.简明参考数据

符号

参数

条件

最小值

最大值

单位

VDD

工作电压

I2C总线无效

Tamb=25℃

1.0

5.5

V

I2C总线有效

Fscl = 400KHz

Tamb:-40℃—80℃

AF保持设置,直到通过软件清除。一旦AF被清0,它只会被重新设置时间增量,以符合再次报警条件。若报警寄存器AE置1,则该报警寄存器被忽略。

8.6.6LKOUT频率寄存器

8.6.7 减计数器寄存器

8位二进制减计数器有效与否是由计数控制寄存器的TE位控制,计数器的时钟源也是由计数控制寄存器选择。计数器中断的产生与控制有状态控制寄存器2(Control/Status2)控制。为了准确读出计数器的值,I2C总线的SCL时钟至少应为计数器时钟的2倍。

8.2 定时器模式

8位减数计时器(地址0FH)由定时控制寄存器(地址0EH,参见表25)控制。定时控制寄存器可以选择定时器的时钟源频率(4096,64,1,或1/60Hz)和启用/禁用计时器。从软件加载的8位二进制值的倒计时,在每个倒计时结束时,定时器设置的定时器标志TF(见表7)。定时器标志位TF只能由软件清零。根据定时器标志位TF可以产生一个中断(INT)。每个倒计时阶段都可能会产生中断脉冲信号,作为一个永久的积极信号,如TF条件下。TI/ TP(见表7)用于控制这种模式的选择。当读取定时器,当前的倒计时数值作为返回值。

8.9串行接口

PCF8563的串行接口是I2C总线。一个I2C总线规范的详细描述,包括应用和小册子:I2C总线和如何使用,时序(no9398 393 40011或I2C外设的数据手册IC12)。

8.9.5 PCF8563 I2C协议

寻址:在I2C总线上传输的任何数据之前,首先处理设备应该响应。寻址总是进行传输启动程序后的第一个字节。

9.重复第7、8步骤,看额外的变量;

8.8上电复位(POR)override模式

POR的持续时间和晶体振荡器的启动时间直接相关。由于长期启动这些类型的电路所需要的时间,一个禁用POR和加强硬板设备测试机制已建成。这种模式的设置要求,I2C总线引脚,SDA和SCL,如图5所示,在一个特定的顺序切换。所有的时间值是最低要求。

1.8

5.5

V

工作电流

(定时器和时钟输出无效)

Fscl = 400KHz

—

800

uA

Fscl = 100KHz

—

200

uA

Fscl = 0KHz; Tamb=25℃

—

VDD = 5 V

—

550

nA

VDD =2V

—

450

nA

Tamb

工作环境温度

-40

85

℃

Tstg

储存温度

-65

150

℃

8.功能描述

PCF8563内有16个8位的地址递增寄存器,一个32.768 kHz片上集成电容振荡器,一个实时时钟源(RTC)的分频器,可编程的时钟输出,一个定时器,报警器,一个低压检测器和400KHz的I2C接口。

一旦已进入override模式,芯片立即停止复位和正常运行,开始进入EXT_CLK测试模式,即通过I2C总线访问。位TESTC写逻辑0,停止override模式。只有位TESTC被设置为逻辑1,才能再次进入override模式。正常运行期间位TESTC设置逻辑0无效,只是为了防止进入PORoverride模式。

表6Control/Status 1寄存器概述

位

符号

描述

7

TEST1

TEST1=0:常规模式。

TEST1=1:EXT_CLK测试模式,见8.7章节。

5

STOP

STOP=0:RTC时钟源运行。

STOP=1:所有RTC分频器触发器异步设置为逻辑0;RTC时钟停止(32.768KHz的CLKOUT的仍然是可用的)。

9.限制值

10.静态特性

11.动态特性

12.应用信息

12.1石英晶体频率调整

方法1:配置振荡输入电容---通过平均估算应用需要的电容进行电容布局。时钟频率最好是通过测量CLKOUT管脚的32.768KHz的可用信号。频率容限取决于石英晶体的公差,电容的容量和设备到设备容量(平均±5/1000000)。每年就可以轻松实现平均偏差±5分钟。

世纪标志;

大工作电压范围:1.0V--5.5V;

低休眠电流典型值为:0.25 A(VDD=3.0V,Tamb=25 );

400KHz的I2C总线接口:VDD=1.8 5.5V时;

可编程时钟输出频率为:32.768KHz、1024Hz、32Hz、1Hz;

报警和定时器;

内部集成的振荡器电容片内电源复位功能掉电检测器;

1

定时器标志位无效

写

0

报警器标志位清零

0

定时器标志位清零

1

报警器标志位保持

1

定时器标志位保持

8.6.3Seconds, Minutes,Hours寄存器

8.6.4Days, Weekdays, Months/Century,Years寄存器

8.6.5Alarm寄存器

当一个或多个报警寄存器加载一个有效的分、时、日或平日信息,其相应的AE(Alarm Enable)位为逻辑0,然后将这些信息将与当前的分、时、日和平日进行比较。当所有启用的比较第一个匹配的,位AF(Alarm Flag)设置。

CLKOUT管脚提供的信号的最小脉冲带宽为300nS,最小周期为1000nS。内部64Hz时钟,或者外部信号源被内部预分频器分为1Hz。使用STOP预分频器可设置成已知状态,当位STOP置位,预分频器复位为0。在预分频器再次工作前,STOP位必须先清0。从STOP状态,第一个1S的占用CLKOUT信号32个上升沿,之后每1S的增量占用64个上升沿。

方法2:振荡器输入微调节---通过调整振荡器管脚的电容和上电后测量CLKOUT管脚的32.768KHz的可用信号,将振荡器调节到所需精度。

方法3:振荡器输出---直接测量输出管脚(说明测试探头电容)

所有16个寄存器被设计成可寻址的8位并行寄存器,虽然不是所有的位都有效。前两个寄存器(内存地址00H和01H),用于控制与/或状态寄存器。内存地址02H至08H是时钟功能的计数器,用于(秒、分、时、日、月、年计数器)。内存地址09H至0CH包含定义报警的条件的报警寄存器。内存地址0DH控制CLKOUT的输出频率。0EH和0FH分别是定时控制器和定时器。

PCF8563的包括内部复位电路,振荡器停止时,复位电路激活。在复位状态下,I2C总线初始化,所有寄存器和地址指针被清零,VL、TD1、TD0、TESTC和AE被设置为逻辑1。

8.5低电压检测器和时钟监视器

PCF8563芯片的低电压探测器。当VDD低于Vlow,VL位(秒寄存器第7位)设置表明可靠的时钟/日历信息将不再保证。VL标志只能由软件清零。