三态输出门电路TSL门

第八讲 其它功能的TTL门电路

课时授课计划 - 8课号:8课题:3.3.3 其它功能的TTL门电路3.3.4 TTL数字集成电路系列3.3.5 TTL集成逻辑门的使用注意事项目的与要求:熟悉OC门和TTL三态门的工作原理及有关的逻辑概念;了解国际上通用标准型号和我国现行国家标准。

重点与难点:重点:OC门和TTL三态门的应用。

难点:OC门和TTL三态门的工作原理。

教具:课堂讨论:高阻态的含义;OC门和TTL三态门的应用。

现代教学方法与手段:数字电路网络课程PowerPoint复习(提问):TTL集成与非门的外特性;提高TTL集成与非门开关速度的方法。

授课班次:课时分配:提纲3.3.3 其它功能的TTL门电路一、集电极开路与非门(OC门)1.OC门的工作原理2.OC门的应用二、与或非门三、三态输出门(TSL门)1.三态输出门的工作原理2.三态输出门的应用3.3.4 TTL数字集成电路系列一、CT54系列和CT74系列二、TTL集成逻辑门电路的子系列三、各系列TTL集成逻辑门电路性能的比较3.3.5 TTL集成逻辑门的使用注意事项一、电源电压及电源干扰的消除二、输出端的连接三、闲置输入端的处理四、电路安装接线和焊接应注意的问题五、调试中应注意的问题作业:P87 3.43.3.3 其它功能的TTL门电路一、集电极开路与非门(OC门)1.OC门的工作原理工作原理:当输入人A、B、C都为高电平时,V2和V5饱和导通,输出低电平;当输入A、B、C中有低电平时,V2和V5截止,输出高电平。

因此,OC门具有与非功能,其逻辑表达式为:二、与或非门三、三态输出门(TSL门)1.三态输出门的工作原理2.三态输出门的应用(1)用三态输出门构成单向总线(2)用三态输出门构成双向总线3.3.4 TTL数字集成电路系列一、CT54系列和CT74系列表3. 3. 2 CT54系列和CT74系列的对比CT54系列和CT74系列具有完全相同的电路结构和电气性能参数。

8.VHDL语言基础(六)

双向和三态电路设计

1

双向和三态电路信号赋值

1、三态门设计

三态门,简称TSL(Three-state Logic)门,是在普 通门电路的基础上,附加使能控制端和控制电路构成 的。三态门除了通常的高电平和低电平两种输出状态 外,还有第三种输出状态-高阻态。处于高阻态时,电 路与负载之间相当于开路。

双向和三态电路信号赋值

2、双向端口设计 用INOUT模式设计双向端口也必须考虑三 态的使用,因为双向端口的设计与三态端口的 设计十分相似,都必须考虑端口的三态控制。 这是由于双向端口在完成输入功能时,必须使 原来呈输出模式的端口呈高阻态,否则,待输 入的外部数据势必会与端口处原有电平发生 “线与”,导致无法将外部数据正确地读入, 从而实现“双向”的功能。

24

双向和三态电路信号赋值

课堂练习:

修改8位4通道三态总线驱动器的第一 个设计,使其能综合出正确的电路。

25

2

双向和三态电路信号赋值

1、三态门设计

3

双向和三态电路信号赋值

1、三态门设计 三态门用途之一是实现总线传输。总线 传输的方式有两种,单向总线和双向总线。 单向总线方式下,要求只有需要传输信息的 那个三态门的控制端处于使能状态,其余各 门皆处于禁止状态。

4

双向和三态电路信号赋值

三态门实现总线传输的原理:

11

双向和三态电路信号赋值

2、双向端口设计

双向端口设计实例

12

双向和三态电路信号赋值

2、双向端口设计

双向端口设计实例

13

双向和三态电路信号赋值

14

双向和三态电路信号赋值

2、双向端口设计

分析:

q定义为双向端口,而x定义为三态控制输出口。 在q履行输入功能时,前者没有将其设定为高 阻态输出,即执行语句:q<=“ZZZZZZZZ”,从 而没有使q成为真正的双向端口,导致了错误 的逻辑电路; 执行语句:q<=“ZZZZZZZZ”,使q 在IF 语句 中有了完整的条件描述,从而克服了时序元件 的引入。

数字电路习题-第二章

第二章 逻辑门电路集成逻辑门电路是组成各种数字电路的基本单元。

通过本章的学习,要求读者了解集成逻辑门的基本结构,理解各种集成逻辑门电路的工作原理,掌握集成逻辑门的外部特性及主要参数,掌握不同逻辑门之间的接口电路,以便于正确使用逻辑门电路。

第一节 基本知识、重点与难点一、基本知识(一) TTL 与非门 1.结构特点TTL 与非门电路结构,由输入极、中间极和输出级三部分组成。

输入级采用多发射极晶体管,实现对输入信号的与的逻辑功能。

输出级采用推拉式输出结构(也称图腾柱结构),具有较强的负载能力。

2.TTL 与非门的电路特性及主要参数 (1)电压传输特性与非门电压传输特性是指TTL 与非门输出电压U O 与输入电压U I 之间的关系曲线,即U O=f (U I )。

(2)输入特性当输入端为低电平U IL 时,与非门对信号源呈现灌电流负载,1ILbe1CC IL R U U U I −−−=称为输入低电平电流,通常I IL =-1~1.4mA 。

当输入端为高电平U IH 时,与非门对信号源呈现拉电流负载,通常I IH ≤50μA 称为输入高电平电流。

(3)输入负载特性实际应用中,往往遇到在与非门输入端与地或信号源之间接入电阻的情况。

若U i ≤U OFF ,则电阻的接入相当于该输入端输入低电平,此时的电阻称为关门电阻,记为R OFF 。

若U i ≥U ON ,则电阻的接入相当于该输入端输入高电平,此时的电阻称为开门电阻,记为R ON 。

通常R OFF ≤0.7K Ω,R ON ≥2K Ω。

(4)输出特性反映与非门带载能力的一个重要参数--扇出系数N O 是指在灌电流(输出低电平)状态下驱动同类门的个数IL OLmax O /I I N =其中OLmax I 为最大允许灌电流,I IL 是一个负载门灌入本级的电流(≈1.4mA )。

N O 越大,说明门的负载能力越强。

(5)传输延迟时间传输延迟时间表明与非门开关速度的重要参数。

其他类型TTL门电路all

(2)逻辑符号

低电平有效

控制端低电平有效的三态门

用“▽” ▽ 表示输出 为三态。

高电平有效

控制端高电平有效的三态门

2010-9-14 18

2.三态门的主要应用-实现总线传输 要求各门的控制 端EN轮流为高电平, 且在任何时刻只有一 个门的控制端为高电 平。 如有8个门,则8 个EN端的波形应依 次为高电平,如下页 所示。

系列 参数 tpd/ns P/门/mw

54LS/74LS 低功耗肖特基 10 2

54ALS/74ALS 低功耗肖特基高速 4 1

其中LS系列的综合性能(功耗延迟积)较优, 价格较ALS系列优越,因此得到了较广的应用。

2010-9-14 6

对于不同系列的TTL器件,只要器件型号的后 几位数码一样,则它们的逻辑功能、外形尺寸、引 脚排列就完全相同。 例如,7420、74H20、74S20、74LS20都是四 、 、 、 输入双与非门,都采用14条引脚双列直插式封装, 而且各引脚的位置也是相同的。

系列 参数 工作环境温度 电源电压工作范围

2010-9-14

74系列 系列 0~70OC 5V±5% ±

54系列 系列 -55~125OC 5V±10% ±

5

表2-6 不同系列TTL门电路的比较

系列 参数 tpd/ns P/门/mw 54/74 标准 10 10 54H/74H 高速 6 22.5 54S/74S 肖特基 4 20

2010-9-14 8

很大的电流 1 不高不低的 电平:1/0?

0

图2-18 推拉式输出级并联的情况

2010-9-14 9

其次,在采用推拉式输出级的门电路中,电 源一经确定(通常规定为5V),输出的高电平也 就固定了(不可能高于电源电压5V),因而无法 满足对不同输出高电平的需要。 集电极开路门(简称OC门)就是为克服以上 局限性而设计的一种TTL门电路。

实验三三态门

实验三三态门实验三三态门一、实验目的1.熟悉计三态输出门的逻辑功能和使用方法。

2.掌握用三态门构成公共总线的特点和方法。

二、实验器材1.数字逻辑实验箱2.双踪示波器3.与非门74LS00(1片)、三态门74LS125(1片)三、预习要求1.复习三态门有关知识,了解其逻辑功能及管脚。

2.复习三态门实现总线传输的方法。

四、实验原理1.三态门(TS)三态门有三种输出状态:高电平输出、低电平输出和高阻输出状态。

常见的三态门有控制端高电平有效和低电平有效两种类型。

三态输出门除了有多输入三态与非门,还经常做成单输入、单输出的总线驱动器,并且输入与输出有同相和反相两种类型。

例如:74LS125就是单输入、单输出的控制端低电平有效的同相三态输出门。

即E=0时,Y=A;E=1时为高阻态。

三态门主要用途之一是实现总线传输,各三态门输出端可以并联使用一个传输通道,以选通的方式传送多路信息。

使用时注意输出端并接的三态门只能有一个处于工作状态(E=0)。

其余必须处于高阻状态(E=1)。

三态门驱动能力强,开关速度快,在中大规模集成电路中广泛采用三态门输出电路,作为计算机和外围电路的接口电路。

如图2-1为三态门逻辑符号。

AB图2-1三态门逻辑符号五、实验内容1.三态门逻辑功能测试:查出三态门74LS125的引脚图,验证各三态门逻辑功能。

按图2-1(A)在实验箱上连线,先接上电源和地线,然后用逻辑电平控制输入端A和使能端E,用L显示输出Y的状态,实验结果填入下表:表2-174LS125逻辑功能表:使能输入端E0011数据输入A0101输出Y2.用三态门74LS125构成公共总线:要求:用三个三态门构成一条公共总线,参考图21(B)。

使三个输入端状态分别为“0”、“1”、CP,观测公共总线输出状态。

(1)按上述要求画出公共总线的逻辑图。

(2)在实验箱上连线:A1、0(GND),A2、1(Vcc),A3、CP(1KHz或100KHz信号源输出),三个使能端E1??E3分别由三个逻辑开关控制其电平的高低。

OC门与三态门

实验3.4 三态门和OC门的应用一、实验目的1.掌握TTL三态门的逻辑应用;2.掌握TTL OC门的逻辑应用;3.熟悉TTL三态门、OC门电路应用的测试方法。

二、知识点三态门和OC门输出端可并接。

三态门有低电平、高电平和高阻三种状态;OC门可实现“线与”功能。

三、实验原理在实际应用中,常需要把几个逻辑门的输出端并联使用,实现逻辑与,称为“线与”。

但普通TTL门电路不允许将输出端直接并联在一起,因为这种门电路输出高电平还是低电平,其输出电阻都很小,只有几欧姆或几十欧姆。

若把两个TTL门输出端连在一起,当其中一个输出高电平,另一个输出低电平时,它们中的导通管就会在Vcc和地之间形成一个低阻串联通路,通过这两个门的输出级产生很大的电流,损坏电路。

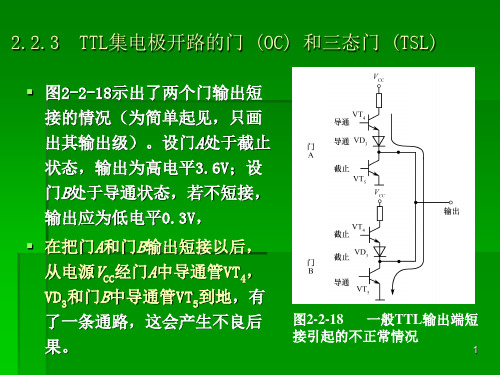

图3-3-1示出了两个TTL门输出短接的情况,为简单起见,图中只画出了两个与非门的推拉式输出级。

设门A处于截止状态,若不短接,输出应为高电平;设门B处于导通状态,若不短接,输出应为低电平。

在把门A和门B的输出端作如图3-3-1所示连接后,从电源Vcc经门A中导通的T4、D3和门B中导通的 T5到地,形成了一个低阻通路,其不良后果为:(1)输出电平既不是高电平也不是低电平,而是两者之间的某一值,导致逻辑功能混乱;(2)上述通路导致输出级电流远大于正常值,导致功耗剧增,发热增大,可能烧坏器件。

图3-4-1普通TTL门输出短接1.三态门(TS门)三态门,简称TSL(Three-state Logic)门,是在普通门电路的基础上,附加使能控制端和控制电路构成的。

三态门除了通常的高电平和低电平两种输出状态外,还有第三种输出状态——高阻态。

处于高阻态时,电路与负载之间相当于开路。

(a )使能端高电平有效 (b )使能端低电平有效 图3-4-2三态门的结构和逻辑符号图3-4-2所示为三态门的结构和逻辑符号,图(a)是使能端高电平有效的三态与非门,当使能端EN = 1时,电路为正常的工作状态,与普通的与非门一样,实现Y = ;当EN = 0时,为禁止工作状态,Y 输出呈高阻状态。

数字逻辑课件——TTL集电极开路的门和三态门

当EN1 = 1而其余为0时,门G2和G3呈 高阻,信号A1的非送到了总线Y上;

1

0

0

图2-2-23 用三态非门构 成单向总线

15

当仅有EN2 = 1时,信号A2的非送到 了总线Y上;

当仅有EN3 = 1时,信号A3的非送到 了总线Y上。

这样,就实现了信号A1,A2,A3向总 线Y的分时传送。见表2-2-3所示,

与非门1:

i

功耗

T4热击穿

与非门2:UOL

不允许输出直接“短

接”

2

(1)输出电平既非“1”(3.6V),也非“0”(0.3V),而 是两者之间的某一值,导致逻辑混乱。 (2)导致输出级电流远大于正常值,导致功耗剧增,可能烧 毁管子。 两种允许输出端连接在一起的TTL电路。 (一)集电极开路门电路—OC门(Open-Collector Gate) 集电极开路与非门的电路结构与逻辑符号示于图2-2-19。它

而当两个门的输出端连在一起,只要其中 有一个输出低电平(即VT5和VT’5中至少 有一个饱和),总的输出Y就是低电平;

7

只有当两个门都输出高电平(即VT5和 VT’5都截止)时,总的输出Y才是高电平, 这相当于“与”逻辑关系:

Y Y1 Y2 A1B1 A2B2

8

由于这个“与”关系是通过将输出线Y1和Y2短接实现的,

27

VD3的作用:VD3经过VT2为VT4提 供了一个低电阻放电回路,使

VT4更快地截止,有利于缩短传 输延迟时间。

VD4的作用:Y由高变低时,VD4经 VT2c、VT5b为CL提供另一条放电回 路,既加快了CL的放电速度,又 为VT5增加了基极驱动电流,加 快了VT5的导通。

实验四 OC门与三态门

实验四 OC门和TS门

4. 实验内容及步骤

(1)用OC门实现“线与”

(a)四2输入与非门(oc)74LS03 电源电压VCC为+5V。

(b)六非门74LS04

负载电阻RL用100Ω 电阻和10K电位器串联代替, 用实验方法确定RLmax和RLmin的值, 并与理论计算值相比。

计算时取 VOH=2.8V, VOL=0.35V, n=4,VCC=+5V, IOH=0.05mA,ILM=20mA, IIL=1.6mA, IIH=0.05mA。

负载电阻的测定

RL RL(max)

理论值

实测值

RL(min) 验证:Y = A1 + A2 +A3+A4

OC“线与”实验电路

(2)用OC门实现电平转换 OC门实现TTL~CMOS接口电路

实验四 OC门和TS门

(4)三态(TS)门逻辑功能测试

四总线缓冲器74LSl25 (低电平使能有效)

电源电压为+5V

74LSl26(高电平使能有效)

实验四 OC门和TS门

Байду номын сангаас

测试TS门的总线功能

① 通过译码器 G 控制,使 Y0~Y3全部为“1”, 用万用表测量总线输出端 Y的电平,并观察LED状态。

RL(max)

VC' C nIOH

VOH mIIH

53

k 2.63k

20.2 9 0.04

RL(min)

VC'C VOL ILM mIIL

5 0.4 k 0.35k 16 31

选定的 RL值应在 2.63kΩ 与 0.35kΩ 之间,考虑标称值

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2.TTL门电路的改进系列

为了提高工作速度,降低功耗,提高抗干扰能力, 各生产厂家对门电路作了多次改进。 74系列与54系列的电路具有完全相同的电路结构 和电气性能参数。其不同之处见下表所示。

系列 参数 工作环境温度 电源电压工作范围

2018/12/3

74系列 0~70OC 5V±5%

集电极开路门(简称OC门)就是为克服以上 局限性而设计的一种TTL门电路。

2018/12/3

10

1.集电极开路门的电路结构 (1)电路结构:输出级是集电极开路的。 (2)逻辑符号:用“◇”表示集电极开路。 集电极 开路

2018/12/3

图2-19 集电极开路的TTL与非门 (a)电路 (b)逻辑符号

2.4.3 三态输出门电路(TS门)

三态门电路的输出有三种可能出现的状态: 高电平、低电平、高阻。 何为高阻状态?

悬空、悬浮状态,又称为禁止状态。

测电阻为∞,故称为高阻状态。 测电压为0V,但不是接地。 因为悬空,所以测其电流为0A。

2018/12/3

15

1.三态门的电路结构 (1)电路结构:增加了控制输入端( Enable)。 EN = 0时,电路为正常的与非工作状态, 所以称控制端低电平有效。 (2) 工作原理:

tpd/ns

P/门/mw

10

2

4

1

其中LS系列的综合性能(功耗延迟积)较优, 价格较ALS系列优越,因此得到了较广的应用。

2018/12/3 6

对于不同系列的TTL器件,只要器件型号的后 几位数码一样,则它们的逻辑功能、外形尺寸、引

脚排列就完全相同。

例如,7420、74H20、74S20、74LS20都是四

2018/12/3 8

数值远远超过正常的工作电流,可能使门电路损坏。

很大的电流 1 不高不低的 电平:1/0?

0

图2-18 推拉式输出级并联的情况

2018/12/3

9

其次,在采用推拉式输出级的门电路中,电 源一经确定(通常规定为 5V),输出的高电平也 就固定了(不可能高于电源电压 5V),因而无法 满足对不同输出高电平的需要。

1.TTL与非门的电路结构及工作原理 集电 结导 通

箝位于1.0V 有0.3V

图2-16 多发射极三极管

全为3.6V

每一个发射极能各自独立形成正向偏置的发 射结,并可使三极管进入放大或饱和区。

2018/12/3 3

1V 2.1V

有0 全1

输出1

输出0

图2-17 三输入TTL与非门电路 (a)电路 (b) 逻辑符号

图2-23 用三态门实现总线传输

2018/12/3 19

2018/12/3

20

作业题

1、2-2

2、2-3

2018/12/3

21

输入双与非门,都采用14条引脚双列直插式封装,

而且各引脚的位置也是相同的。

2018/12/3

7

2.4.2 集电极开路门(OC门)

为何要采用集电极开路门呢?

推拉式输出电路结构存在局限性。

首先,输出端不能并联使用。若两个门的输出 一高一低,当两个门的输出端并联以后,必然有很 大的电流同时流过这两个门的输出级,而且电流的 而且,输出端也呈现不高不低的电平,不能实现应 有的逻辑功能。

11

(3)工作原理:

当VT3饱和,输出低电平UOL=0.3V;

当VT3截止,由外接电源E通过外接上拉电阻 提供高电平UOH=E。 因此, OC门电路必须外接电源ቤተ መጻሕፍቲ ባይዱ负载电阻, 才能提供高电平输出信号。

2018/12/3

12

2. OC门的应用举例

(1) OC门的输出端并联,实现线与功能。 RL为外接负载电阻。

1

Y=AB

0

2018/12/3

截止

16

1.0V

1.0V

截止

悬空

截止

1

0

导通

当EN = 1时,门电路输出端处于悬空的高阻状态。

2018/12/3 17

(2)逻辑符号

低电平有效

控制端低电平有效的三态门

用“▽” 表示输出 为三态。

高电平有效

控制端高电平有效的三态门

2018/12/3 18

2.三态门的主要应用-实现总线传输 要求各门的控制 端EN轮流为高电平, 且在任何时刻只有一 个门的控制端为高电 平。 如有8个门,则8 个EN端的波形应依 次为高电平,如下页 所示。

Y1 =AB

Y2 = CD

Y1 0 0 1 1 Y2 0 1 0 1 Y 0 0 0 1

2018/12/3

Y图 2-20 Y1 OC Y2门的输出端并联实现线与功能 AB CD AB CD

13

(2)用OC门实现电平转换

图2-21 用OC门实现电平转换的电路

2018/12/3 14

2.4

2.4.1 2.4.2 2.4.3

其它类型TTL门电路

TTL与非门 集电极开路门(OC门)

结束 放映

三态输出门电路(TSL门)

2018/12/3

1

复习

TTL反相器的电压传输特性有哪几个区? TTL反相器主要有哪些特性? TTL反相器的主要参数有哪些?

2018/12/3

2

2.4.1 TTL与非门

54系列 -55~125OC 5V±10%

5

表2-6 不同系列TTL门电路的比较

系列 参数 tpd/ns P/门/mw 54/74 标准 10 10 54H/74H 高速 6 22.5 54S/74S 肖特基 4 20

系列 参数

54LS/74LS 低功耗肖特基

54ALS/74ALS 低功耗肖特基高速