寄存器结构体

TI DSP位域寄存器文件(Bit Field and Register-File Structure)结构

SPI接口详解1

SPI接口是一种同步串行总线(Serial Peripheral Interface)。

四线SPI接口连线图:CS为片选脚,用于选中从机。

SCLK为时钟脚,用于数据传输时提供时钟信号。

MOSI为主output,从input,即主机发送脚。

对应从机的引脚为SDI。

MISO为主input,从output,机主机接收脚。

对应从机的引脚为SDO。

上述SPI为标准SPI协议(Standard SPI)或单线SPI协议(Single SPI),其中的单线是指该SPI协议中使用单根数据线MOSI 进行发送数据,单根数据线MISO 进行接收数据。

为了适应更高速率的通讯需求,半导体厂商扩展SPI协议,主要发展出了Dual/Quad/Octal SPI协议,加上标准SPI协议(Single SPI),这四种协议的主要区别是数据线的数量及通讯方式,见下表:除了上述接法,SPI还支持半双工1bit模式:SCLK:时钟线。

I/O:数据线,同一时刻要么主机发送,要么主机接收。

SS:片选脚。

Dual SPI的2bit模式:由于是半双工,同一时刻要么主机使用MOSI、MISO线,要么从机使用MOSI、MISO线。

Quad SPI(4线)模式与Dual SPI类似,也是针对SPI Flash,也是半双工,Quad SPI Flash增加了两根I/O线(SIO2,SIO3),目的是SCLK一次触发传输4bit数据。

以AC63芯片SPI接口为例,进行代码分析:根据SPI接口的时序要求,SPI接口可以通过软件实现,也可以通过硬件实现。

这里仅分析硬件实现方式。

查看数据手册可知,芯片最多支持三个SPI接口,SPI接口支持DMA发送、接收功能。

每个SPI接口引脚可以映射到不同的引脚,分别为不同的组,即组A、组B、组C、组D。

SPI硬件包含控制寄存器、波特率寄存器、buf缓冲区寄存器、DMA地址寄存器、DMA计数寄存器。

寄存器结构体定义如下:typedef struct {__RW __u32 CON;__WO __u32 BAUD;__RW __u32 BUF;__WO __u32 ADR;__WO __u32 CNT;} JL_SPI_TypeDef;每个SPI接口寄存器基地址:#define JL_SPI0_BASE (ls_base + map_adr(0x1c, 0x00))#define JL_SPI0 ((JL_SPI_TypeDef *)JL_SPI0_BASE)#define JL_SPI1_BASE (ls_base + map_adr(0x1d, 0x00))#define JL_SPI1 ((JL_SPI_TypeDef *)JL_SPI1_BASE)#define JL_SPI2_BASE (ls_base + map_adr(0x1e, 0x00))#define JL_SPI2 ((JL_SPI_TypeDef *)JL_SPI2_BASE)现将三个SPI寄存器首地址定义在数组中:static JL_SPI_TypeDef *const spi_regs[SPI_MAX_HW_NUM] = { JL_SPI0,JL_SPI1,JL_SPI2,};通过SPI的编号就可以进行对应SPI寄存器的访问操作。

stm32结构体的定义及外部引用方法

stm32结构体的定义及外部引用方法在STM32中,结构体通常用于描述复杂的数据类型,例如硬件寄存器、协议数据单元等。

在C语言中,结构体是一种用户自定义的数据类型,允许我们将多个不同类型的数据组合在一起。

下面是一个简单的STM32结构体定义的例子:```ctypedef struct {uint32_t Register1;uint8_t ByteRegister;uint16_t BitRegister;} RegisterStruct;```在这个例子中,我们定义了一个名为`RegisterStruct`的结构体,它包含了三个成员:一个32位的寄存器`Register1`,一个8位的寄存器`ByteRegister`和一个16位的寄存器`BitRegister`。

要使用这个结构体,你可以创建一个该类型的变量,并为其成员赋值:```cRegisterStruct myRegister;= 0x;= 0x11;= 0x2233;```如果你想从其他文件引用这个结构体,你可以在头文件中声明它:```c// my_ifndef MY_REGISTER_Hdefine MY_REGISTER_Htypedef struct {uint32_t Register1;uint8_t ByteRegister;uint16_t BitRegister;} RegisterStruct;endif // MY_REGISTER_H```然后在需要使用这个结构体的源文件中包含这个头文件:```c//include "my_"int main() {RegisterStruct myRegister;= 0x;= 0x11;= 0x2233;// 其他代码...return 0;}```这就是在STM32中定义和引用结构体的基本方法。

具体的实现可能会根据你的项目需求和使用的库有所不同。

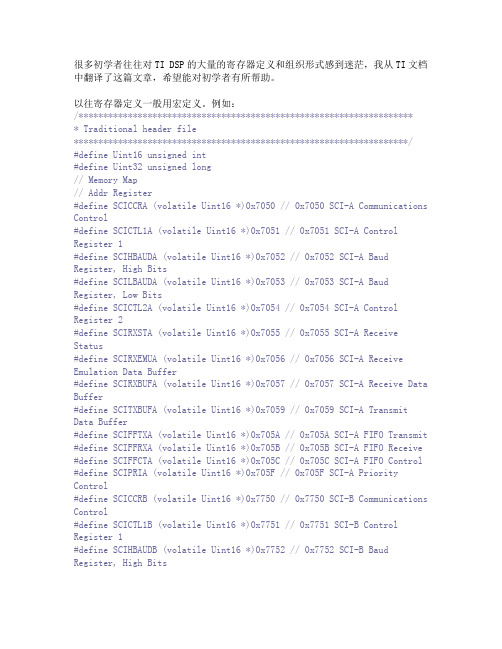

使用C语言操作SCI寄存器与CMD文件的编写

[cpp] view plaincopy

SciaRegs.SCICCR.all = 0x0007;

对 SCIHBAUD 和 SCILBAUD 进行操作

[cpp] view plaincopy

SciaRegs.SCIHBAUD = 0; SciaRegs.SCILBAUD = 0xF3;

六.寄存器文件的空间分配(CMD 文件的产生)

值得注意的是,之前所做的工作只是将 F2812 的寄存器按照 C 语言中位域定义和寄存器结构体的方式组织了数据结构,当编译时, 编译器会把这些变量分配到存储空间中,但是很显然还有一个问题需 要解决,就是如何将这些代表寄存器数据的变量同实实在意的是之前所做的工作只是将f2812的寄存器按照c语言中位域定义和寄存器结构体的方式组织了数据结构当编译时编译器会把这些变量分配到存储空间中但是很显然还有一个问题需要解决就是如何将这些代表寄存器数据的变量同实实在在的物理寄存器结合起来

使用 C 语言操作 SCI 寄存器与 CMD 文件的编写

13. };

14.

15. extern volatile struct SCI_REGS SciaRegs;

16. extern volatile struct SCI_REGS ScibRegs;

定义为 union 形式的成员既可以实现对寄存器整体的操作,也可以实

现对寄存器位的操作。

定义为 Uint16 形式的成员只能直接对寄存器进行操作

对 SCICCR 按位进行操作[cpp] view plaincopy

SciaRegs.SCICCR.bit.STOPBITS = 0; SciaRegs.SCICCR.bit.PARITYENA = 0; SciaRegs.SCICCR.bit.LOOPBKENA = 0; SciaRegs.SCICCR.bit.ADDRIDLE_MODE = 0; SciaRegs.SCICCR.bit.SCICHAR = 7;

SysTick系统定时器(功能框图和优先级配置)

SysTick系统定时器(功能框图和优先级配置)SysTick—系统定时器是属于 CM3 内核中的⼀个外设,内嵌在 NVIC 中。

系统定时器是⼀个 24bit (2^24)的向下递减的计数器,计数器每计数⼀次的时间为 1/SYSCLK,⼀般我们设置系统时钟 SYSCLK 等于 72M。

当重装载数值寄存器的值递减到 0 的时候,系统定时器就产⽣⼀次中断,以此循环往复。

因为 SysTick 是属于 CM3 内核的外设,所以所有基于 CM3 内核的单⽚机都具有这个系统定时器,使得软件在 CM3 单⽚机中可以很容易的移植。

系统定时器⼀般⽤于操作系统,⽤于产⽣时基,维持操作系统的⼼跳.SysTick的执⾏过程:counter在时钟的驱动下,从reload初值开始往下递减计数到0(在递减的过程中值可以在STK_VAL中查看到),产⽣中断和置位COUNTFLAG标志。

然后⼜从reload 值开始重新递减计数,如此循环。

SysTick相关寄存器SysTick—系统定时器有4 个寄存器(CTRL LOAD VAL CALIB),简要介绍如下。

在使⽤ SysTick 产⽣定时的时候,只需要配置前三个寄存器,最后⼀个校准寄存器不需要使⽤。

SysTick寄存器结构体SysTick寄存器(在固件库⽂件:core_cm3.h中定义)typedef struct{_IO uint32_t CTRL; /*控制及状态寄存器*/_IO uint32_t LOAD; /*重装载数值寄存器*/_IO uint32_t VAL; /*当前数值寄存器*/_IO uint32_t CALIB; /*校准寄存器*/}SysTick库函数SysTick配置库函数(在固件库⽂件:core_cm3.h中定义)__STATIC_INLINE uint32_t SysTick_Config(uint32_t ticks){// 不可能的重装载值,超出范围if ((ticks - 1UL) > SysTick_LOAD_RELOAD_Msk) {return (1UL);}// 设置重装载寄存器SysTick->LOAD = (uint32_t)(ticks - 1UL);// 设置中断优先级,默认优先级最低 __NVIC_PRIO_BITS 4(1111)系统定时器此时设置的优先级在内核外设中是最低的NVIC_SetPriority (SysTick_IRQn, (1UL << __NVIC_PRIO_BITS) - 1UL);// 设置当前数值寄存器SysTick->VAL = 0UL;// 设置系统定时器的时钟源为 AHBCLK=72M// 使能系统定时器中断// 使能定时器SysTick->CTRL = SysTick_CTRL_CLKSOURCE_Msk |21 SysTick_CTRL_TICKINT_Msk |22 SysTick_CTRL_ENABLE_Msk;23 return (0UL);24 }⽤固件库编程的时候我们只需要调⽤库函数 SysTick_Config()即可,形参ticks⽤来设置重装载寄存器的值,最⼤不能超过重装载寄存器的值 2^24,当重装载寄存器的值递减到 0的时候产⽣中断,然后重装载寄存器的值⼜重新装载往下递减计数,以此循环往复。

使用C语言操作SPI的寄存器及相应的CMD文件

使用C语言操作SPI的寄存器及相应的CMD文件1.SPI寄存器结构体文件定义:struct SPI_REGS{union SPICCR_REG SPICCR; // 配置控制寄存器定义union SPICTL_REG SPICTL; //工作控制寄存器定义union SPISTS_REG SPISTS; // 状态寄存器定义Uint16 rsvd1; // 保留位Uint16 SPIBRR; // 波特率寄存器定义Uint16 rsvd2; // 保留位Uint16 SPIRXEMU; //仿真缓冲寄存器定义Uint16 SPIRXBUF; //串行接收缓冲寄存器定义Uint16 SPITXBUF; //串行发送缓冲寄存器定义Uint16 SPIDAT; // 串行数据寄存器定义union SPIFFTX_REG SPIFFTX; // FIFO发送寄存器定义union SPIFFRX_REG SPIFFRX; // FIFO接收寄存器定义union SPIFFCT_REG SPIFFCT; // FIFO控制寄存器定义Uint16 rsvd3[2]; //保留位union SPIPRI_REG SPIPRI; // FIFO优先级控制寄存器定义};extern volatile struct SPI_REGS SpiaRegs;extern volatile struct SPI_REGS SpibRegs;2.使用DATA_SECTION方法将寄存器文件分配到数据空间# pragma DATA_SECTION(SpiaRegs,”SpiaRegsFile”);volatile struct SPI_REGS SpiaRegs;# pragma DATA_SECTION(SpibRegs,”SpibRegsFile”);volatile struct SPI_REGS SpibRegs;3.将数据段映射到寄存器对应的存储空间(.CMD)MEMORY{PAGE 1:SPIA : origin = 0x007040, length = 0x000010 /* SPIA寄存器*/ SPIB : origin = 0x007740, length = 0x000010 /* SPIB寄存器*/ }SECTIONS{SpiaRegsFile : > SPIA, PAGE = 1SpibRegsFile : > SPIB, PAGE = 1}。

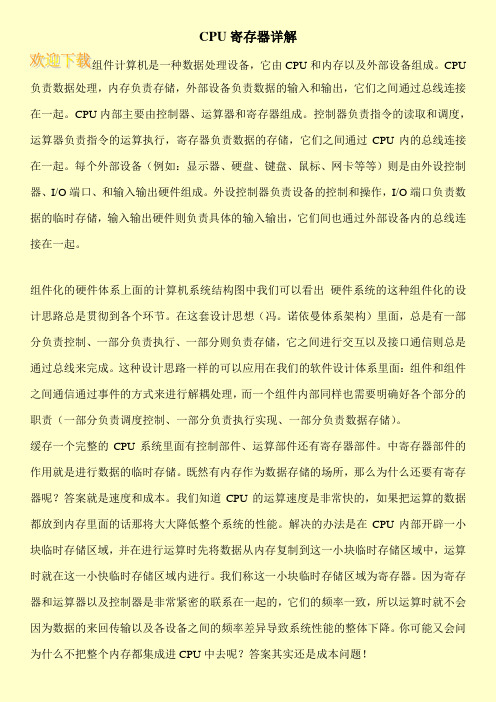

CPU寄存器详解

CPU寄存器详解组件计算机是一种数据处理设备,它由CPU和内存以及外部设备组成。

CPU 负责数据处理,内存负责存储,外部设备负责数据的输入和输出,它们之间通过总线连接在一起。

CPU内部主要由控制器、运算器和寄存器组成。

控制器负责指令的读取和调度,运算器负责指令的运算执行,寄存器负责数据的存储,它们之间通过CPU内的总线连接在一起。

每个外部设备(例如:显示器、硬盘、键盘、鼠标、网卡等等)则是由外设控制器、I/O端口、和输入输出硬件组成。

外设控制器负责设备的控制和操作,I/O端口负责数据的临时存储,输入输出硬件则负责具体的输入输出,它们间也通过外部设备内的总线连接在一起。

组件化的硬件体系上面的计算机系统结构图中我们可以看出硬件系统的这种组件化的设计思路总是贯彻到各个环节。

在这套设计思想(冯。

诺依曼体系架构)里面,总是有一部分负责控制、一部分负责执行、一部分则负责存储,它之间进行交互以及接口通信则总是通过总线来完成。

这种设计思路一样的可以应用在我们的软件设计体系里面:组件和组件之间通信通过事件的方式来进行解耦处理,而一个组件内部同样也需要明确好各个部分的职责(一部分负责调度控制、一部分负责执行实现、一部分负责数据存储)。

缓存一个完整的CPU系统里面有控制部件、运算部件还有寄存器部件。

中寄存器部件的作用就是进行数据的临时存储。

既然有内存作为数据存储的场所,那么为什么还要有寄存器呢?答案就是速度和成本。

我们知道CPU的运算速度是非常快的,如果把运算的数据都放到内存里面的话那将大大降低整个系统的性能。

解决的办法是在CPU内部开辟一小块临时存储区域,并在进行运算时先将数据从内存复制到这一小块临时存储区域中,运算时就在这一小快临时存储区域内进行。

我们称这一小块临时存储区域为寄存器。

因为寄存器和运算器以及控制器是非常紧密的联系在一起的,它们的频率一致,所以运算时就不会因为数据的来回传输以及各设备之间的频率差异导致系统性能的整体下降。

PCI配置寄存器

io内存和io端口

我们知道,外设都是通过读写设备上的寄存器来进行的,外设寄存器也 称为“I/O端口”。而IO端口有两种编址方式:独立编址和统一编制。 而具体采用哪一种则取决于CPU的体系结构。 如,PowerPC、m68k等

采用 统一编址;而X86等则采用独立编址。 对于某一既定的系统,它要么是独立编址,也即“I/O端口”方式,外设 寄存器位于“I/O空间”; 要么是统一编制,也即“I/O内存”方式,外设寄存器位于“内存空间”

PCI总线简介

PCI寻址(物理)

pci域:(16位) 总线号:(8位) 设备号:(5位) 功能号:(3位) 总线号、设备号和功能号共同组成pci外设的16位硬件地址。 但是由于256个总线对许多大系统是不够的, Linux 现在支持 PCI 域。每个 PCI 域可以占用多达 256 个总线. 每个总线占 用 32 个设备, 每个设备可以是一个多功能卡(例如一个声音 设备, 带有一个附加的 CD-ROM 驱动)有最多 8 个功能 这样,linux系统可以支持更多的pci设备

。

linxu对io内存和io端口的访问

对于Linux内核而言,它可能用于不同的CPU,所以它必须都要考虑这两种访问方式: 1.linux访问IO内存的流程是: request_mem_region() -> ioremap()

-> ioread8()/iowrite8() -> iounmap() -> release_mem_region() 。 2.访问IO端口的方式: (1)Linux内核提供了如下一些访问I/O端口的内联函数(这种方法比较常用) unsigned inb(unsigned port); void outb(unsigned char byte, unsigned port); unsigned inw(unsigned port); void outw(unsigned short word, unsigned port); unsigned inl(unsigned port); void outl(unsigned longword, unsigned port); (2)linux访问io端口的新机制 ioport_map() -> ioread8()/iowrite8() ->ioport_unmap()