第1讲.电路设计的解题技巧

电路解题技巧

电路解题技巧

1. 了解基本电路知识:了解电流、电压、电阻等概念,并熟悉欧姆定律、基尔霍夫定律、电功率等基本电路理论。

2. 绘制电路图:根据题目给出的条件,将电路图绘制出来,清楚标记电源、电阻、电流、电压等元件。

3. 使用基尔霍夫定律:根据题目所给条件,利用基尔霍夫定律解出电路中的电流和电压,可以采用节点电流法或者回路电压法。

4. 利用欧姆定律:根据欧姆定律,计算电阻的值。

5. 使用串联和并联规则:对于串联电路,电流相同,电压相加;对于并联电路,电压相同,电流相加。

6. 注意符号的正负:在计算电流和电压时,要注意符号的正负,特别是在使用基尔霍夫定律时。

7. 注意电路的稳定性:在解题过程中,需要判断电路是否稳定,避免出现电路不稳定或产生杂散电流等情况。

8. 通过实际应用场景进行推理:在解题过程中,可以通过实际应用场景进行推理,例如根据电路的功能来推测电流的方向、电源的极性等。

9. 多用实例和练习:通过多做实例和练习,可以加深对电路解

题技巧的理解和掌握。

10. 注意特殊情况:在解题过程中要注意特殊情况,例如电路中存在开关、变压器等特殊元件,需要根据这些特殊情况进行分析。

电路题解题技巧

电路题解题技巧1. 哎呀呀,电路题解题可别蛮干呀!就像走迷宫,得找到关键入口。

你看,碰到那种复杂的电路图,先别急着下手,得像侦探一样观察,找到那些特别的节点或元件,那就是解题的突破口啦!比如一个电阻特别大的,或者一个奇怪连接的地方。

2. 嘿,记住啦,公式就是你的秘密武器!但可别死记硬背哟。

好比钥匙开不同的锁,一个公式可能在这道题好用,另一道就不行啦。

就像算电流,欧姆定律就是那把厉害的钥匙,在合适的场合用起来!比如说给定电压和电阻,那电流不就轻松算出来啦。

3. 哇塞,分析电路的串并联可太重要啦!这就跟辨认朋友关系一样,串联就是手牵手,并联就是肩并肩。

像那些灯泡啊,如果一个亮其他都亮,大概率就是串联啦。

这样一想,是不是一下子就清楚多了呀?4. 别小看了画图啊亲!画个清晰的图就像给自己建了个清晰的地图。

有时候题目里的图乱七八糟的,自己动手重新画一个,那感觉,豁然开朗啊!比如说把复杂的连线整理清楚,问题一下子就变得简单啦。

5. 哎呀呀,遇到难题别退缩呀!想一想,就像爬山,虽然累但爬上去风景多美呀。

每次解开一道难题,那成就感,爆棚啦!就像好不容易算出一个超级复杂电路里的参数,那开心劲儿,别提啦。

6. 要善于借鉴别人的方法哦!每个人都有自己的小妙招,就像武林高手,都有独家秘籍。

和同学讨论讨论,说不定别人的一招就能点亮你呢!比如说人家对某个概念的理解角度很独特,瞬间让你恍然大悟。

7. 最重要的是,要保持热情和耐心呀!电路题就像个小调皮,有时候会捉弄你,但只要你不离不弃,它最终会被你征服的。

就一直坚持下去,总会越来越厉害的!相信自己呀!总之,解电路题就是一场有趣的冒险,有技巧有方法,只要用心就能玩得转!。

电路题解题技巧

电路题解题技巧电路是电气工程中的基础,解题技巧对于学习和应用电路非常重要。

本文将介绍一些电路题解题的技巧和方法,帮助读者更好地理解和解决电路问题。

I. 了解基本电路定律在解决电路问题之前,我们首先要熟悉一些基本的电路定律,例如欧姆定律、基尔霍夫定律和电压分压定律等。

欧姆定律告诉我们电流和电阻的关系,可以表示为I = V/R。

基尔霍夫定律则描述了电流在电路中的流动和分配原理,包括电流守恒定律和电压守恒定律。

电压分压定律则是描述在串联电路中电压的分配原理,即V1/V2 = R1/R2。

理解这些基本的电路定律可以帮助我们更好地分析和解决各种电路问题。

II. 将电路转化为等效电路有时候,我们需要解决比较复杂的电路问题,此时将电路转化为等效电路可以简化我们的计算。

等效电路是指具有相同电流-电压关系的简化电路。

例如,如果我们需要计算一个由多个电压源和电阻串联组成的电路总电阻,我们可以将电路简化为一个等效电阻,这个等效电阻与原电路在终端电压和终端电流方面具有相同的关系。

通过等效电路的计算,我们可以用更简便的方式得到电路总电阻。

III. 使用戴维南等效电阻和诺顿等效电流定理戴维南定理和诺顿定理是解决电路问题非常重要的定理。

根据戴维南定理,任何线性电路都可以用一个等效电动势和一个等效电阻表示。

而诺顿定理则是戴维南定理的对偶,将等效电动势替换为等效电流。

运用这两个定理,我们可以通过简化电路分析,减少计算量,从而更快地得到电路的解答。

IV. 理解放大电路的工作原理放大电路是电子设备中常用的一种电路。

理解放大电路的工作原理对于解决与其相关的电路问题至关重要。

放大电路的核心是放大器。

放大器能够将输入信号放大到更大的幅度。

在放大电路中,我们需要关注放大器的增益、带宽、输出阻抗等参数。

了解这些参数和放大器的工作原理,我们能够更好地设计和改进放大电路,提高电路性能。

V. 使用频域分析法和相位提取法在解决电路问题时,有时我们需要进行频域分析。

电路设计中的电路图绘制技巧

电路设计中的电路图绘制技巧电路设计是电子工程领域中非常重要的一部分,电路图是电路设计的基础。

电路图是由各种不同的符号和线条组成的图形,代表着电路中的各个部件和元件,指示电路元件之间的连接方式和电路功能。

在这篇文章中,我们将讨论电路设计中电路图的绘制技巧。

1. 仔细阅读电路原理图首先,为了正确绘制电路图,必须对电路原理图进行仔细的阅读和理解。

电路原理图是一份比较直观的设计文件,需要我们通过对图形元素的理解来确定每个元件的功能。

2. 绘制导线导线是电路图的基本元素之一。

绘制导线时,需要将导线与元件正确地连接起来。

必须将导线与符号的线接头相对应,以确保电路中的各个部分可以正常地连接。

3. 标记电路元件在电路图中,必须标出所有使用的元器件型号,这是确保电路图的正确性非常重要的一个步骤。

标记电路元件时,必须要仔细查看原理图规格书或元器件的规格书,确保准确地标注元件的型号。

这将使得电路图可以作为一个非常准确的参考文档。

4. 鉴别元件电路中使用的元器件有很多,有的很小,部分甚至只有几个针脚。

在绘制电路图时,必须具备区别不同元器件的能力,只有这样才能保证电路图的准确性。

5. 线条宽度、颜色及反向设定正确的线条宽度和颜色对于电路图的绘制非常重要。

线条宽度和颜色可以使得电路图更加清晰易懂。

另外,反向设定也是非常重要的。

可以通过黑白和反色来表示交流和直流电路,这样可以方便地把不同的电路区分开来。

6. 进行电路模拟及实验验证电路模拟和电路验证是电路设计中非常重要的一环。

它可以通过软件仿真和实际电路验证,来验证电路图的正确性。

7. 重复审查电路图通过以上步骤对电路图进行了绘制之后,需要进行多次的审查以确保电路图的准确性。

可以通过让多个人分别阅读电路图的方式来审查电路图。

通过这种方法,可以更加容易地检测电路图中的各种问题。

总结:以上是电路设计中的电路图绘制技巧介绍。

电路图的准确性非常重要,只有准确的电路图才能保证电路的实际效果。

电路设计的几大基本方法

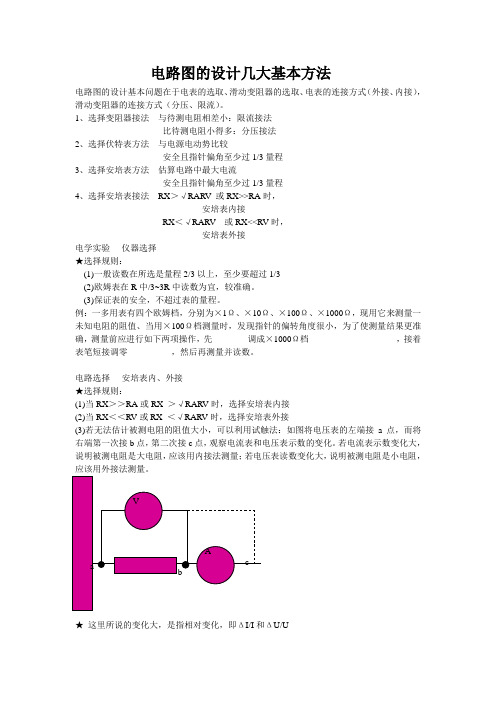

电路图的设计几大基本方法电路图的设计基本问题在于电表的选取、滑动变阻器的选取、电表的连接方式(外接、内接),滑动变阻器的连接方式(分压、限流)。

1、选择变阻器接法---与待测电阻相差小:限流接法比待测电阻小得多:分压接法2、选择伏特表方法---与电源电动势比较安全且指针偏角至少过1/3量程3、选择安培表方法---估算电路中最大电流安全且指针偏角至少过1/3量程4、选择安培表接法---RX >√RARV 或RX>>RA 时,安培表内接RX <√RARV 或RX<<RV 时,安培表外接电学实验----仪器选择★选择规则:(1)一般读数在所选是量程2/3以上,至少要超过1/3(2)欧姆表在R 中/3~3R 中读数为宜,较准确。

(3)保证表的安全,不超过表的量程。

例:一多用表有四个欧姆档,分别为×1Ω、×10Ω、×100Ω、×1000Ω,现用它来测量一未知电阻的阻值、当用×100Ω档测量时,发现指针的偏转角度很小,为了使测量结果更准确,测量前应进行如下两项操作,先 调成×1000Ω档 ,接着 表笔短接调零 ,然后再测量并读数。

电路选择----安培表内、外接★选择规则:(1)当RX >>RA 或RX >√RARV 时,选择安培表内接(2)当RX <<RV 或RX <√RARV 时,选择安培表外接(3)若无法估计被测电阻的阻值大小,可以利用试触法:如图将电压表的左端接a 点,而将右端第一次接b 点,第二次接c 点,观察电流表和电压表示数的变化。

若电流表示数变化大,说明被测电阻是大电阻,应该用内接法测量;若电压表读数变化大,说明被测电阻是小电阻,应该用外接法测量。

★ 这里所说的变化大,是指相对变化,即ΔI/I 和ΔU/Ua V Ab c电路选择----变阻器分压、限流接法★选择规则----限流接法(1)电阻上电压读数范围较小。

初中物理电路设计的解题技巧.教师版

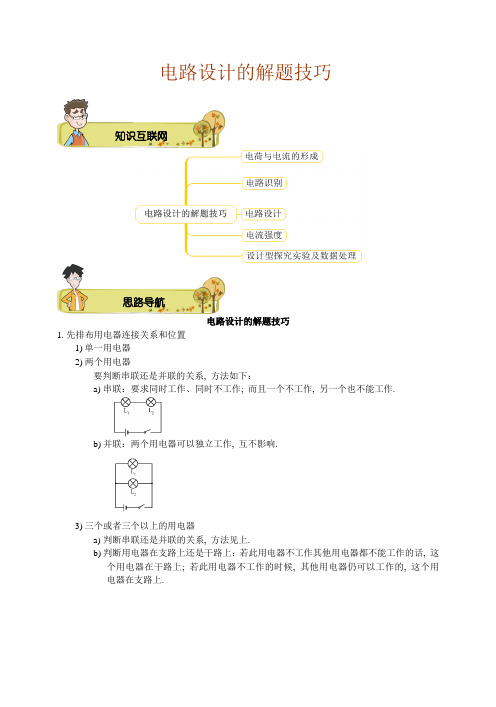

电路设计的解题技巧知识互联网思路导航电路设计的解题技巧1.先排布用电器连接关系和位置1)单一用电器2)两个用电器要判断串联还是并联的关系, 方法如下:a)串联:要求同时工作、同时不工作; 而且一个不工作, 另一个也不能工作.b)并联:两个用电器可以独立工作, 互不影响.3)三个或者三个以上的用电器a)判断串联还是并联的关系, 方法见上.b)判断用电器在支路上还是干路上:若此用电器不工作其他用电器都不能工作的话, 这个用电器在干路上; 若此用电器不工作的时候, 其他用电器仍可以工作的, 这个用电器在支路上.2. 再排布开关的位置和连接关系1) 判断支路开关还是干路开关a) 若开关断开, 干路、支路所有用电器都不工作了, 说明是干路开关.b) 若开关可以单独控制其中某一个用电器, 对其他用电器没有影响, 说明是支路开关. 2) 判断多个开关之间是串联还是并联a) 开关串联:多条件同时满足(一个条件就是一个开关), 也叫“一票否决制”.b) 开关并联:只要满足任何一个条件, 也叫“一票通过制”.3) 单刀多掷开关、双刀双掷开关【例1】 (2013昌平一模)2.下列文具中, 通常情况下属于绝缘体的是( )A .铅笔芯B .塑料笔杆C .金属小刀D .不锈钢尺 【答案】 B【例2】 (2013东城一模)2.下列物体通常情况下都属于绝缘体的一组是( )A .汽油和盐水B .塑料和陶瓷C .人体和大地D .黄铜和石墨 【答案】 B 例题精讲模块一 电荷与电流的形成【例3】(2013大兴一模)20.定向移动形成电流. 物理学中规定定向移动的方向为电流的方向.【答案】电荷; 正电荷【例4】判断: 1. 闭合的电路中有电流, 就一定有正电荷发生定向移动( )2. 只有正电荷定向移动才能形成电流( )3. 金属导体中的电流是自由电子定向移动形成的()4. 金属导体中的电流方向与自由电子定向移动方向相反( )5. 如果正负电荷同时做定向移动, 则不会形成电流( )【答案】×× √ √ ×【解析】金属导电靠带负电的自由电子; 溶液导电靠正、负离子.【例5】电源是将能转化成能的装置; 用电器是将能转化成能的装置. 【答案】其他形式电; 电其他形式【例6】(2013朝阳一模)11.如图甲为一实物电路连接图, 如图乙是某同学所画出其对应的电路图, 正确的是( )【答案】C【例7】只改动一根导线, 让两盏灯并联发光.【答案】例题精讲模块二电路识别L1S2SL1L2SL1L2SSL1+-L2A B C D图甲图乙【例8】 (2013丰台一模)11.某品牌的微型电脑吸尘器有两个开关, 开关S 1控制照明灯L 和电动机M, 开关S 2只控制电动机M. 如图所示电路中, 符合要求的是( )【答案】 B【例9】 (2013海淀一模)12.图甲所示为一台电压力锅, 它结合了高压锅和电饭锅的优点, 省时省电、安全性高. 当电压力锅内部气压过大或温度过高时, 发热器都会停止工作. 图乙中S 1为过压保护开关, S 2为过热保护开关, 压强过大时开关S 1自动断开, 温度过高时开关S 2自动断开. 图乙表示S 1、S 2和锅内发热器的连接情况, 其中符合上述工作要求的是( )【答案】 A发热器S 1 S 2220V发热器S 1S 2 220V发热器S 1 220VS 2S 1220VS 2发热器 A B C D甲 乙ABDCLS 1 S 2 M LMS 1S 2L MS 1S 2L MS 1S 2 例题精讲模块三 电路设计【答案】【例10】(2011年天津市和平区一模)如图所示, 有带风叶的小电动机一只, 电热丝R一段, 开关两只, 插头一只, 导线若干.利用这些器材可以连成一个有冷热两档风的电吹风电路.要求:只闭合S1时吹冷风, 只闭合S2时既无风又不发热, 同时闭合S1、S2时吹热风.(1)请你在虚线框内画出电路图; (2)请你按要求将图中的元件连接起来.【答案】【例11】(第21届全国应用物理知识竞赛初赛)为了节省电能, 居民楼的楼道灯通常由两个开关共同控制. 一个是利用光敏器件制成的“光控开关”, 它的作用是光线暗时自动闭合, 光线亮时自动断开; 一个是利用声敏器件制成的“声控开关”, 它的作用是有声音时自动闭合电路, 两分钟后, 若再无声音则自动断开.(1)请将图甲中的器材连成符合上述楼道灯要求的电路.(2)小明受楼道灯电路的启发, 在爷爷的卧室里也安装了这样一个“聪明”的电路. 晚上只要拍拍手, 灯就亮了, 过一会自动熄灭, 给爷爷带来了方便. 不过遇到晚上有雷雨,就麻烦了, 雷声使灯不断被点亮, 影响爷爷休息. 还有爷爷睡觉前需要这盏灯一直被点亮. 现在再给你两个开关S1、S2, 在图乙中完成对这个“聪明”电路的改装. 并分别说明在灯自动工作、晚上打雷需取消自动功能和需要灯一直被点亮时开关S1、S2的断开与闭合情况.【答案】(1)见左图. 电源声控开关光控开关电源声控开关光控开关甲乙(2)见右图.需灯自动工作时, 断开S l , 闭合S2 .晚上打雷时断开S2.需要灯一直被点亮时闭合S1和S2【例12】(2013昌平一模)13.在学习了电路知识以后, 教师要求学生练习安装楼梯照明灯, 即用两个单刀双掷开关S1和S2同时控制同一盏灯, 其中任意一个开关都可以使灯亮或灭.请判断如图所示的四个电路中, 不符合上述要求的是(图中均用电池符号表示照明电路)电源)(【例13】请分析一下单刀多掷开关拨到不同档位时用电器的工作情况【答案】1图:0档位不工作; 1档位时2~7号电阻串联工作; 2档位时1和8号电阻串联工作.2图:1档位时东西方向红灯亮、南北方向绿灯亮; 2档位时东西南北方向均黄灯亮;3档位时东西方向绿灯亮、南北方向红灯亮.【例14】“五一”长假即将来临, 小红和爸爸妈妈商量外出旅游的事. 为此, 他们设计了一架简易的游戏机, 如图所示, 电路由三个单独单刀双掷开关、一个电池组、一个灯泡和若干导线组成, 三人各自操纵自己的开关, 以表示自己愿意去旅游还是留守家中. 考虑到小红还属于未成年人在所有方案中, 只要出现小红单独一人出外旅游或留守家中的方案时,灯泡将不发光, 表明该方案无效, 除此以外的一切旅游方案均有效(即灯泡会发光). 为了满足该条件, 游戏机线路设计图应该是下图的()【答案】 D【例15】 (2013大兴一模)11.如图所示的四个电路中, 电流表连接正确的是( )A B C D 【答案】 B【例16】 某同学在连接电流表的过程中, 出现下列现象并及时加以处理, 其中处理错误的是( )A .表针静止不动, 表明电流表与被测电路并联; 拆除全部导线、重新连接B .表针向右微转, 没有超过表盘上的一个小格; 换用能够测量较小的量程C .表针向右猛偏, 超过表盘上的最大电流; 换用能够测量较大的量程D .表针向左反转, 表明电流表两个接线柱接反; 立即对调连接两接线柱的导线头例题精讲模块四 电流强度【答案】 A【例17】 (2012•益阳)如图所示的电路中, 闭合开关时, 下列说法正确的是( )A .两灯泡串联B .电流表测的是总电流C .电流表测的是L 1的电流D .电流表测的是L 2的电流【答案】 C【例18】 如图所示的电路中, 已知S 闭合后, 通过两灯L 1、L 2列说法中正确的是( )A .A 1的示数为0.6A, A 2的示数为0.4AB .A 1的示数为0.6A, A 2的示数为1AC .A 1的示数为1A, A 2的示数为0.4AD .A 1、A 2示数都是1A 【答案】 C【例19】 如图所示, a 接电源正极, b 接电源负极, 通过电阻1R 的电流I 1=2.5A, 通过电阻2R 的电流I 2=2A, 通过电阻3R 电流I 3=3A, 试问, 电流表A 1和A 2的读数各为多大?【答案】 A 1:5A A 2:4.5A【例20】 如图是小李同学研究并联电路电流特点的电路图.当开关S 闭合时, 电流表A 1无示数,电流表A 2有正常示数; 如把两灯互换, 闭合开关S 后两电流表均有正常示数.则该电路中存在的故障是( )SL 1L 2A 2A 1A .L 1开路B .L 1短路C .L 2开路D .L 2短路【答案】 A【例21】 (2008•黄石)如图所示电路中, 电源电压保持不变.当闭合开关S 后, 两灯均能发光, 过了一会儿, L 1灯熄灭, 但L 2仍在发光, 经检查L 1灯丝被烧断了.对前后二种不同情况下电路中电流表示数的判断正确的是( )A .A 1表示数减小, A 2表示数不变B .A 1、A 2表示数均不变C .A 1表示数减小, A 2表示数增大 L2L 1S A 2A 1SL 1L 2A 2A 1D .A 1、A 2表示数均增大【答案】 A【例22】 (2012门头沟二模)36.实验桌上有如下实验器材:满足实验要求的电源、阻值已知的定值电阻各一个, 电阻箱(电路图符号)一个, 已调零的电流表两块, 开关两个, 导线若干. 请选用上述实验器材, 设计一个实验证明“两个电阻R 1与R 2并联时, 干路电流I 与支路电流I 2的关系为:I = I 2+ b (b 为常量)”. 请你画出实验电路图, 写出实验步骤, 画出实验数据记录表.【答案】 (由于学生都上过电学预科, 知道电阻箱的基本特点)电路图实验步骤:(1)按电路图将已调好的各电路元件连入电路.(2)闭合开关, 调节电阻箱R 2的阻值, 用电流表A 1测量通过干路的电流I , 用电流表A 2测量通过电阻箱的电流I 2,并记录I 和I 2.(3)仿照步骤(2), 分别改变5次电阻箱R 2的阻值, 用电流表A 1测量通过干路的电流I , 用 电流表A 2测量通过电阻箱的电流I 2, 并分别将测量数据记录在实验数据记录表中. (4)分析实验数据, 得出结论. I 2/AI /A【例23】 (2012海淀一模)32.小明在探究并联电路中电流关系时, 根据实验数据绘制了干路电流I 随支路电流I 1变化的图像, 如图所示, 请你根据该图像写出干路电流I 和支路电流I 1的关系式:I = .例题精讲模块五 设计型探究实验及数据处理A 1 R 1A 2 R 2S【答案】I=I1+0.6A复习巩固【练1】(2012丰台二模)2. 下列说法正确的是( )A.自由电子的定向移动可以形成电流B.负电荷定向移动的方向为电流方向C.金属导体中形成电流的是正电荷的定向移动D.金属导体中, 电流方向与电荷的定向移动方向相同【答案】A【练2】(2009•威海)如图所示, 在探究并联电路中的电流关系时, 小明同学用电流表测出A、B、C三处的电流分别为I A=0.5A, I B=0.3A, I C=0.2A, 在表格中记录数据后, 下一步首先应该做的是( )A.整理器材, 结束实验B.分析数据, 得出结论C.换用不同规格的小灯泡, 再测出几组电流值D.换用电流表的另一量程, 再测出一组电流值【答案】C【练3】如图所示的电路中, 闭合开关, 电流表测量的是( )A.通过灯L l的电流B.通过灯L2的电流C.通过灯L1和灯L2的电流之和D.电源供给电路的总电流【答案】B。

解析电路计算题的基本步骤与技巧

解析电路计算题的基本步骤与技巧电路计算是电子工程领域中的重要基础,它涉及到电流、电压、电阻等概念的运用与计算。

掌握解析电路计算题的基本步骤与技巧,对于提高电子工程师的计算能力和电路设计能力至关重要。

本文将介绍一些基本的步骤与技巧,帮助读者更好地理解和解决电路计算题。

一、明确问题要求和已知条件解析电路计算题首先要明确题目中要求解决的问题以及已知的条件。

对于给定的电路,常常需要计算电流、电压和功率等数值。

通过仔细阅读和分析题目中的描述,明确需要计算的量和已知的条件,有助于我们更好地理解问题的本质,从而为解决问题做好准备。

二、应用欧姆定律和基本电路知识解析电路计算题的基本工具是欧姆定律,即U=IR,它描述了电压、电流和电阻之间的关系。

在计算过程中,我们可以根据已知条件利用欧姆定律推导出需要求解的变量与已知变量之间的关系式。

此外,还需要熟悉串联、并联电阻的计算公式,以及电流分流、电压分压等基本电路知识,这些都是解决电路计算题的基础。

三、应用基尔霍夫电流法和基尔霍夫电压法基尔霍夫电流法和基尔霍夫电压法是求解复杂电路的重要工具。

基尔霍夫电流法是指在节点法的基础上,根据电流守恒原理,在每个节点处建立方程,通过解方程组可以计算各节点的电流值。

基尔霍夫电压法是指在网孔法的基础上,根据能量守恒原理,在每个网孔处建立方程,通过解方程组可以计算各支路电流和电压值。

掌握这两种方法可以解决复杂电路的分析与计算问题。

四、注意电路中的特殊情况和细节在解析电路计算题时,还需要注意电路中的特殊情况和细节。

例如,在串联电路中,电流相等而电压不同;在并联电路中,电压相等而电流不同。

此外,还需要注意并联电阻的计算方法和电源的内阻对电路计算的影响等。

这些特殊情况和细节都会影响电路的计算结果,因此我们在解决问题的过程中应该保持细致和耐心。

五、通过实例演练提高计算能力掌握电路计算的基本步骤和技巧需要不断的实践和学习。

我们可以通过大量的实例演练,提高自己的计算能力和解析问题的能力。

电路的识别与设计

电路的识别与设计考点 考查规律电路的识别 串并联电路的认识和识别电路的设计 根据要求考查学生对题意的理解,设计合理电路 【知识链接】连接方式电流路径工作特点开关控制1条用电器同时工作,相互影响开关控制整个电路,与位置无关两条或两条以上用电器独立工作,互不影响干路开关控制整个电路,支路开关控制所在支路【解题技巧】1、电路识别的方法:识别串并联电路的方法有许多,常用的有“路径法”、“拆除法”、“去表法”等等。

“路径法”——按电路中电流的方向画出电流路径,看有几条。

判断的依据是:串联电路只有一条电路路径,并联则有多条。

“拆除法”——即拆除电路中的某个用电器观察其他用电器是否正常工作,依据是:串联电路中的用电器工作相互影响,并联电路则能够独立工作。

“去表法”——电压表所在位置视为断路(因电压表内阻很大,几乎无电流通过);电流表所在位置可视为导线(因电流表内阻很小,电阻可视为零)2、电路设计方法及技巧:(1)用电器串并联:用电器互相影响的,一般设计为串联电路;用电器互不影响的,一般设计为并联电路。

(2)开关的串并联:两个或两个以上的开关同时闭合,用电器才能工作的,开关一般设计为串联;无论闭合哪一个开关,都能控制用电器,开关一般设计为并联。

(3)开关与用电器的关系:开关只能控制某个用电器,开关与用电器串联;开关能控制整个电路,开关设计在干路上。

开关与用电器并联,开关闭合后用电器不工作,开关断开后用电器工作——局部短路。

【例1】与实物图对应的电路图是()A B C D【例2】小明利用如图所示的电路探究并联电路中干路电流是否等于各支路电流之和,其中有一根导线接错了,接错的导线是()A.导线1 B.导线2 C.导线3 D.导线4【例3】如图所示的电路中,闭合开关S 1、S 2,电流表、灯泡L 1和L 2均能正常工作。

则下列说法正确的是( )A .开关S 1、S 2都闭合,灯泡L 1和L 2并联B .开关S 1闭合,S 2断开,电源外部电流流向为a→b→c→dC .开关S 1、S 2都闭合,通过灯泡L 1的电流一定大于通过灯泡L 2的电流D .闭合S 1、S 2中任意一个开关,都会有灯泡发光【例4】如图,下列说法错误的是( )A .S 1、S 3断开,S 2闭合时,灯L 1、L 2串联B .S 1、S 3闭合,S 2断开时,灯L 1、L 2并联C .S 1、S 2闭合,S 3断开时,灯L 1亮D .S 2、S 3闭合,S 1断开时,灯L 1亮【例5】小明为养鸡场设计报警器电路,养鸡场的前、后门分别装有开关S1、S2,动物闯入时开关会自动闭合,要求:只要动物闯入任意一个门,电铃都能响起警报,图中符合设计要求的是()A B C D【例6】有人发明了“感应照孔门把手”只有在夜间且有人摸门把手时,锁孔旁的灯才亮,从而方使夜间开锁,它利用感应开关S1(有人摸门把手时,S1闭合;无人摸门把手,S1断开)以及光敏开关S2(天暗时S2闭合,天亮时S2断开)控制电路,达到目的。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

(2)见右图.

需灯自动工作时,断开Sl,闭合S2.

晚上打雷时断Biblioteka S2需要灯一直被点亮时闭合S1和S2.

【例12】(2013昌平一模)13.在学习了电路知识以后,教师要求学生练习安装楼梯照明灯,即用两个单刀双掷开关S1和S2同时控制同一盏灯,其中任意 一个开关都可以使灯亮或灭.请判断如图所示的四个电路中,不符合上述要求的是(图中均用电池符号表示照明电路电源)( )

【答案】D

【例13】请分析一下单刀多掷开关拨到不同档位时用电器的工作情况

【答案】1图:0档位不工作; 1档位时2~7号电阻串联工作; 2档位时1和8号电阻串联工作.

2图:1档位时东西方向红灯亮、南北方向绿灯亮; 2档位时东西南北方向均黄灯亮;

3档位时东西方向绿灯亮、南北方向红灯亮.

【例14】“五一”长假即将来临,小红和爸爸妈妈商量外出旅游的事.为此,他们设计了一架简易的游戏机,如图所示,电路由三个单独单刀双掷开关、一个电池组、一个灯泡和若干导线组成,三人各自操纵自己的开关,以表示自己愿意去旅游还是留守家中.考虑到小红还属于未成年人在所有方案中,只要出现小红单独一人出外旅游或留守家中的方案时,灯泡将不发光,表明该方案无效,除此以外的一切旅游方案均有效(即灯泡会发光).为了满足该条件,游戏机线路设计图应该是下图的( )

【答案】

【例11】(第21届全国应用物理知识竞赛初赛)为了节省电能,居民楼的楼道灯通常由两个开关共同控制.一个是利用光敏器件制成的“光控开关”,它的作用是光线暗时自动闭合,光线亮时自动断开;一个是利用声敏器件制成的“声控开关”,它的作用是有声音时自动闭合电路,两分钟后,若再无声音则自动断开.

(1)请将图甲中的器材连成符合上述楼道灯要求的电路.

【答案】B

【例3】(2013大兴一模)20.定向移动形成电流.物理学中规定定向移动的方向为电流的方向.

【答案】电荷;正电荷

【例4】判断:1.闭合的电路中有电流,就一定有正电荷发生定向移动( )

2.只有正电荷定向移动才能形成电流( )

3.金属导体中的电流是自由电子定向移动形成的( )

4.金属导体中的电流方向与自由电子定向移动方向相反( )

C三处的电流分别为IA=0.5A,IB=0.3A,IC=0.2A,在表格中记录数据后,下一步首先应该

做的是( )

b)开关并联:只要满足任何一个条件,也叫“一票通过制”.

3)单刀多掷开关、双刀双掷开关

【例1】(2013昌平一模)2.下列文具中,通常情况下属于绝缘体的是( )

A.铅笔芯B.塑料笔杆C.金属小刀D.不锈钢尺

【答案】B

【例2】(2013东城一模)2.下列物体通常情况下都属于绝缘体的一组是( )

A.汽油和盐水B.塑料和陶瓷C.人体和大地D.黄铜和石墨

1【答案】(由于学生都上过电学预科,知道电阻箱的基本特点)

电路图

实验步骤:

(1)按电路图将已调好的各电路元件连入电路.

(2)闭合开关,调节电阻箱R2的阻值,用电流表A1测量通过干路的电流I,用电流表A2

测量通过电阻箱的电流I2,并记录I和I2.

(3)仿照步骤(2),分别改变5次电阻箱R2的阻值,用电流表A1测量通过干路的电流I,用

A.L1开路B.L1短路C.L2开路D.L2短路

【答案8】A

【例21】 (2008•黄石)如图所示电路中,电源电压保持不变.当闭合开关S后,两灯均能发光,过了一会儿,L1灯熄灭,但L2仍在发光,经检查L1灯丝被烧断了.对前后二种不同情况下电路中电流表示数的判断正确的是( )

A.A1表示数减小,A2表示数不变

【答案2】D

【例15】(2013大兴一模)11.如图所示的四个电路中,电流表连接正确的是( )

ABCD

【答案3】B

【例16】某同学在连接电流表的过程中,出现下列现象并及时加以处理,其中处理错误的是( )

A.表针静止不动,表明电流表与被测电路并联;拆除全部导线、重新连接

B.表针向右微转,没有超过表盘上的一个小格;换用能够测量较小的量程

【例19】 如图所示,a接电源正极,b接电源负极,通过电阻 的电流I1=2.5A,通过电阻 的电流I2=2A,通过电阻 电流I3=3A,试问,电流表A1和A2的读数各为多大?

【答案7】A1:5A A2:4.5A

【例20】如图是小李同学研究并联电路电流特点的电路图.当开关S闭合时,电流表A1无示数,电流表A2有正常示数;如把两灯互换,闭合开关S后两电流表均有正常示数.则该电路中存在的故障是( )

电路设计的解题技巧

1.先排布用电器连接关系和位置

1)单一用电器

2)两个用电器

要判断串联还是并联的关系,方法如下:

a)串联:要求同时工作、同时不工作;而且一个不工作,另一个也不能工作.

b)并联:两个用电器可以独立工作,互不影响.

3)三个或者三个以上的用电器

a)判断串联还是并联的关系,方法见上.

b)判断用电器在支路上还是干路上:若此用电器不工作其他用电器都不能工作的话,这个用电器在干路上;若此用电器不工作的时候,其他用电器仍可以工作的,这个用电器在支路上.

(2)小明受楼道灯电路的启发,在爷爷的卧室里也安装了这样一个“聪明”的电路.晚上只要拍拍手,灯就亮了,过一会自动熄灭,给爷爷带来了方便.不过遇到晚上有雷雨,就麻烦了,雷声使灯不断被点亮,影响爷爷休息.还有爷爷睡觉前需要这盏灯一直被点亮.现在再给你两个开关S1、S2,在图乙中完成对这个“聪明”电路的改装.并分别说明在灯自动工作、晚上打雷需取消自动功能和需要灯一直被点亮时开关S1、S2的断开与闭合情况.

5.如果正负电荷同时做定向移动,则不会形成电流( )

【答案】×× √√×

【解析】金属导电靠带负电的自由电子;溶液导电靠正、负离子.

【例5】电源是将能转化成能的装置;用电器是将能转化成能的装置.

【答案】其他形式电;电其他形式

【例6】(2013朝阳一模)11.如图甲为一实物电路连接图,如图乙是某同学所画出其对应的电路图,正确的是( )

【答案5】C

【例18】 如图所示的电路中,已知S闭合后,通过两灯L1、L2的电流分别为0.6A和0.4A,则下列说法中正确的是( )

A.A1的示数为0.6A,A2的示数为0.4A

B.A1的示数为0.6A,A2的示数为1A

C.A1的示数为1A,A2的示数为0.4A

D.A1、A2示数都是1A

【答案6】C

B.A1、A2表示数均不变

C.A1表示数减小, A2表示数增大

D.A1、A2表示数均增大

【答案9】A

【例22】(2012门头沟二模)36.实验桌上有如下实验器材:满足实验要求的电源、阻值已知的定值电阻各一个,电阻箱(电路图符号 )一个,已调零的电流表两块,开关两个,导线若干.请选用上述实验器材,设计一个实验证明“两个电阻R1与R2并联时,干路电流I与支路电流I2的关系为:I=I2+b(b为常量)”.请你画出实验电路图,写出实验步骤,画出实验数据记录表.

【答案】C

【例7】只改动一根导线,让两盏灯并联发光.

【答案】

【例8】(2013丰台一模)11.某品牌的微型电脑吸尘器有两个开关,开关S1控制照明灯L和电动机M,开关S2只控制电动机M.如图所示电路中,符合要求的是( )

【答案】B

【例9】(2013海淀一模)12.图甲所示为一台电压力锅,它结合了高压锅和电饭锅的优点,省时省电、安全性高.当电压力锅内部气压过大或温度过高时,发热器都会停止工作.图乙中S1为过压保护开关,S2为过热保护开关,压强过大时开关S1自动断开,温度过高时开关S2自动断开.图乙表示S1、S2和锅内发热器的连接情况,其中符合上述工作要求的是( )

2【答案】I=I1+0.6A

【练1】(2012丰台二模)2.下列说法正确的是( )

A.自由电子的定向移动可以形成电流

B.负电荷定向移动的方向为电流方向

C.金属导体中形成电流的是正电荷的定向移动

D.金属导体中,电流方向与电荷的定向移动方向相同

3【答案】A

【练2】(2009•威海)如图所示,在探究并联电路中的电流关系时,小明同学用电流表测出A、B、

电流表A2测量通过电阻箱的电流I2,并分别将测量数据记录在实验数据记录表中.

(4)分析实验数据,得出结论.

实验数据记录表

I2/A

I/A

【例23】(2012海淀一模)32.小明在探究并联电路中电流关系时,根据实验数据绘制了干路电流I随支路电流I1变化的图像,如图所示,请你根据该图像写出干路电流I和支路电流I1的关系式:I=.

2.再排布开关的位置和连接关系

1)判断支路开关还是干路开关

a)若开关断开,干路、支路所有用电器都不工作了,说明是干路开关.

b)若开关可以单独控制其中某一个用电器,对其他用电器没有影响,说明是支路开关.

2)判断多个开关之间是串联还是并联

a)开关串联:多条件同时满足(一个条件就是一个开关),也叫“一票否决制”.

【答案】A

【例10】(2011年天津市和平区一模)

如图所示,有带风叶的小电动机一只,电热丝R一段,开关两只,插头一只,导线若干.利用这些器材可以连成一个有冷热两档风的电吹风电路.

要求:只闭合S1时吹冷风,只闭合S2时既无风又不发热,同时闭合S1、S2时吹热风.

(1)请你在虚线框内画出电路图; (2)请你按要求将图中的元件连接起来.

C.表针向右猛偏,超过表盘上的最大电流;换用能够测量较大的量程

D.表针向左反转,表明电流表两个接线柱接反;立即对调连接两接线柱的导线头

【答案4】A

【例17】 (2012•益阳)如图所示的电路中,闭合开关时,下列说法正确的是( )

A.两灯泡串联

B.电流表测的是总电流

C.电流表测的是L1的电流

D.电流表测的是L2的电流