本科毕业设计---基于fpga的汉明码译码器的设计

基于FPGA汉明码编译码器设计

基于FPGA汉明码编译码器设计汉明码是一种能够检测和纠正错误的编码方式。

在FPGA(Field Programmable Gate Array)中,我们可以使用FPGA来设计并实现一个基于(7,4)汉明码的编码器和解码器。

1.编码器设计:编码器将4位数据编码为7位汉明码。

下面是一个基于FPGA的(7,4)汉明码编码器的设计步骤:-设置一个4位输入端口和一个7位输出端口。

-创建一个4×7的矩阵,用于存储所有可能输入与对应汉明码的关系。

每行代表一个输入,每列代表一个汉明码位。

-在FPGA中,使用逻辑门(如XOR门和AND门)来实现矩阵的功能。

根据矩阵,依次设计逻辑门电路来计算每个汉明码位。

例如,对于第一个汉明码位,使用四个输入位的异或门计算出结果。

-将每个汉明码位的结果输出到对应的输出端口。

2.解码器设计:解码器将7位汉明码解码为4位数据。

下面是一个基于FPGA的(7,4)汉明码解码器的设计步骤:-设置一个7位输入端口和一个4位输出端口。

-创建一个7×4的矩阵,用于存储所有可能的汉明码与对应的输出数据的关系。

每行代表一个汉明码,每列代表一个输出数据位。

-同样,使用逻辑门来实现矩阵的功能。

根据矩阵,依次设计逻辑门电路来计算每个输出数据位。

例如,对于第一个数据位,使用七个输入位的与门计算出结果。

-将每个输出数据位的结果输出到对应的输出端口。

3.性能分析和优化:可以通过FPGA的资源利用率和时钟频率等指标对设计进行性能评估。

通过仔细设计逻辑电路,合理分配资源和优化电路,可以提高编码器和解码器的性能。

可以考虑使用并行计算、流水线等技术来提高时钟频率和减少时延。

另外,还可以在FPGA中使用多个编码器和解码器来实现更高级的错误检测和纠正功能。

可以考虑使用更高级的汉明码,如(15,11)汉明码或(31,26)汉明码,来提高错误检测和纠正能力。

可以结合其他编码技术,如校验和,奇偶校验等,来增加冗余度和提高系统的可靠性。

实验报告书汉明码设计与实现

实验报告书------汉明码设计与实现汉明码编译码器系统班级: 姓名: 学号:一.实验原理描述1.1汉明码编码原理一般来说,若汉明码长为n ,信息位数为k ,则监督位数r=n-k 。

若希望用r 个监督位构造出r 个监督关系式来指示一位错码的n 种可能位置,则要求21r n -≥或211rk r -≥++(1)下面以(7,4)汉明码为例说明原理:设汉明码(n,k )中k=4,为了纠正一位错码,由式(1)可知,要求监督位数r ≥3。

若取r=3,则n=k+r=7。

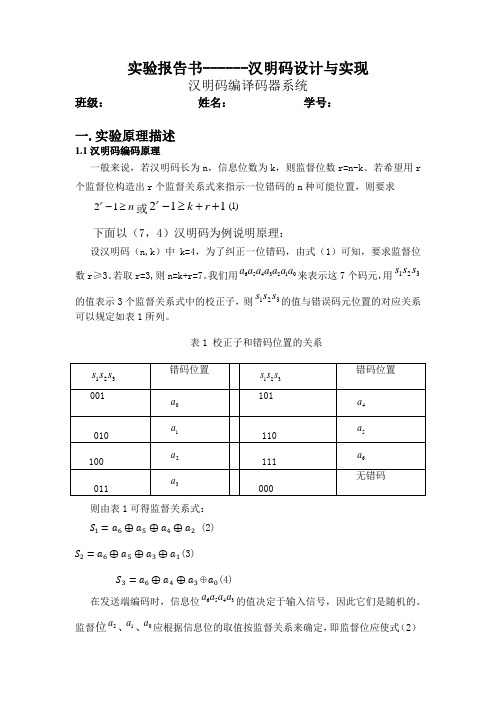

我们用6543210a a a a a a a 来表示这7个码元,用123s s s 的值表示3个监督关系式中的校正子,则123s s s 的值与错误码元位置的对应关系可以规定如表1所列。

表1 校正子和错码位置的关系则由表1可得监督关系式: S 1=a 6⊕a 5⊕a 4⊕a 2 (2)S 2=a 6⊕a 5⊕a 3⊕a 1(3)S 3=a 6⊕a 4⊕a 3⊕a 0(4) 在发送端编码时,信息位6543a a a a 的值决定于输入信号,因此它们是随机的。

监督位2a 、1a 、0a 应根据信息位的取值按监督关系来确定,即监督位应使式(2)~式(4)中1s 、2s 、3s的值为0(表示编成的码组中应无错码){a 6⊕a 5⊕a 4⊕a 2=0a 6⊕a 5⊕a 3⊕a 1=0a 6⊕a 4⊕a 3⊕a 0=0(5)式(5)经过移项运算,接触监督位{a 2=a 6⊕a 5⊕a 4a 1=a 6⊕a 5⊕a 3a 0=a 6⊕a 4⊕a 3(6)式(5)其等价形式为: [1 1 1 0 1 0 01 1 0 1 0 1 01 0 1 1 0 0 1][ a 6a 5a 4a 3a 2a 1a 0]=[000](7)式(6)还可以简记为H ∙A T =0T 或A ∙H T =0 (8)其中H =[1 1 1 0 1 0 01 1 0 1 0 1 01 0 1 1 0 0 1]A =[a 6a 5a 4a 3a 2a 1a 0]P =[1 1 1 01 1 0 11 0 1 1]I r =[1 0 00 1 00 0 1]0=[0 0 0]所以有H =[PI r ](9)式(6)等价于[a 2a 1a a ]=[a 6 a 5 a 4 a 3][1 1 11 1 01 0 10 1 1]=[a 6 a 5 a 4a 3]Q (10)其中Q 为P 的转置,即T Q P (11)式(10)表示,信息位给定后,用信息位的行矩阵乘矩阵Q 就产生出监督位。

FPGA实验二2-4译码器设计实验报告原版

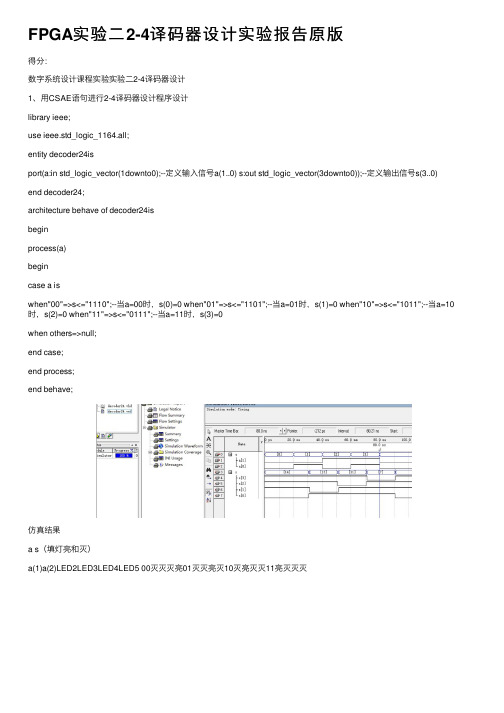

FPGA实验⼆2-4译码器设计实验报告原版得分:数字系统设计课程实验实验⼆2-4译码器设计1、⽤CSAE语句进⾏2-4译码器设计程序设计library ieee;use ieee.std_logic_1164.all;entity decoder24isport(a:in std_logic_vector(1downto0);--定义输⼊信号a(1..0) s:out std_logic_vector(3downto0));--定义输出信号s(3..0) end decoder24;architecture behave of decoder24isbeginprocess(a)begincase a iswhen"00"=>s<="1110";--当a=00时,s(0)=0 when"01"=>s<="1101";--当a=01时,s(1)=0 when"10"=>s<="1011";--当a=10时,s(2)=0 when"11"=>s<="0111";--当a=11时,s(3)=0when others=>null;end case;end process;end behave;仿真结果a s(填灯亮和灭)a(1)a(2)LED2LED3LED4LED5 00灭灭灭亮01灭灭亮灭10灭亮灭灭11亮灭灭灭下载后LED2,6,7亮按下up后LED4,6,7亮2、⽤IF语句进⾏2-4译码器设计程序设计library ieee;use ieee.std_logic_1164.all;entity d24isport(a:in std_logic_vector(1downto0);--定义输⼊信号a(1..0) s:out std_logic_vector(3downto0));--定义输出信号s(3..0) end d24;architecture behave of d24isbeginprocess(a)beginif a="00"then s<=(0=>'0',others=>'1');--当a=00时,s(0)=0 elsif a="01"then s<=(1=>'0',others=>'1');--当a=01时,s(1)=0 elsifa="10"then s<=(2=>'0',others=>'1');--当a=10时,s(2)=0 elsif a="11"then s<=(3=>'0',others=>'1');--当a=11时,s(3)=0 else s<= (others=>'0');end if;end process;end behave;仿真结果a s(填灯亮和灭)a(1)a(2)LED2LED3LED4(pin68)LED5 00灭灭灭亮01灭灭亮灭10灭亮灭灭11亮灭灭灭引脚配置如表:端⼝引脚实验板上名称端⼝引脚实验板上名称端⼝引脚实验板上名称a(1)132up s(3)64LED2s(1)68LED4 a(0)131left s(2)67LED3s(0)69LED5实验总结:由于有了之前实验的操作基础,所以在做这个实验时遇到的阻⼒不⼤,⽐较顺利的完成了。

汉明码编译码器系统仿真设计..

课程设计报告题目:汉明码编译码器仿真设计学生姓名:学生学号:系别:专业:届别:指导教师:汉明码编译码器仿真设计1 课程设计任务汉明码是一种能够纠正一位错码或检测两位错码的一种效率较高的线性分组码。

本次课程设计的任务就是利用Systemview 软件实现(7,4)汉明码的编译码器的仿真设计。

进一步分析该系统的性能。

2 汉明码编译码原理的研究背景在通信编码方面,其发展的速度是非常快的,而且未来的发展空间还很巨大。

20世纪40年代才开始形成编码原理。

数字通信系统是利用数字信号来传递信息的通信系统数字通信系统设计的问题很多,其中编码是数字通信系统必不可少的模块。

编码包括信源编码和信道编码,信源编码有两个基本功能:一是提高传输系统的有效性,即通过某种数据压缩技术减少码元数目和降低码元速率。

码元速率决定传输所占的带宽,而传输带宽反应了信道的有效性。

二是完成数模转换。

信道编码的目的是增强数字信号的抗干扰能力。

信道编码对传输的信息码元按一定的规则加入保护成分,组成所谓抗干扰编码。

接收端的信道译码器按相应的逆规则进行解码从中发现错误或者纠正错误,提高通信系统的可靠性。

我们把建立在数学基础上的编码称为代数码。

在代数码中常见的是线性码。

在线性码中信息位和监督位是由一些线性代数方程联系着的,或者说线性码是按照一定的线性方程构成的。

汉明码是1950年由美国贝尔实验室提出来的,是第一个设计用来纠正错误的线性分组码,从20世纪50年代问世以来,在提高系统可靠性方面获得了广泛的应用。

最先用于磁芯存储器,60年代初用于大型计算机,70年代在MOS存储器中得到应用,后来在中小型计算机中普遍采用,随着科技的发展,现代编码理论和大规模集成电路的应用,性能优良的编译码方法不断出现而实现成本不断降低,其应用已不局限语音、图像等方面,现在更多的是扩展到计算机存储系统、磁盘,甚至在移动通信及卫星通信中得到应用,而且人们研究的不仅仅是纠正一位错码,而倾向于纠正多位错码。

毕业设计(论文)-在fpga上设计汉明码的编码器和解码器[管理资料]

![毕业设计(论文)-在fpga上设计汉明码的编码器和解码器[管理资料]](https://img.taocdn.com/s3/m/ef08c1f5cc175527062208e2.png)

南京大学金陵学院本科毕业论文院系信息科学与工程系专业电子信息科学与技术题目在FPGA上设计汉明码的编码器和解码器年级四学号学生姓名指导教师职称讲师论文提交日期2010年6月3 日摘要本文用Verilog语言实现了汉明码的编码和译码。

在介绍汉明码编码和译码原理的基础上,设计出了汉明码的编码器和译码器,写出了基于Verilog实现的源程序,并通过modelsim软件的仿真。

关键词:现场可编程门阵列;verilog;汉明码ABSTRACTThis passage realized code and decode of hamming with language of on the theory of introduction of code and decode of hamming,this passage designed coder and decoder of source program was written by verilog language.The soft of modelsim simulated and tested the program.Keywords:fpga; verilog; hamming目录序言 (1)第一章 Modelsim简介和仿真的基本步骤 (2)modelsim简介 (2)modelsim仿真的基本步骤 (2)第二章 Verilog的基础知识 (4)verilog的主要功能 (4)verilog基本语法 (4)wire型和reg型 (4)initial模块和always模块 (5)边沿和电平触发事件 (5)条件语句 (6)阻塞和非阻塞赋值 (6)组合逻辑电路 (7)时序逻辑电路 (7)第三章汉明码的编译码设计 (9)汉明码的原理 (9)基本概念 (9)监督矩阵 H (9)生成矩阵G (10)伴随式(校正子)S (10)汉明码的编码器设计 (11)编码器的设计流程图 (11)代码设计 (12)仿真波行及其分析 (14)汉明码解码器的设计 (14)解码器的设计流程图 (14)代码设计 (15)仿真波形及其分析 (16)汉明码的编码器和译码器的连接 (17)结束语 (19)致谢 (20)参考文献 (21)附录 (22)序言硬件语言(HDL)概述硬件描述语言(Hardware Description Language)是硬件设计人员和电子设计自动化(EDA)。

汉明码的编解码在fpga上的实现

南京大学金陵学院本科毕业论文院系信息科学与工程系专业电子信息科学与技术题目在FPGA上设计汉明码的编码器和解码器年级四学号**********学生姓名房伟指导教师姜乃卓职称讲师论文提交日期2010年6月3 日摘要本文用Verilog语言实现了汉明码的编码和译码。

在介绍汉明码编码和译码原理的基础上,设计出了汉明码的编码器和译码器,写出了基于Verilog实现的源程序,并通过modelsim软件的仿真。

关键词:现场可编程门阵列;verilog;汉明码ABSTRACTThis passage realized code and decode of hamming with language of verilog.Based on the theory of introduction of code and decode of hamming,this passage designed coder and decoder of hamming.The source program was written by verilog language. The soft of modelsim simulated and tested the program.Keywords:fpga; verilog; hamming目录序言 (1)第一章 Modelsim简介和仿真的基本步骤 (2)1.1 modelsim简介 (2)1.2 modelsim仿真的基本步骤 (2)第二章 Verilog的基础知识 (4)2.1 verilog的主要功能 (4)2.2 verilog基本语法 (4)2.2.1 wire型和reg型 (4)2.2.2 initial模块和always模块 (5)2.2.3 边沿和电平触发事件 (5)2.2.4 条件语句 (6)2.2.5 阻塞和非阻塞赋值 (6)2.2.6 组合逻辑电路 (7)2.2.7 时序逻辑电路 (7)第三章汉明码的编译码设计 (9)3.1 汉明码的原理 (9)3.1.1 基本概念 (9)3.1.2 监督矩阵 H (9)3.1.3 生成矩阵G (10)3.1.4 伴随式(校正子)S (10)3.2 汉明码的编码器设计 (11)3.2.1 编码器的设计流程图 (11)3.2.2 代码设计 (12)3.2.3 仿真波行及其分析 (14)3.3 汉明码解码器的设计 (14)3.3.1 解码器的设计流程图 (14)3.3.2 代码设计 (15)3.3.3 仿真波形及其分析 (16)3.4 汉明码的编码器和译码器的连接 (17)结束语 (18)致谢 (20)参考文献 (21)附录 (22)序言硬件语言(HDL)概述硬件描述语言(Hardware Description Language)是硬件设计人员和电子设计自动化(EDA)工具之间的界面.其主要目的是用来编写设计文件建立电子系统行为级的仿真模型。

循环汉明码编译器的设计与FPGA实现

循环汉明码编译器的设计与FPGA实现王书省;贺占权;张少甫;肖长春;曹旸【期刊名称】《现代电子技术》【年(卷),期】2014(000)010【摘要】分析了循环码的特性,提出一种循环汉明码编译码器的设计方案。

编译码器中编码采用除法电路,译码采用梅吉特译码器,易于工程应用。

对编译码器在FPGA上进行了实现,通过参数化设置,具有较高的码率,适用于(255,247)及其任意缩短码的循环汉明码,并给出了译码器的仿真和测试结果。

结果表明:编译码器运行速率高、译码时延小,在Virtex-5芯片上,最高工作时钟频率大于270 MHz。

在码组错误个数确定的系统应用中,可以有效降低误码率,一般可将误码率降低一个量级。

实践表明,该设计具有很强的工程实用价值。

%Based on characteristics analysis of cyclic codes,a design scheme of cyclic Hamming code encoder/decoder is proposed. In the encoder/decoder,a division circuit is adopted for encoding,and a Meggitt decoder is adopted for decoding, which are easy to be applied to engineering implementment. The encoder/decoder,which is suited for (255,247) and its cyclic Hamming code of arbitrarily-truncated codes,and has higher code rate,was implemented on FPGA by means of Verilog HDL. Some optimization techniques in the design process are given. The simulation and testing results of the encoder/decoder are of-fered in this paper. Theencoder/decoder can operate at high speed and has short decoding delay. Its max working clock frequen-cy is higher than 270 MHz in Virtex-5 chip.The encoder/decoder can be applied in digital communication systems that have defi-nite error number. Its BER can be reduced efficiently. The encoder/decoder has high practical value.【总页数】5页(P127-131)【作者】王书省;贺占权;张少甫;肖长春;曹旸【作者单位】航天恒星科技有限公司,北京 100086;航天恒星科技有限公司,北京 100086;航天恒星科技有限公司,北京 100086;航天恒星科技有限公司,北京100086;航天恒星科技有限公司,北京 100086【正文语种】中文【中图分类】TN914-34【相关文献】1.汉明码编译码的FPGA设计与实现 [J], 盛孟刚2.针对FPGA的IDL-Verilog编译器的设计与实现 [J], 吴湛;王玲;吴宇3.扩展汉明码的编解码器设计及其FPGA实现 [J], 王爱珍4.一种交织汉明码编译码器设计及其FPGA实现 [J], 庄灿;石和荣;齐永5.基于循环优化的可重构处理器任务编译器设计实现 [J], 栗念龙;唐世卓;何卫锋因版权原因,仅展示原文概要,查看原文内容请购买。

基于FPGA的汉明码译码器的设计

大连交通大学信息工程学院毕业设计 (论文) 题目基于FPGA的汉明码译码器的设计学生姓名芦斌专业班级信息工程09-2 指导教师徐佳职称讲师所在单位电气工程系信息工程教研室教研室主任石桂名完成日期 2013年 6 月 28 日摘要在数字通讯的系统中,数字信号在传输的过程中容易受到干扰,造成码元波形破坏,使得接收端接收到的信号发生错误的判决。

为了提高信息传输的准确性,我们引进了差错控制技术。

该项技术应采用了可靠而且有效的信道编码方法来实现。

汉明码就是一种可以纠正差错的编码。

汉明码编译码器是目前最为常用的数字通信内部器件之一,它被广泛地应用在网络传输、存储器校验纠错以及数据安全中。

本课题是基于FPGA的汉明码译码器的设计,使用Verilog语言来实现汉明码译码器的设计。

通过理解汉明码译码原理的基础上,设计出了汉明码的译码器,并且写出了译码源程序,还通过QuartusII软件实现仿真。

本次设计首先介绍了EDA的硬件描述语言Verilog和仿真调试软件QuartusII,然后介绍了FPGA的发展历程和产品特性,借此选出合适的FPGA的芯片,最后介绍了汉明码。

通过了解汉明码的理论知识来掌握汉明码的译码原理,然后经过理解和分析设计出实现汉明码译码的算法,并且使用Verilog语言在QuartusII软件里完成了基于FPGA的汉明码译码器的编程和仿真实现。

同时根据需要,选择了合适的FPGA的芯片和外围元器件,设计出外围硬件的原理图,将理论和实践结合起来。

关键词:汉明码译码器FPGA Verilog语言QuartusIIABSTRACTIn digital communication systems, digital signal during transmission is easy to be disturbed, resulting in destruction of the symbol waveform, so that the receiver receives the signal error occurred judgment. In order to improve the accuracy of information, we introduce error control techniques. The technology uses a reliable and effective method of channel coding to achieve. Hamming code is a kind of code which is able to correct errors. Hamming code codes is one kind of the most commonly used devices in digital communications, which is widely used in network transmission, memory parity error correction and data security.The design of Hamming code codec in this project, this passage realized decode of hamming with language of verilog. Based on the theory of introduction of decode of hamming, this passage designed decoder of hamming. The source program wad written by verilog language. The soft of QuartusII simulated and tested the program.It requires basic theoretical knowledge of hamming code, and learn how to use the simulation and debugging software QuartusII as well as the hardware description language Verilog, and understand the various features of Hamming codes to master the peinciple of coding and decoding, then to understand and analyze, design its algorithm implementation, and complete the Verilog language programming and simulation on FPGA-based software QuartusII; in the meantime, according to its requirement, select a FPGA chip and external components, finally create the hardware entity, combine the theory with practice.Key words: Hamming Decoder FPGA Verilog language QuartusII目录1 前言 (1)1.1 选题背景 (1)1.2 本课题的研究意义 (2)1.3 本课题研究目标及主要任务 (2)1.4 本课题可行性分析 (3)2 EDA的基础知识与集成运行环境 (4)2.1 EDA概念 (4)2.2 QuartusⅡ的软件介绍 (5)2.3 Verilog的简介 (8)2.3.1 Verilog的主要功能 (10)2.3.2 Verilog的基础语法 (10)2.3.3 Verilog的语言优势 (13)3 FPGA的简介 (14)3.1 FPGA的发展历程 (14)3.2 FPGA的产品特性及发展现状 (14)3.3 FPGA的发展趋势 (15)3.4 FPGA的硬件介绍 (17)4 汉明码译码系统模块设计与实现 (19)4.1 汉明码的原理 (19)4.1.1 汉明码的定义 (19)4.1.2 汉明码的监督矩阵H (21)4.1.3 汉明码的生成矩阵G (22)4.1.4 汉明码的校正子(伴随式)S (22)4.2 汉明码的译码器设计 (24)4.2.1 译码器的流程图设计 (25)4.2.2 译码器的代码设计 (25)4.2.3 译码器的仿真,调试与分析 (27)4.3 基于FPGA的汉明码译码器硬件设计 (30)结论 (32)谢辞 (33)参考文献 (34)附录 (35)1 前言1.1 选题的背景随着现代通信技术的迅速发展,其应用的领域已渗入到社会生活的各个方面,用户对通信系统的质量和对通信系统数据传输的可靠性与有效性的要求也越来越高,通信系统需要具备更高的可靠性、高效率、低复杂性来适应发展的需求[4]。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

大连交通大学信息工程学院毕业设计 (论文) 题目基于FPGA的汉明码译码器的设计学生姓名芦斌专业班级信息工程09-2 指导教师徐佳职称讲师所在单位电气工程系信息工程教研室教研室主任石桂名完成日期 2013年 6 月 28 日摘要在数字通讯的系统中,数字信号在传输的过程中容易受到干扰,造成码元波形破坏,使得接收端接收到的信号发生错误的判决。

为了提高信息传输的准确性,我们引进了差错控制技术。

该项技术应采用了可靠而且有效的信道编码方法来实现。

汉明码就是一种可以纠正差错的编码。

汉明码编译码器是目前最为常用的数字通信内部器件之一,它被广泛地应用在网络传输、存储器校验纠错以及数据安全中。

本课题是基于FPGA的汉明码译码器的设计,使用Verilog语言来实现汉明码译码器的设计。

通过理解汉明码译码原理的基础上,设计出了汉明码的译码器,并且写出了译码源程序,还通过QuartusII软件实现仿真。

本次设计首先介绍了EDA的硬件描述语言Verilog和仿真调试软件QuartusII,然后介绍了FPGA的发展历程和产品特性,借此选出合适的FPGA的芯片,最后介绍了汉明码。

通过了解汉明码的理论知识来掌握汉明码的译码原理,然后经过理解和分析设计出实现汉明码译码的算法,并且使用Verilog语言在QuartusII软件里完成了基于FPGA的汉明码译码器的编程和仿真实现。

同时根据需要,选择了合适的FPGA的芯片和外围元器件,设计出外围硬件的原理图,将理论和实践结合起来。

关键词:汉明码译码器FPGA Verilog语言QuartusIIABSTRACTIn digital communication systems, digital signal during transmission is easy to be disturbed, resulting in destruction of the symbol waveform, so that the receiver receives the signal error occurred judgment. In order to improve the accuracy of information, we introduce error control techniques. The technology uses a reliable and effective method of channel coding to achieve. Hamming code is a kind of code which is able to correct errors. Hamming code codes is one kind of the most commonly used devices in digital communications, which is widely used in network transmission, memory parity error correction and data security.The design of Hamming code codec in this project, this passage realized decode of hamming with language of verilog. Based on the theory of introduction of decode of hamming, this passage designed decoder of hamming. The source program wad written by verilog language. The soft of QuartusII simulated and tested the program.It requires basic theoretical knowledge of hamming code, and learn how to use the simulation and debugging software QuartusII as well as the hardware description language Verilog, and understand the various features of Hamming codes to master the peinciple of coding and decoding, then to understand and analyze, design its algorithm implementation, and complete the Verilog language programming and simulation on FPGA-based software QuartusII; in the meantime, according to its requirement, select a FPGA chip and external components, finally create the hardware entity, combine the theory with practice.Key words: Hamming Decoder FPGA Verilog language QuartusII目录1 前言 (1)1.1 选题背景 (1)1.2 本课题的研究意义 (2)1.3 本课题研究目标及主要任务 (2)1.4 本课题可行性分析 (3)2 EDA的基础知识与集成运行环境 (4)2.1 EDA概念 (4)2.2 QuartusⅡ的软件介绍 (5)2.3 Verilog的简介 (8)2.3.1 Verilog的主要功能 (10)2.3.2 Verilog的基础语法 (10)2.3.3 Verilog的语言优势 (13)3 FPGA的简介 (14)3.1 FPGA的发展历程 (14)3.2 FPGA的产品特性及发展现状 (14)3.3 FPGA的发展趋势 (15)3.4 FPGA的硬件介绍 (17)4 汉明码译码系统模块设计与实现 (19)4.1 汉明码的原理 (19)4.1.1 汉明码的定义 (19)4.1.2 汉明码的监督矩阵H (21)4.1.3 汉明码的生成矩阵G (22)4.1.4 汉明码的校正子(伴随式)S (22)4.2 汉明码的译码器设计 (24)4.2.1 译码器的流程图设计 (25)4.2.2 译码器的代码设计 (25)4.2.3 译码器的仿真,调试与分析 (27)4.3 基于FPGA的汉明码译码器硬件设计 (30)结论 (32)谢辞 (33)参考文献 (34)附录 (35)1 前言1.1 选题的背景随着现代通信技术的迅速发展,其应用的领域已渗入到社会生活的各个方面,用户对通信系统的质量和对通信系统数据传输的可靠性与有效性的要求也越来越高,通信系统需要具备更高的可靠性、高效率、低复杂性来适应发展的需求[4]。

通信的根本任务是传递信息,其中准确地传输数字信号是数字通信的一个重要的环节。

在实际应用中,传输数据的无线信道是非常复杂的。

在传输数字信号时,由于信道的时变性、衰减性、带宽资源有限性以及干扰大等特点,再有加性噪声的影响,这就导致接收端接收到的信息和发送端实际发送的信息之间存在一定的差错,势必会造成接收端接收到的信号存在一定的误差,造成一定程度的失真。

这时就需求我们去寻找一种办法,能够在确保通信系统的可靠性与高效性的基础上来减少数据传输过程中的误比特率。

信道编码就是减少数字信号误比特率的主要手段之一。

图1-1 通讯系统的组成在实际的应用中,衡量一个通信系统的优劣,其中的有效性和可靠性是两个最重要的指标,同时它们也是通信技术设计的重要组成部分。

然而,从信息传输角度来考虑,既要提高通信系统的有效性(即传输速率),又要提高通信系统的可靠性,这样往往是相互矛盾的。

为了提高可靠性,可以在二进制信息序列中以受控的方式引入一些冗余码元(即监督码元),使他们满足一定的约束关系,以期达到检错和纠错的目的。

但是,由于添加了冗余码元(监督码元),导致传输信息的速率下降;同时,为了提高效率,信号以简洁、快速的方式传输,这样在遭受到干扰和噪声时,其自我保护能力大大下降,从而降低了传输的可靠性。

于是,在实际通信的应用中,采取比较折中的方式,可在确保可靠性指标达到系统要求的前提下,尽可能的提高传输速率[1];抑或在满足一定有效性的指标下,尽量提高传输的可靠性。

通信技术设计一直致力于提高信息传输的有效性和可靠性,其中保证通信的可靠性是现代数字通信系统需要解决的首要问题。

信道编码技术正是用来改善通信可靠性问题的主要技术手段之一。

在实际应用中,一个通信系统一般包含信道编码和信道译码两个模块[2]。

信道编码的主要目的是为了降低误比特率,提高数字通信的可靠性,其方法是在二进制信息序列中添加一些冗余码元(监督码元),与信息码元一起组成被传输的码字。

这些冗余码元是以受控的方式引入,它们与信息码元之间有着相互制约的关系。

在信道中传输该码字,如果错误了发生,信息码元和冗余码元之间相互制约的关系就将会被破坏[1]。

那么,在接收端对接收到的信息序列按照既定的规则校验码字各码元间的约束关系,从而达到检错、纠错的目的。

通过信道编码这种方法,能够有效的在接收端克服信号在无线信道中传输时受到噪声和干扰产生的影响。

信道译码也就是信道编码的逆过程,即接收端将接收信息序列按照既定约束关系,同时去掉比特流在传播的过程中混入的噪声干扰和添加的冗余,恢复为比较完整、可靠的信息的过程。

信道编码涉及到的内容也十分广泛,前身纠错编码(FEC)、线性分组码(汉明码、循环码)、理德-所罗门码(RS码)、FIRE码、交织码、卷积码、TCM编码、Turbo码等都是信道编码的研究范畴[11]。

汉明码是信道编码比较好的选择。

汉明码是汉明于1950年提出的,是具有纠正一位错误能力的线性分组码。

汉明码是在原编码的基础上附加一部分代码,使其能满足纠错码的条件[6]。

它的突出特点是:编译码电路简单,易于硬件的实现;用软件实现编译码算法时,软件的效率高;而且性能也比较好。

由于汉明码的抗干扰能力较强,至今仍是应用比较广泛的一类码。

1.2 本课题的研究意义本次课程设计的任务就是基于FPGA,利用EDA的技术在Quartus II软件下用Verilog语言来实现汉明码译码器的设计和仿真。

汉明码是一个在原有数据中插入若干校验码来进行错误检查和纠正的编码技术,在原编码的基础上附加了一部分代码,使其满足纠错码的条件。