移位相加位硬件乘法器电路设计

基于时序电路的移位相加型8位硬件乘法器设计

基于时序电路的移位相加型8位硬件乘法器设计硬件乘法器是计算机中十分重要的一个组成部分,其作用是实现两个二进制数的乘法运算。

在硬件乘法器中,采取“移位相加”的方式进行计算,这种方式就是将一个数乘以另一个数时,将其中一个数的每一位与另一个数相乘,然后相加得到最终结果。

基于此,本文将围绕“基于时序电路的移位相加型8位硬件乘法器设计”进行详细阐述。

第一步,进行原理分析。

在8位硬件乘法器中,两个二进制数各占8位,分别是A、B。

在移位相加的计算方式中,B中的每一位都与A 中相应的位相乘,然后将所得到的结果进行相加即可。

第二步,进行电路设计。

在设计时,需要采用时序电路进行控制,即将所有需要的操作按照一定的步骤进行排列,并确保每一步操作的正确性。

具体来说,需要设计如下模块:1. 寄存器模块:用于存储A、B两个数以及计算时需要用到的中间结果。

将A、B送入寄存器中后,通过移位操作,将B中的各个二进制位与A中对应的位进行相乘,然后得到中间结果。

2. 加法器模块:用于将中间结果进行相加,并将最终结果存储在寄存器中。

3. 控制器模块:用于控制寄存器和加法器的操作顺序,确保计算的正确性。

第三步,进行仿真测试。

在设计完成后,需要进行仿真测试,以确保电路的正确性和稳定性。

在测试时,可以利用Verilog HDL进行仿真,对各个模块进行单独测试,并最终汇总验证。

第四步,进行综合与分析。

在仿真测试完成后,需要进行综合分析。

综合分析的目的是将Verilog代码转化为门电路级别的实现,以便进行电路布局和物理设计。

在综合分析中,需要考虑电路的功耗、时序、面积等因素,以确保电路的可行性和优化性。

总之,基于时序电路的移位相加型8位硬件乘法器设计,是一项复杂且关键的工作。

只有通过对原理的深入了解和对电路的细致设计,才能最终得到稳定、可靠的硬件乘法器。

移位相加8位乘法器的设计

EDA技术课程大作业设计题目:移位相加8位乘法器的设计院系:电子信息与电气工程学院学生姓名:学号:200902070017专业班级:09电子信息工程专升本2010年12月3日移位相加8位乘法器的设计1.设计背景和设计方案1.1设计背景EDA技术(即Electronic Design Automation技术)就是依赖强大的计算机,在EDA工具软件平台上,对以硬件描述语言HDL(Hardware Ddscription Langurage)为系统逻辑描述手段完成的设计文件,自动地完成逻辑编译、化简、分割、综合、布局布线以及逻辑优化和仿真测试,直至实现既定的电子线路系统功能。

它在硬件实现方面融合了大规模集成电路制造技术、IC版图设计、ASIC 测试和封装、FPGA(Gield Peogrammable Gate Array)/CPLD(Complex Programmable Logic Device)编程下载和自动测试等技术;在计算机辅助工程方面融合了计算机辅助设计(CAD),计算机辅助制造(CAM),计算机辅助测试(CAT),计算机辅助工程(CAE)技术以及多种计算机语言的设计概念;而在现代电子学方面则容纳了更多的内容,如电子线路设计理论、数字信号处理技术、数字系统建模和优化技术及长线技术理论等。

本文介绍设计一个两个5位数相乘的乘法器。

用发光二极管显示输入数值,用7段显示器显示十进制结果。

乘数和被乘数分两次输入。

在输入乘数和被乘数时,要求显示十进制输入数据。

输入显示和计算结果显示,采用分时显示方式进行,可参见计算器的显示功能1.2设计方案此设计是由八位加法器构成的以时序逻辑方式设计的八位乘法器,它的核心器件是八位加法器,所以关键是设计好八位加法器。

方案一:八位直接宽位加法器,它的速度较快,但十分耗费硬件资源,对于工业化设计是不合理的。

方案二:由两个四位加法器组合八位加法器,其中四位加法器是四位二进制并行加法器,它的原理简单,资源利用率和进位速度方面都比较好。

移位相加硬件乘法器设计

实验报告

一、实验目的

通过设计8位乘法器,进一步掌握VHDL语言的设计P182 二、实验内容

设计移位相加硬件乘法器

三、实验环境

计算机、QuartusII软件

四、实验步骤

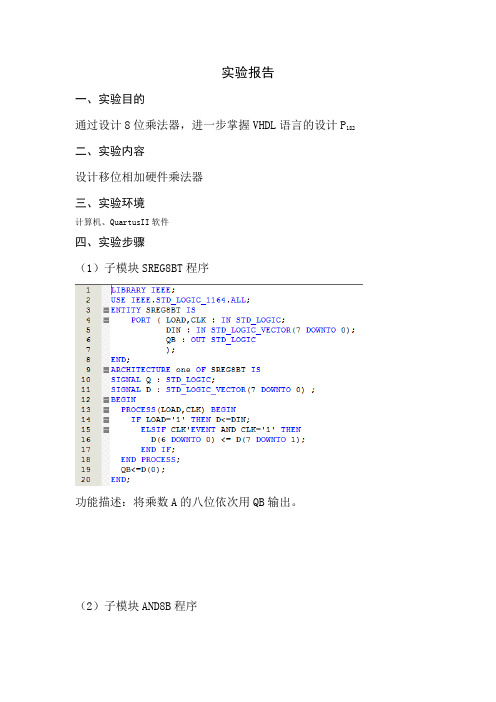

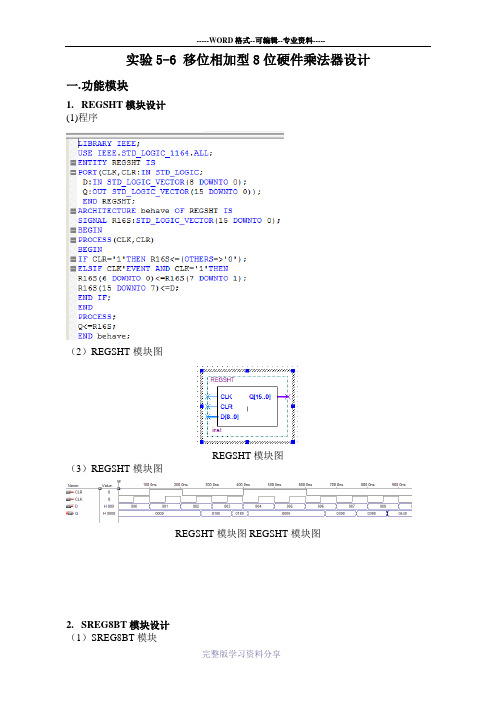

(1)子模块SREG8BT程序

功能描述:将乘数A的八位依次用QB输出。

(2)子模块AND8B程序

功能描述:如果子模块(1)输出的一位乘数是‘1’,即ABIN=‘1’时,输出DOUT为被乘数B,否则输出0.

(3)子模块ADDER8BT程序

(4)子模块REGSHT程序

(5)综合电路:

仿真结果:

五、实验结果与讨论

子模块SEG8BT的功能是依次由QB输出乘数的每一位;子模块AND8B 的功能是判断由QB输出的是‘1’还是‘0’,如果是‘1’则DOUT输出被乘数,否则输出0;子模块ADDER8BT的功能则是带有进位信号S 【8】的全加器;子模块RGSHT的功能是进行移位,锁存。

六、总结

综合电路实现了8位移位相加乘法器的功能;之前自己写了一个只有一个模块的8位乘法器,但实现不了。

代码如下。

EDA乘法器实验报告

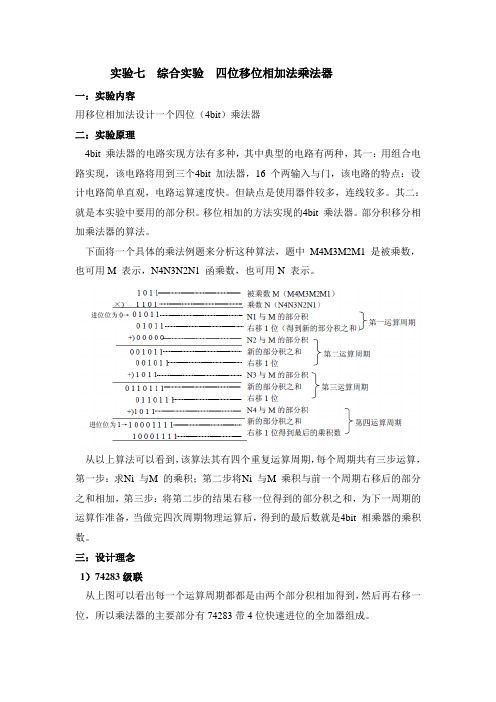

实验七综合实验四位移位相加法乘法器一:实验内容用移位相加法设计一个四位(4bit)乘法器二:实验原理4bit 乘法器的电路实现方法有多种,其中典型的电路有两种,其一:用组合电路实现,该电路将用到三个4bit 加法器,16 个两输入与门,该电路的特点:设计电路简单直观,电路运算速度快。

但缺点是使用器件较多,连线较多。

其二:就是本实验中要用的部分积。

移位相加的方法实现的4bit 乘法器。

部分积移分相加乘法器的算法。

下面将一个具体的乘法例题来分析这种算法,题中M4M3M2M1 是被乘数,也可用M 表示,N4N3N2N1 函乘数,也可用N 表示。

从以上算法可以看到,该算法其有四个重复运算周期,每个周期共有三步运算,第一步:求Ni 与M 的乘积;第二步将Ni 与M 乘积与前一个周期右移后的部分之和相加,第三步:将第二步的结果右移一位得到的部分积之和,为下一周期的运算作准备,当做完四次周期物理运算后,得到的最后数就是4bit 相乘器的乘积数。

三:设计理念1)74283级联从上图可以看出每一个运算周期都都是由两个部分积相加得到,然后再右移一位,所以乘法器的主要部分有74283带4位快速进位的全加器组成。

将乘法器打包成如下形式波形图:在时钟的每一个上升沿的时候,乘法器进行运算。

2)将二进制转换为10进制但是由于要在七段LED数码管中显示,所以原始的输出形式不能满足,因为上边的器件输出的是二进制,所以要将输入的乘数被乘数和结果转化为10进制,最大四位二进制即十进制的15,将被乘数A【3..0】和乘数B【3..0】除以10,余数即为个位,同理输出的结果最大为225,连续两次除以10,分别得到个位,十位的数,这样就将二进制的乘数,被乘数和结果转化为了10进制的数,从而方便了数码管的显示。

如图:rl rm rn个位,q4 q5 rh十位,q2百位。

3)选择器下面是将输出结果用7449译码器译码到数码管中,但是一个译码器不能同时译码(最多7个)数据,所以要用时钟信号以及多选器。

移位相加8位硬件乘法器电路电子课程设计

移位相加8位硬件乘法器电路电子课程设计电子课程设计---移位相加8位硬件乘法器电路设计学院:电子信息工程学院班级: 通信071501姓名:许瀛指导老师:高文华2009年12月目录一.设计任务与要求 (2)二.总体框图 (3)三.选择器件 (4)四.功能模块 (5)五.总体设计电路图………………………………………………………………15六.心得体会 (17)移位相加8位硬件乘法起一、设计任务与要求设计一个乘法器的控制模块,接受实验系统上的连续脉冲,当给定启动/清零信号后,能自动发出CLK信号驱动乘法运算,当8个脉冲后自动停止。

设计一个纯组合电路的8X8等于16位的乘法器(选择不同的流水线方式),具体说明并比较这几种乘法器的逻辑资源占用情况和运行速度情况。

二、总体框图控制16位锁存器/分段8位右移1位乘8位加7段数码1、模块功能A、运算控制模块:控制电路的起始和终止。

B、8位右移寄存器:在时钟脉冲的作用下,高位寄存器的数码送给低位寄存器,作为低位寄存器的次态输出;每输入一个时钟脉冲,寄存器的数据就顺序向右移动一位。

C、1位乘法器:D、8位加法器:E、16位锁存器/右移寄存器:此设计是由八位加法器构成的以时序逻辑方式设计的八位乘法器,它的核心器件是八位加法器,所以关键是设计好八位加法器。

方案:由两个四位加法器组合八位加法器,其中四位加法器是四位二进制并行加法器,它的原理简单,资源利用率和进位速度方面都比较好。

综合各方面的考虑,决定采用方案二。

2、设计思路:纯组合逻辑构成的乘法器虽然工作速度比较快,但过于占用硬件资源,难以实现宽位乘法器,由八位加法器构成的以时序逻辑方式设计的八位乘法器,具有一定的实用价值,而且由FPGA 构成实验系统后,可以很容易的用ASIC大型集成芯片来完成,性价比高,可操作性强。

其乘法原理是:乘法通过逐项移位相加原理来实现,从被乘数的最低位开始,若为1,则乘数左移后与上一次的和相加;若为0,左移后以全零相加,直至被乘数的最高位。

使用乘法器实现各种移位操作

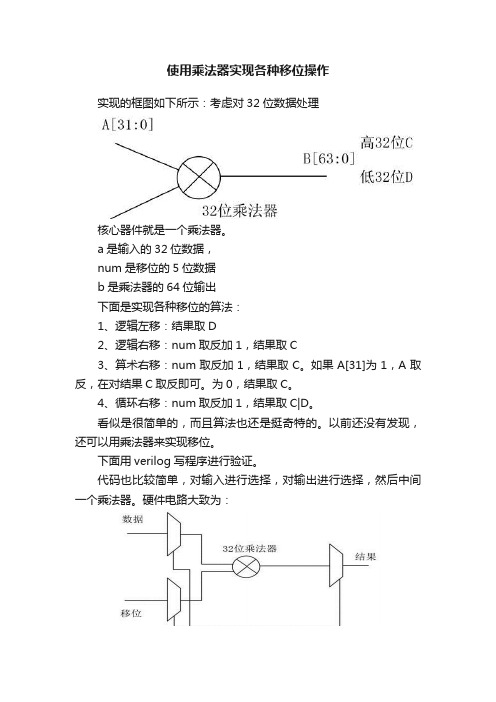

使用乘法器实现各种移位操作实现的框图如下所示:考虑对32位数据处理核心器件就是一个乘法器。

a是输入的32位数据,num是移位的5位数据b是乘法器的64位输出下面是实现各种移位的算法:1、逻辑左移:结果取D2、逻辑右移:num取反加1,结果取C3、算术右移:num取反加1,结果取C。

如果A[31]为1,A取反,在对结果C取反即可。

为0,结果取C。

4、循环右移:num取反加1,结果取C|D。

看似是很简单的,而且算法也还是挺奇特的。

以前还没有发现,还可以用乘法器来实现移位。

下面用verilog写程序进行验证。

代码也比较简单,对输入进行选择,对输出进行选择,然后中间一个乘法器。

硬件电路大致为:有了这个图,写代码就更容易了。

module shitf_according_mul( input [31:0] a, input [4:0] num, input [1:0] shift_mode, output reg[31:0] out ); localparam logic_left_shift = 2'b00; localparam logic_right_shift = 2'b01; localparam cycle_right_shift = 2'b10; localparam airth_right_shift = 2'b11; //data reg [31:0] reg_a; always@(*) begin case(shift_mode) logic_left_shift: reg_a = a; logic_right_shift: reg_a = a; cycle_right_shift: reg_a = a; airth_right_shift: reg_a = a[31] ? ~a:a; endcase end//shift number reg [31:0] reg_num; always@* begin case(shift_mode) logic_left_shift: reg_num = 32'b1(~num>(~num>(~num>纯组合逻辑设计,设计好了,需要写testbench验证吧。

基于FPGA的8位移位相加型硬件乘法器的设计

基于FPGA的8位移位相加型硬件乘法器的设计作者:张建妮来源:《智能计算机与应用》2014年第04期摘要:乘法器是数字信号处理中非常重要的模块。

本文首先介绍了硬件乘法器的原理,在此基础上提出了硬件乘法器的设计方法,最后再利用EDA技术,在FPGA开发平台上,通过VHDL编程和图形输入对其进行了实现,具有实用性强、性价比高、可操作性强等优点。

关键词:硬件乘法器;加法器; VHDL中图分类号:TP2 文献标识码:A文章编号:2095-2163(2014)04-0087-04Abstract:Multiplier is very important in digital signal processing module. In this paper, the principle of the hardware multiplier is introduced at first. Based on it, a design method is put forward.Finally , using EDA technology,the hardware -multiplier is implemented through VHDL programming combining with the input mode of schematic diagram on the FPGA development platform. The design has strong practicability ,high cost-effective, strong operability, etc.Key words:Hardware-Multiplier; Adder; VHDL0引言在数字信号处理中,经常会遇到卷积、数字滤波、FFT等运算,而在这些运算中则存在大量类似ΣA(k)B(n-k)的算法过程。

因此,乘法器是数字信号处理中必不可少的一个模块。

移位相加型8位硬件乘法器设计

实验5-6 移位相加型8位硬件乘法器设计一.功能模块1.REGSHT模块设计(1)程序(2)REGSHT模块图REGSHT模块图(3)REGSHT模块图REGSHT模块图REGSHT模块图2.SREG8BT模块设计(1)SREG8BT模块(2)SREG8BT模块SREG8BT模块(3)SREG8BT模块仿真波形SREG8BT模块仿真波形3.AND8B模块设计(1)AND8B模块(2)AND8B模块AND8B模块(3)AND8B模块仿真波形AND8B模块仿真波形4.ADDER8BT模块设计(1)ADDER8BT模块程序(2)ADDER8BT模块ADDER8BT模块(3)ADDER8BT模块仿真波形ADDER8BT模块仿真波形二.8位乘法器逻辑原理图三.8位移位相加乘法器运算逻辑波形图8位移位相加乘法器运算逻辑波形图四.实验总结通过这次设计,进一步加深了对EDA的了解,让我对它有了更加浓厚的兴趣。

特别是当每一个子模块编写调试成功时,心里特别的开心。

但是在编写顶层文件的程序时,遇到了不少问题,特别是各元件之间的连接,以及信号的定义,总是有错误,在细心的检查下,终于找出了错误和警告,排除困难后,程序编译就通过了,心里终于舒了一口气。

器件的选择也很重要,只有选择合适的器件,才能正确的编译,从而能更好的做好本次试验!通过这次课程设计使我懂得了理论与实际相结合是很重要的,只有理论知识是远远不够的,只有把所学的理论知识与实践相结合起来,从理论中得出结论,从而提高自己的实际动手能力和独立思考的能力。

在设计的过程中遇到问题,可以说得是困难重重,难免会遇到过各种各样的问题,同时在设计的过程中发现了自己的不足之处,对以前所学过的知识理解得不够深刻,掌握得不够牢固。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

电子技术课程设计----移位相加8位硬件乘法器电路计学院: 华科学院专业: 通信工程班级:通信052201H姓名: 张茹学号:2指导教师:柴婷婷2007年12月30日一,设计任务与要求--------------------(3)1,内容2,要求二,总体框图---------------------------(3)1,电路的总体框图2,框图的说明3,设计思路4,方案设计三,选择器件与功能模块-----------------(5)1,选择器件各功能模块及功能说明四,功能模块----------------------------(8)1,ADDER8B的模块2,ANDARITH的模块3,ARICTL的模块4,REG16B的模块5,SREG8B的模块五,总体设计电路图----------------------(14)1,总体原理图2,仿真波形图3,管脚分配图4,硬件验证情况六,心得体会--------------------------------------(18)移位相加8位硬件乘法器一.设计任务与要求1.内容: 由8位加法器构成的以时序逻辑方式设计的8位乘法器乘法通过逐向移位加原理来实现,从被乘数的最低位开始,若为1,则乘数左移与上一次和相加;若为0,左移后以全零相加,直至被乘数的最高位。

2.要求: (1) 重点掌握VHDL设计电路模块(2)在掌握8位加法器设计的基础上,进一步掌握8×8位乘法器的设计;(3)进一步学习开发系统,掌握MAX+PLUS II的设计流程。

二.总体框图(电路的总体框图)1,说明:此电路由五部分组成2,它们分别是控制器,锁存器,寄存器,乘法器,加法器。

1控制器是一个乘法器的控制模块,用来接受实验系统上的连续脉冲。

2锁存器起锁存的作用,它可以锁存8位乘数。

3移位寄存器起移位的作用,便于被乘数可以逐位移出。

4乘法器功能类似一个特殊的与非门。

5加法器用于8位乘数和高8位相加。

2,设计思路:纯组合逻辑构成的乘法器虽然工作速度比较快,但过于占用硬件资源,难以实现宽位乘法器,基于PLD器件外接ROM九九表的乘法器则无法构成单片系统,也不实用。

这里介绍由八位加法器构成的以时序逻辑方式设计的八位乘法器,具有一定的实用价值,而且由FPGA构成实验系统后,可以很容易的用ASIC大型集成芯片来完成,性价比高,可操作性强。

其乘法原理是:乘法通过逐项移位相加原理来实现,从被乘数的最低位开始,若为1,则乘数左移后与上一次的和相加;若为0,左移后以全零相加,直至被乘数的最高位。

3,方案设计:此设计是由八位加法器构成的以时序逻辑方式设计的八位乘法器,它的核心器件是八加法器,所以关键是设计好八位加法器方案一:八位直接宽位加法器,它的速度较快,但十分耗费硬件资源,对于工业化设计是不合理的方案二:由两个四位加法器组合八位加法器,其中四位加法器是四位二进制并行加法器它的原理简单,资源利用率和进位速度方面都比较好。

综合各方面的考虑,决定采用方案二。

2 三,选择器件与功能模块1,选择器件SREG8B(移位寄存器);REG16B(16位琐存器);ARICTL(运算控制器);ANDARITH(1位乘法器);ADDER8B(8位加法器);数码管(显示结果)。

(1)SREG8B的模块图SREG8B是一个移位寄存器,SREG8B有三个输入端,分别是clk,load,din[7..0]。

其中clk为时钟信号。

一个输出端,它是qb。

(2)REG16B的模块图REG16B是一个16位锁存器,REG16B有三个输入端,它们分别是clk,clr,d[8..0].其中clk为时钟信号。

有一个输出端,它是q[15..0].(3)ARICTL的模块图ARICTL是乘法器的控制模块,ARICTL有两个输入端,它们分别是clk,start。

有三个输入端,它们分别是clkout,rstall,ariend。

(4)ANDARITH的模块图ANDARITH是一个一位乘法器,ANDARITH有两个输入端。

它们分别是abin,din[7..0]。

有一个输出端,它是dout[7..0]。

(5)ADDER8B的模块图ADDER8B是一个8位加法器,ADDER8B有三个输入端,它们分别是cin,a[7..0],b[7..0]。

其中a[7..0]为被乘数;b[7..0]为乘数。

有两个输出端,它们分别是s[7..0],cout。

四,功能模块(1)ADDER8B模块设计ADDER8B的模块图ADDER8B(8位加法器)的模块ADDER8B的波形图ADDER8B模块的功能:ADDER8B是一个8位加法器。

有三个输入端(CIN,A[7..0],B[7..0]),其中A[7..0]是被乘数.B[7..0]是乘数。

ADDER8B起到使两个数相加的作用;即在加法的基础上才能相乘。

所以8位加法器是一个必不可少的模块。

(2) ANDARITH模块设计ANDARITH的模块图ANDARITH(乘法器)的模块ANDARITH的波形图ANDARITH模块的功能:ANDARITH是一个1位乘法器。

有两个输入端(ABIN,DIN[7.0]).有一个输出端.DOUT[7..0]。

ANDARITH起乘法的作用。

它类似于一个特殊的与门。

即当ABIN为‘1’时,DOUT直接输出DIN,而当ABIN为‘0’时,DOUT输出“”。

(3)ARICTL模块设计ARICTL的模块图ARICTL(控制器)的模块ARICTL的波形图ARICTL模块的功能:ARICTL是一个乘法器的控制模块。

为了接受实验系统上的连续脉冲。

有两个输入端(CLK,START);其中START信号的上跳沿及其高电平有两个功能,即16位寄存器清零和被乘数A[7..0]向移位寄存器SREG8B加载;它的低电平则作为乘法使能信号。

CLK为乘法时钟信号。

有三个输出(CLKOUT,RSTALL,ARIEND)。

(4)REG16B模块设计REG16B的模块REG16B(锁存器)的模块REG16B的波形图REG16B模块的功能:REG16B是一个16位锁存器。

有三个输入端(CLK,CLR,D[8..0]);其中CLK为时钟信号。

有一个输出端(Q[15..0])。

16位锁存器主要为了锁存一些数,便于以后程序应用。

(5)SREG8B模块设计SREG8B的模块图SREG8B(移位寄存器)的模块图SREG8B的波形图SREG8B模块的功能:SREG8B是一个移位寄存器。

有三个输入端(CLK,LOAD,DIN[7..0]);当被乘数被加载于8位右移寄存器后,随着每一时钟节拍,最低位在前,由低位至高位逐位移出。

有一个输出端(QB)。

五.总体设计电路图说明原理图:本乘法器由五个模块组成,其中ARICTL是乘法运算控制电路,它的START信号上的上跳沿与高电平有2个功能,即16位寄存器清零和被乘数A[7...0]]向移位寄存器SREG8B加载;它的低电平则作为乘法使能信号,乘法时钟信号从ARICTL的CLK输入。

当被乘数被加载于8位右移寄存器SREG8B后,随着每一时钟节拍,最低位在前,由低位至高位逐位移出。

当为1时,一位乘法器ANDARITH打开,8位乘数B[7..0]在同一节拍进入8位加法器,与上一次锁存在16位锁存器REG16B中的高8位进行相加,其和在下一时钟节拍的上升沿被锁进此锁存器。

而当被乘数的移出位为0时,一位乘法器全零输出。

如此往复,直至8个时钟脉冲后,由ARICTL的控制,乘法运算过程自动中止,ARIEND输出高电平,乘法结束。

此时REG16B的输出即为最后的乘积。

2.时序仿真结果(以下是8位乘法器顶层设计的仿真波形图)从上面的波形图看出,当9FH和FDH相乘时,第一个时钟上升沿后,其移位相加的结果(在REG16B端口)是4F80H,第8个上升沿后,最终相乘结果是9D23H。

3.管脚分配图4,实验下载验证情况由于我们实验室采用GW48系列EDA系统平台,根据GW48系统和乘法器原理,定义管脚是:ARIEND接PIO39(D8),乘法运算时钟CLK接Clock0,清零及启动运算信号START由键8(PIO38)控制,乘数B[7..0]接PIO58-PIO66(由键2,键1输入8位二进制数),被乘数A[7..0]接PIO47-PIO54(由键4,键3输入8位二进制数),乘积输出DOUT[15..0] 接PIO31-PIO16。

编译,综合后向目标苡片下载适配后的逻辑设计文件。

下载适配后,键8输入高电平时,乘积锁存器清零,乘数和被乘数值加载;低电平时开始乘法操作,8个脉冲后乘法结束,乘积显示在数码管8~5位,高位在左。

例如:我们在乘数和被乘数都输入08H,键8输入低电平,8个脉冲后在高四个数码管显示0040H,实验证明成功。

心得体会通过三周的电子设计的数字部分EDA设计,我们掌握了系统的数字电子设计的方法,也知道了实验调试适配的具体操作方法。

在设计过程中,我们遇到了各种问题,在老师的指导下和我们自己的努力,克服了各种问题,最后得到了成功。

但是我也发现了一些问题,我们无法解决。

如:在ARICTL控制器模块中有一个警告,还有在适配后得到频率高的执行速度还要慢一些等等。

总之,这次设计使我掌握了很多有用的经验也学到了很多在书本上学不到知识,为以后的学习和工作打下坚实的基础通过这次设计,进一步加深了对EDA的了解,让我对它有了更加浓厚的兴趣。

特别是当每一个子模块编写调试成功时,心里特别的开心。

但是在编写顶层文件的程序时,遇到了不少问题,特别是各元件之间的连接,以及信号的定义,总是有错误,在细心的检查下,终于找出了错误和警告,排除困难后,程序编译就通过了,心里终于舒了一口气。

器件的选择也很重要,只有选择合适的器件,才能正确的编译,从而能更好的做好本次试验!通过这次课程设计使我懂得了理论与实际相结合是很重要的,只有理论知识是远远不够的,只有把所学的理论知识与实践相结合起来,从理论中得出结论,才能真正为社会服务,从而提高自己的实际动手能力和独立思考的能力。

在设计的过程中遇到问题,可以说得是困难重重,难免会遇到过各种各样的问题,同时在设计的过程中发现了自己的不足之处,对以前所学过的知识理解得不够深刻,掌握得不够牢固。

最后,对给过我帮助的所有同学和各位指导老师再次表示忠心的感谢!。