微电子工艺流程(PDF 44页)

第二章-电子封装的基本工艺-PDF全

点面积大,无方向性,可自动化焊接。

三种引线键合的焊接拉力比较

热压焊:<0.05N/点 超声焊:>0.1N/点(Al丝, 40µm) 热超声焊:0.07-0.09N/点(Au丝, 25µm)

引线键合可能产生的失效

脱焊(lift-off):原因是焊盘上存在有机沾污或是 表面氧化层太厚 疲劳断裂(fatigue break):原因是生成金属间化 合物,使接触电阻增大。金属间化合物形成的同 时,在焊接点产生空洞,在热冲击、温度循环过 程中,空洞越来越大,导致焊点断裂。 (金属间化合物的生成是二种金属键合的关键, 金属间化合物的剪切强度比纯金和纯铝高。)

TAB的应用

主要应用在低成本,大规模生产的电子产品。

TAB的引线在九十年代: 200—300根,内引线间距50—80um,外引线

间距<0.3mm 2000年:达到800—1000根引线

2.2.3 倒装焊

倒装焊(FCB)是芯片面朝下,芯片焊区直接与基板 焊区直接互连的一种方法。

优点: • 互连线短,互连电容、电阻、电感小,适合高频高速器件; • 占基板的面积小,安装密度高; • 芯片焊区可面分布,适合高I/O器件; • 芯片安装和互连可以同时进行,工艺简单、快速,适合

1.热压焊:

利用加热和加压力使金属丝与Al或Au金属焊区压焊在一 起。 原理:使焊区金属塑性形变,破坏压焊界面氧化层,使金属 丝和焊区金属接触面产生原子间吸引力,达到键合的目的。 此外,界面上、下金属在加热加压下相互镶嵌。 焊接压力:0.5-1.5N/点 焊头温度:150℃ 芯片温度:>200℃ 缺点:高温:氧化,生成金属间化合物;

第二章 电子封装的基本工艺

微电子制造工艺流程PPT课件

Metal = 金属

Gate = 栅

Metal = 金属

Source = 源

n-type

p-type

n-type

Drain = 漏

第4页/共83页

CMOS工作原理 (3)

• N-MOS电路 (2)

Gate = 栅

Source = 源

第5页/共83页

Drain = 漏

CMOS工作原理 (4)

Future PMOS Transistor

No current can flow through here!

第19页/共83页

Silicon Dioxide Silicon Nitride Future NMOS Transistor

Silicon Epi Layer PSilicon Substrate P+

Source = 源

第10页/共83页

Drain = 漏

CMOS工艺流程

1. Shallow Trench Formation

2. Well Formation 3. Gate Formation 4. Source/Drain

Formation

5. Salicide Formation 6. 1st Interconnect Layer 7. 2nd through Nth

第2页/共83页

CMOS工作原理 (1)

• 回顾录像:IC制造工艺

P-MOS

n-well

p-well

N-MOS

CMOS = Complementary Metal-Oxide-Semiconductor (Transistor) = 互补金属氧化物半导体(晶体管)

微电子工艺的流程

微电子工艺的流程

1. 硅片制备:

从高纯度的多晶硅棒开始,通过切割、研磨和抛光等步骤制成具有一定直径和厚度的单晶硅片(晶圆)。

2. 氧化层生长:

在硅片表面生长一层二氧化硅作为绝缘材料,这通常通过热氧化工艺完成。

3. 光刻:

使用光刻机将设计好的电路图案转移到光刻胶上,通过曝光、显影等步骤形成掩模版上的图形。

4. 蚀刻:

对经过光刻处理的硅片进行干法或湿法蚀刻,去除未被光刻胶覆盖部分的硅或金属层,形成所需的结构。

5. 掺杂:

通过扩散或离子注入技术向硅片中添加特定元素以改变其电学性质,如N型或P型掺杂,形成PN结或晶体管的源极、漏极和栅极。

6. 薄膜沉积:

包括物理气相沉积(PVD,如溅射)和化学气相沉积(CVD),用于在硅片上沉积金属互连、导体、半导体或绝缘介质层。

7. 平坦化:

随着制作过程中的多次薄膜沉积,可能需要进行化学机械平坦化(CMP)处理,确保后续加工时各层间的均匀性。

8. 金属化与互联:

制作金属连线层来连接不同功能区,通常采用铝、铜或其他低电阻金属,并利用过孔实现多层布线之间的电气连接。

9. 封装测试:

完成所有芯片制造步骤后,对裸片进行切割、封装以及质量检测,包括电气性能测试、可靠性测试等。

微电子工艺的流程

微电子工艺的流程一、工艺步骤1. 材料准备:微电子工艺的第一步是准备好需要的材料,这些材料包括硅片、硼化硅、氧化铝、金属等。

其中,硅片是制造半导体芯片的基本材料,它具有优良的导电性和导热性能,而硼化硅和氧化铝则用于作为绝缘层和保护层。

金属材料则用于连接不同的电路元件。

2. 清洗:在进行下一步的工艺之前,需要对硅片进行清洗,以去除表面的杂质和污垢。

常用的清洗方法包括浸泡在溶剂中、超声波清洗等。

清洗后的硅片表面应平整光滑,以便后续的工艺步骤能够顺利进行。

3. 刻蚀:刻蚀是微电子工艺中的重要步骤,它用于在硅片表面上形成需要的电路图案。

刻蚀一般采用化学法或物理法,化学法包括湿法刻蚀和干法刻蚀,物理法包括离子束刻蚀、反应离子刻蚀等。

刻蚀后,硅片表面将形成不同深度和形状的电路结构。

4. 清洗:刻蚀后的硅片需要再次进行清洗,以去除刻蚀产生的残留物,并保证表面的平整度和清洁度。

清洗一般采用流动水冲洗、超声波清洗等方法。

5. 沉积:沉积是在硅片表面上沉积一层薄膜来形成电路元件或连接线的工艺步骤。

常用的沉积方法包括化学气相沉积、物理气相沉积、离子束沉积等。

沉积后,硅片表面将形成具有特定性能和功能的导电膜或绝缘膜。

6. 光刻:光刻是将需要的电路图案投射在硅片表面上的工艺步骤。

光刻过程中,先在硅片表面涂上感光胶,然后利用光刻机将光阴影形成在感光胶上,最后用化学溶液溶解感光胶,形成需要的电路结构。

光刻过程需要高精度的设备和技术支持。

7. 离子注入:离子注入是将控制的离子注入硅片表面形成电子器件的重要工艺步骤。

通过控制注入的离子种类、注入能量和注入剂量,可以形成不同性能和功能的电子器件。

离子注入是微电子工艺中的关键技术之一。

8. 清洗和检测:在工艺步骤完成后,硅片需要再次进行清洗和检测,以确保电路结构和性能符合要求。

清洗和检测一般采用高精度的设备和技术支持,包括扫描电子显微镜、原子力显微镜等。

二、工艺参数和设备微电子工艺需要严格控制各种工艺参数,包括温度、压力、流量、时间等。

微电子制造概论-SMT工艺流程

SMT工艺流程

SMA Introduce

D:来料检测 => PCB的B面点贴片胶 => 贴片 => 固化 => 翻板 => PCB的A 面 丝印焊膏 => 贴片 =>

A面回流焊接 => 插件 => B面波峰焊 => 清洗 => 检测 => 返修 A面混装,B面贴装。先贴两面SMD,回流焊接,后插装,波峰焊

优点

成本最低 周转最快

提供完美的工艺定位 没有几何形状的限制 改进锡膏的释放 纵横比1:1 错误减少 消除位置不正机会 纵横比1:1

缺点

形成刀锋或沙漏形状 纵横比1.5:1

要涉及一个感光工具 电镀工艺不均匀失去 密封效果 密封块可能会去掉

激光光束产生金属熔渣 造成孔壁粗糙

Screen Printer

微电子制造概论-SMT工 艺流程

2024/2/9

目录

SMA Introduce

什么是SMA? SMT工艺流程 Screen Printer MOUNT REFLOW AOI ESD WAVE SOLDER SMT Tester SMA Clean SMT Inspection spec.

什么是SMA?

对

策

• 提高锡膏中金属成份比例(提高到88 %以上)。

• 增加锡膏的粘度(70万 CPS以上) • 减小锡粉的粒度(例如由200目降到

300目)

• 降低环境的温度(降至27OC以下) • 降低所印锡膏的厚度(降至架空高度

SNAP-OFF,减低刮刀压力及速度)

• 加强印膏的精准度。 • 调整印膏的各种施工参数。 • 减轻零件放置所施加的压力。 • 调整预热及熔焊的温度曲线。

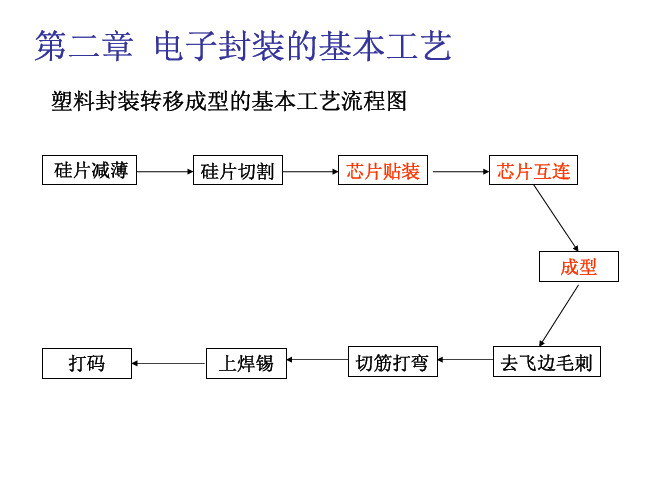

微电子封装技术第2章 封装工艺流程

2.4芯片贴装

焊接粘贴法工艺是将芯片背面淀积一定厚度的 Au或Ni,同时在焊盘上淀积Au-Pd-Ag和Cu的金属 层。

其优点是热传导好。工艺是将芯片背面淀积一 定厚度的Au或Ni,同时在焊盘上淀积Au-Pd-Ag和 Cu的金属层。这样就可以使用Pb-Sn合金制作的合 金焊料将芯片焊接在焊盘上。焊接温度取决于PbSn合金的具体成分比例。

微电子封装技术

董海青 李荣茂

第2章 封装工艺流程

2.1 流程概述 2.2 芯片减薄 2.3 芯片切割 2.4 芯片贴装 2.5 芯片互连技术 2.6 成形技术 2.7 后续工艺

2.1 流程概述

芯片封装工艺流程一般可以分为两个部分:前 段操作和后段操作。前段操作一般是指用塑料封装 (固封)之前的工艺步骤,后段操作是指成形之后 的工艺步骤。

2.4芯片贴装

导电胶粘贴法不要求芯片背面和基板具有金属 化层,芯片座粘贴后,用导电胶固化要求的温度时 间进行固化,可以在洁净的烘箱中完成固化,操作 起来比较简便易行。

导电胶进行芯片贴装的工艺过程如下:用针筒 或注射器将黏着剂涂布在芯片焊盘上,然后将芯片 精确地放置到焊盘的黏着剂上面。

导电胶粘贴法的缺点是热稳定性不好,容易在 高温时发生劣化及引发黏着剂中有机物气体成分泄 露而降低产品的可靠度,因此不适用于高可靠度要 求的封装。

2.4芯片贴装

玻璃胶粘贴芯片时,先以盖印、网印、点胶等 技术将玻璃胶原料涂布在基板的芯片座上,将IC芯 片放置在玻璃胶上后,再将封装基板加热至玻璃熔 融温度以上即可完成粘贴。

玻璃胶粘贴法的优点是可以得到无空隙、热稳 定性优良、低结合应力与低湿气含量的芯片粘贴; 其缺点是玻璃胶中的有机成分与溶剂必须在热处理 时完全去除,否则对封装结构及其可靠度将有所损 害。

微电子工艺流程

微电子工艺流程1. 概述微电子工艺是处理微尺寸的电子器件的制造过程,它涉及到一系列精细的工艺步骤。

在本文档中,我们将介绍微电子工艺的基本流程,包括光刻、沉积、腐蚀、离子注入等关键步骤。

了解微电子工艺流程的基本原理和步骤对于微电子设备的制造和理解至关重要。

2. 光刻光刻是微电子工艺中的关键步骤之一,用于在半导体材料上定义图案和结构。

下面是光刻的基本流程:1.准备基片:首先,选择合适的半导体材料作为基片,并进行清洗和处理,以确保表面的纯洁度和平坦度。

2.胶涂覆:将光刻胶涂覆在基片表面上,利用旋涂机或涂覆机来均匀地涂布光刻胶。

3.预烘烤:将涂覆了光刻胶的基片放入烘箱中进行预烘烤,以去除胶液中的溶剂和气泡。

4.对准与曝光:使用光刻机将掩膜对准和曝光到光刻胶表面,通过可见光或紫外光刺激光刻胶,形成所需图案。

5.显影:将曝光后的光刻胶基片浸泡在显影液中,显影液会将未曝光部分的光刻胶溶解掉,形成所需的图案。

6.后烘烤:将显影后的光刻胶基片进行后烘烤,以去除残留的显影液和增强光刻胶的附着力。

7.清洗:使用溶剂将光刻胶残留物彻底清洗干净,以保证基片表面的纯净度。

3. 沉积沉积是微电子工艺中另一个重要的步骤,用于在基片上沉积薄膜材料。

以下是典型的沉积过程:1.基片准备:与光刻类似,首先需要准备基片,并确保表面的平整度和清洁度。

2.选择沉积方法:根据需要沉积的材料和要求,选择合适的沉积方法,包括化学气相沉积(CVD)、物理气相沉积(PVD)等。

3.沉积薄膜:将基片放入沉积室中,并通过提供适当的气体或蒸发源来沉积所需的薄膜材料。

4.监控和控制:在沉积过程中,通过监控和调整沉积速率、温度和气体浓度等参数,以确保薄膜的质量和厚度符合要求。

5.结束和清洗:当沉积达到预定的厚度后,停止供气或蒸发,将基片取出并清洗,以去除表面的残留物。

4. 腐蚀腐蚀是微电子工艺中的一种重要的加工方法,用于去除或改变薄膜或基片的部分区域。

以下是典型的腐蚀流程:1.基片准备:与前面的过程类似,准备基片并确保表面的清洁和平整。

微电子工艺技术

微电子工艺技术引言微电子工艺技术是现代电子工程领域中的关键技术之一。

它主要涉及到在微米或纳米尺度范围内,对半导体材料进行加工和制备的技术方法。

微电子工艺技术的发展使得集成电路的制造变得更加精细化和复杂化,从而推动了电子设备的发展和智能化。

本文将介绍微电子工艺技术的基本原理、常用的工艺步骤以及最新的研究进展。

基本原理微电子工艺技术主要基于半导体材料的特性和物理原理进行设计和研究。

它通过在半导体表面上进行一系列加工步骤,形成电子元件和电路。

这些加工步骤包括:光刻、沉积、蚀刻、离子注入、热处理等。

光刻是微电子工艺中最关键的步骤之一。

它通过将光敏感的光刻胶涂覆在半导体表面上,然后通过光学投影曝光和显影的方式,将电路的图形转移到光刻胶上。

接着,通过蚀刻的方式,将暴露在光刻胶上的区域去除,以形成所需的电路图形。

沉积是指在半导体表面上进行材料层的沉积,主要是用于形成导电层、绝缘层和敏感层等。

常用的沉积方法包括化学气相沉积(CVD)、物理气相沉积(PVD)和溅射沉积等。

蚀刻是指通过化学或物理的方式,使材料表面的部分区域被移除。

蚀刻可以用于去除不需要的材料,在半导体制造过程中起到精确控制电路形状和结构的作用。

离子注入是将离子注入到半导体材料中,改变其导电性质的过程。

离子注入可以形成导电层和控制器件的电性能。

热处理是通过高温处理,使材料发生结构和性能的改变。

热处理可以提高材料的晶格结构和电学性能,从而改善器件的性能。

工艺步骤微电子工艺技术涉及的步骤较为复杂,下面将介绍一般情况下的典型工艺步骤:1. 表面清洁表面清洁是微电子工艺中的第一步,它可以去除杂质、氧化物和有机物等对器件性能的影响。

常用的清洗方法包括浸泡清洗、超声波清洗和等离子体清洗等。

2. 沉积沉积是指在半导体表面上沉积材料层,形成所需的结构和功能。

常用的材料包括金属、绝缘层和敏感层等。

沉积方法根据要求的材料和性能不同,选择不同的方法,如化学气相沉积、物理气相沉积和溅射沉积等。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

20、电极多晶硅的淀积

• 利用低压化学气相沉积(LPCVD ) 技 术在晶圆表面沉积多晶硅,以做为连接 导线的电极。

华中科技大学电子科学与技术系

21、电极掩膜的形成

• 涂布光刻胶在晶圆上,再利用光刻技术 将电极的区域定义出来。

华中科技大学电子科学与技术系

22、活性离子刻蚀

晶格排列。退火就是利

用热能来消除晶圆中晶

格缺陷和内应力,以恢

复晶格的完整性。同时

使注入的掺杂原子扩散

到硅原子的替代位置,

使掺杂元素产生电特

性。

华中科技大学电子科学与技术系

11、去除二氧化硅

• 利用湿法刻蚀方法去除晶圆表面的二氧化 硅。

华中科技大学电子科学与技术系

12、前置氧化

• 利用热氧化法在晶圆上形成一层薄的氧 化层,以减轻后续氮化硅沉积工艺所产 生的应力。

• 利用活性离子刻蚀技术刻蚀出多晶硅电 极结构,再将表面的光刻胶去除。

华中科技大学电子科学与技术系

23、热氧化

• 利用氧化技术,在晶圆表面形成一层氧 化层。

华中科技大学电子科学与技术系

24、NMOS源极和漏极形成

• 涂布光刻胶后,利用光刻技术形成NMOS源极与漏极 区域的屏蔽,再利用离子注入技术将砷元素注入源极 与漏极区域,而后将晶圆表面的光刻胶去除。

1. 洁净室和清洗 2. 氧化和化学气相淀积 3. 光刻和腐蚀 4. 扩散和离子注入 5. 金属连接和平面化 三. 标准CMOS工艺流程

华中科技大学电子科学与技术系

1、初始清洗

• 初始清洗就是将晶圆放入清洗槽中,利用化学或物理的 方法将在晶圆表面的尘粒或杂质去除,防止这些杂初始 清洗就是将晶圆放入清洗槽中,利用化学或物理的方法 将在晶圆表面的尘粒或杂质去除,防止这些杂质尘 粒, 对后续的工艺造成影响,使得器件无法正常工作。

3、淀积氮化硅

• 利用低压化学气相沉积(LPCVD)的技术, 沉积一层氮化硅,用来做为离子注入的mask 及后续工艺中,定义P型井的区域。

华中科技大学电子科学与技术系

4、P阱的形成

•将光刻胶涂在晶圆上之后,利用光刻技术, 将所要形成的P型阱区的图形定义出来,即将 所要定义的P型阱区的光刻胶去除掉。

9、 N阱离子注入

• 利用离子注入技术,将磷打入晶圆中, 形成n型阱。而在P型阱的表面上由于有 一层二氧化硅膜保护,所以磷元素不会 植入打入P型阱之中。

华中科技大学电子科学与技术系

10、N阱退火

• 离子注入之后会严重地

破坏硅晶圆晶格的完整

性。所以掺杂离子注入

之后的晶圆必须经过适

当的处理以回复原始的

华中科技大学电子科学与技术系

2、前置氧化

• 利用热氧化法生长一层二氧化硅薄膜,目的是为了降 低后续生长氮化硅薄膜工艺中的应力(stress),氮化硅 具有很强的应力,会影响晶圆表面的结构,因此在这 一层氮化硅及硅晶圆之间,生长一层二氧化硅薄膜来 减缓氮化硅与硅晶圆间的应力。

华中科技大学电子科学与技术系

华中科技大学电子科学与技术系

25、 PMOS源极和漏极形成

• 利用光刻技术形成PMOS源极及漏极区域的屏蔽之 后,再利用离子注入技术将硼元素注入源极及漏极区 域,而后将晶圆表面之光刻胶去除。

华中科技大学电子科学与技术系

26、未掺杂的氧化层化学气相淀积

• 利用等离子体增强化学气相沉积 ( PECVD )技术沉积一层无掺杂的氧化 层,保护器件表面,免于受后续工艺的 影响。

• 将晶圆放入炉管中,做高温的处理,以达到硅晶圆退 火的目的,并且顺便形成一层n型阱的离子注入mask 层,以阻止下一步骤中﹝n型阱的离子注入﹞,n型掺 杂离子被打入P型井内。

华中科技大学电子科学与技术系

8、去除氮化硅

• 将晶圆表面Leabharlann 氮化硅,利用热磷酸 湿式蚀刻的方法将其去除掉。

华中科技大学电子科学与技术系

华中科技大学电子科学与技术系

18、利用氢氟酸去除电极区域的氧化层 • 除去氮化硅后,将晶圆放入氢氟酸化学

槽中,去除电极区域的氧化层,以便能 在电极区域重新成长品质更好的二氧化 硅薄膜,做为电极氧化层。

华中科技大学电子科学与技术系

19、电极氧化层的形成

• 此步骤为制做CMOS的关键工艺,利用 热氧化法在晶圆上形成高品质的二氧化 硅,做为电极氧化层。

华中科技大学电子科学与技术系

15、氮化硅的刻蚀

• 以活性离子刻蚀法去除氧化区域上的氮 化硅。接着再将所有光刻胶去除。

华中科技大学电子科学与技术系

16、元件隔离区的氧化

• 利用氧化技术,长成一层二氧化硅膜, 形成器件的隔离区。

华中科技大学电子科学与技术系

17、去除氮化硅

• 利用热磷酸湿式蚀刻的方法将其去 除掉。

华中科技大学电子科学与技术系

27、CMOS源极和漏极的活化与扩散

• 利用退火技术,将经离子注入过的漏极 及源极进行电性活化及扩散处理。

华中科技大学电子科学与技术系

28、淀积含硼磷的氧化层

• 加入硼磷杂质的二氧化硅有较低的溶点,硼磷氧化层 (BPSG)加热到摄氏800度时会有软化流动的特性,可 以利用来进行晶圆表面初级平坦化,以利后续光刻工 艺条件的控制。

华中科技大学电子科学与技术系

5、去除氮化硅

• 将晶圆表面的氮化硅,利用干法刻蚀的方法 将其去除掉。

华中科技大学电子科学与技术系

6、P阱离子注入

• 利用离子注入的技术,将硼打入晶圆 中,形成P型阱。接着利用无机溶液, 如硫酸或干式臭氧(O3)烧除法将光刻 胶去除。

华中科技大学电子科学与技术系

7、P阱退火及氧化层的形成

华中科技大学电子科学与技术系

13、氮化硅的淀积

• 利用低压化学气相沉积方法(LPCVD)淀积 氮化硅薄膜,用来定义出器件隔离区域,使 不被氮化硅遮盖的区域,可被氧化而形成组 件隔离区。

华中科技大学电子科学与技术系

14、元件隔离区的掩膜形成

• 利用光刻技术,在晶圆上涂布光刻胶, 进行光刻胶曝光与显影,接着将氧化绝 缘区域的光刻胶去除,以定义出器件隔 离区。

微电子工艺

雷鑑铭 博士

华中科技大学电子科学与技术系 2005年7月

华中科技大学电子科学与技术系

课程介绍

教材:《半导体制造技术》 韩郑生 译 电子工艺出版社出版

学时:24 参考书: 1、《芯片制造》 2、《微电子科学原理与工程技术》

华中科技大学电子科学与技术系

课程讲授内容:

一. 微电子工艺概述 二. 微电子工艺步骤介绍