EDA仿真图

eda课程设计—算术逻辑运算单元 (1)

燕山大学EDA课程设计报告书题目:算术运算逻辑单元ALU 姓名:班级:学号:成绩:一、设计题目及要求题目名称:算术运算单元ALU要求:1.进行两个四位二进制数的运算;2.算术运算:A+B, A-B, A×B;3.逻辑运算:A and B, A or B, A not, A xor B;4. 用数码管显示算术运算结果,以LED指示灯显示逻辑运算结果。

二、设计过程及内容(包括○1总体设计的文字描述,即由哪几个部分构成的,各个部分的功能及如何实现方法;○2主要模块比较详尽的文字描述,并配以必要的图片加以说明,但图片数量无需太多)1.整体设计思路(1)根据设计要求将题目划分为五个模块。

包括两个逻辑运算模块,两个算术运算模块,和一个控制模块。

其中逻辑运算模块为A and B和A or B,A not和A xor B;算术模块为A±B,A×B。

(2)因为需要进行四位二进制数的运算,因此用A4,A3,A2,A1表示四位二进制数A,用B4,B3,B,B1表示四位二进制数B,用C4,C3,C2,C1表示四位二进制数C。

其中A,B为输入,C为输出。

2.分模块设计(1)A+B和A-B模块A+B可以直接通过74283 两个四位二进制数加法器实现。

A-B可以看作A+(-B),即A加B的补码来实现。

同时再设计一个转换控制端M。

M=0时实现A+B,M=1时实现A-B。

最后再设计一个总的控制端K1,K1=1时模块正常工作,K1=0时不工作。

做加法时,C0为进位输出,C0输出1表示有进位,做减法时,C0为借位输出,C0输出1表示有借位。

通过74283五位输出,进入译码器将五位变成八位输出,在通过数码管显示。

实现A+B,例:0111+0111=1110(7+7=14)则数码管应显示14。

实现A-B 例:1100-0110=0110(12-6=6)则数码管显示06。

A+B,A-B总原理图如下:A+B,A-B分原理图如下:译码器原理图如下:扫描电路原理图如下:A+B仿真图:A-B仿真图:(2)AXB模块AXB模块采用乘数累加被乘数的次的原理来实现乘法功能。

EDA-实验报告

实验一五人表决器设计一、实验目的1 加深对电路理论概念的理解3 加深计算机辅助分析及设计的概念4 了解及初步掌握对电路进行计算机辅助分析的过程二、实验要求制作一个五人表决器,共五个输入信号,一个输出信号。

若输入信号高电平数目多于低电平数目,则输出为高,否则为低。

三、实验原理根据设计要求可知,输入信号共有2^5=32种可能,然而输出为高则有15种可能。

对于本设计,只需一个模块就能完成任务,并采用列写真值表是最简单易懂的方法。

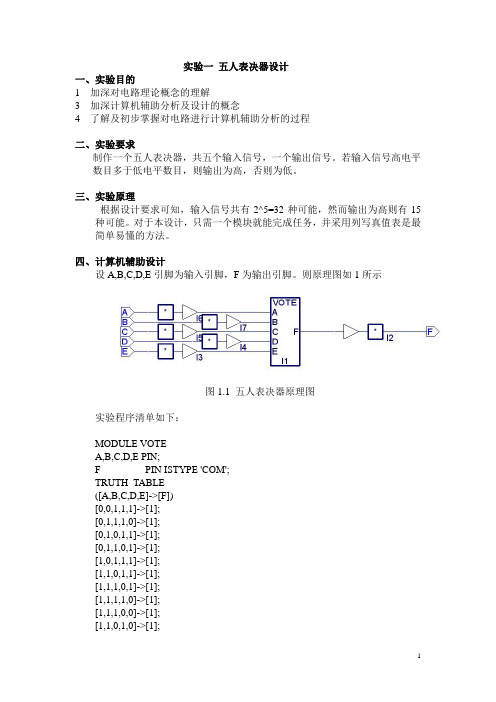

四、计算机辅助设计设A,B,C,D,E引脚为输入引脚,F为输出引脚。

则原理图如1所示图1.1 五人表决器原理图实验程序清单如下:MODULE VOTEA,B,C,D,E PIN;F PIN ISTYPE 'COM';TRUTH_TABLE([A,B,C,D,E]->[F])[0,0,1,1,1]->[1];[0,1,1,1,0]->[1];[0,1,0,1,1]->[1];[0,1,1,0,1]->[1];[1,0,1,1,1]->[1];[1,1,0,1,1]->[1];[1,1,1,0,1]->[1];[1,1,1,1,0]->[1];[1,1,1,0,0]->[1];[1,1,0,1,0]->[1];[1,1,1,1,1]->[1];[1,1,0,0,1]->[1];[1,0,0,1,1]->[1];[1,0,1,0,1]->[1];[1,0,1,1,0]->[1];END五、实验测试与仿真根据题目要求,可设输入分别为:0,0,0,0,0;1,1,1,1,1;1,0,1,0,0;0,1,0,1,1。

其测试程序如下所示:MODULE fivevoteA,B,C,D,E,F PIN;X=.X.;TEST_VECTORS([A,B,C,D,E]->[F])[0,0,0,0,0]->[X];[1,1,1,1,1]->[X];[1,0,1,0,0]->[X];[0,1,0,1,1]->[X];END测试仿真结果如图1.2所示:图1.2 五人表决器设计仿真图可知,设计基本符合题目要求。

EDA基本操作一

File → New Project Wizard →填写相关信息(其实就是把刚才保存的文件名输入进去)如图10→Next → 点 →弹出一个框,选择我们前面保存的文件,确定(图11)→回到原来的界面选择Add→ Next→按图12选择后 Next→Next→Finish

图10

完成

第二部分待续

然后习惯的改一下全屏显示

右键→zoom → fit inwindows

3.添加信号源

View→Untility_windows →Node_Finder(alt+1) →如图20点list →点开以后如图21,按住Ctrl点选信号源,拖动到左侧→做完之后关闭对话框

图20

图214.仿真Leabharlann 如图般设置之后,点击蓝色三角形

图11

图12

做完这一步就可以编译了

Ⅳ.编译

编译只需要点击图中的棕色向右的三角形就可以了

至于编译出错的话处理方法下次再说,做word太累了

Ⅴ.编译

1.新建一个时序仿真波形图

File→ New…→ Vector wavefom File → OK

2.改仿真时长

Eidt→ Endtime → 输入你想要的数字,确定

第一部分

Ⅰ.建立一个新的程序与工程

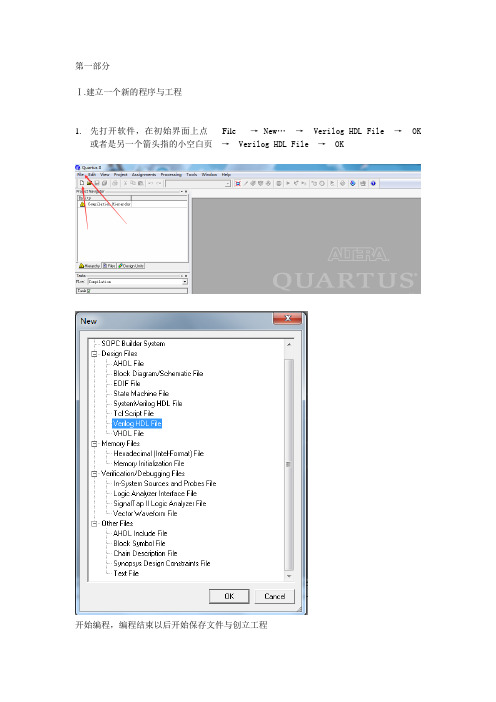

1.先打开软件,在初始界面上点File→ New…→ Verilog HDL File → OK或者是另一个箭头指的小空白页→ Verilog HDL File → OK

开始编程,编程结束以后开始保存文件与创立工程

Ⅱ.保存

点击 →选择保存路径(点开时路径默认是安装程序,一般不保存在这)→改文件名,文件名与模块名一致,如图中的abc→保存→在弹出的对话框上选择否(意思是问你是否希望现在就新建一个工程,在这里我们先选择否)

集成电路EDA与验证技术课件:模拟集成电路设计与仿真

模拟集成电路设计与仿真

常用命令格式: (1) DEFINE 格式:DEFINE <库名> <库路径> 例: DEFINE sample /export/cadence/IC615USER5/tools.lnx86/dfII/samples/cdslib/sa mple (2) INCLUDE 格式:INCLUDE <另外一个cds.lib 的全路径>

模拟集成电路设计与仿真

图3.2 Spectre中包含的各种仿真器

模拟集成电路设计与仿真

2.精确的晶体管模型 Spectre为所有的仿真器提供一致的器件模型,这有利于 消除不同模型间的相关性,从而得到快速收敛的仿真结果。 模型的一致性也保证了器件模型在升级时可以同时应用于所 有的仿真器。 3.高效的程序语言和网表支持 Spectre仿真平台支持多种设计提取方法,并兼容绝大多 数SPICE输入平台。Spectre可以读取Spectre、SPICE以及 Verilog-A格式的器件模型,并支持标准的Verilog-AMS、 VHDL-AMS、Verilog-A、Verilog以及VHDL格式的文本输 入。

模拟集成电路设计与仿真

5.有力衔接了版图设计平台 对于完整的版图设计平台而言,Spectre是不可或缺的重 要环节,它能方便地利用提取的寄生元件参数来快速完成后 仿真(post-layout simulation)的模拟,并与前仿真(pre-layout simulation)的模拟结果作比较,紧密的连接了电路 (Schematic)和版图(layout)的设计。 6.交互的仿真模式 设计者可以在仿真过程中快速改变参数,并在不断调整 参数和模拟之中找到最佳的电路设计结果,减少电路设计者 模拟所花费的时间。

电子课程设计EDA课程设计乐曲硬件演奏电路

电子课程设计——乐曲硬件演奏电路设计学院太原科技大学华科学院专业、班级电子信息工程姓名学号指导教师2011年12月目录一、设计任务与要求 (3)二、总框体图 (3)三、选择器件 (4)四、功能模块 (4)一、音乐数据模块 (4)二、音符控制输出模块 (7)3、音符译码模块 (8)4、数控分频器模块 (11)五、分频器模块 (12)六、译码模块 (13)五、整体设计电路图 (15)一、整体电路原理图……………………………15二、管脚分派图……………………………153、电路仿真结果 (15)4、硬件验证 (16)六、设计心得 (17)七、附录 (19)乐曲硬件演奏电路设计一、设计任务与要求:一、实验内容利用可编程逻辑器件FPGA,设计乐曲硬件演奏电路,可自动演奏乐曲。

二、实验要求(1)利用数控分频器设计硬件乐曲演奏电路。

(2)利用给定的音符数据定制ROM“music”。

(3)设计乘法器逻辑框图,并在QuartusII上完成全部设计。

(4)将音乐通过实验箱上的喇叭播放出来。

(5)与演奏发音相对应的简谱码输出在数码管上显示。

二、整体框图设计思路:C调音阶频率表:同的预置数即可发出不同频率的声音。

由此,可以以此为设计基础。

设计一功能模块,能够将乐曲中的音符一一以对应的频率以预置数的形式置入数控分频计中,即可利用该数控分频计产生不同的声音,演奏出设定好的音乐。

ROM 中的音乐数据文件刚可由编辑好的音符填入MIF 文件中再定制LPM_ROM 将音符数据加载入ROM 中,并设计程序在运行时自动读取ROM 中的文件并置入数控分频器中。

当采用四四拍曲子时,每节拍持续时间为秒。

置入数控分频器的速度也应与此同步或一致,避免音乐过快或过快慢而失真。

由已知的C 调音阶频率表,各频率对应的预置数就与数控分频推动蜂鸣器发作声音的频率对应。

在编写数控分频器时,不仅要考虑预置数的输入方式,还要考虑输入的速度,和驱动蜂鸣器发声的频率。

EDA技术基础实验报告

《EDA技术基础》实验报告学院:信息科学技术学院专业:电子信息工程指导教师:龙翔完成日期:2013年12月目录实验一MAX-plusll 及开发系统使用 (3)实验二高速四位乘法器设计 (6)实验三秒表的设计 (9)实验四序列检测器的设计 (13)实验五数字频率计的设计 (18)六实验总结 (20)实验一一:实验名称:MAX-plusll 及开发系统使用二:实验内容1.利用MAX-plusII中的图形编辑器设计一半加器,进行编译、仿真,并将其设置成为一元件。

2.建立一个更高的原理图设计层次,利用前面生成的半加器元件设计一个全加器,进行编译、仿真,并将其设置成为一个元件。

3.再建立一个更高的原理图设计层次,利用前面生成的半加器元件设计一个全加器,进行编译、仿真。

4.选择器件“Assign”“Device”“MAX7000S”“EPM7128SLC84-6”,并根据下载板上的标识对管脚进行配置。

然后下载,进行硬件测试,检验结果是否正确。

三.实验程序1).半加器图2)全加器图3)四位全加器四:仿真图1).半加器仿真图2).全加器仿真图3).四位全加器仿真图实验二一:实验名称高速四位乘法器设计二: 实验内容1.利用MAX-plusⅡ中的图形编辑器设计1-4的二进制乘法器,进行编译、仿真,并将其设置成为一元件,命名为and14。

2.建立一个更高得原理图设计层次,利用前面生成的1-4的二进制乘法器和调用库中的74283元件设计一高速4位乘法器。

三:实验程序1.2.四:仿真图实验三一:实验名称秒表的设计二:实验内容(一)、实验步骤1、采用自顶向下的设计方法,首先将系统分块;2、设计元件,即逻辑块;3、一级一级向上进行元件例化(本实验只需例化一次即可),设计顶层文件。

(二)、实验程序设计原理实验程序如三所示,其中输入信号分别为使能信号ENA、清零信号CLR、时钟信号CLK,输出信号有秒针信号CA和分针信号CB。

EDA大作业 课程设计 简易计算器

在掌握常用数字电路功能和原理的基础上,根据EDA技术课程所学知识,利用硬件描述语言Verilog HDL、EDA软件Quartus II和硬件平台Cyclone/Cyclone II FPGA进行电路系统的设计。

本次实验我完成的内容是简单计算器的设计,下面我简单的进行一下原理的阐述。

设计一个简单计算器,输入为8位二进制数,分别用两位数码管显示,输出的计算结果为16位二进制数,并用四位数码管显示,能够实现+、-、 *、/ 四种运算,其中除法的结果显示分为商和余数两部分,分别用两位数码管显示。

为了完成要求的效果显示,我先设计了一个简单的四则运算器,为了使其结果能清楚的看到,所以计算器模块和一个7段数码管模块连接。

实验要求,输入分别用两位数码管显示,输出用四位数码管显示,所以用一个3—8译码器和数码管连接,通过开关控制,形成动态显示。

从左向右,依次是第一位数码管显示a的高四位,第二位数码管显示a的低四位;第三位数码管显示b的高四位,第四位数码管显示b的低四位;第五位数码管到第八位数码管显示输出的结果。

通过改变时钟,使其看起来像同时显示在数码管上。

设计流程如下图,分别用两个数码管表示八位二进制数,用一个case 语句表示输入数值采用哪种运算方式,分别用00,01,10,11表示加,减,乘,除。

用3—8译码器选择从哪个数码管输出。

硬件流程图输出结果 A. B 的显示软件流程图LED 灯接线部分显示:中心控制 复位编码 数码管输出输入A 输入B 运算选择C 输出out L E D 8 L E D 7 L E D 6 L E D 5 L E D 4 L E D 3 L E D 2 L E D 1第三章程序简单计算器的程序如下:module jsq9(a,b,c,Dout,count,clk,rst);input[7:0]a,b;input clk,rst;input[1:0]c;output[6:0]Dout;output [2:0]count;reg[6:0]Dout;reg[2:0]count;reg[15:0]out;reg[6:0] LED7S1,LED7S2,LED7S3,LED7S4, LED7S5,LED7S6,LED7S7,LED7S8; DECL7S u1(.A(a[7:4]) , .LED7S(LED7S1));DECL7S u2(.A(a[3:0]) , .LED7S(LED7S2));DECL7S u3(.A(b[7:4]) , .LED7S(LED7S3));DECL7S u4(.A(b[3:0]) , .LED7S(LED7S4));DECL7S u5(.A(out[15:12]) , .LED7S(LED7S5));DECL7S u6(.A(out[11:8]) , .LED7S(LED7S6));DECL7S u7(.A(out[7:4]) , .LED7S(LED7S7));DECL7S u8(.A(out[3:0]) , .LED7S(LED7S8));reg[7:0]out1,out2;always@(a,b,c,Dout,count,clk,rst)case(c)2'b00:out=a+b;2'b01:out=a-b;2'b10:out=a*b;2'b11:beginout1=a/b;out2=a%b;out={out1,out2};enddefault:;endcasealways@(posedge clk or negedge rst)beginif(!rst)count<=3'b000;else if(count==3'b111)count<=3'b000;elsecount<=count+3'b001;endalways@(posedge clk)begincase(count)3'b000: Dout<=LED7S1;3'b001:Dout<=LED7S2;3'b010:Dout<=LED7S3;3'b011:Dout<=LED7S4;3'b100: Dout<=LED7S5;3'b101:Dout<=LED7S6;3'b110:Dout<=LED7S7;3'b111:Dout<=LED7S8;endcaseendendmodulemodule DECL7S (A, LED7S);input [3:0] A;output [6:0] LED7S;reg [6:0] LED7S;always @(A)begincase(A)4'b0000 : LED7S<=7'b0111111; 4'b0001: LED7S <= 7'b0000110 ; 4'b0010: LED7S <= 7'b1011011; 4'b0011: LED7S <= 7'b1001111; 4'b0100: LED7S <= 7'b1100110 ; 4'b0101: LED7S <= 7'b1101101; 4'b0110: LED7S <= 7'b1111101 ; 4'b0111: LED7S <= 7'b0000111 ; 4'b1000: LED7S <= 7'b1111111 ; 4'b1001: LED7S <= 7'b1101111 ; 4'b1010: LED7S <= 7'b1110111 ; 4'b1011: LED7S <= 7'b1111100 ; 4'b1100: LED7S <= 7'b0111001 ;4'b1101: LED7S <= 7'b1011110 ; 4'b1110: LED7S <= 7'b1111001 ; 4'b1111: LED7S <= 7'b1110001 ; endcaseendendmodule第四章模块连接在本程序中,共由三个模块组成,第一个模块是一个四选一多路器其仿真图为:第二个模块是7段数码管显示程序如下module DECL7S (A, LED7S);input [3:0] A;output [6:0] LED7S;reg [6:0] LED7S;always @(A)begincase(A)4'b0000 : LED7S<=7'b0111111;4'b0001: LED7S <= 7'b0000110 ;4'b0010: LED7S <= 7'b1011011;4'b0011: LED7S <= 7'b1001111;4'b0100: LED7S <= 7'b1100110 ;4'b0101: LED7S <= 7'b1101101;4'b0110: LED7S <= 7'b1111101 ;4'b0111: LED7S <= 7'b0000111 ;4'b1000: LED7S <= 7'b1111111 ;4'b1001: LED7S <= 7'b1101111 ;4'b1010: LED7S <= 7'b1110111 ;4'b1011: LED7S <= 7'b1111100 ;4'b1100: LED7S <= 7'b0111001 ;4'b1101: LED7S <= 7'b1011110 ;4'b1110: LED7S <= 7'b1111001 ;4'b1111: LED7S <= 7'b1110001 ;endcaseendendmodule仿真图如下:把这个两个模块用一个3—8译码器进行连接,使其达到实验的要求。

EDA课程设计智能函数发生器

EDA课程设计题目:智能函数发生器专业:通信工程班级:通信082姓名:谢振峰学号:0810920213一、设计题目:智能函数发生器设计一个智能函数发生器,能够产生递增、递减、方波、三角波、正弦波及及阶梯波波形,并可通过开关选择输出的波形。

二、设计目标:1)设计一个智能函数发生器,能够以稳定的频率发生递增斜波、递减斜波、三角波、梯形波,正弦波和方波。

2)设置一个波形选择输入信号,通过此改变该信号可以选择以上各种不同种类的输出函数波形,系统具有复位功能。

三、设计原理:1.原理图框图如下:图1、原理图框图2.原理图说明本设计采用VHDL语言和原理图设计结合的方法,首先用文本输入法设计了六个波形模块,分别为递增、递减、三角波、梯形、正弦波、方波模块,和一个选择模块。

然后进行原理图设计,将各波形模块与选择模块相应的引脚连接,从而完成智能函数发生器的设计。

四、设计内容:1)递增模块递增模块是用VHDL语言描述的递增函数,实体部分部分说明三个端口,两个输入端口时钟信号clk、复位信号rst和一个输出端口q。

设计思路为:通过设计一个中间变量从0x00到0xFF的递增赋值给输出信号q,从而实现递增数字信号的输出。

递增模块仿真图如下:图2、递增模块仿真图2)递减模块递减模块的实体包含时钟信号输入端口clk和复位信号端口rst,输出信号端口q。

设计思路为:通过设计一个中间变量从0xFF到0x00的递减赋值给输出信号q,从而实现递减数字信号的输出。

图3、递减模块仿真图3)三角波模块三角波模块的实体包含时钟信号输入端口clk和复位信号端口rst,输出信号端口q。

设计思路为:通过设计一个中间变量先从0x00递增到0x7F,然后从0x7F递减到0x00,将中间变量赋值给输出信号q,从而实现一个周期三角波形的输出。

三角波模块仿真图如下:图4、三角波模块仿真图4)阶梯波模块阶梯波模块的实体包含时钟信号输入端口clk和复位信号端口rst,输出信号端口q。

EDA课程设计-交通灯-图文

EDA课程设计-交通灯-图文交通信号灯控制电路设计一、概述城市道路交叉口是城市道路网络的基本节点,也是网络交通流的瓶颈。

目前,大部分无控制交叉口都存在高峰小时车流混乱、车速缓慢、延误情况严重、事故多发、通行能力和服务水平低下等问题。

特别是随着城市车流量的快速增长,城市无控制道路交叉口的交通压力越来越大。

因此,做好基于EDA技术平台的交叉口信号控制设计是缓解交通阻塞、提高城市道路交叉口车辆通行效率的有效方法。

交通信号控制的目的是为城市道路交叉口(或交通网络)提供安全可靠和有效的交通流,通常最为常用的原则是车辆在交叉口的通过量最大或车辆在交叉口的延误最小。

交通信号灯控制电路是显示主干道和支干道交替放行时间并用试验箱左上角的彩灯来红黄绿支红代替信号灯的一种实际电路。

设计一个基于FPGA的红绿灯交通信号控制器。

假设某个十干黄绿道字路口是由一条主干道和一条次干道汇合而成,在每个方向设置红绿黄三种信号灯,红灯亮禁止通行,绿灯亮允许通行。

黄灯亮允许行驶中车辆有时间停靠到禁止线以外。

第-1-页共18页二、方案设计与论证在硬件时钟电路的基础上,采用分频器,输出一个1S的时钟信号,在时钟信号的控制下,实现主干道和支干道红绿灯交替显示。

红绿灯交通灯控制器层次设计:EDA技术的基本设计方法有电路级设计方法和系统级设计方法。

电路级设计方法已经不能适应新的形势,本系统采用的是系统级层次设计方法,对整个系统进行方案设计和功能划分,系统的关键电路用一片FPGA芯片实现,首先用VHDL语言编写各个功能模块程序,最后通过综合器和适配器生成最终的目标器件,然后用顶层原理图将各功能模块连接起来。

下面给出各模块的VHDL设计过程和仿真结果。

1、系统时序发生电路clk_gen的VHDL设计在红绿灯交通信号控制系统中,大多数的情况是通过自动控制的方式指挥交通的。

因此,为了避免意外事件的发生,电路必须给一个稳定的时钟(clock)才能让系统正常运作。

EDA课程设计——数字跑表

第一章引言数字电子技术的应用一直在向着广度和深度扩展。

时至今日,“数字化”的浪潮几乎席卷了电子技术应用的一切领域。

由于电子产品的更新周期日益缩短,新产品开发速度日益加快,因而对电子设计自动化(EDA)提出了更高的要求,也有力地促进了EDA技术的发展和普及。

在数字集成电路方面,电路的集成度如摩尔定律(Moore’s Law)所预言的那样,以每1-2年翻一番的速度增长,使电路的复杂程度越来越高、规模越来越大。

同时,在基本技能方面,对使用EDA工具的能力也提出了更高的要求。

因此,学好EDA课程设计至关重要。

第二章 设计说明1.器件介绍-集成十进制加法计数器74160集成同步十进制加法计数器74160。

图2-1给出了74160的引脚排列图和逻辑符号图。

除了具有十进制加法计数功能外,还具有异步复位、同步预置数和计数状态保持、对输入的时钟信号进行分频等功能。

CLRN 为异步复位端,LDN 为预置数控制端,A-D 为预置状态输入端,RCO 为进位输出端,ENT 和ENP 为工作状态控制端(双使能端)。

图2-1 74160逻辑符号图 表2-1 74160功能特性 表2-2是74160的功能表,它给出了各种控制信号作用下计数器的工作状态,具体如下。

序号 CLK CLRN LDN ENP ENT 工作状态 1 × 0 × × × 复位 2 ↑ 1 0 × × 预置数 3 ↑ 1 1 1 1 正常计数 4 × 1 1 × 0 保持,且C=0 5×110 1保持表2-2 74160的功能表⑴当CLRN=0时,无论其他功能端为何状态,计数器都将复位,有QD ~QA=0000(注:QD 为状态端最高位)。

⑵当CLRN=1、LDN=0时,计数器处于预置数状态。

在出现此情况后的第一个CLK 上升沿,将预置输入端加载的数据送入计数器,即有QD ~QA=D ~A(注:D 为置入端最高位)。