基于STM32的四路抢答器原理图

4路智力抢答器及原理电路图

1.设计目的当今的社会竞争日益激烈,选拔人才,评选优胜,知识竞赛之类的活动愈加频繁,而在竞赛中往往分为几组参加,这时针对主持人提出的问题,如果要是让抢答者用举手等方法,这在某种程度上会因为主持人的主观误断造成比赛的不公平性。

比赛中为了准确、公正、直观地判断出第一抢答者,这就要有一种抢答设备作为裁判员,这就必然离不开抢答器。

在数字电路设计的过程中具体的目的如下:1)巩固和加深对电子电路基本知识的理解,提高综合运用本课程所学知识的能力。

2)培养根据设计需要选学参考书籍,查阅相关手册、图表和文献资料的自学能力,并掌握抢答器的基本原理,掌握4D锁存器、计数器、555定时器的工作原理和使用方法。

3)通过电路方案的分析、论证和比较,设计计算和选取元器件、电路组装、调试和检测等环节,初步掌握简单实用电路的分析方法和工程设计方法。

4)学会简单电路的实验调试和性能指标的测试方法,提高学生动手能力和进行数字电子电路实验的基本技能,学会使用Multisim仿真软件。

2.设计要求及方案论证2.1设计要求(1)四组参赛者在进行抢答时(用4组彩灯代表),当抢先者按下面前的按钮时,抢答器能准确地判断出抢先者,并以声、光为标志。

要求声响、光亮时间为9秒后自动熄灭。

(2)抢答器应具有互锁功能,某组抢答后能自动封锁其他各组进行抢答。

(3)抢答器应具有限时(抢答时间、回答问题时间)的功能。

限时档次分别为30秒、60秒、90秒;时间到时应发出声响。

同时,时间数据要用数码管显示出来。

(4)抢答者犯规或违章时,应自动发出警告信号,以提示灯光闪为标志。

(5)系统应具有一个总复位开关。

2.2方案论证方案一,用优先编码器74LS148和74LS279锁存器实现抢答和锁存功能,用加法器74LS160实现计数功能,但此方案电路繁琐复杂,不做选用。

方案二,用4D触发器74LS175实现抢答并锁存功能,用计数器74LS192实现定时功能,此方案电路相对简单,并且74LS192可以实现减数倒计时功能,所以选用方案二。

四路抢答器电路组成及工作原理(含电路图)

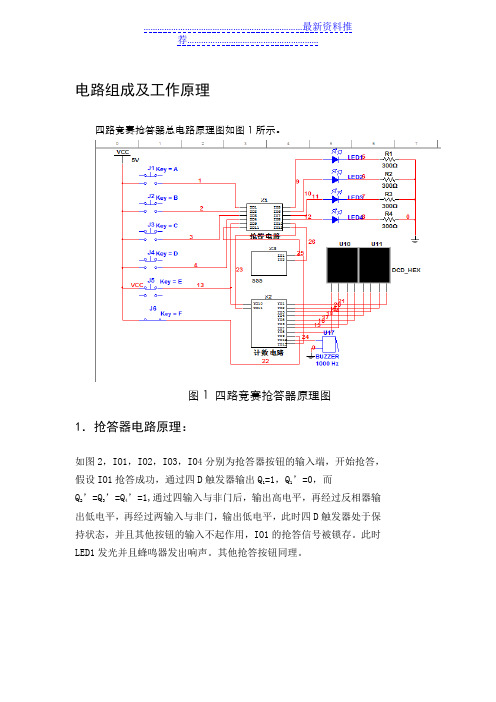

电路组成及工作原理四路竞赛抢答器总电路原理图如图1所示。

图1 四路竞赛抢答器原理图1.抢答器电路原理:如图2,IO1,IO2,IO3,IO4分别为抢答器按钮的输入端,开始抢答,假设IO1抢答成功,通过四D触发器输出Q1=1,Q1’=0,而Q 2’=Q3’=Q4’=1,通过四输入与非门后,输出高电平,再经过反相器输出低电平,再经过两输入与非门,输出低电平,此时四D触发器处于保持状态,并且其他按钮的输入不起作用,IO1的抢答信号被锁存。

此时LED1发光并且蜂鸣器发出响声。

其他抢答按钮同理。

图2 抢答器部分电路图2.计时电路原理:计时电路为两片74LS160用置数法构成的31进制计数器,因为可以为了让答题者直观的看到30S这个时间点,所以设置了31进制的计数器。

两片的四个输入端均接低电平,两片的输出端分别接七段译码管直接显示数字,高位的74LS160芯片的Q1Q2接到一个二输入的与非门(U8A)输出到计数器的LD端、三输入与非门端、反相器端。

输出到LD端是为了构成31进制计数器,当高位变为3时,计数器置0。

输出到三输入与非门(U9A)和时钟脉冲、开关的电平信号一起输入到与非门中,这就是为什么能控制计时的开始与暂停了,当开关输入低电平时,无论是否有时钟信号,时钟均不发生改变,此时时钟信号为无效信号;而当开关输入高电平时,U8A输出也为高,因此,时钟信号为有效信号,因此,凭借这样的类似锁存的电路,就可以控制计时的开始与暂停。

而当时间到了30s时,U8A输出为低电平,时钟信号又成为无效信号,时间被停止在30s,此时将U8A信号通过一个反相器输出到蜂鸣器,蜂鸣器发出响声。

图3 计时器电路3.555函数发生器:输出高电平时间:T1=(R1+R2)Cln2 输出低电平时间:T2=R2Cln2 振荡周期:T=(R1+2R2)Cln2图4 555函数发生器。

基于STM32的四路抢答器

课程设计说明书题目:基于STM32的四路抢答器学院:年级专业:学号:学生姓名:指导教师:摘要在各种智力竞赛场合,抢答器是必不可少的最公正的用具。

在我们各种竞赛中我们也经常能看到有抢答的环节,某些举办方采用让选手通过举答题板的方法判断选手的答题权,这在某种程度上会因为主持人的主观误断造成比赛的不公平性,而抢答器的应用就能避免这种弊端。

今天随着科技的不断进步抢答器的制作也更加追求精益求精,人们摆脱了耗费很多元件仅来实现用指示灯和一些电路来实现简单的抢答功能,使第一个抢答的参赛者的编号能通过指示灯显示出来,避免不合理的现象发生。

但这种电路不易于扩展,而且当有更高要求时就无法实现,例如参赛人数的增加。

随着数字电路的发展,数字抢答器诞生了,它易于扩展,可靠性好,集成度高,而且费用低,功能更加多样,是一种高效能的产品。

而如今在市场上销售的抢答器大多采用可编程逻辑元器件,或利用单片机技术进行设计。

本文实现了一个基于嵌入式STM32单片机的4路抢答器系统设计,本系统设计主要分为硬件设备和软件控制两大部分。

外部硬件使用STM32单片机作为控制中心,用4个按键作为抢答输入,抢答开始后,抢答成功者的LED灯标识为红色闪烁,并且显示各抢答输入的时间。

关键词:智能抢答器,STM32,按键输入,数码管显示目录摘要 (2)目录 (3)第1章绪论 (5)1.1课题研究的相关背景 (5)1.2选题的目的和意义 (5)1.3课题研究的内容 (5)1.4国内外研究现状 (6)1.5抢答器目前存在的主要问题 (6)第2章抢答器的系统概述 (7)2.1系统的主要功能 (7)2.2抢答器的工作流程 (7)2.3STM32的功能及简介 (7)2.4抢答器的优点及组成 (10)2.5本章小结 (11)第3章系统的硬件设计与开发 (11)3.1系统硬件总体设计 (11)3.2STM32最小系统 (12)3.4时钟频率电路的设计 (14)3.5复位电路的设计 (15)3.6数码管显示 (16)3.7键盘电路的设计 (16)3.8LED电路 (18)3.9本章小结 (18)第4章系统的软件设计与开发 (19)4.4主要程序分析 (20)4.5本章小结 (29)第5章总结与展望 (30)5.1总结 (30)5.2展望 (31)致谢 (32)参考文献 (33)第1章绪论1.1 课题研究的相关背景抢答器是一种应用非常广泛的设备,在各种竞赛、抢答场合中,它能迅速、客观地分辨出最先获得发言权的选手。

四路抢答器电路组成及工作原理(含电路图)

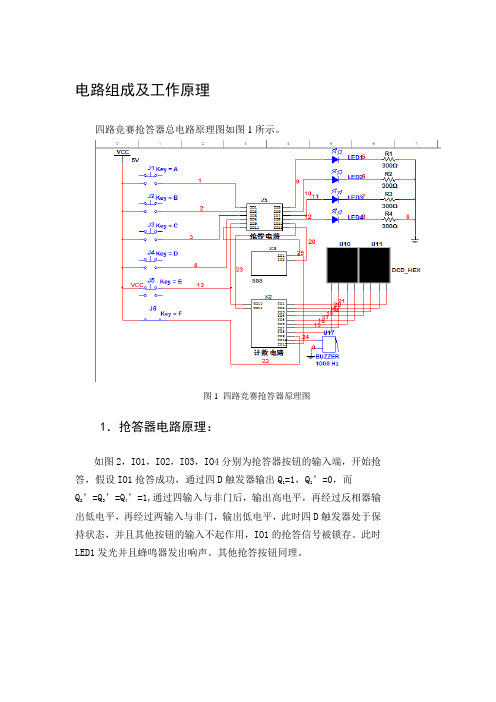

电路组成及工作原理四路竞赛抢答器总电路原理图如图1所示。

图1 四路竞赛抢答器原理图1.抢答器电路原理:如图2,IO1,IO2,IO3,IO4分别为抢答器按钮的输入端,开始抢答,假设IO1抢答成功,通过四D触发器输出Q1=1,Q1’=0,而Q 2’=Q3’=Q4’=1,通过四输入与非门后,输出高电平,再经过反相器输出低电平,再经过两输入与非门,输出低电平,此时四D触发器处于保持状态,并且其他按钮的输入不起作用,IO1的抢答信号被锁存。

此时LED1发光并且蜂鸣器发出响声。

其他抢答按钮同理。

图2 抢答器部分电路图2.计时电路原理:计时电路为两片74LS160用置数法构成的31进制计数器,因为可以为了让答题者直观的看到30S这个时间点,所以设置了31进制的计数器。

两片的四个输入端均接低电平,两片的输出端分别接七段译码管直接显示数字,高位的74LS160芯片的Q1Q2接到一个二输入的与非门(U8A)输出到计数器的LD端、三输入与非门端、反相器端。

输出到LD端是为了构成31进制计数器,当高位变为3时,计数器置0。

输出到三输入与非门(U9A)和时钟脉冲、开关的电平信号一起输入到与非门中,这就是为什么能控制计时的开始与暂停了,当开关输入低电平时,无论是否有时钟信号,时钟均不发生改变,此时时钟信号为无效信号;而当开关输入高电平时,U8A输出也为高,因此,时钟信号为有效信号,因此,凭借这样的类似锁存的电路,就可以控制计时的开始与暂停。

而当时间到了30s时,U8A输出为低电平,时钟信号又成为无效信号,时间被停止在30s,此时将U8A信号通过一个反相器输出到蜂鸣器,蜂鸣器发出响声。

图3 计时器电路3.555函数发生器:输出高电平时间:T1=(R1+R2)Cln2输出低电平时间:T2=R2Cln2振荡周期:T=(R1+2R2)Cln2图4 555函数发生器。

四人抢答器电路的制作与调试(单片机)

编号:审定成绩:XXXX大学课程设计(单片机)设计(论文)题目:四人抢答器电路的制作与调试(单片机)学院名称:计算机学院学生姓名:X X专业:计算机科学与技术班级:学号:指导教师:X X X答辩组负责人:填表时间:2005 年 6 月XXXX大学教务处P2-M4.1抢答器功能分析抢答器是竞赛问答中一种常用的必备装置,从原理上讲,它是一种典型的数字电路,其中包括了组合逻辑电路和时序电路。

本课题介绍一款采用D触发器数字集成电路制成的数字显示四路抢答器,它利用数字集成电路的锁存特性,实现优先抢答和数字显示功能,要求如下:1.设计一个可供4名选手参加比赛的4路数字显示抢答器。

他们的编号分别为“1”、“2”、“3”、“4”各用一个抢答按钮,编号与参赛者的号码一一对应。

2.抢答器具有数据锁存功能,并将锁存的数据用LED数码管显示出抢答成功者的号码。

3.抢答器对抢答选手动作的先后有很强的分辨能力,即使他们的动作仅相差几毫秒,也能分辨出抢答者的先后来。

即不显示后动作的选手编号。

4.主持人具有手动控制开关,可以手动清零复位,为下一轮抢答做准备。

一、抢答器的组成抢答器的一般组成框图如图2-4-1所示。

它主要由开关阵列电路、触发锁存电路、编码器、7段显示译码器、数码显示器等几部分组成。

下面逐一给予介绍。

图2-4-1抢答器的组成框图(1) 开关阵列电路该电路由多路开关所组成,每一竞赛者与一组开关相对应。

开关应为常开型,当按下开关时,开关闭合;当松开开关时,开关自动弹出断开。

(2) 触发锁存电路当某一开关首先按下时,触发锁存电路被触发,在输出端产生相应的开关电平信息,同时为防止其它开关随后触发而产生紊乱,最先产生的输出电平变化又反过来将触发电路锁定。

(3) 编码器编码器的作用是将某一开关信息转化为相应的8421BCD码,以提供数字显示电路所需要的编码输入。

(4) 7段显示译码器译码驱动电路将编码器输出的8421BCD码转换为数码管需要的逻辑状态,并且为保证数码管正常工作提供足够的工作电流。

四路竞赛抢答器设计·PPT

RS触发器分三种:基本RS触发器、 同步RS触发器、主从RS触发器。 74ls279是四个基本RS触发器,输入 的是R非、S非。当S非端输入0,R 非端输入0,则Q为1。当S非端输入 0,R非端输入1,则Q为1。当S非端 输入1,R非端输入0,则Q为0。S非 端输入1,当R非端输入1,则Q为保 持。

单稳态触发器 无触发信号时电路工作在稳定 状态,当UI受到下降脉冲时, 触发器由0变为1,但此状态不 稳定,会根据电阻与电容的大 小回复稳定状态。根据此特点 来作为此电路中的定时器。

多谐振荡器 在电容UC充电与放电的过程与 比较器C1在1、0之间跳变的过 程的作用下,电路会在两个暂稳 态之间来回翻转—振荡,因此产 生矩形脉冲。根据此特点为此电 路产生秒脉冲。

四路竞赛抢答器设计

设计人:杨翔 樊明 班级:162903

设计要求

• 该电路的根本任务是准确的判断出第一抢答者 的信号并将其锁存。实现这一功能可用触发器 和锁存器等。在得到第一信号后应立即将电路 的输入封锁,即使其他组再次发出抢答信号也 无效。同时还必须注意,第一抢答信号应该在 主持人发出抢答命令之后才有效。当电路形成 第一抢答信号之后,用编码、译码及数码显示 电路显示出抢答者的组别,也可以用发光二级 管直接指示出组别。

编号显示器 显示抢答选 手编号

倒计时器控式开 关 由主持人控制

七段数码管译码器驱动 器74LS48

同步十进制可逆计数器 74LS192

555构成的多谐振荡器, 用来产生秒脉冲

74LS192具有:双时钟十进制可逆计数功能;并具有清除 和置数等功能。 A—D :并行数据输入端 QA— QD :数据输出端 UP:加法计数器脉冲输入端 DOWN:减法计数脉冲输入端 CLR:异步置0端(高电平有效) ~LOAD:置数控制端(低电平有效) ~CO:加法计数时,进位输出端(低电平有效) ~BO:减法计数时,借位输出端(低电平有效)

4路抢答器设计原理图

module jiaozhiqi(clk,out,waveout);input clk;output out,waveout;reg[0:0] out;reg[0:0] waveout;reg code0,code1,code2,code3;reg A[15:0];reg B[15:0];reg[4:0] I,J,f;wire clk;reg c;reg[30:0] count;//将个变量进行初始化initialbeginI<=0;J<=0;f<=0;code0<=1;code1<=0;code2<=0;code3<=0;end//分频器的产生,可以调节交织器的频率大小always @(posedge clk)begincount=count+1;if(count==1)begincount=0;c=~c;endend//这里分两个部分,一是伪随机码的产生,二是交织码的产生always @(posedge c)begincode0<=1;code1<=1;code2<=1;code3<=0;if(code0|code1|code2|code3)begincode0<=code0^code3; //用模二加法产生反馈信号,产生伪随机码code1<=code0;code2<=code1;code3<=code2;endif(I==15) //循环机制的产生,用于产生4*4的数组beginI=0;f=~f;endelseI=I+1;if(J==3)beginJ=0;endelseJ=J+1;if(!f) //当第一个循环周期时,pn码按行写入A,同时B按列读出,但此时B里面的单元为都0,所以第一个循环begin //周期内,out(未交织)和waveout(交织后)输出均为0;A[I]<=code3;out<=B[I];if(I<4)waveout<=B[0+4*J];else if(I<8)waveout<=B[1+4*J];else if(I<12)waveout<=B[2+4*J];elsewaveout<=B[3+4*J];endelse // 第二个循环周期,pn码开始写入B,因为A在前面第一个周期已经写满(16个值),begin //A可以同时按行按列读出了,此时交织才正式开始。

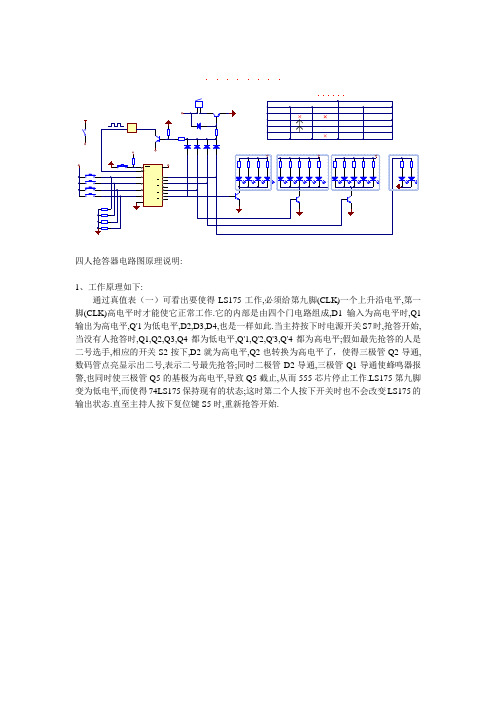

四人抢答器电路图原理说明

1、工作原理如下:

通过真值表(一)可看出要使得LS175工作,必须给第九脚(CLK)一个上升沿电平,第一脚(CLK)高电平时才能使它正常工作.它的内部是由四个门电路组成,D1输入为高电平时,Q1输出为高电平,Q'1为低电平,D2,D3,D4,也是一样如此.当主持按下时电源开关S7时,抢答开始,当没有人抢答时,Q1,Q2,Q3,Q4都为低电平,Q'1,Q'2,Q'3,Q'4都为高电平;假如最先抢答的人是二号选手,相应的开关S2按下,D2就为高电平,Q2也转换为高电平了,使得三极管Q2导通,数码管点亮显示出二号,表示二号最先抢答;同时二极管D2导通,三极管Q1导通使蜂鸣器报警,也同时使三极管Q5的基极为高电平,导致Q5截止,从而555芯片停止工作.LS175第九脚变为低电平,而使得74LS175保持现有的状态;这时第二个人按下开关时也不会改变LS175的输出状态.直至主持人按下复位键S5时,重新抢答开始.